半导体装置、放大装置以及半导体装置的制造方法与流程

本发明涉及半导体装置、放大装置以及半导体装置的制造方法。

背景技术:

1、在量子计算机中,来自量子位的微波输出信号极其微弱,使用以低噪声放大微波输出信号的低噪声放大器。放大器中使用的晶体管的噪声特性很大程度上依赖于栅电容,因此优选缩短栅长度来降低栅电容。但是,即使缩短栅长度来减小本征电容,在为了从外部布线供给信号而与栅电极连接的电极焊盘之下也存在介电常数高的半导体层,其结果,成为相对较大值的电极焊盘的寄生电容作为栅电极的电容而残留。电极焊盘的面积为几μm见方,远大于栅长度的几十nm,因此,电极焊盘的寄生电容成为对放大器的噪声降低的大的阻碍因素。由于为了电连接而设置的电极焊盘需要最小限度程度的面积,所以通过电极焊盘的尺寸减小来降低寄生电容是有限的。

2、现有技术文献

3、专利文献

4、专利文献1:日本特开2001-96499号公报

5、专利文献2:日本特开平6-53714号公报

6、专利文献3:美国专利申请公开2013-0043945号说明书

技术实现思路

1、发明要解决的课题

2、鉴于以上情况,期望降低与栅电极连接的电极焊盘的寄生电容的半导体装置。

3、解决课题的手段

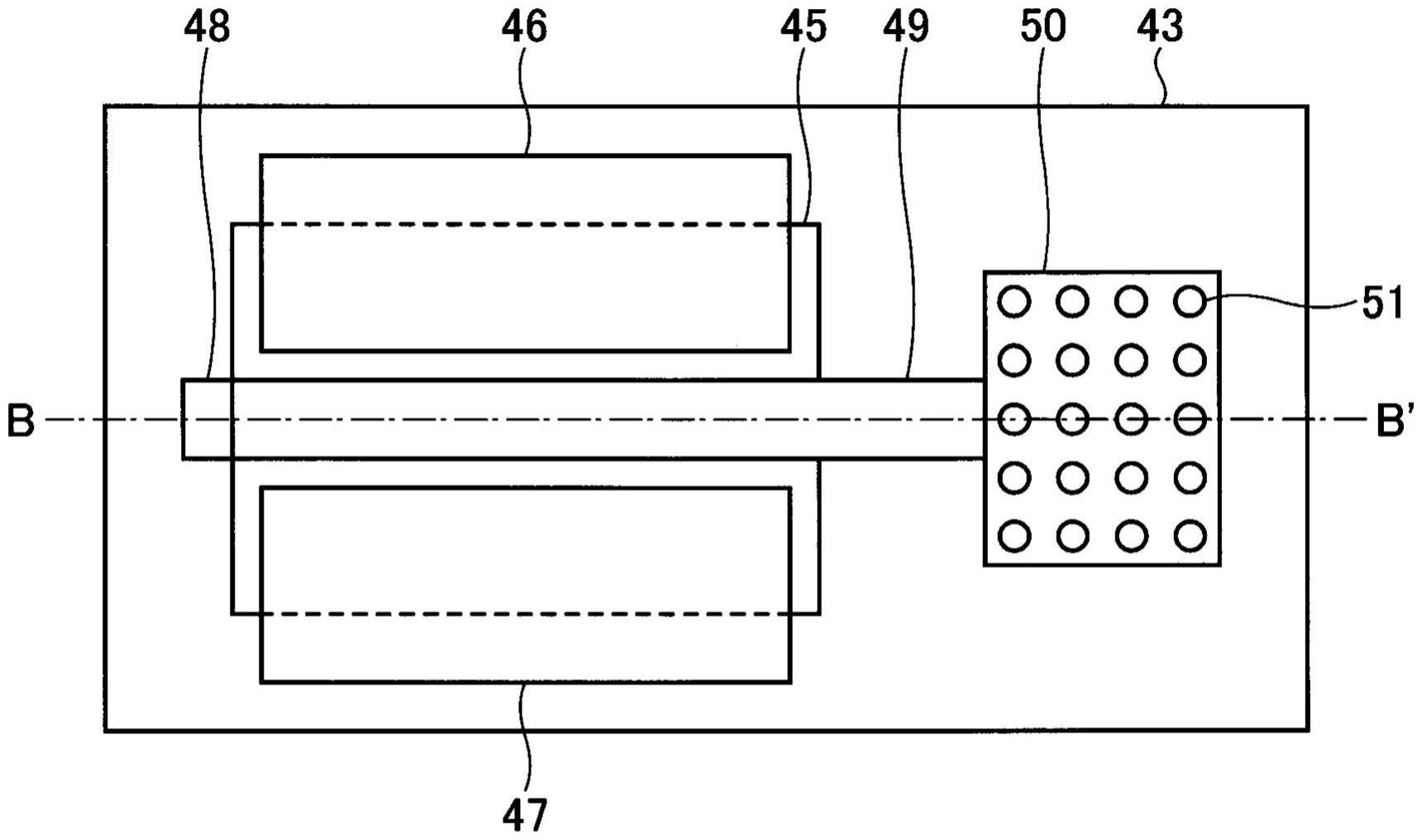

4、半导体装置包括基板、配置在基板上的栅电极、源电极及漏电极、以相对于基板的上表面垂直延伸的方式在基板的上表面2维排列的非导电性的多个纳米线、在多个纳米线的上端以与基板之间具有空隙的方式配置并由多个纳米线支撑的电极焊盘、以及连接电极焊盘与栅电极的引出电极。

5、发明的效果

6、根据本申请的至少1个实施例,能够得到降低了与栅电极连接的电极焊盘的寄生电容的半导体装置。

技术特征:

1.一种半导体装置,其包括:

2.根据权利要求1所述的半导体装置,其中,该半导体装置还包括形成在所述基板的上表面上的有源区,所述栅电极、源电极和漏电极形成在所述有源区的上表面上,所述有源区包括沟道层和电子供给层。

3.根据权利要求1或2所述的半导体装置,其中,所述多个纳米线由非掺杂的gaas形成。

4.根据权利要求1至3中的任意一项所述的半导体装置,其中,所述基板包括由与形成所述多个纳米线的材料相同的材料形成的第1层,所述多个纳米线的下端与所述第1层相接。

5.根据权利要求1至4中的任意一项所述的半导体装置,其中,所述多个纳米线由通过引入缺陷而钝化的半导体形成。

6.根据权利要求1至5中的任意一项所述的半导体装置,其中,该半导体装置还包括设置在所述基板之上的绝缘膜,所述绝缘膜在所述多个纳米线的位置处具有间隙,从而所述多个纳米线中的至少一部分不与所述绝缘膜相接。

7.根据权利要求1或2所述的半导体装置,其中,所述纳米线由绝缘体形成。

8.一种放大电路,其包括:

9.一种半导体装置的制造方法,包括如下的各个阶段:

技术总结

半导体装置包括基板、配置在基板上的栅电极、源电极及漏电极,以相对于基板的上表面垂直延伸的方式在基板的上表面2维排列的非导电性的多个纳米线、在多个纳米线的上端以与基板之间具有空隙的方式配置并由多个纳米线支撑的电极焊盘以及将电极焊盘与栅电极连接的引出电极。

技术研发人员:高桥刚,河口研一

受保护的技术使用者:富士通株式会社

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!