具有主动衬底偏置的双向开关的制作方法

1.本发明涉及半导体装置制造及集成电路,且更具体地说,涉及用于双向开关(bidirectional switch)的结构及形成这样结构的方法。

背景技术:

2.双向开关是用于ac-ac矩阵转换器(matrix converter)、太阳能微型逆变器(solar micro-inverter)、电池管理及其他功率装置应用。在双向开关中发现的高压功率电子装置(例如高电子迁移率晶体管(high-electron-mobility transistor))可使用iii-v族化合物半导体制造,以利用它们的材料特性(例如载流子迁移率(carrier mobility)大于硅的载流子迁移率,且比硅较高的临界电场强度(critical electric field strength),从而能够以较低的漏极至源极电阻(lower-drain-to-source resistance)及较小的装置尺寸实现较高电压的操作。iii-v族化合物半导体包含与v族元素(氮、磷、砷、锑)组合的iii族元素(铝、镓、铟)。高电子迁移率晶体管可包含具有不同带隙(band gaps)的结晶iii-v族化合物半导体材料之间的异质结(heterojunction)(例如二元氮化镓与三元氮化铝镓之间的异质结)。在操作期间,在异质结的界面处附近产生二维电子气。

3.与金属氧化物半导体场效应晶体管不同,高电子迁移率晶体管从源极到漏极欠缺可偏置的本体二极管(body diode)。本体二极管的欠缺有利于切换应用(switching applications),因为可实现改进的双向电流流动。然而,现有的双向开关在装置操作期间未考虑到衬底偏置(substrate biasing)。

4.对于某些切换应用,一对高电子迁移率晶体管可串联连接以形成双向开关。然而,串联连接需要各装置的额定值是所需总开关电阻的二分之一。

5.需要改进的双向开关结构及形成这样结构的方法。

技术实现要素:

6.在本发明的一实施例中,一种结构包含具有沟槽的衬底及在沟槽中的衬底接触件。位于衬底上的双向开关包含第一源极/漏极电极、第二源极/漏极电极、第一源极/漏极电极与第二源极/漏极电极之间的延伸区、及栅极结构。也位于衬底上的衬底偏置开关包含栅极结构、耦接到第一衬底接触件的第一源极/漏极电极、耦接到双向开关的第一源极/漏极电极的第二源极/漏极电极、及横向地位于栅极结构与第一源极/漏极区之间的延伸区。

7.在本发明的一实施例中,一种方法包含在衬底中形成第一沟槽、在第一沟槽中形成第一衬底接触件、在衬底上形成双向开关、以及在衬底上形成衬底偏置开关。双向开关包含第一源极/漏极电极、第二源极/漏极电极、第一源极/漏极电极与第二源极/漏极电极之间的延伸区、及第一栅极结构。衬底偏置开关包含栅极结构、耦接到第一衬底接触件的第一源极/漏极电极、耦接到双向开关的第一源极/漏极电极的第二源极/漏极电极、及横向地位于栅极结构与第一源极/漏极区之间的延伸区。

附图说明

8.包含在本说明书中且构成本说明书的一部分的附图说明本发明的各种实施例,且与上方给出的本发明的一般描述及下方给出的实施例的详细描述一起用于解释本发明的实施例。在各种附图中,相同的附图标记表示相同的特征。

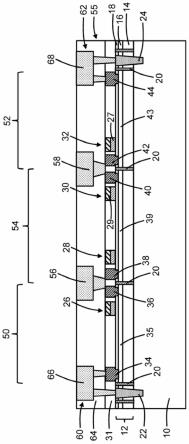

9.图1是根据本发明实施例的在初始制造阶段的结构的截面视图。

10.图2是在图1之后的制造阶段的结构的截面视图。

11.图3是图2的结构的电路示意图。

12.图4是根据本发明实施例的结构的布局(layout)视图。

13.图5-图8是根据本发明实施例的结构的截面视图。

14.图9是根据本发明实施例的结构的布局视图。

具体实施方式

15.参照图1且根据本发明的实施例,在衬底10上形成层堆栈(layer stack)12。衬底10可以是包含单晶半导体材料(例如,单晶硅)的块状衬底(bulk substrate)。在一实施例中,衬底10的单晶半导体材料可以是具有《111》晶体定向(crystal orientation)的单晶硅。在其他实施例中,衬底10可由碳化硅、蓝宝石或氮化镓组成。

16.层堆栈12可包含缓冲层14、沟道层16及阻挡层18,各层包含一个或多个化合物半导体层。使用外延生长工艺(例如金属有机化学气相沉积(metalorganic chemical vapor deposition)、气相外延(vapor phase epitaxy)或分子束外延(molecular beam epitaxy))可连续沉积层14、16、18以形成层堆栈。在层堆栈12与衬底10之间可提供成核层(nucleation layer)(未示出)。层14、16、18各层可具有单晶的晶体结构,或者,具有不同程度的结晶缺陷存在的实质上单晶的晶体结构。缓冲层14可包含二元或三元iii-v族化合物半导体材料,例如氮化镓、氮化铝、氮化铝镓或这些材料的组合,其在材料成分、掺杂及/或层厚度方面被定制以适应衬底10的材料与沟道层16的材料之间的晶格失配、热性能差异及机械性能差异。设置在缓冲层14上方的沟道层16可包含二元iii-v族化合物半导体材料(例如氮化镓),且可以是未掺杂的。设置在沟道层16上方的阻挡层18可包含三元iii-v族化合物半导体,例如具有15原子百分比铝至35原子百分比铝的氮化铝镓,其提供与沟道层16的异质界面不同的成分。阻挡层18连同沟道层16的材料特性有助于在装置操作期间在层16、18之间的界面处产生二维电子气。

17.隔离区20形成在层堆栈12中。通过例如物种(例如氮或氩)的掩蔽离子注入(masked ion implantation)可形成隔离区20。隔离区20可用于终止及定位在操作期间形成的二维电子气层。或者,隔离区20可以是具有深度足以穿透在操作期间形成的二维电子气层的沟槽。

18.形成衬底接触件22、24,其延伸穿过层堆栈12的层14、16、18的各自区段且进入层堆栈12下方的衬底10的部分。通过用光刻及蚀刻工艺图案化沟槽23、25且用平坦化的导体(例如包含钨或掺杂多晶硅的插塞(plug))填充沟槽23、25可形成布置在装置结构的外围的衬底接触件22、24。衬底接触件22、24通过隔离区20与层堆栈12的层14、16、18的周围区段电性隔离。

19.栅极结构26、28、30、32形成在层堆栈12的不同部分上。栅极结构28及30横向地布

置在栅极结构26与栅极结构32之间。栅极结构26、28、30、32可包括栅极27及位于栅极27上和上方的栅极金属层29。各栅极27可定位成与阻挡层18接触,且在一实施例中,各栅极27可与阻挡层18直接接触。栅极27可由掺杂的iii-v族化合物半导体组成,例如掺杂有镁的p型氮化镓或p型铝镓氮化物,且栅极金属层29可由一个或多个金属组成,例如铝铜、氮化钛、钛等。

20.通过用光刻及蚀刻工艺图案化掺杂的iii-v族化合物半导体(例如,p型氮化镓)层可形成栅极27,接着通过介电层31(例如,二氧化硅、氧化铝、或氮化硅)的沉积以钝化阻挡层18的表面且内衬栅极27的侧壁。在栅极27的位置处的介电层31中图案化开口,接着通过沉积一个或多个金属的层,用光刻及蚀刻工艺图案化,且退火以限定栅极金属层29。在栅极结构26、28、30、32及介电层31上方可形成介电栅极盖层(dielectric gate cap layer)(未示出)。

21.参照图2,其中相同的附图标记表示与图1中相同的特征,且在随后的制造阶段,源极/漏极电极34、36、38、40、42、44形成在层堆栈12的不同部分上。源极/漏极电极34、36、38、40、42、44可包括奥姆金属(例如钛、氮化钛、铝、硅或这些材料的组合)。通过用光刻和蚀刻工艺及退火而图案化延伸穿过介电层31且可选地部分地穿过阻挡层18的窗口、沉积奥姆金属层、图案化所沉积的层可形成源极/漏极电极34、36、38、40、42、44。源极/漏极电极34、36、38、40、42、44可定位成与阻挡层18接触,且在一实施例中,可与阻挡层18直接接触。隔离区20的一者是横向地定位于源极/漏极电极36与源极/漏极电极38之间的层堆栈12中,且隔离区20的另一者是横向地位于源极/漏极电极40与源极/漏极电极42之间的层堆栈12中。

22.提供衬底偏置的衬底偏置开关50包含源极/漏极电极34、源极/漏极电极36及横向地布置在源极/漏极电极34与源极/漏极电极36之间的栅极结构26。在一实施例中,源极/漏极电极34可提供衬底偏置开关50的漏极,且源极/漏极电极36可提供衬底偏置开关50的源极。通过沟道层16的一区段所提供的延伸区35是横向地定位于源极/漏极电极34与栅极结构26之间。延伸区35通过隔离区20的其中一者而与穿过沟道层16的区段的衬底接触件22电性隔离。

23.提供衬底偏置的衬底偏置开关52包含源极/漏极电极42、源极/漏极电极44及横向地布置在源极/漏极电极42与源极/漏极电极44之间的栅极结构32。在一实施例中,源极/漏极电极44可提供衬底偏置开关52的漏极,且源极/漏极电极42可提供衬底偏置开关52的源极。通过沟道层16的一区段所提供的延伸区43是横向地位于源极/漏极电极42与源极/漏极电极44之间。延伸区43通过隔离区20的其中一者而与穿过沟道层16的区段的衬底接触件24电性隔离。衬底偏置开关52在结构上类似于衬底偏置开关50。

24.可提供双向切换(bidirectional switching)的双向开关54包含源极/漏极电极38、源极/漏极电极40及横向地布置在源极/漏极电极38与源极/漏极电极40之间的栅极结构28、30。通过沟道层16的一区段所提供的延伸区39是横向地定位于源极/漏极电极38与源极/漏极电极40之间。当作为开关操作时,栅极结构28及30的间隔距离足以支持双向开关54的操作电压。双向开关54可在增强模式下操作,其中需要将正偏置电压施加到栅极结构28或栅极结构30以改变方向性。

25.源极/漏极电极34、36、38、40、42、44可包含与各自的延伸区35、39、43重叠的可选场板(field plates)(未示出)。栅极金属层29可包含通过在各自的延伸区上方延伸栅极金

属或通过添加与各自的延伸区35、39、43重叠的额外金属层而形成可选场板(未示出)。

26.接着是中段处理(middle-of-line processing)及后段处理(back-end-of-line processing),其包含用于定位于衬底10上方且耦接到衬底偏置开关50、52及双向开关54的互连结构的金属化层级的接触件、通孔及布线的形成。在这方面,衬底偏置开关50的源极/漏极电极36及双向开关54的源极/漏极电极38两者物理性且电性耦接到互连结构的金属化层级55中的金属特征56。衬底偏置开关52的源极/漏极电极42及双向开关54的源极/漏极电极40两者物理性且电性耦接到互连结构的金属化层级55中的金属特征58。通孔及金属特征66在互连结构的金属化层级55中定义互连件60,该互连结构耦接衬底偏置开关50的源极/漏极电极34与衬底接触件22。通孔及金属特征68在互连结构的金属化层级55中定义互连件62,该互连结构耦接衬底偏置开关52的源极/漏极电极44与衬底接触件24。

27.在一实施例中,金属特征56、58及互连件60、62可被包含在最靠近衬底10的互连结构的第一金属化(m1)层级中。金属特征56、58及互连件60、62可形成在一个或多个介电层64中,介电层64例如由二氧化硅及/或氮化硅组成。互连结构的额外金属化层级可形成在m1层级上方,且最顶部的金属化层级可包含接合焊盘(bond pad)。

28.参照图2及3且根据本发明的实施例,衬底偏置开关50、52及双向开关54可用于电路中以提供耦接功率装置70与功率装置72的横向双向开关。功率装置70与双向开关54的栅极结构28耦接,且功率装置72与双向开关54的栅极结构30耦接。在一实施例中,功率装置70、72可以是交流(alternating-current,ac)电源。

29.衬底偏置开关50、52在位于内部且未有外部连接的双向开关54的操作期间提供主动(active)衬底偏置。在这方面,衬底偏置开关52的栅极结构26耦接到双向开关54的栅极结构28,且衬底偏置开关52的栅极结构32耦接到双向开关54的栅极结构30。通过其中栅极结构26、28为臂(arm)的u形栅极结构及其中栅极结构30、32为臂的另一u形栅极结构可实现栅极耦接,如图4最佳所示。

30.如果栅极结构26、28在操作期间被偏置在“导通”状态,则通过从源极/漏极电极36在内部连接中供应的电流,衬底10经由衬底接触件22被偏置,该内部连接包含栅极结构26下方的沟道、延伸区35、源极/漏极电极34及互连件60。如果栅极结构30、32在操作期间被偏置在“导通”状态,则通过从源极/漏极电极42在内部连接中供应的电流,衬底10经由衬底接触件24被偏置,该内部连接包含栅极结构32下方的沟道、延伸区43、源极/漏极电极44及互连件62。

31.在一实施例中,可提供与栅极结构26、28串联耦接的栅极电阻器74,且可提供与栅极结构30、32串联耦接的栅极电阻器76。栅极电阻器74可用于调节衬底偏置开关50的开启速度,且栅极电阻器76可用于调节衬底偏置开关52的开启速度。在替代实施例中,可以省略栅极电阻器74、76。

32.在一实施例中,源极/漏极电极36定义耦接到源极/漏极电极38的衬底偏置开关50的源极,其提供取决于功率装置70、72之间的电流流动方向的双向开关54的源极或漏极,且源极/漏极电极34定义通过互连件60耦接到衬底接触件22的衬底偏置开关50的漏极。在一实施例中,源极/漏极电极42定义耦接到源极/漏极电极40的衬底偏置开关52的源极,其提供取决于功率装置70、72之间的电流流动方向的双向开关54的源极或漏极,且源极/漏极电极44定义通过互连件62耦接到衬底接触件24的衬底偏置开关52的漏极。

33.参照图4,其中相同的附图标记表示图2中相同的特征,且根据本发明的实施例,双向开关54可包括布置为栅极指(gate finger)的多个栅极结构26、28以及也布置为栅极指的多个栅极结构30、32。多个栅极结构26、28可具有并联布置且可在一端共同连接。多个栅极结构26、28共同耦接到互连结构中的接合焊盘80。多个栅极结构30、32可具有并联布置且可在一端共同连接。多个栅极结构30、32共同耦接到互连结构中的接合焊盘82。

34.金属特征56布置在具有在各金属特征56下方所布置的源极/漏极电极的栅极结构28之间,如图2中的金属特征56下方的源极/漏极电极36、38所示。金属特征58布置在具有在各金属特征58下方所布置的源极/漏极电极的栅极结构30之间,如图2中的金属特征58下方的源极/漏极电极40、42所示。金属特征56共同耦接到互连结构中的接合焊盘84。金属特征58共同耦接到互连结构中的接合焊盘86。可选的栅极电阻器74、76可通过衬底10的部分来提供。

35.参照图5,其中相同的附图标记表示图2中相同的特征,且根据本发明的替代实施例,互连件60的金属特征66及互连件62的金属特征68可形成在布置在互连结构中的金属化层级55上方的金属化层级57中。在一实施例中,金属化层级57可以是仅通过互连结构的m1层级与衬底10分隔开的互连结构的第二金属化(m2)层级。互连件60、62的金属特征56、58放置在m1层级之上的m2层级中可能有利于较高电压(例如,大于200伏的电压)应用。

36.参照图6,其中相同的附图标记表示图2中相同的特征,且根据本发明的替代实施例,衬底10可以是绝缘体上硅(silicon-on-insulator)衬底,其包含装置层90、掩埋氧化物层91以及通过掩埋氧化物层91与装置层90分隔开的处理衬底(handle substrate)92。装置层90可由单晶半导体材料(例如,单晶硅)组成,且可以操作为用于层堆栈12的生长的种子层。掩埋氧化物层91可由二氧化硅组成,且处理衬底92可由单晶硅组成。

37.参照图7,其中相同的附图标记表示图2中相同的特征,且根据本发明的替代实施例,衬底10可以是工程衬底(engineered substrate),其包含由多晶陶瓷材料组成的处理衬底94,该多晶陶瓷材料与层堆栈12的材料的热膨胀特性紧密匹配。在一实施例中,处理衬底94可由与氮化镓的热膨胀特性紧密匹配的多晶氮化铝组成。在一实施例中,处理衬底94可由多晶碳化硅组成,其也与氮化镓的热膨胀特性紧密匹配。处理衬底94被包括工程层的层堆栈95覆盖,工程层为例如由二氧化硅、氮化硅、多晶硅等组成的层。层堆栈95被用于层堆栈12的生长而定制的种子层96覆盖。在实施例中,种子层96可由单晶《111》定向的硅、单晶氮化镓或单晶碳化硅组成。在代表性实施例中,衬底接触件22、24延伸到种子层96中且耦接到种子层96。

38.参照图8,其中相同的附图标记表示图7中相同的特征,且根据本发明的替代实施例,衬底接触件22、24可穿透种子层96且进入工程层的层堆栈95中。由于它们穿透种子层96,因此衬底接触件22、24耦接到种子层96。

39.参照图9,其中相同的附图标记表示图4中相同的特征,且根据本发明的替代实施例,衬底接触件22、24可重新定位到与金属特征56下方的源极/漏极电极相邻的位置(如图2中的金属特征56下方的源极/漏极电极36、38所示)以及与金属特征58下方的源极/漏极电极相邻的位置(如图2中的金属特征58下方的源极/漏极电极40、42所示)。

40.如上所述方法用于集成电路芯片的制造,最终的集成电路芯片可以原始晶圆形式(例如,作为具有多个未封装芯片的单个晶圆)、作为裸管芯(bare die)、或者以封装形式分

配。在后者的情况下,芯片安装在单个芯片封装中(例如,塑料载体,具有固定在主板(motherboard)或其他较高层级的载体上的引线(leads))或在多个芯片封装中(例如,具有表面互连或埋入互连的其中一者或两者的陶瓷载体)。在任何情况下,芯片可以与其他芯片、分立电路元件及/或其他信号处理设备集成,作为中间产品或最终产品的一部分。

41.本文中引用的由近似语言例如“约”、“大约”、和“实质上”修饰的用语,不限于精确的特定值。近似语言可对应于用于测量值的仪器的精度,除非依赖于仪器的精度,否则可表示所述值的+/-10%。

42.本文中引用术语例如“垂直”、“水平”等作为示例来建立参考框架,并非限制。本文中所使用的术语“水平”被定义为与半导体衬底的传统平面平行的平面,而不论其实际的三维空间取向。术语“垂直”及“正交”是指垂直于如刚刚所定义的水平面的方向。术语“横向”是指在该水平平面内的方向。

43.与另一个特征“连接”或“耦接”的特征可与该另一个特征直接连接或耦接,或者可存在一个或多个中间特征。如果不存在中间特征,则特征可与另一个特征“直接连接”或“直接耦接”。如果存在至少一个中间特征,则特征可与另一个特征“非直接连接”或“非直接耦接”。在另一个特征“上”或与其“接触”的特征可直接在该另一个特征上或与其直接接触,或者可存在一个或多个中间特征。如果不存在中间特征,则特征可直接在另一个特征“上”或与其“直接接触”。如果存在至少一个中间特征,则特征可“不直接”在另一个特征“上”或与其“不直接接触”。

44.对本发明的各种实施例所做的说明是出于示例说明目的,而非意图详尽无遗或限于所披露的实施例。许多修改及变更对于本领域的普通技术人员将显而易见,而不背离所述实施例的范围及精神。本文中所使用的术语经选择以最佳解释实施例的原理、实际应用或在市场已知技术上的技术改进,或者使本领域的普通技术人员能够理解本文中所披露的实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1