晶体管、半导体存储装置及晶体管的制造方法与流程

晶体管、半导体存储装置及晶体管的制造方法

1.[相关申请]

[0002]

本技术享有在2021年6月15日提出申请的日本专利申请编号2021-99736的优先权的利益,该日本专利申请的全部内容被引用在本技术中。

技术领域

[0003]

本发明的实施方式涉及一种晶体管、半导体存储装置及晶体管的制造方法。

背景技术:

[0004]

cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)晶体管等晶体管例如具备元件区域、及配置在元件区域上的栅极电极。在晶体管的制造步骤中,考虑到栅极电极会相对于元件区域发生位置偏移,有时会将栅极电极的宽度形成得比元件区域的宽度大。有时这会成为妨碍晶体管的小型化的主要因素。

技术实现要素:

[0005]

实施方式提供一种能够抑制栅极电极相对于元件区域的位置偏移的晶体管、半导体存储装置及晶体管的制造方法。

[0006]

实施方式的晶体管具备:半导体层;凸状的元件区域,设置在所述半导体层,在沿着所述半导体层的面的第1方向上具有指定宽度,且在沿着所述半导体层的面并且与所述第1方向交叉的第2方向上延伸;栅极电极,配置在所述元件区域的上方;及衬层,覆盖所述栅极电极;在所述元件区域的所述第1方向的两侧,沿所述第2方向延伸有元件分离部,且所述衬层从所述栅极电极连续地延伸到所述元件分离部,在所述元件分离部潜伏在所述元件分离部的下方。

附图说明

[0007]

图1是实施方式1的半导体存储装置的框图。

[0008]

图2是表示实施方式1的半导体存储装置所具备的存储单元阵列、感测放大器电路及锁存电路的构成的一例的等效电路图。

[0009]

图3是表示实施方式1的半导体存储装置所具备的感测放大器模块及数据寄存器的布局的一例的示意图。

[0010]

图4a及图4b是表示实施方式1的半导体存储装置所具备的晶体管的布局的一例的示意图。

[0011]

图5a~图5d是表示应用于实施方式1的半导体存储装置的晶体管的构成的一例的图。

[0012]

图6a及图6b是表示用于制造实施方式1的晶体管的模板的构成的一例的图。

[0013]

图7a~图7d是表示实施方式1的模板的制造方法的顺序的一例的图。

[0014]

图8aa~图8cb是表示实施方式1的晶体管的制造方法的顺序的一例的图。

[0015]

图9aa~图9cb是表示实施方式1的晶体管的制造方法的顺序的一例的图。

[0016]

图10aa~图10cb是表示实施方式1的晶体管的制造方法的顺序的一例的图。

[0017]

图11aa~图11cb是表示实施方式1的晶体管的制造方法的顺序的一例的图。

[0018]

图12a及图12b是表示实施方式1及比较例的半导体存储装置所具备的晶体管的布局的一例的示意图。

[0019]

图13a~图13c是表示应用于实施方式1的变化例1的半导体存储装置的晶体管的构成的一例的图。

[0020]

图14aa~图14cb是表示实施方式1的变化例1的晶体管的制造方法的顺序的一例的图。

[0021]

图15a及图15b是表示实施方式1的变化例2及比较例的半导体存储装置所具备的晶体管的布局的一例的示意图。

[0022]

图16是表示实施方式2的半导体存储装置所具备的行解码器的构成的一例的电路图。

[0023]

图17a及图17b是表示实施方式2的半导体存储装置所具备的晶体管的布局的一例的示意图。

[0024]

图18是实施方式3的半导体存储装置的框图。

[0025]

图19是表示包含实施方式3的半导体存储装置所具备的感测放大器电路的电路构成的一例的电路图。

[0026]

图20a及图20b是表示实施方式3及比较例的半导体存储装置所具备的晶体管的布局的一例的示意图。

具体实施方式

[0027]

以下,参照附图对本发明详细地进行说明。此外,并不利用下述实施方式来限定本发明。另外,下述实施方式中的构成要素中包含业者能容易地设想的构成要素或实质上相同的构成要素。

[0028]

[实施方式1]

[0029]

以下,参照附图,对实施方式1详细地进行说明。

[0030]

(半导体存储装置的概略构成)

[0031]

图1是实施方式1的半导体存储装置1的框图。如图1所示,半导体存储装置1具备输入输出电路110、逻辑控制电路120、状态寄存器130、地址寄存器140、指令寄存器150、定序器160、就绪/忙碌电路170、电压产生电路180、存储单元阵列10、行解码器20、感测放大器模块30、数据寄存器40及列解码器50。

[0032]

输入输出电路110对与控制半导体存储装置1的未图示的存储器控制器等外部装置的信号dq的输入输出进行控制。输入输出电路110具备未图示的输入电路与输出电路。

[0033]

输入电路将从外部装置接收到的写入数据wd等数据dat发送到数据寄存器40,将地址add发送到地址寄存器140,并将指令cmd发送到指令寄存器150。

[0034]

输出电路将从状态寄存器130接收到的状态信息sts、从数据寄存器40接收到的读出数据rd等数据dat以及从地址寄存器140接收到的地址add发送到外部装置。

[0035]

逻辑控制电路120从外部装置接收例如芯片使能信号cen、指令锁存使能信号cle、

地址锁存使能信号ale、写使能信号wen及读使能信号ren。另外,逻辑控制电路120根据所接收到的信号,控制输入输出电路110及定序器160。

[0036]

状态寄存器130例如暂时保存数据的写入动作、读出动作及抹除动作中的状态信息sts,向外部装置通知动作是否已正常结束。

[0037]

地址寄存器140暂时保存经由输入输出电路110从外部装置接收到的地址add。另外,地址寄存器140将行地址ra传输到行解码器20,将列地址ca传输到列解码器50。

[0038]

指令寄存器150暂时保存经由输入输出电路110从外部装置接收到的指令cmd,并传输到定序器160。

[0039]

定序器160对整个半导体存储装置1的动作进行控制。更具体来说,定序器160根据指令寄存器150所保存的指令cmd,控制例如状态寄存器130、就绪/忙碌电路170、电压产生电路180、行解码器20、感测放大器模块30、数据寄存器40及列解码器50等,执行写入动作、读出动作及抹除动作等。

[0040]

就绪/忙碌电路170根据定序器160的动作状况,将就绪/忙碌信号r/bn发送到外部装置。

[0041]

电压产生电路180根据定序器160的控制,产生写入动作、读出动作及抹除动作所需的电压,并将所产生的电压供给至例如存储单元阵列10、行解码器20及感测放大器模块30等。行解码器20及感测放大器模块30将从电压产生电路180供给的电压施加到存储单元阵列10内的存储单元。

[0042]

存储单元阵列10包含多个块blk(blk0~blkn)。n为2以上的整数。块blk是与位线及字线建立关联的多个存储单元的集合,例如成为数据的抹除单位。存储单元构成为例如晶体管,保存非易失性数据。

[0043]

通过具备这种存储单元,半导体存储装置1构成为例如nand(not and,与非)型非易失性存储器。但是,半导体存储装置1也可以构成为例如nor(not or,或非)型等其它非易失性存储器。

[0044]

行解码器20将行地址ra解码。另外,行解码器20基于解码结果,选择任一个块blk。另外,行解码器20对块blk施加所需电压。

[0045]

感测放大器模块30在读出动作时,感测从存储单元阵列10读出的数据。另外,感测放大器模块30将读出数据rd发送到数据寄存器40。在写入动作时,感测放大器模块30将写入数据wd发送到存储单元阵列10。

[0046]

数据寄存器40具备多个锁存电路。锁存电路保存写入数据wd及读出数据rrd。例如,在写入动作中,数据寄存器40暂时保存从输入输出电路110接收到的写入数据wd,并发送到感测放大器模块30。另外,例如,在读出动作中,数据寄存器40暂时保存从感测放大器模块30接收到的读出数据rd,并发送到输入输出电路110。

[0047]

列解码器50例如在写入动作、读出动作及抹除动作时,将列地址ca解码,并根据解码结果来选择数据寄存器40内的锁存电路。

[0048]

此外,将除存储单元阵列10以外的半导体存储装置1的所述各构成也称为周边电路。也就是说,周边电路包含输入输出电路110、逻辑控制电路120、状态寄存器130、地址寄存器140、指令寄存器150、定序器160、就绪/忙碌电路170、电压产生电路180、行解码器20、感测放大器模块30、数据寄存器40及列解码器50。

[0049]

像这样,实施方式1的半导体存储装置1具备包含多个存储单元的存储单元阵列10、及使多个存储单元进行动作的周边电路。

[0050]

(存储单元阵列的电路构成)

[0051]

图2是表示实施方式1的半导体存储装置1所具备的存储单元阵列10、感测放大器电路sa及锁存电路dl、xdl的构成的一例的等效电路图。首先,以下,对半导体存储装置1所具备的存储单元阵列10的电路构成的一例进行说明。

[0052]

如上所述,存储单元阵列10具备多个块blk。多个块blk分别具备多个串组件su。多个串组件su分别具备多个存储器串ms。多个存储器串ms的一端分别经由位线bl而连接于行解码器20及感测放大器模块30等周边电路。多个存储器串ms的另一端分别经由共通的源极线sl而连接于周边电路。

[0053]

存储器串ms具备串联连接在位线bl与源极线sl之间的漏极选择晶体管std、多个存储单元mc、及源极选择晶体管sts。以下,有时将漏极选择晶体管std及源极选择晶体管sts简称为选择晶体管(std、sts)。

[0054]

存储单元mc例如是栅极绝缘层中包含电荷储存层的场效应型晶体管(fet:field effect transistor)。存储单元mc的阈值电压根据电荷储存层中的电荷量而变化。可以通过设置1种或多种阈值电压,而使存储单元mc能够存储1比特或多比特的数据。在与1个存储器串ms对应的多个存储单元mc的栅极电极分别连接字线wl。这些字线wl分别共通连接于1个块blk中的所有存储器串ms。

[0055]

选择晶体管(std、sts)例如是场效应型晶体管。在选择晶体管(std、sts)的栅极电极分别连接选择栅极线(sgd、sgs)。连接于漏极选择晶体管std的漏极选择线sgd对应于串组件su而设置,且共通连接于1个串组件su中的所有存储器串ms。连接于源极选择晶体管sts的源极选择线sgs共通连接于1个块blk中的所有存储器串ms。

[0056]

(感测放大器模块的构成)

[0057]

接下来,利用图2及图3,对感测放大器模块30的构成例进行说明。

[0058]

所述感测放大器模块30包括针对每一个位线bl而设置的多个感测放大器电路sa。各感测放大器电路sa例如在读出动作中,感测已被读出到对应的位线bl的数据,判定所读出的数据是“0”还是“1”。

[0059]

另外,所述数据寄存器40中包含与多个感测放大器电路sa分别对应的多个锁存电路dl、xdl。另外,锁存电路xdl也针对每一个位线bl而设置。另一方面,锁存电路dl相对于对应的感测放大器电路sa而设置有多个。在该情况下,锁存电路dl的个数例如基于1个存储单元mc能够保存的数据的比特数而设计。锁存电路dl、xdl暂时保存与对应的位线bl有关的数据。

[0060]

首先,接着利用图2,对感测放大器模块30的电路构成的一例进行说明。图2中示出了感测放大器模块30内的1个感测放大器电路sa、及数据寄存器40内的1个锁存电路dl、xdl。此外,供给至感测放大器电路sa等的多个控制信号由定序器160控制。

[0061]

如图2所示,感测放大器电路sa包含晶体管tr

31

~tr

38

及电容器cap。图中,晶体管tr

31

是低耐压p通道mos(metal-oxide-semiconductor,金属氧化物半导体)晶体管。另外,晶体管tr

32

~tr

38

是低耐压n通道mos晶体管。以下,有时将感测放大器电路sa中包含的晶体管tr

31

~tr

38

简称为晶体管tr。

[0062]

晶体管tr

31

的一端连接于供给电源电压vdd的电源线,晶体管tr

31

的栅极电极连接于节点inv。晶体管tr

32

的一端连接于晶体管tr

31

的另一端,晶体管tr

32

的另一端连接于节点com,对晶体管tr

32

的栅极电极输入控制信号blx。晶体管tr

33

的一端连接于节点com,晶体管tr

33

的另一端连接于对应的位线bl,对晶体管tr

33

的栅极电极输入控制信号blc。

[0063]

晶体管tr

34

的一端连接于节点com,晶体管tr

34

的另一端连接于节点src,晶体管tr

34

的栅极电极连接于节点inv。

[0064]

晶体管tr

35

的一端连接于晶体管tr

31

的另一端,晶体管tr

35

的另一端连接于节点sen,对晶体管tr

35

的栅极电极输入控制信号hll。晶体管tr

36

的一端连接于节点sen,晶体管tr

36

的另一端连接于节点com,对晶体管tr

36

的栅极电极输入控制信号xxl。

[0065]

对晶体管tr

37

的一端输入时钟clk,晶体管tr

37

的栅极电极连接于节点sen。晶体管tr

38

的一端连接于晶体管tr

37

的另一端,晶体管tr

38

的另一端连接于总线lbus,对晶体管tr

38

的栅极电极输入控制信号stb。电容器cap的一端连接于节点sen,对电容器cap的另一端输入时钟clk。

[0066]

锁存电路dl具备反相器iva、ivb及晶体管tr

41

、tr

42

。图中,晶体管tr

41

、tr

42

是低耐压n通道mos晶体管。以下,有时将数据寄存器40中包含的晶体管tr

41

、tr

42

简称为晶体管tr。

[0067]

此外,图2中示出了1个锁存电路dl,但数据寄存器40也可以像所述那样,相对于1个感测放大器电路sa具备多个锁存电路dl。未图示的其它锁存电路dl具有与图2的锁存电路dl同样的构成。

[0068]

反相器iva的输入端子连接于节点lat,输出端子连接于节点inv。反相器ivb的输入端子连接于节点inv,输出端子连接于节点lat。

[0069]

晶体管tr

41

的一端连接于节点inv,另一端连接于总线lbus,对栅极电极输入控制信号sti。晶体管tr

42

的一端连接于节点lat,另一端连接于总线lbus,对栅极电极输入控制信号stl。

[0070]

锁存电路xdl例如具备与锁存电路dl大致相同的构成,以能够与感测放大器电路sa及锁存电路dl收发数据的方式连接于总线lbus。另外,锁存电路xdl连接于所述输入输出电路110,用于感测放大器电路sa与输入输出电路110之间的数据的输入输出。

[0071]

另外,锁存电路xdl也使用于半导体存储装置1的高速缓冲动作用途。也就是说,即使与感测放大器电路sa对应的锁存电路dl全部在使用中,只要锁存电路xdl空闲,半导体存储装置1也能够从外部受理数据。

[0072]

像这样,属于周边电路的感测放大器电路sa及锁存电路dl、xdl具备多个晶体管tr。

[0073]

接下来,对所述构成的感测放大器电路sa的动作简单地进行说明。

[0074]

作为将数据写入到存储单元mc的情况的例子,将电荷注入到存储单元mc而使阈值上升时,在锁存电路dl的节点inv中存储“h”电平(“1”数据)。由此,使晶体管tr

34

接通,将位线bl设为0v。

[0075]

作为将数据写入到存储单元mc的情况的另一例,不将电荷注入到存储单元mc而未使阈值变化时,在锁存电路dl的节点inv中存储“l”电平(“0”数据)。由此,使晶体管tr

31

接通,对位线bl赋予指定的正电压。

[0076]

在读出时,将节点inv设为“l”电平,使晶体管tr

31

接通。另外,经由晶体管tr

41

、

tr

42

,通过晶体管tr

31

将位线bl预充电。另外,使晶体管tr

35

也接通,将节点sen充电到指定电位。

[0077]

然后,使晶体管tr

35

断开,将信号xxl设为“h”电平,使晶体管tr

36

接通。由此,如果对应的存储单元mc接通,那么节点sen的电位降低,晶体管tr

37

断开。另一方面,如果对应的存储单元mc断开,那么节点sen的电位维持“h”电平,晶体管tr

37

接通。

[0078]

另外,通过信号stb使晶体管tr

38

接通,将与晶体管tr

37

的接通/断开对应的电位读出到总线lbus,并保存在锁存电路dl中。

[0079]

此外,图2所示的感测放大器电路sa及锁存电路dl、xdl的电路构成、彼此的连接方式及彼此的数据传输方式等皆是一例,感测放大器电路sa及锁存电路dl、xdl除了所述形态以外,也可以采用其他各种构成、连接方式或数据传输方式等。在该情况下,感测放大器电路sa及锁存电路dl、xdl中分别包含的晶体管tr的个数及种类也可以有各种变化。例如,感测放大器电路sa及锁存电路dl、xdl也可以包含高耐压p通道mos晶体管或高耐压n通道mos晶体管等而构成。

[0080]

图3是表示实施方式1的半导体存储装置1所具备的感测放大器模块30及数据寄存器40的布局的一例的示意图。图3中,作为一例所采用的形态是,感测放大器电路sa及锁存电路dl、xdl具有所述图2的连接方式及数据传输方式。

[0081]

此处,将沿着与多个存储单元mc分别连接的多个位线bl的方向定义为y方向并将其作为第2方向。另外,将与x方向交叉的方向、即沿着与多个存储单元mc分别连接的多个字线wl的方向定义为x方向并将其作为第1方向。

[0082]

如图3所示,在半导体存储装置1的物理构成中,数据寄存器40的多个锁存电路dl经由所述总线lbus与感测放大器模块30的1个感测放大器电路sa组合,而形成了多个小组sa/dl(sa/dl<0>~sa/dl<15>)。

[0083]

这些小组sa/dl以指定数量的位线bl为单位集聚在一起。在图3的例子中,16个小组sa/dl<0>~sa/dl<15>在沿着16个位线bl的y方向上汇集并排列成一列。

[0084]

另外,数据寄存器40的锁存电路xdl(xdl<0>~xdl<15>)也以16个为1组而设置,对应于排列成一列的感测放大器电路sa与锁存电路dl的小组sa/dl<0>~sa/dl<15>地,在沿着16个位线bl的y方向上排列成一列。

[0085]

感测放大器电路sa及锁存电路dl的小组sa/dl与对应的锁存电路xdl通过总线lbus以能够相互收发数据的方式连接。在图3的例子中,排列成一列的16个小组sa/dl<0>~sa/dl<15>共有1根总线lbus。

[0086]

(晶体管的构成)

[0087]

接下来,利用图4a~图5d,对感测放大器电路sa及锁存电路dl、xdl中包含的晶体管tr的物理构成例进行说明。

[0088]

图4a及图4b是表示实施方式1的半导体存储装置1所具备的晶体管tr的布局的一例的示意图。图4a是多个晶体管tr的简化俯视图,图4b是多个晶体管tr的沿着y方向的简化剖视图。

[0089]

如图4a所示,排列成一列的感测放大器电路sa及锁存电路dl、xdl中包含的晶体管tr在16个位线bl的间距内排列成例如一列。各晶体管tr具备元件区域aa、及配置在元件区域aa的上方的栅极电极gc。

[0090]

元件区域aa在与栅极电极gc在上下方向上重叠的位置具有通道,在通道的y方向两侧具有源极/漏极区域。但是,排成一列的晶体管tr与在沿着位线bl的y方向上邻接的晶体管tr共有源极/漏极区域。

[0091]

图4a中示出了4个晶体管tr在y方向上排列成一列且彼此共有源极/漏极区域的例子。但是,彼此共有源极/漏极区域的晶体管tr的数量是任意的,并不限于4个。

[0092]

另外,于在x方向上邻接的晶体管tr的元件区域aa间设置有元件分离部sti。

[0093]

此外,为了加长晶体管tr的栅极宽度w,抑制由窄通道效应(nce:narrow channel effect)或反窄通道效应引起的阈值变动,优选尽可能增大y方向上的元件区域aa的宽度且尽可能缩小元件分离部sti的宽度。

[0094]

在窄通道效应下,晶体管的栅极宽度变窄会导致阈值上升。因此,接通电流以比栅极宽度缩小所产生的影响更大的程度变小。另一方面,在反窄通道效应下,晶体管的栅极宽度变窄会导致即使以指定电压关闭晶体管的通道,流经通道下部的漏电流也增加。因晶体管的栅极长度(图4a中的“l”)变窄所引起的短通道效应也会导致这种阈值变动。另外,一般来说,接近晶体管间的阈值偏差取决于1/√lw(l表示栅极长度,w表示栅极宽度)。感测放大器及数据锁存器由于对各个位线皆要设置,所以数量非常多,因此,从读出动作的稳定性观点来看,希望该阈值偏差较小。在晶体管tr的栅极电极gc连接有与未图示的上层配线等连接的栅极接点cg。在元件区域aa连接有与未图示的上层配线等连接的源极/漏极接点cs。在y方向上排成一列的晶体管tr共有源极/漏极区域,同样地与在y方向上邻接的晶体管tr共有源极/漏极接点cs。

[0095]

此外,多个晶体管tr中存在栅极电极gc被输入相同控制信号的晶体管tr。在这种情况下,这些晶体管tr的栅极电极gc例如通过未图示的上层配线等而电连接。像这样,感测放大器电路sa及锁存电路dl、xdl的多个晶体管tr中分别包含的栅极电极gc即使彼此被输入共通的控制信号,在构成栅极电极gc的层(下述栅极电极层gcr)的电平下也各个物理分离。

[0096]

在图4b中示出了如下情况,即,多个晶体管tr在y方向上共有源极/漏极区域及源极/漏极接点cs,另外,多个晶体管tr的栅极电极gc各自分离。如图4b所示,在y方向上排列成一列的晶体管tr除了y方向端部的晶体管tr以外,在多个晶体管tr间共有源极/漏极区域及源极/漏极接点cs。另外,在y方向端部的晶体管tr的y方向一侧配置有元件分离部sti。

[0097]

图5a~图5d是表示应用于实施方式1的半导体存储装置1的晶体管tr的构成的一例的图。图5a是表示晶体管tr的栅极电极gc与元件区域aa的示意性俯视图。图5b是y方向、也就是图5a的a-a'线上的晶体管tr的剖视图。图5c是x方向、也就是图5a的b-b'线上的晶体管tr的剖视图。图5d是多个晶体管tr的沿着y方向的方向的剖视图。图5a~图5d中,省略了栅极接点cg及源极/漏极接点cs。

[0098]

此外,图5a~图5c中,作为可以应用于半导体存储装置1的晶体管tr的例子,示出了单独构成的1个晶体管tr。但是,在像所述那样将多个晶体管tr以彼此共有源极/漏极区域的方式排列成一列的情况下,如图5d所示,在沿着y方向的截面中,在除排列的两端部以外的晶体管tr两侧未配置元件分离部sti。另外,相对于排列的两端部的晶体管tr,元件分离部sti仅配置在一侧。

[0099]

如图5a~图5c所示,实施方式1的晶体管tr具备衬底wf、元件区域aa、栅极电极gc、

侧壁swg、swa、swga及衬层lr。

[0100]

衬底wf例如是硅衬底等半导体衬底。在衬底wf中形成有从衬底wf的表面到达指定深度的阱aar。阱aar是例如含有砷、磷、硼等杂质的层。根据晶体管tr是n通道型或p通道型的哪一个,而适当选择含有的杂质。

[0101]

元件区域aa在x方向上具有指定宽度,且构成为沿y方向延伸的凸状。也就是说,元件区域aa具有形成有阱aar的衬底wf的表面被加工成凸状的构成。

[0102]

在元件区域aa的x方向两侧及y方向两侧,分别在从衬底wf的表面凹陷的凹部rcw内配置有一对元件分离部sti。也就是说,在单独构成的1个晶体管tr的周围,以包围晶体管tr的方式配置元件分离部sti。

[0103]

元件分离部sti包括填充在凹部rcw内的氧化硅层等层间绝缘层ild。由此,元件分离部sti将各晶体管tr在x方向及y方向上电分离。

[0104]

在元件区域aa上,在俯视下与栅极电极gc重叠的位置,配置有栅极绝缘层gox。栅极绝缘层gox例如是氧化硅层或者包含氧化铪或氧化锆等的高介电常数(high-k)层等。

[0105]

栅极电极gc介隔栅极绝缘层gox配置在元件区域aa的上方。更具体来说,在栅极绝缘层gox上配置多晶硅栅极电极(poly gate electrode)gcp,在多晶硅栅极电极gcp上配置金属栅极电极gcm。多晶硅栅极电极gcp是掺杂有p型或n型杂质的导电性多晶硅层。金属栅极电极gcm是包含钨、硅化钨或硅化镍等的金属层。

[0106]

像这样,栅极电极gc构成为例如将多晶硅栅极电极gcp与金属栅极电极gcm组合而成的多金属栅极电极。

[0107]

在栅极电极gc上配置有顶盖层cp。顶盖层cp例如是氮化硅层或氧化硅层等。

[0108]

此外,如图5b所示,在y方向上,栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp具有实质上相等的宽度,它们的y方向的中心位置实质上一致。也就是说,栅极绝缘层gox及顶盖层cp具有与栅极电极gc的栅极长度l实质上相等的宽度。

[0109]

另外,在y方向上,栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的两侧面分别实质上位于同一平面上。也就是说,栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的y方向的端部位置从它们的积层方向来看,实质上重叠。

[0110]

此处,它们的宽度实质上相等,且y方向的中心位置及端部位置实质上一致,是指在栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的加工误差的范围内,它们的宽度相等,且y方向的中心位置及端部位置一致。

[0111]

另外,如图5c所示,在x方向上,元件区域aa的突出的上表面、栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp具有实质上相等的宽度,它们的x方向的中心位置实质上一致。也就是说,元件区域aa的上表面、栅极绝缘层gox及顶盖层cp具有与栅极电极gc的栅极宽度w实质上相等的宽度。

[0112]

另外,在x方向上,元件区域aa、栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的两侧面分别实质上位于同一平面上。也就是说,元件区域aa、栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的x方向的端部位置从它们的积层方向来看,实质上重叠。

[0113]

此处,它们的宽度实质上相等,且x方向的中心位置及端部位置实质上一致,是指

在元件区域aa的上表面、栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的加工误差的范围内,它们的宽度相等,且x方向的中心位置及端部位置一致。

[0114]

作为第1侧壁的侧壁swg覆盖栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的在y方向上对向的侧面。作为第2侧壁的侧壁swa覆盖元件区域aa的在y方向上对向的侧面。

[0115]

另一方面,在x方向上,覆盖栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的侧面的侧壁swg与覆盖元件区域aa的侧面的侧壁swa一体化所得的作为第1及第2侧壁的侧壁swga,覆盖元件区域aa、栅极绝缘层gox、多晶硅栅极电极gcp、金属栅极电极gcm及顶盖层cp的各侧面。

[0116]

这些侧壁swg、swa、swga例如是氧化硅层等。

[0117]

衬层lr例如具有氧化硅层ol与氮化硅层nl依序积层所得的多层结构,覆盖顶盖层cp、栅极电极gc、栅极绝缘层gox以及从衬底wf突出的元件区域aa。

[0118]

更具体来说,衬层lr从顶盖层sp的上表面到达顶盖层sp、栅极电极gc及栅极绝缘层gox的侧面。另外,衬层lr介隔侧壁swg或侧壁swga覆盖顶盖层sp、栅极电极gc及栅极绝缘层gox的侧面。

[0119]

另外,衬层lr从栅极电极gc连续地延伸到元件分离部sti。在元件分离部sti处,衬层lr潜伏在元件分离部sti的下方。也就是说,衬层lr潜伏在衬底wf的凹部rcw内所填充的层间绝缘层ild的下方,从栅极电极gc的侧面连续地覆盖凹部rcw的底面。

[0120]

包括栅极电极gc在内,晶体管tr被层间绝缘层ild覆盖。如上所述,层间绝缘层ild也填充在元件区域aa的x方向两侧及y方向两侧的凹部rcw内,构成元件分离部sti。也就是说,覆盖晶体管tr的层间绝缘层ild与将各晶体管tr电分离的元件分离层sti构成为一体。衬层lr介于由层间绝缘层ild构成的元件分离层sti与衬底wf的凹部rcw之间。层间绝缘层ild例如是未掺杂的氧化硅(nsg:non-doped silicate glass,非掺杂硅酸盐玻璃)层等。

[0121]

如上所述,实施方式1的晶体管tr构成为例如n通道或p通道的mos晶体管,所述感测放大器模块30包含例如互补型mos(cmos:complementary mos)晶体管等而构成。

[0122]

(晶体管的制造方法)

[0123]

接下来,利用图6a~图11cb,对实施方式1的晶体管tr的制造方法进行说明。晶体管tr是使用通过形成有图案的模板将图案转印到抗蚀层等的压印技术来制造。首先,以下,对用于制造晶体管tr的模板进行说明。

[0124]

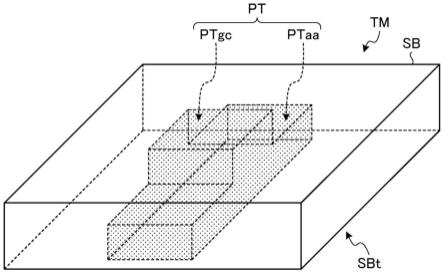

图6a及图6b是表示用于制造实施方式1的晶体管tr的模板tm的构成的一例的图。图6a是模板tm的斜透视图,图6b是从模板tm的转印面sbt侧观察所得的俯视图。

[0125]

如图6a及图6b所示,模板tm具有透明衬底sb及图案pt。透明衬底sb例如是使紫外线等透过的石英衬底等,具备设置有图案pt的转印面sbt。通过将图案pt转印到所述衬底wf而形成晶体管tr的形状。因此,图案pt具有转印到衬底wf而成为元件区域aa的元件区域图案ptaa、及成为栅极电极gc的栅极电极图案ptgc。

[0126]

元件区域图案ptaa是在透明衬底sb的转印面sbt具有开口,且从转印面sbt到达透明衬底sb的指定深度的槽状图案。也就是说,元件区域图案ptaa具有使凸状的元件区域aa的形状反转所得的凹状形状。因此,在图6b中,元件区域图案ptaa朝向纸面里侧凹陷。

[0127]

栅极电极图案ptgc配置在与元件区域图案ptaa重叠的位置,从元件区域图案ptaa

的到达深度进一步到达指定深度。也就是说,栅极电极图案ptgc具有使从元件区域aa突出的栅极电极gc的形状反转所得的凹状形状。因此,在图6b中,栅极电极图案ptgc从朝向纸面里侧凹陷的元件区域图案ptaa进一步朝向纸面里侧凹陷。

[0128]

在沿指定方向延伸的元件区域图案ptaa的短边方向上,元件区域图案ptaa的宽度与栅极电极图案ptgc的宽度实质上相等。此处,它们的宽度实质上相等是指在元件区域图案ptaa及栅极电极图案ptgc的加工误差的范围内,它们的宽度相等。

[0129]

此外,在图6a及图6b的例子中,仅示出了1个栅极电极图案ptgc及1个元件区域图案ptaa。但是,在压印处理中,将晶圆状态的衬底wf划分为称为压射区域(shot region)的指定区域,将模板tm压抵于每一个压射区域而转印图案pt。因此,1个模板tm具有数量与形成在压射区域内的元件区域aa的数量及栅极电极gc的数量相同的图案pt。

[0130]

图7a~图7d是表示实施方式1的模板tm的制造方法的顺序的一例的图。图7表示使转印面sbt朝向上方的衬底sb的斜透视图。

[0131]

如图7a所示,在衬底sb的转印面sbt形成钴层等掩模层ms。另外,通过例如使用电子束等的绘图,在掩模层ms中的栅极电极图案ptgc的形成位置形成开口opgc。

[0132]

如图7b所示,对从掩模层ms露出的衬底sb的转印面sbt进行加工,形成在转印面sbt具有开口的栅极电极图案ptgc。

[0133]

如图7c所示,通过例如使用电子束等的绘图,在掩模层ms中的元件区域图案ptaa的形成位置形成开口opaa。

[0134]

如图7d所示,对从掩模层ms露出的部分的衬底sb进行加工,形成在转印面sbt具有开口的元件区域图案ptaa。此时,在转印面sbt具有开口的栅极电极图案ptgc被下挖得更深,成为从元件区域图案ptaa的底面进一步凹陷的栅极电极图案ptgc。

[0135]

通过以上步骤,制造实施方式1的模板tm。

[0136]

接下来,对使用所述模板tm的晶体管tr的制造方法进行说明。此外,晶体管tr的制造是作为实施方式1的半导体存储装置1的制造步骤的一环而实施。

[0137]

图8aa~图11cb是表示实施方式1的晶体管tr的制造方法的顺序的一例的图。在图8aa~图11cb中,对图号标注有小写字母“a”的图是沿着衬底wf的y方向的剖视图,对图号标注有小写字母“b”的图是沿着衬底wf的x方向的剖视图。

[0138]

如图8aa及图8ab所示,在衬底wf中形成从衬底wf的表面到达指定深度的阱aar。阱aar是通过对硅衬底等作为半导体衬底的衬底wf将例如砷、磷、硼等杂质注入到指定深度而形成。

[0139]

另外,在阱aar的上方,介隔栅极绝缘层goxr依序形成栅极电极层gcr与抗蚀层rs。更具体来说,形成覆盖阱aar的整面的栅极绝缘层goxr。另外,形成覆盖栅极绝缘层goxr的整面的多晶硅栅极电极层gcpr,在多晶硅栅极电极层gcpr中适当掺杂p型或n型杂质。另外,形成覆盖多晶硅栅极电极层gcpr的整面的金属栅极电极层gcmr,形成覆盖金属栅极电极层gcmr的整面的顶盖层cpr。另外,形成覆盖顶盖层cpr的整面的抗蚀层rs。

[0140]

作为掩模层的抗蚀层rs例如是通过照射紫外线等而硬化的光硬化型抗蚀层等。

[0141]

此外,栅极绝缘层goxr、多晶硅栅极电极层gcpr、金属栅极电极层gcmr及顶盖层cpr例如可以使用化学气相沉积(cvd:chemical vapor deposition)法等而形成。

[0142]

另外,抗蚀层rs例如可以使用旋转涂布法等而形成。但是,不限于图8aa及图8ab的

例子,例如也可以使用喷墨法等,将抗蚀剂材料呈液滴状滴加到每一个压射区域中。

[0143]

如图8ba~图8cb所示,通过将所述模板tm的图案pt压抵于抗蚀层rs,而将元件区域图案rspa与栅极电极图案rspg转印到抗蚀层rs。

[0144]

更具体来说,如图8ba及图8bb所示,以模板tm的元件区域图案ptaa的延伸方向与衬底wf的y方向一致的方式,使模板tm的转印面sbt与衬底wf上的抗蚀层rs对向,在该状态下,将模板tm压抵于抗蚀层rs。此时,在衬底wf的最上层的顶盖层cpr与模板tm之间维持间隙,使衬底wf及衬底wf上的各种构成与模板tm不接触。

[0145]

如图8ca及图8cb所示,在将模板tm压抵于抗蚀层rsr的状态下,经由模板tm对抗蚀层rs照射紫外线等,使抗蚀层rs硬化。另外,抗蚀层rs硬化后,将模板tm脱模。

[0146]

由此,形成转印有元件区域图案rspa与栅极电极图案rspg的抗蚀图案rsp。作为掩模图案的抗蚀图案rsp具有元件区域图案rspa及栅极电极图案rspg。

[0147]

元件区域图案rspa是转印有模板tm的元件区域图案ptaa的图案。因此,元件区域图案rspa在x方向上具有指定宽度,且具有沿y方向延伸的凸状形状。另外,栅极电极图案rspg是转印有模板tm的栅极电极图案ptgc的图案。因此,栅极电极图案rspg具有配置在元件区域图案rspa的上表面的凸状形状。

[0148]

另外,抗蚀图案rsp具有使顶盖层cpr与模板tm之间的间隙的抗蚀层rs硬化而成的抗蚀剂残留层rlt。

[0149]

如图9aa及图9ab所示,通过氧等离子体等对抗蚀图案rsp进行处理,将抗蚀剂残留层rlt去除。由此,元件区域aa的形成位置以外的顶盖层cpr露出。

[0150]

如图9ba及图9bb所示,使用抗蚀图案rsp,将元件区域图案rspa转印到栅极电极层gcr与阱aar,形成在x方向上具有指定宽度且沿y方向延伸的凸状的元件区域aa。

[0151]

更具体来说,对从抗蚀图案rsp露出的部分的顶盖层cpr、金属栅极电极层gcgr、多晶硅栅极电极层gcpr、栅极绝缘层goxr及阱aar依次进行加工。它们的加工可以使用例如反应性离子刻蚀(rie:reactive ion etching)法等来进行。此时,以将阱aar加工到所需深度的方式控制加工时间等。

[0152]

由此,形成加工有阱aar的元件区域aa。但是,在该时间点,尚未形成元件区域aa的源极/漏极区域。另外,通过将元件区域aa的周围下挖,而在衬底wf形成凹部rcw。另外,形成栅极电极层gcaa及栅极绝缘层goxa,所述栅极电极层gcaa包含在各层的积层方向上与元件区域aa实质上重叠的形状的顶盖层cpa、金属栅极电极层gcga及多晶硅栅极电极层gcpa。

[0153]

此处,这些构成为与元件区域aa实质上重叠的形状,是指顶盖层cpa、金属栅极电极层gcga、多晶硅栅极电极层gcpa及栅极绝缘层goxa在加工误差的范围内成为与元件区域aa重叠的形状。

[0154]

如图9ca及图9cb所示,通过氧等离子体等对抗蚀图案rsp进行处理,将残留的元件区域图案rspa去除。由此,栅极电极gc的形成位置以外的顶盖层cpa露出。

[0155]

如图10aa及图10ab所示,使用抗蚀图案rsp,将栅极电极图案rspg转印到栅极电极层gcaa,形成介隔栅极绝缘层gox配置在元件区域aa的上方的栅极电极gc。

[0156]

更具体来说,对从抗蚀图案rsp露出的部分的顶盖层cpa、金属栅极电极层gcga、多晶硅栅极电极层gcpa及栅极绝缘层goxa依次进行加工。它们的加工与所述同样地,可以使用例如rie法等来进行。此时,一边相对于阱aar维持选择比,一边进行加工,由此,能够抑制

元件区域aa的上表面及凹部rcw的底面被加工。

[0157]

由此,在元件区域aa的上方形成顶盖层cp、栅极电极gc及栅极绝缘层gox,它们的x方向的宽度与元件区域aa的宽度实质上相等,且x方向的中心位置与元件区域aa的中心位置实质上一致。

[0158]

此处,这些构成的宽度与元件区域aa的宽度实质上相等,且它们的中心位置与元件区域aa的中心位置实质上一致,是指顶盖层cp、栅极电极gc及栅极绝缘层gox在加工误差的范围内具有与元件区域aa的宽度相等的宽度,且在加工误差的范围内具有与元件区域aa的中心位置一致的中心位置。

[0159]

此外,有时会因加工误差而导致在顶盖层cp、栅极电极gc及栅极绝缘层gox的至少一部分发生侧蚀,从而x方向及y方向的至少任一尺寸变小。另外,有时会因加工误差而导致俯视下呈例如矩形状的顶盖层cp、栅极电极gc及栅极绝缘层gox的至少一部分的顶角部分成为带弧度的倒圆角形状。

[0160]

如图10ba及图10bb所示,通过氧等离子体等将残留的抗蚀图案rsp灰化去除。

[0161]

另外,在元件区域aa中形成使例如砷、磷、硼等杂质低浓度地扩散所得的扩散层。所述任一种杂质的扩散受顶盖层cp、栅极电极gc及栅极绝缘层gox阻碍,而不向栅极绝缘层gox正下方扩散。

[0162]

如图10ca及图10cb所示,在包含栅极电极gc等的衬底wf的整面形成例如氧化硅层等侧壁层swr。由此,侧壁层swr连续地覆盖顶盖层cp的上表面及侧面、栅极电极gc的侧面、栅极绝缘层gox的侧面、元件区域aa的上表面及侧面、以及凹部rcw的底面。

[0163]

如图11aa及图11ab所示,使用例如rie法等对侧壁层swr进行全面回蚀。此时,通过以能够获得各向异性的条件进行处理,从顶盖层cp的上表面、元件区域aa的上表面及凹部rcw的底面去除侧壁层swr。另一方面,使侧壁层swr残留在顶盖层cp、栅极电极gc、栅极绝缘层gox及元件区域aa的侧面。

[0164]

由此,在顶盖层cp、栅极电极gc及栅极绝缘层gox的在y方向上对向的侧面形成侧壁swg。另外,在元件区域aa的在y方向上对向的侧面形成侧壁swa。另外,在顶盖层cp、栅极电极gc、栅极绝缘层gox及元件区域aa的在x方向上对向的侧面形成侧壁swga。

[0165]

形成侧壁swg、swa、swga后,在元件区域aa形成使例如砷、磷、硼等杂质高浓度地扩散所得的扩散层。所述任一种杂质的扩散受包含侧壁swg、swa、swga的顶盖层cp、栅极电极gc及栅极绝缘层gox阻碍,而不向栅极绝缘层gox正下方扩散。

[0166]

由此,在顶盖层cp、栅极电极gc及栅极绝缘层gox两侧的元件区域aa形成杂质高浓度地扩散所得的源极/漏极区域。另外,栅极绝缘层gox正下方的元件区域aa作为通道发挥功能。此外,所述杂质的种类由形成n通道型或p通道型的哪一种晶体管tr所决定。

[0167]

如图11ba及图11bb所示,形成覆盖栅极电极gc及元件区域aa的衬层lr。此时,元件区域aa的x方向两侧及y方向两侧的凹部rcw也从元件区域aa的上表面连续地由衬层lr覆盖。

[0168]

更具体来说,在包含栅极电极gc等的衬底wf的整面依序积层例如氧化硅层ol与氮化硅层nl。由此,氧化硅层ol与氮化硅层nl连续地覆盖顶盖层cp的上表面及侧面、栅极电极gc的侧面、栅极绝缘层gox的侧面、元件区域aa的上表面及侧面、以及凹部rcw的底面。

[0169]

此外,在顶盖层cp、栅极电极gc及栅极绝缘层gox的各侧面,侧壁swg或侧壁swga介

于所述各侧面与衬层lr之间。另外,在元件区域aa的侧面,侧壁swa或侧壁swga介于该侧面与衬层lr之间。

[0170]

如图11ca及图11cb所示,利用层间绝缘层ild覆盖栅极电极gc、元件区域aa及元件区域aa的x方向两侧及y方向两侧的凹部rcw。层间绝缘层ild可以通过将例如聚硅氮烷等原料气体供给至衬底wf而形成。此时,由覆盖凹部rcw的层间绝缘层ild形成元件分离部sti。

[0171]

通过以上步骤,制造实施方式1的晶体管tr。

[0172]

(实施方式1的效果)

[0173]

如上所述,例如读出存储单元的数据的感测放大器电路及锁存电路等的小型化有所发展。作为其中一环,例如将沿y方向排列的感测放大器电路数即层(tier)数从例如16层削减到12层或10层,实现了其电路面积的缩小化。为了削减层数,必须缩小这些电路的x方向的宽度,将其限制在指定数量的位线的间距内。

[0174]

此前,形成晶体管时,考虑到元件区域与栅极电极的对准偏移等,有时会构成为x方向上的栅极电极的宽度比元件区域的宽度大。在该情况下,为了保证栅极电极从元件区域突出的量及在x方向上邻接的栅极电极间的距离合适,并且缩小晶体管的x方向的宽度,有时必须使元件区域的x方向的宽度缩小。

[0175]

但是,如果采用所述方法,那么栅极电极的栅极宽度会变小,也会随之产生窄通道效应,从而无法达到所需电流值。另外,根据晶体管的结构,也有可能产生反窄通道效应。在该情况下,存在漏电流变大的风险,尤其连接于位线的感测放大器和与它连接的数据锁存器的数量较多,因此,存在漏电流增大影响变得非常大的风险。另外,受窄通道效应、反窄通道效应的影响,即使是较小的栅极宽度偏差,也很容易导致阈值改变,因此,存在由加工偏差影响所导致的阈值偏差变大的风险。此外,取决于1/√lw的接近晶体管间的阈值偏差也会变大,因此,存在妨碍动作稳定性的风险。因此,较为理想的是通过缩小元件分离部的x方向的宽度而不是缩小元件区域的宽度,来实现晶体管的小型化。

[0176]

根据实施方式1的晶体管tr的制造方法,通过将模板tm的图案pt压抵于抗蚀层rs,而将凸状的元件区域图案rspa及配置在元件区域图案rspa的上表面的凸状的栅极电极图案rspg转印到抗蚀层rs。

[0177]

通过使用像这样形成的抗蚀图案rsp,能够抑制栅极电极gc相对于元件区域aa的位置偏移。因此,能够消除栅极电极gc从元件区域aa突出的部分,并且缩小在x方向上邻接的栅极电极gc间的距离。因此,容易通过缩小元件分离部sti的x方向的宽度而不是缩小元件区域aa的宽度,来实现晶体管tr的小型化。也就是说,能够抑制窄通道或反窄通道效应,并且使晶体管tr小型化。

[0178]

另外,如上所述,通过使用压印技术来制造晶体管tr,能够同时进行元件区域aa与栅极电极gc的图案化。由此,能够减少例如光刻法等的步骤数而削减制造成本。

[0179]

在图12a及图12b中示出了比较例的半导体存储装置及实施方式1的半导体存储装置1的构成例。图12a及图12b是表示实施方式1及比较例的半导体存储装置所具备的晶体管的布局的一例的示意图。

[0180]

如图12a所示,比较例的半导体存储装置所具备的晶体管tr'具有x方向的两端从元件区域aa'突出的栅极电极gc'。由此,比较例的晶体管tr'难以充分减小元件分离部sti'的x方向的宽度。

[0181]

另外,从栅极电极gc'的图案化时的分辨率的观点来看,必须将在x方向上邻接的栅极电极gc'间保持在指定距离以上,这也妨碍了元件分离部sti'的宽度缩小。

[0182]

由此,在同样16个位线bl的间距内,比较例的晶体管tr'的元件区域aa'及栅极宽度w'比图12b所示的实施方式1的晶体管tr窄。

[0183]

此外,在比较例的晶体管tr'的制造步骤中,首先,将元件区域aa'图案化,然后,将栅极电极gc'图案化。因此,在通过元件区域aa'的图案化而形成的凹部内,与层间绝缘层分开地填充绝缘层,例如在栅极电极gc'的图案化之前形成元件分离部sti'。

[0184]

由此,在比较例的晶体管tr'中,使栅极电极gc'被输入相同控制信号的晶体管tr'彼此在x方向上邻接,使栅极电极gc'延伸到两个晶体管tr'间的元件分离部sti'上,在两个晶体管tr'中共有栅极电极gc'。由此,从共通的栅极接点cg'输入的控制信号被分配到两个晶体管tr'。

[0185]

根据这些情况,以下,列举实施方式1的晶体管tr与比较例的晶体管tr'的几种差异。

[0186]

根据实施方式1的晶体管tr,在x方向上,元件区域aa的上表面与栅极电极gc具有实质上相等的宽度,元件区域aa的上表面的中心位置与栅极电极gc的中心位置在x方向上实质上一致。根据比较例的晶体管tr',考虑到栅极电极gc'相对于元件区域aa'的位置偏移,而使栅极电极gc'从元件区域aa'突出,因此,不具有如上所述的构成。

[0187]

根据实施方式1的晶体管tr,衬层lr从栅极电极gc连续地延伸到元件分离部sti,在元件分离部sti潜伏在元件分离部sti的下方。根据比较例的晶体管tr',在成为元件分离部sti'的凹部内填充绝缘层之后,形成栅极电极gc'及衬层,因此,衬层配置在元件分离部sti'上,而不具有如上所述的构成。

[0188]

此外,根据实施方式1的晶体管tr,衬层lr例如包含氮化硅层nl。像这样,通过衬层lr至少一部分包含氮化物,而容易辨别衬层lr潜伏在元件分离部sti的下方。

[0189]

根据实施方式1的晶体管tr,层间绝缘层ild在凸状的元件区域aa的x方向的两侧位置构成元件分离部sti。根据比较例的晶体管tr',层间绝缘层与元件分离部sti'的绝缘层分开地形成,因此,不具有如上所述的构成。

[0190]

根据实施方式1的晶体管tr,具备覆盖元件区域aa的侧面的侧壁swa、swga。根据比较例的晶体管tr',在成为元件分离部sti'的凹部内填充绝缘层之后,形成栅极电极gc'及侧壁,因此,在元件区域aa'的侧面未形成侧壁,而不具有如上所述的构成。

[0191]

根据实施方式1的晶体管tr,多个晶体管tr中分别包含的栅极电极gc各个物理分离。根据比较例的晶体管tr',在栅极电极gc'的图案化之前形成元件分离部sti',因此,被输入共通的控制信号的栅极电极gc'在多个晶体管tr'间物理连接,而不具有如上所述的构成。

[0192]

(变化例1)

[0193]

接下来,利用图13a~图14cb,对应用于实施方式1的变化例1的半导体存储装置的晶体管tra进行说明。变化例1的晶体管tra与所述实施方式1的不同之处在于,具备缩小化的元件区域aaa。

[0194]

如果制造晶体管时使用压印技术,那么如上所述,能够使元件区域与栅极电极的x方向上的宽度实质上相等。但是,如上所述,有时会因加工误差而导致在栅极电极gc等发生

侧蚀或者栅极电极gc等的顶角部分成为倒圆角形状。

[0195]

在变化例1中,当因这些加工误差而导致栅极电极gca等的尺寸超出规定值而变小时,抑制栅极电极gca进入元件区域aaa的内侧。

[0196]

图13a~图13c是表示应用于实施方式1的变化例1的半导体存储装置的晶体管tra的构成的一例的图。图13a是表示晶体管tra的栅极电极gca与元件区域aaa的示意性俯视图。图13b是y方向、也就是图13a的a-a'线上的晶体管tra的剖视图。图13c是x方向、也就是图13a的b-b'线上的晶体管tra的剖视图。此外,在图13a~图13c中,省略了栅极接点及源极/漏极接点。另外,在图13a~图13c中,示出了栅极电极gca成为倒圆角形状rd的例子。

[0197]

如图13a所示,晶体管tra的栅极电极gca在俯视下构成为例如矩形状,栅极电极gca的4个顶角部分成为倒圆角形状rd。更具体来说,栅极电极gca所包含的多晶硅栅极电极gcp及金属栅极电极gcm的至少任一个具有倒圆角形状rd。

[0198]

另外,栅极电极gca具有在x方向上从元件区域aaa略微突出的形状。如下所述,这是由元件区域aaa的在x方向上对向的侧面被侧蚀所致。像这样,变化例1的晶体管tra在元件区域aaa的x方向的两侧具有减宽部se。因此,x方向上的元件区域aaa的上表面的宽度比栅极电极gca的宽度窄。但是,在该情况下,栅极电极gca相对于元件区域aaa的位置偏移也得到了抑制,因此,元件区域aaa的上表面的中心位置与栅极电极gca的中心位置在x方向上实质上一致。

[0199]

由于元件区域aaa具有比栅极电极gca略窄的宽度,所以,栅极电极gca的倒圆角部分离开元件区域aaa,从而可以抑制栅极电极gca进入元件区域aaa的内侧。

[0200]

在图13c中表示晶体管tra的减宽部se处的截面。如图13c所示,通过在x方向上减宽,而变化例1的元件区域aaa例如具有比所述实施方式1的元件区域aa的x方向的宽度窄的宽度。

[0201]

另外,虽然根据图13b难以辨别,但元件区域aaa的y方向的尺寸也比例如所述实施方式1的元件区域aa的y方向的尺寸小。

[0202]

图14aa~图14cb是表示实施方式1的变化例1的晶体管tra的制造方法的顺序的一例的图。在图14aa~图14cb中,对图号标注有小写字母“a”的图是沿着衬底wf的y方向的剖视图,对图号标注有小写字母“b”的图是沿着衬底wf的x方向的剖视图。

[0203]

在变化例1的晶体管tra的制造步骤中,直到形成元件区域aa为止采用与所述实施方式1的晶体管tr同样的制造方法。图14aa及图14ab表示所述实施方式1的图9ba及图9bb的处理已结束的状态。

[0204]

如图14ba及图14bb所示,变化例1的晶体管tra的制造步骤中包含如下步骤,即,对转印有元件区域图案rspa的阱aar侧面进行侧蚀,形成在x方向上具有比之后形成的栅极电极gca的宽度窄的宽度的元件区域aaa。

[0205]

更具体来说,形成元件区域aa之后,对元件区域aa的侧面进行侧蚀,形成x方向及y方向的宽度比元件区域aa窄的元件区域aaa。元件区域aa的侧面可以通过例如以能够获得各向同性的条件进行使用rie法的处理来侧蚀。

[0206]

此时,通过一边维持与除阱aar以外的各层的选择比一边对元件区域aa进行加工,可以抑制被加工成在各层的积层方向上与元件区域aa重叠的形状的顶盖层cpr、栅极电极层gcr及栅极绝缘层goxr的侧面被侧蚀。

[0207]

另外,去除元件区域图案rspa之前,一边利用元件区域图案rspa保护顶盖层cpa的上表面,一边进行元件区域aa的加工,因此,能够将栅极电极gca等的加工误差限制为最小限度。

[0208]

由此,晶体管tra在元件区域aaa的在x方向上对向的侧面侧及在y方向上对向的侧面侧分别具有减宽部se。另外,通过对元件区域aa的加工,凹部rcw的底面也略微被刻蚀,而凹部rcw略微变深。

[0209]

但是,也可以设想凹部rcw的底面被刻蚀,在形成凹部rcw时预先调整深度,由此成为例如与实施方式1的凹部rcw同样的深度。

[0210]

如图14ca及图14cb所示,形成元件区域aaa后,将残留的元件区域图案rspa与所述实施方式1同样地去除,并使用栅极电极图案rspg,对顶盖层cpa、金属栅极电极层gcga、多晶硅栅极电极层gcpa及栅极绝缘层goxa依次进行加工。

[0211]

由此,在元件区域aaa上形成顶盖层cp、栅极电极gca及栅极绝缘层gox,它们的x方向的宽度比元件区域aa的宽度宽,且x方向的中心位置与元件区域aaa的中心位置实质上一致。

[0212]

此外,多晶硅栅极电极gcp及金属栅极电极gcg的至少任一个的倒圆角可能在图14aa及图14ab中的元件区域aa的图案化处理中产生。或者,多晶硅栅极电极gcp及金属栅极电极gcg的至少任一个的倒圆角可能在图14ca及图14cb中的栅极电极gc的图案化处理中产生。或者,多晶硅栅极电极gcp及金属栅极电极gcg的至少任一个的倒圆角可能在元件区域aa的图案化处理及栅极电极gc的图案化处理这两个处理中产生。

[0213]

至少在图14ca及图14cb的处理结束的时间点,成为具有倒圆角形状rd的栅极电极gca。

[0214]

之后,进行与所述实施方式1的图10ba及图10bb以及这两个图之后的处理同样的处理。

[0215]

通过以上步骤,制造变化例1的晶体管tra。

[0216]

如上所述,例如有时栅极电极中会产生规定值以上的加工误差,导致栅极电极在x方向上不完全覆盖元件区域,而是进入元件区域的内侧。

[0217]

例如,当因栅极电极具有倒圆角形状而导致栅极电极的顶角部分进入元件区域的内侧时,认为从栅极电极到达成为通道的元件区域的端部的电场变弱。在该情况下,栅极电极的控制性降低,漏电流增大。另外,如果栅极电极成为倒圆角形状,那么该部分的栅极长度短于规定值。由此,也会引起漏电流增大。

[0218]

另外,例如,如果栅极电极中发生侧蚀等,导致栅极电极的x方向的宽度比元件区域窄,那么也可能会导致栅极电极的控制对元件区域的x方向端部完全无效。在该情况下,电流始终经由晶体管持续流通,从而不能作为晶体管发挥功能。

[0219]

根据变化例1的晶体管tra,在x方向上,元件区域aaa的上表面的宽度比栅极电极gca的宽度窄。由此,可以抑制栅极电极gca进入元件区域aaa的内侧。因此,能够使栅极电极gca的控制性提高,还能够确保栅极长度以抑制晶体管tra中的漏电流增大。

[0220]

根据变化例1的晶体管tra的制造方法,对转印有元件区域图案的阱aar侧面进行侧蚀,形成在x方向上具有比栅极电极gca的宽度窄的宽度的元件区域aaa。由此,能够以x方向的宽度实质上相等的栅极电极gca与元件区域aa为基础,容易地形成宽度比栅极电极gca

窄的元件区域aaa。

[0221]

(变化例2)

[0222]

接下来,利用图15a及图15b,对实施方式1的变化例2的半导体存储装置所具备的晶体管trb进行说明。关于变化例2的晶体管trb,沿y方向排列的晶体管trb的排列形态与所述实施方式1不同。

[0223]

关于所述实施方式1的半导体存储装置1所具备的周边电路中的锁存电路dl、xdl,仍有使晶体管tr的栅极宽度比感测放大器电路sa的晶体管tr的栅极宽度进一步缩小的余地。因此,将来也可以考虑例如在指定数量的位线bl的间距内,将感测放大器电路sa的晶体管像所述那样排列成一列,并且将锁存电路的晶体管排列成多列。在图15a及图15b中示出了锁存电路的晶体管排列成多列的例子。

[0224]

图15a及图15b是表示实施方式1的变化例2及比较例的半导体存储装置所具备的晶体管trb、trb'的布局的一例的示意图。图15a是比较例的晶体管trb'的布局,图15b是变化例2的晶体管trb的布局。图15a及图15b中,省略了连接于晶体管trb、trb'的栅极接点及源极/漏极接点。

[0225]

如图15a及图15b所示,变化例2及比较例的晶体管trb、trb'例如在16个位线bl的间距内排列成多列。如上所述,这些晶体管trb、trb'例如是属于锁存电路的晶体管。

[0226]

如图15a所示,比较例的晶体管trb'具备x方向上的两端从元件区域aab'突出的栅极电极gcb'。因此,为了确保所需的栅极宽度,并且在16个位线bl的间距内排列多列晶体管trb',而于在x方向上邻接的晶体管trb'中,使栅极电极gcb'的y方向的位置错开而排列。也就是说,在多列晶体管trb'中,将栅极电极gcb'的配置设为错位状。

[0227]

然而,如果使栅极电极gcb'排列成错位状,那么晶体管trb'排列整体在y方向上增大。

[0228]

如图15b所示,变化例2的晶体管trb具备x方向上的宽度与元件区域aab实质上相等的栅极电极gcb。因此,即使确保所需的栅极宽度,并且在16个位线bl的间距内排列多列晶体管trb,也能够于在x方向上邻接的晶体管trb中使栅极电极gcb的y方向的位置一致而排列。也就是说,能够在多列晶体管trb中将栅极电极gcb的配置设为网格状。

[0229]

像这样,通过使栅极电极gcb排列成网格状,能够在y方向上以更短的距离排列更多的晶体管trb,从而能够缩小晶体管trb排列的y方向的尺寸。

[0230]

[实施方式2]

[0231]

以下,参照附图对实施方式2详细地进行说明。像以下所说明的那样,所述实施方式1及变化例1的晶体管tr、tra的构成也可以应用于行解码器20的晶体管。

[0232]

(行解码器的构成)

[0233]

首先,利用图16,对实施方式2的半导体存储装置所具备的行解码器20的电路构成进行说明。图16是表示实施方式2的半导体存储装置所具备的行解码器20的构成的一例的电路图。

[0234]

如图16所示,实施方式2的半导体存储装置具备与实施方式1的半导体存储装置1同样地构成的存储单元阵列10。实施方式2的定序器160及电压产生电路180也与所述实施方式1同样地构成。

[0235]

实施方式2的行解码器20具备地址解码器21、块选择电路22及电压选择电路23。此

外,在电路构成上,行解码器20也可以设为与所述实施方式1的行解码器相比未改变的构成。

[0236]

地址解码器21具备多个块选择线blksel及多个电压选择线volsel。

[0237]

地址解码器21例如根据来自定序器160的控制信号,参照所述周边电路中包含的地址寄存器(参照图1)的地址数据。

[0238]

另外,地址解码器21对所参照的地址数据进行解码,使与地址数据对应的晶体管tr

22

及晶体管tr

23

接通,使除此以外的晶体管tr

22

及晶体管tr

23

断开。此外,晶体管tr

22

及晶体管tr

23

是下述的块选择电路22及电压选择电路23中分别包含的晶体管。

[0239]

另外,地址解码器21将与地址数据对应的块选择线blksel及电压选择线volsel的电压设为例如“h”状态,将除此以外的电压设为“l”状态。此外,对这些配线施加的电压根据对块选择电路22及电压选择电路23使用n通道型或p通道型的哪一种晶体管而相反。所述电压是晶体管为n通道型时的例子。

[0240]

在图16的例子中,在地址解码器21中,对存储单元阵列10内的1个块blk各设置有1个块选择线blksel。但是,该构成可以适当变更。例如,也可以对2个以上的块blk各设置1个块选择线blksel。

[0241]

块选择电路22具备与存储单元阵列10的块blk分别对应的多个块选择部220。所述多个块选择部220分别具备与字线wl及选择栅极线(sgd、sgs)对应的多个晶体管tr

22

。

[0242]

晶体管tr

22

是高耐压n通道mos晶体管,作为块驱动晶体管发挥功能。晶体管tr

22

的漏极电极分别电连接于对应的字线wl或选择栅极线(sgd、sgs)。晶体管tr

22

的源极电极分别经由配线wr及电压选择电路23而电连接于电压输出端子otm。晶体管tr

22

的栅极电极共通连接于对应的块选择线blksel。

[0243]

另外,块选择电路22还具备未图示的多个晶体管。所述多个晶体管是连接在选择栅极线(sgd、sgs)与接地电压供给端子之间的高耐压cmos晶体管。所述多个晶体管使存储单元阵列10内的非选择的块blk中包含的选择栅极线(sgd、sgs)与接地电压供给端子导通。此外,非选择的块blk中包含的多个字线wl成为浮动状态。

[0244]

电压选择电路23具备与字线wl及选择栅极线(sgd、sgs)对应的多个电压选择部230。所述多个电压选择部230分别具备多个晶体管tr

23

。

[0245]

晶体管tr

23

是高耐压n通道mos晶体管,作为电压选择晶体管发挥功能。晶体管tr

23

的漏极端子分别经由配线wr及块选择电路22而电连接于对应的字线wl或选择栅极线(sgd、sgs)。源极端子分别电连接于对应的电压输出端子otm。栅极电极分别连接于对应的电压选择线volsel。

[0246]

像这样,属于周边电路的行解码器20具备多个晶体管tr

22

、tr

23

等。但是,图16所示的行解码器20的电路构成是一例,行解码器20中包含的晶体管tr

22

、tr

23

等的个数及种类也可以有各种变化。

[0247]

(晶体管的构成)

[0248]

接下来,利用图17a及图17b,对实施方式2的行解码器20中包含的晶体管tr

22

的物理构成例进行说明。

[0249]

图17a及图17b是表示实施方式2及比较例的半导体存储装置所具备的晶体管trc、trc'的布局的一例的示意图。图17a是实施方式2的晶体管trc的布局,图17b是比较例的晶

体管trc'的布局。图中的晶体管trc是包含在行解码器20的块选择电路22中,作为例如块驱动晶体管发挥功能的所述晶体管tr

22

。

[0250]

如图17a所示,对实施方式2的晶体管trc应用所述实施方式1的晶体管tr的构成。也就是说,晶体管trc具备沿y方向延伸的元件区域aac、及配置在元件区域aac上的多个栅极电极gcc。所述多个栅极电极gcc具有与元件区域aac的x方向的宽度实质上相等的宽度。于在x方向上邻接的元件区域aac间,沿y方向延伸有元件分离部stic。

[0251]

在晶体管trc的栅极电极gcc连接有栅极接点cgc。栅极接点cgc分别连接于对应的块选择线blksel。

[0252]

在晶体管trc的元件区域aac连接有源极/漏极接点csc。排成一列的晶体管trc与在y方向上邻接的晶体管trc共有源极/漏极接点csc。晶体管trc的漏极电极侧的源极/漏极接点csc分别连接于对应的字线wl。晶体管trc的源极电极侧的源极/漏极接点csc经由配线wr而分别连接于对应的电压选择部230。

[0253]

如图17b所示,比较例的晶体管trc'具备x方向上的两端从元件区域aac'突出的栅极电极gcc'。因此,在晶体管trc'中,元件分离部stic'的x方向的宽度不充分时,施加到栅极电极gcc'的高电压有可能到达元件分离部stic'的底面。在该情况下,于在x方向上邻接的晶体管trc'产生场反转泄漏。

[0254]

对作为块驱动晶体管的栅极电极gcc'经由块选择线blksel施加例如30v的高电压。如果将这种高电压施加到栅极电极gcc',那么在元件分离部stic'的底面也会形成反转层。场反转泄漏是经由所述反转层流到在x方向上邻接的晶体管trc'的漏电流。

[0255]

根据实施方式2的晶体管trc,栅极电极gcc不具有突出部分。由此,施加到栅极电极gcc的高电压不易到达元件分离部stic的底面,从而能够抑制场反转泄漏。另外,能够抑制场反转泄漏,并且减小元件分离部stic的x方向的宽度,容易使块选择电路22的尺寸小型化。

[0256]

此外,行解码器20的块选择电路22中包含的晶体管tr

22

也可以具有所述实施方式1的变化例1的晶体管tra的构成。

[0257]

另外,所述实施方式1及变化例1的晶体管tr、tra的构成也可以应用于行解码器20的其它晶体管。也就是说,电压选择电路23中包含的晶体管tr

23

或包含在块选择电路22中且连接在选择栅极线(sgd、sgs)与接地电压供给端子之间的晶体管等同样也可以具备不具有所述突出部分的栅极电极。

[0258]

[实施方式3]

[0259]

以下,参照附图对实施方式3详细地进行说明。像以下所说明的那样,所述实施方式1及变化例1的晶体管tr、tra的构成也可以应用于例如dram(dynamic random access memory,动态随机存取存储器)等易失性存储器的周边电路的晶体管。

[0260]

(半导体存储装置的概略构成)

[0261]

首先,利用图18,对实施方式3的半导体存储装置2的构成例进行说明。图18是实施方式3的半导体存储装置2的框图。

[0262]

如图18所示,实施方式3的半导体存储装置2具备存储单元阵列201、输入输出电路210、行解码器222、读写放大器233、指令解码器241、列解码器250、指令地址输入电路260、时钟输入电路271、内部时钟产生电路272及电压产生电路280等周边电路、以及时钟端子

ck、ck/、指令/地址端子cat、数据端子dqt、数据掩模端子dmt及电源端子vpp、vdd、vss、vddq、vssq等多个外部端子。

[0263]

存储单元阵列201包含多个存储体bnk0~7。多个存储体bnk0~1分别具有多个字线wlv与多个位线blv、/blv,在字线wlv与位线blv的各个交点处配置有存储单元mcv。存储单元mcv构成为例如晶体管,保存易失性数据。因此,为了维持存储单元阵列201中所存储的数据,而定期进行更新。图18中,为了便于说明,省略了设置在dram中的更新电路等。

[0264]

通过具备这种存储单元mcv,半导体存储装置2构成为例如dram(dram:dynamic random access memory)。此外,半导体存储装置2也可以构成为sram(静态ram)等其它易失性存储器。

[0265]

感测放大器电路samp对应于位线blv、/blv而配置。另外,感测放大器电路samp经由列开关ysw而连接于局域输入输出线liot、liob,并且经由传输栅极tg而连接于主输入输出线miot、miob。传输栅极tg作为开关发挥功能。感测放大器电路samp与所述实施方式1的感测放大器电路sa(参照图2)同样地,感测已从存储单元mcv读出的数据。

[0266]

存储单元阵列201内的多个存储单元mcv分别与存储器地址建立对应。多个外部端子中,指令/地址端子cat例如从存储器控制器等外部装置接收存储器地址。指令/地址端子cat所接收到的存储器地址被传送到指令地址输入电路260。指令地址输入电路260接收存储器地址时,将解码后的行地址xadd发送到行解码器222,并将解码后的列地址yadd发送到列解码器250。

[0267]

另外,指令/地址端子cat例如从存储器控制器等接收指令。指令/地址端子cat所接收到的指令作为内部指令信号icmd经由指令地址输入电路260发送到指令解码器241。

[0268]

指令解码器241包含用来对内部指令icmd进行解码而产生用于执行内部指令的信号的电路。指令解码器241例如将已被启动的指令act及更新指令aref发送到行解码器222。行解码器222连接于字线wlv,根据从指令解码器241接收到的指令act及更新指令aref来选择字线wlv。

[0269]

另外,指令解码器241例如将读/写指令r/w发送到列解码器250。列解码器250连接于位线blv,根据从指令解码器241接收到的读/写指令r/w来选择位线blv。

[0270]

读出数据时,指令/地址端子cat接收读取指令与存储器地址。由此,从存储器地址所指定的存储单元阵列201内的存储单元mcv读出数据。读出数据经由读写放大器233及输入输出电路210从数据端子dqt输出到外部。

[0271]

写入数据时,指令/地址端子cat接收写入指令与存储器地址,数据端子dqt接收写入数据。另外,视需要对数据掩模端子dmt发送数据掩模。写入数据经由输入输出电路210及读写放大器233被发送到存储单元阵列201。由此,写入数据被写入到存储器地址所指定的存储单元mcv。

[0272]

读写放大器233具备暂时保存读出数据及写入数据的各种锁存电路。由读写放大器233与感测放大器电路samp形成相当于所述实施方式1的感测放大器模块30及数据寄存器40(参照图1)的构成。

[0273]

对电源端子vdd、vss供给电源电压,电源电压还被供给至电压产生电路280。电压产生电路280基于电源电压产生各种内部电压vpp、vod、vary、vperi。内部电压vpp主要在行解码器222中使用,内部电压vod、vary主要在存储单元阵列201的感测放大器电路samp中使

用,内部电压vperi在其它周边电路块中使用。

[0274]

另外,也对电源端子vddq、vssq供给电源电压,电源电压还被供给至输入输出电路210。对电源端子vddq、vssq赋予专用的电源电压,以免输入输出电路210中产生的电源噪声传播到其它电路块。此外,供给至电源端子vddq、vssq的电源电压可以是与供给至电源端子vdd、vss的电源电压相同的电压。

[0275]

对时钟端子ck、/ck输入互补的外部时钟信号。外部时钟信号被供给至时钟输入电路271。时钟输入电路271产生内部时钟信号iclk。内部时钟信号iclk被供给至内部时钟产生电路272及指令解码器241。

[0276]

内部时钟产生电路272通过来自指令地址输入电路260的时钟使能cke而启用时,产生各种内部时钟信号lclk。内部时钟信号lclk用于计量各种内部动作的时序。例如,内部时钟信号lclk被输出到输入输出电路210。输入输出电路210基于所输入的内部时钟信号lclk进行动作,由此,在数据端子dqt上发送及接收数据。

[0277]

(感测放大器电路的构成)

[0278]

接下来,利用图19,对实施方式3的半导体存储装置2所具备的感测放大器电路samp的构成例进行说明。图19是表示包含实施方式3的半导体存储装置2所具备的感测放大器电路samp的电路构成的一例的电路图。

[0279]

如图19所示,在存储单元阵列201内连接于存储单元mcv的位线blv及与位线blv成对的位线/blv与感测放大器电路samp连接。

[0280]

感测放大器电路samp包含晶体管tr

51

~tr

54

。晶体管tr

51

、tr

53

是低耐压p通道mos晶体管,晶体管tr

52

、tr

54

是低耐压n通道mos晶体管。

[0281]

晶体管tr

51

的一端连接于供给感测信号sap的信号线,另一端连接于晶体管tr

52

的一端。晶体管tr

52

的另一端连接于供给感测信号san的信号线。另外,在晶体管tr

51

、tr

52

间连接位线blv。

[0282]

晶体管tr

53

的一端连接于供给感测信号sap的信号线,另一端连接于晶体管tr

54

的一端。晶体管tr

54

的另一端连接于供给感测信号san的信号线。另外,在晶体管tr

53

、tr

54

间连接位线/blv。

[0283]

另外,晶体管tr

51

、tr

52

的栅极电极连接在晶体管tr

53

、tr

54

间,晶体管tr

53

、tr

54

的栅极电极连接在晶体管tr

51

、tr

52

间。

[0284]

在比感测放大器电路samp更靠下游侧的位线blv、/blv连接有列开关ysw。列开关ysw包含晶体管tr

71

、tr

72

。晶体管tr

71

、tr

72

是低耐压n通道mos晶体管。

[0285]

晶体管tr

71

的一端连接于位线blv,另一端连接于局域输入输出线liob。晶体管tr

72

的一端连接于位线/blv,另一端连接于局域输入输出线liot。晶体管tr

71

、tr

72

的栅极电极连接于供给列选择信号ys的信号线。

[0286]

比列开关ysw更靠下游侧的位线blv、/blv与均衡电路eq连接。

[0287]

均衡电路eq包含晶体管tr

81

~tr

83

。晶体管tr

81

~tr

83

是低耐压n通道mos晶体管。

[0288]

晶体管tr

81

的一端连接于位线blv,另一端连接于晶体管tr

82

。晶体管tr

82

的另一端连接于位线/blv。另外,在晶体管tr

81

、tr

82

间连接供给均衡电压vbleq的电源线。均衡电压vbleq的大小是感测放大器电路samp用的电源电压vddsa的1/2。

[0289]

晶体管tr

83

的一端连接于位线blv,另一端连接于位线/blv。

[0290]

晶体管tr

81

~tr

83

的栅极电极连接于供给均衡信号bleq的信号线。

[0291]

接下来,对包含所述感测放大器电路samp的电路动作简单地进行说明。

[0292]

通常,在稳定状态下,均衡信号bleq被驱动为高电平。由此,均衡电路eq的晶体管tr

81

~tr

83

接通,使位线blv、/blv均衡为预充电电位。

[0293]

接着,发出激活指令时,解除均衡,并且基于所输入的行地址xadd将对应的字线wl驱动为vpp电平。均衡的解除、即均衡电路eq的非活动状态从发出激活指令开始持续到发出预充电指令为止。

[0294]

由于字线wl被驱动为vpp电平,对应的存储单元mcv的单元晶体管接通,因此,所述存储单元mcv的单元电容器连接于位线blv或位线/blv。结果,根据存储单元mcv的单元电压vcel,位线blv或位线/blv的电位略微产生变化。在图19的例子中,示出了位线blv的电位略微上升的情况。

[0295]

然后,在指定时序,感测信号san、sap分别变化为低电平及高电平,使感测放大器电路samp启动。结果,位线blv、/blv的电位差放大。在图19的例子中,示出了位线/bl被驱动为低电平且位线bl被驱动为高电平的情况。

[0296]

接着,发出读取指令时,根据与读取指令同步地输入的列地址yadd,使对应的列选择信号ys变化为高电平。在列选择信号ys启动之前的时间点,局域输入输出线liot、liob被预充电为电源电压vcc。

[0297]

由于列选择信号ys启动时,列开关ysw的晶体管tr

71

、tr

72

接通,因此,位线bl、/bl连接于对应的局域输入输出线liob、liot。结果,局域输入输出线liob维持为预充电电平,局域输入输出线liot从预充电电平降低到低电平。

[0298]

通过以上步骤,从存储单元mcv读出数据。

[0299]

(晶体管的构成)

[0300]

接下来,利用图20a及图20b,对实施方式3的感测放大器电路samp所包含的晶体管trd的物理构成例进行说明。

[0301]

图20a是表示实施方式3的半导体存储装置所具备的晶体管trd的布局的一例的示意图,图20b是表示比较例的晶体管trd'的布局的一例的示意图。

[0302]

如图20a所示,在感测放大器电路samp中,多个晶体管trd分别具备的多个元件区域aad沿x方向及y方向配置成网格状。多个元件区域aad通过元件分离部stid而彼此电分隔。

[0303]

在各元件区域aad上,配置有沿x方向排列的多个栅极电极gcd。在图20a的例子中,在元件区域aad上配置2个栅极电极gcd。此外,元件区域aad在夹在2个栅极电极gcd之间的区域中沿y方向延伸,且与邻接的元件区域aad连接。

[0304]

对实施方式3的感测放大器电路samp的晶体管trd应用所述实施方式1的晶体管tr的构成。也就是说,在晶体管trd中,多个栅极电极gcd具有与元件区域aad的y方向的宽度实质上相等的宽度。也就是说,在实施方式3的晶体管trd中,多个栅极电极gcd也具有与元件区域aad的y方向的宽度实质上相等的栅极宽度。

[0305]

在晶体管trd的栅极电极gcd连接有栅极接点cgd。在晶体管trd的元件区域aad连接有源极/漏极接点csd。沿x方向排列的晶体管trd与邻接的晶体管trd共有源极/漏极接点csd。源极/漏极接点csd也配置于在y方向上彼此连接的元件区域aad的连接部分。

[0306]

多个源极/漏极接点csd中,配置在x方向一侧的晶体管trd的一端的源极/漏极接点csd分别连接于位线bl。配置在x方向另一侧的晶体管trd的另一端的源极/漏极接点csd分别连接于位线/bl。在图20a中示出了如下情况,即,在属于沿x方向排列的2个元件区域aad中的一个元件区域aad的晶体管trd连接这些位线bl、/bl。

[0307]

在x方向上邻接的晶体管trd彼此所共有的源极/漏极接点csd共通连接于供给感测信号sap的信号线或供给感测信号san的信号线。具体来说,当晶体管trd为p通道mos晶体管时,源极/漏极接点csd连接于供给感测信号sap的信号线。当晶体管trd为n通道mos晶体管时,源极/漏极接点csd连接于供给感测信号san的信号线。

[0308]

与感测信号sap/san的信号线连接时,源极/漏极接点csd被引出到上层,然后与沿x方向延伸的这些信号线中的任一个信号线连接。也就是说,这些信号线与所述位线bl、/bl配置在不同的层级。在图20a中示出了如下情况,即,在属于沿x方向排列的2个元件区域aad中的一个元件区域aad的晶体管trd连接感测信号sap/san的信号线。

[0309]

如图20b所示,比较例的晶体管trd'具备y方向上的两端从元件区域aad'突出的栅极电极gcd'。

[0310]

根据实施方式3的晶体管trd,栅极电极gcd不具有突出部分。由此,能够使晶体管trd的面积缩小。另外,通过晶体管trd缩小,而设计自由度增大,半导体存储装置3的小型化变得容易。

[0311]

此外,实施方式3的感测放大器电路samp也可以具备应用了实施方式1的变化例1的晶体管tra的构成的晶体管。另外,所述实施方式1及变化例1的晶体管tr的构成也可以应用于实施方式3的行解码器222中包含的晶体管。

[0312]

在所述实施方式1~3等中,晶体管tr、tra~trd配置在硅衬底等衬底wf上。但是,衬底wf也可以不是半导体衬底,晶体管tr、tra~trd也可以包含另外形成在衬底wf上的半导体层而构成。在该情况下,晶体管tr、tra~trd的元件区域aa、aaa~aad设置在半导体层。

[0313]

对本发明的若干实施方式进行了说明,但这些实施方式是作为示例而提出的,并不意图限定发明的范围。这些新颖的实施方式能以其它多种方式实施,可以在不脱离发明主旨的范围内进行各种省略、替换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其均等的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1