半导体存储装置的制作方法

半导体存储装置

1.相关申请

2.本技术享受以日本专利申请2021-093092号(申请日:2021年6月2日)为基础申请的优先权。本技术通过参照该基础申请而包括基础申请的所有内容。

技术领域

3.本发明的实施方式涉及半导体存储装置。

背景技术:

4.已知有一种具有壳体、收容于壳体的基板、安装于基板的发热部件以及安装于基板的半导体存储器部件的半导体存储装置。

技术实现要素:

5.本发明的一实施方式提供能够实现可靠性的提高的半导体存储装置。

6.实施方式的半导体存储装置具备壳体、基板、控制器以及半导体存储器部件。所述控制器构成为控制所述半导体存储器部件。所述基板收容于所述壳体,包括第一区域和与所述第一区域不同的第二区域。所述控制器安装于所述第一区域与所述第二区域中的一方。所述半导体存储器部件安装于所述第一区域与所述第二区域中的另一方。所述壳体具有:第一壁部,在作为所述基板的厚度方向的第一方向上相对于所述基板位于第一侧且面向所述第一区域;第二壁部,在所述第一方向上相对于所述基板位于所述第一侧且面向所述第二区域;第三壁部,在所述第一方向上相对于所述基板位于与所述第一侧相反的一侧即第二侧且面向所述第一区域;以及第四壁部,在所述第一方向上相对于所述基板位于所述第二侧且面向所述第二区域。所述第一壁部与所述第二壁部形成为能够相互分离。所述第三壁部与所述第四壁部形成为能够相互分离。

附图说明

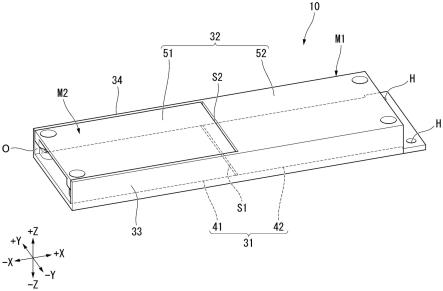

7.图1是表示第一实施方式的半导体存储装置的立体图。

8.图2是表示第一实施方式的基板单元的立体图。

9.图3是表示第一实施方式的基板单元的仰视图。

10.图4是表示第一实施方式的基板单元的俯视图。

11.图5是表示第一实施方式的壳体的立体图。

12.图6是表示第一实施方式的第一部件的立体图。

13.图7是表示第一实施方式的第二部件的立体图。

14.图8是用于说明第一实施方式的第二部件相对于第一部件的安装方法的图。

15.图9是沿着图1中所示的半导体存储装置的f9-f9线的剖面图。

16.图10是沿着图9中所示的半导体存储装置的f10-f10线的剖面图。

17.图11是表示第一实施方式的壳体的下壁的一部分的仰视图。

18.图12是分解表示第二实施方式的壳体的立体图。

19.图13是分解表示第三实施方式的壳体的立体图。

20.图14是分解表示第四实施方式的壳体的立体图。

21.附图标记说明

[0022]1…

半导体存储装置,10、10a、10b、10c

…

壳体,23

…

控制器(发热部件),24

…

电力转换部件(发热部件),25

…

电源电路部件(发热部件),27

…

半导体存储器部件,28

…

电容器(电子部件),31

…

下壁,32

…

上壁,33

…

第一侧壁,34

…

第二侧壁,41

…

第一下壁部,42

…

第二下壁部,51

…

第一上壁部,52

…

第二上壁部,61

…

第三连接部,62

…

第四连接部,m1

…

第一部件,m2

…

第二部件,m3a

…

第三部件,m4a

…

第四部件,m5b

…

第五部件,m6b

…

第六部件,m7c

…

第七部件,m8c

…

第八部件,m9c

…

第九部件,m10c

…

第十部件,r1

…

第一区域,r2

…

第二区域,s1

…

第一间隙,s2

…

第二间隙,s3

…

第三间隙,s4

…

第四间隙,s5

…

第五间隙,s6

…

第六间隙

具体实施方式

[0023]

以下,参照附图对实施方式的半导体存储装置进行说明。在以下的说明中,对具有相同或类似的功能的构成标注相同的附图标记。而且,有时省略这些构成的重复说明。在本技术中,所谓“平行”、“正交”、或者“相同”也可以分别包括“大致平行”、“大致正交”、或者“大致相同”的情况。在本技术中“连接”并不限定于机械连接,也可以包括电连接。另外,“连接”并不限于多个构成要素直接连接的情况,也可以包含使其他要素夹设于其间而连接的情况。

[0024]

这里,首先定义+x方向、-x方向、+y方向、-y方向、+z方向以及-z方向。+x方向、-x方向、+y方向及-y方向是与后述的基板21的第一面21a(参照图9)平行的方向。+x方向是从后述的壳体10的第一上壁部51朝向第二上壁部52的方向(参照图1)。-x方向是与+x方向相反的方向。在不区分+x方向与-x方向的情况下,仅称作“x方向”。+y方向以及-y方向是与x方向交叉(例如正交)的方向。+y方向是从后述的壳体10的第一侧壁33朝向第二侧壁34的方向(参照图1)。-y方向是与+y方向相反的方向。在不区分+y方向与-y方向的情况下,仅称作“y方向”。

[0025]

+z方向以及-z方向是与x方向以及y方向交叉(例如正交)的方向,是后述的基板21的厚度方向。+z方向是从后述的壳体10的第一下壁部41朝向第一上壁部51的方向(参照图9)。-z方向是与+z方向相反的方向。在不区分+z方向与-z方向的情况下,仅称作“z方向”。在本技术中,为了方便说明,有时将+z方向侧称作“上”、将-z方向侧称作“下”。但是,它们并不限定重力方向。+z方向是“第一方向”的一个例子。+x方向是“第二方向”的一个例子。+y方向是“第三方向”的一个例子。

[0026]

(第一实施方式)

[0027]

<1.半导体存储装置的整体构成>

[0028]

参照图1至图11,对第一实施方式的半导体存储装置1进行说明。半导体存储装置1例如是ssd(solid state drive,固态硬盘)那样的存储装置。半导体存储装置1例如安装于服务器、个人计算机等信息处理装置,被用作信息处理装置的存储区域。在本技术中,将安装半导体存储装置1的信息处理装置称作“主机装置”。

[0029]

图1是表示半导体存储装置1的立体图。半导体存储装置1例如具有壳体10、基板单元20以及多个固定部件80。这里为了方便说明,先对基板单元20说明,之后对壳体10以及固定部件80进行说明。

[0030]

<2.基板单元>

[0031]

首先,对基板单元20进行说明。如图1所示,基板单元20收容于壳体10。

[0032]

图2是表示基板单元20的立体图。基板单元20例如具有基板21、外部连接连接器22、控制器23、电力转换部件24、电源电路部件25、多个dram(dynamic random access memory,动态随机存取存储器)26、多个半导体存储器部件27以及多个电容器28。

[0033]

基板21是沿着x方向以及y方向的板状。基板21例如是细长的矩形状。基板21为印刷布线板,具有绝缘基材以及设于该绝缘基材的布线图案。在基板21的四个角部设有供固定部件80通过的多个插通孔21ha。另外,在基板21上例如设有供定位销41c(参照图6)插入的一个以上的插通孔21hb以及供止转销42c(参照图7)插入的一个以上的插通孔21hc。

[0034]

基板21具有第一端部21e1以及在x方向上位于与第一端部21e1相反的一侧的第二端部21e2。第一端部21e1是-x方向侧的端部。第一端部21e1通过壳体10的开口o向壳体10的外部突出(参照图1)。基板21具有第一面21a以及在z方向上位于与第一面21a相反的一侧的第二面21b。第一面21a是朝向-z方向的面。第二面21b是朝向+z方向的面。

[0035]

图3是表示基板单元20的仰视图。图4是表示基板单元20的俯视图。在本实施方式中,基板21具有第一区域r1以及第二区域r2。在本技术中,“基板的区域”并不限定于基板21的特定的表面上的区域,可包含基板21的多个表面(例如第一面21a以及第二面21b)各自的一部分。

[0036]

如图3以及图4所示,第一区域r1以及第二区域r2在+x方向上按第一区域r1、第二区域r2的顺序排列。即,第一区域r1在x方向上位于比第二区域r2靠近基板21的第一端部21e1的位置。第二区域r2在x方向上位于比第一区域r1靠近基板21的第二端部21e2的位置。

[0037]

外部连接连接器22设于基板21的第一端部21e1,通过开口o而在壳体10的外部露出。外部连接连接器22具有在y方向上排列的多个金属端子22a。外部连接连接器22能够与主机装置的连接器连接。

[0038]

控制器23安装于基板21的第一区域r1。控制器23例如安装于基板21的第一面21a。控制器23统一地控制半导体存储装置1的整体。控制器23例如是包括将相对于主机装置的主机接口电路、控制多个dram26的控制电路以及控制多个半导体存储器部件27的控制电路等集成在一个半导体芯片的soc(system on a chip,系统芯片)的半导体封装。控制器23是在动作时发热的部件,是“发热部件”的一个例子。例如,控制器23与半导体存储器部件27相比为高温。另外,在本技术中,“某个部件安装于某个区域”是指,该部件的一半以上安装于该区域的意思,可包含该部件的一部分从该区域突出的情况。

[0039]

电力转换部件24安装于基板21的第一区域r1。电力转换部件24例如安装于基板21的第一面21a。电力转换部件24例如是dc-dc转换器。电力转换部件24将从主机装置供给的电力转换为基板单元20所含的各部件(控制器23、dram26、半导体存储器部件27等)所需的电力,并将转换后的电力供给至各部件。电力转换部件24是在动作时发热的部件,是“发热部件”的一个例子。例如,电力转换部件24与半导体存储器部件27相比为高温。

[0040]

电源电路部件25安装于基板21的第一区域r1。电源电路部件25例如安装于基板21

的第二面21b。电源电路部件25例如具有pmic(power management ic,电源管理ic)、电源管理功能。电源电路部件25进行对基板单元20所含的各部件(控制器23、dram26、半导体存储器部件27等)的电力控制。电源电路部件25是在动作时发热的部件,是“发热部件”的一个例子。例如,电源电路部件25与半导体存储器部件27相比为高温。

[0041]

多个dram26安装于基板21的第一区域r1。多个dram26包括第一dram26a和第二dram26b。第一dram26a安装于基板21的第一面21a。第二dram26b安装于基板21的第二面21b。各dram26是包含易失性半导体存储器芯片的半导体封装。各dram26可以用作将从主机装置接收到的写入对象数据以及从一个以上的半导体存储器部件27读出的读出对象数据等暂时储存的数据缓冲器。但是,半导体存储装置1也可以不具有dram26。

[0042]

多个半导体存储器部件27安装于基板21的第二区域r2。多个半导体存储器部件27包括多个第一半导体存储器部件27a和多个第二半导体存储器部件27b。多个第一半导体存储器部件27a安装于基板21的第一面21a,在x方向以及y方向上排列。多个第二半导体存储器部件27b安装于基板21的第二面21b,在x方向以及y方向排列。各半导体存储器部件27是包含非易失性的半导体存储器芯片的半导体封装。各半导体存储器部件27例如是nand型闪存。

[0043]

但是,半导体存储器部件27并不限定于nand型闪存,也可以是nor型存储器、mram(magnetoresistive random access memory,磁阻式随机存取存储器)、电阻变化型存储器、或者其他类型的存储装置。即,“半导体存储器部件”并不限定于包含根据电荷的累积状态存储数据的存储器元件的部件,也可以是包含根据磁状态或者电阻状态等存储数据的存储器元件的部件。

[0044]

多个电容器28包括多个第一电容器28a和多个第二电容器28b。多个第一电容器28a安装于基板21的第一面21a。多个第一电容器28a例如配置于控制器23与多个第一半导体存储器部件27a之间。多个第二电容器28b安装于基板21的第二面21b。多个第二电容器28b例如配置于第二dram26b与多个第二半导体存储器部件27b之间。各电容器28具有以意外的电力切断时的数据保护为目的电源备份功能。例如,在来自主机装置的电力供给意外地被切断的情况下,多个电容器28在一定时间内向控制器23、多个dram26以及多个半导体存储器部件27等供给电力。各电容器28例如是铝电解电容器。但是,电容器28并不限定于上述例。电容器28是“电子部件”的一个例子。

[0045]

<3.壳体>

[0046]

<3.1壳体的整体构成>

[0047]

接下来,对壳体10进行说明。

[0048]

图5是表示壳体10的立体图。壳体10例如具有下壁31、上壁32、第一侧壁33以及第二侧壁34。

[0049]

下壁31位于壳体10的-z方向侧的端部,在壳体10的外部露出。即,下壁31相对于基板单元20位于-z方向侧。下壁31是沿着x方向以及y方向的板状。下壁31包括第一下壁部41和第二下壁部42。第一下壁部41从-z方向侧面向基板21的第一区域r1(参照图9)。第二下壁部42相对于第一下壁部41位于+x方向侧。第二下壁部42在z方向上配置于与第一下壁部41相同的位置(相同的高度)。第二下壁部42从-z方向侧面向基板21的第二区域r2(参照图9)。第一下壁部41以及第二下壁部42分别是沿着x方向以及y方向的板状。第一下壁部41

以及第二下壁部42具有相同的厚度。-z方向侧是“第一侧”的一个例子。第一下壁部41是“第一壁部”的一个例子。第二下壁部42是“第二壁部”的一个例子。

[0050]

上壁32位于壳体10的+z方向侧的端部,在壳体10的外部露出。即,上壁32相对于基板单元20位于+z方向侧。上壁32是沿着x方向以及y方向的板状。上壁32包括第一上壁部51和第二上壁部52。第一上壁部51从+z方向侧面向基板21的第一区域r1(参照图9)。第二上壁部52相对于第一上壁部51位于+x方向侧。第二上壁部52在z方向上配置于与第一上壁部51相同的位置(相同的高度)。第二上壁部52从+z方向侧面向基板21的第二区域r2(参照图9)。第一上壁部51以及第二上壁部52分别是沿着x方向以及y方向的板状。第一上壁部51以及第二上壁部52具有相同的厚度。+z方向侧是“第二侧”的一个例子。第一上壁部51是“第三壁部”的一个例子。第二上壁部52是“第四壁部”的一个例子。

[0051]

第一侧壁33位于壳体10的-y方向侧的端部,在壳体10的外部露出。即,第一侧壁33相对于基板单元20位于-y方向侧。第一侧壁33是沿着x方向以及z方向的板状。第一侧壁33在z方向上横跨下壁31与上壁32。即,第一侧壁33从-y方向侧覆盖下壁31与上壁32之间的空间。在本实施方式中,第一侧壁33在x方向上遍及第一上壁部51的全长以及第二上壁部52的全长。第一侧壁33是“第五壁部”的一个例子。

[0052]

第二侧壁34位于壳体10的+y方向侧的端部,在壳体10的外部露出。即,第二侧壁34相对于基板单元20位于+y方向侧。第二侧壁34是沿着x方向以及z方向的板状。第二侧壁34在z方向上横跨下壁31与上壁32。即,第二侧壁34从+y方向侧覆盖下壁31与上壁32之间的空间。在本实施方式中,第二侧壁34在x方向上遍及第一上壁部51的全长以及第二上壁部52的全长。第二侧壁34是“第六壁部”的一个例子。

[0053]

壳体10包括上述的下壁31、上壁32、第一侧壁33以及第二侧壁34,是扁平的矩形筒状。在本实施方式中,壳体10包括一片第一部件m1和一片第二部件m2。第一部件m1与第二部件m2是分体的。第一部件m1与第二部件m2通过组合构成壳体10。第一部件m1与第二部件m2能够相互分离。以下,对该内容进行详细地说明。

[0054]

<3.2第一部件>

[0055]

图6是表示第一部件m1的立体图。第一部件m1例如包括第一下壁部41、第二上壁部52、第一侧壁33以及第二侧壁34。例如,第一部件m1通过挤压加工等由金属材料一体成型。

[0056]

第一下壁部41具有板状的壁主体41a、一对支承部41b、第一凹陷u1、第二凹陷u2的第一部分u2a、以及一个以上的定位销41c。一对支承部41b、第一凹陷u1、第二凹陷u2的第一部分u2a以及一个以上的定位销41c设于壁主体41a的+z方向侧的表面。

[0057]

一对支承部41b设于第一下壁部41的-x方向侧的端部。一对支承部41b在y方向上分开位于第一下壁部41的两端部。一对支承部41b从壁主体41a的表面向+z方向突出。在一对支承部41b之上载置基板21的第一端部21e1。在一对支承部41b分别设有供固定部件80卡合的卡合孔41h。

[0058]

第一凹陷u1以及第二凹陷u2的第一部分u2a从壁主体41a的表面向-z方向凹陷。第一凹陷u1设于与控制器23对应的位置,是避开控制器23的凹陷(参照图9)。第二凹陷u2设于与多个第一电容器28a对应的位置,是避开多个第一电容器28a的凹陷(参照图9)。在本实施方式中,在第一下壁部41设有第二凹陷u2的一部分(第一部分u2a)。

[0059]

定位销41c从壁主体41a的表面向+z方向突出。定位销41c插入基板21的插通孔

21hb,用于进行基板单元20的定位。

[0060]

第二上壁部52相对于第一下壁部41位于+x方向侧且+z方向侧。第二上壁部52具有板状的壁主体52a和一对支承部52b。一对支承部52b设于壁主体52a的-z方向侧的表面。一对支承部52b设于第二上壁部52的+x方向侧的端部。一对支承部52b在y方向上分开位于第二上壁部52的两端部。一对支承部52b从壁主体52a向-z方向突出。一对支承部52b与基板21的第二端部21e2抵接。在一对支承部52b上分别设有供固定部件80通过的插通孔52h。

[0061]

第一侧壁33位于第一部件m1的-y方向侧的端部。第一侧壁33连接第一下壁部41的-y方向侧的端部和第二上壁部52的-y方向侧的端部。另一方面,第二侧壁34位于第一部件m1的+y方向侧的端部。第二侧壁34连接第一下壁部41的+y方向侧的端部和第二上壁部52的+y方向侧的端部。在本实施方式中,y方向上的第一侧壁33以及第二侧壁34各自的厚度t2比z方向上的第一下壁部41的厚度t1(例如壁主体41a的厚度)薄。

[0062]

通过具有以上那样的构成,在第一部件m1之中设有第一下壁部41的区域形成为向+z方向开放的碗装。另外,在第一部件m1之中设有第二上壁部52的区域形成为向-z方向开放的碗装。

[0063]

<3.3第二部件>

[0064]

图7是表示第二部件m2的立体图。第二部件m2例如包括第二下壁部42、第一上壁部51、第三连接部61以及第四连接部62。例如第二部件m2通过挤压加工等由金属材料一体成型。

[0065]

第二下壁部42具有板状的壁主体42a、一对支承部42b、第二凹陷u2的第二部分u2b、以及一个以上的止转销42c。一对支承部42b、第二凹陷u2的第二部分u2b以及一个以上的止转销42c设于壁主体42a的+z方向侧的表面。

[0066]

一对支承部42b设于第二下壁部42的+x方向侧的端部。一对支承部42b在y方向上分开位于第二下壁部42的两端部。一对支承部42b从壁主体42a的表面向+z方向突出。在一对支承部42b之上载置基板21的第二端部21e2。在一对支承部42b分别设有供固定部件80卡合的卡合孔42h。

[0067]

第二凹陷u2的第二部分u2b从壁主体42a的表面向-z方向凹陷。第二凹陷u2的第二部分u2b与上述的第一下壁部41的第二凹陷u2的第一部分u2a在x方向上相邻。换言之,第二凹陷u2遍及第一下壁部41与第二下壁部42而设置。

[0068]

止转销42c从壁主体42a的表面向+z方向突出。止转销42c插入基板21的插通孔21hc,例如用于抑制在组装时基板单元20旋转。

[0069]

第二下壁部42的+x方向侧的端部比第二上壁部52的+x方向侧的端部向+x方向突出。第二下壁部42的+x方向侧的端部作为在将半导体存储装置1安装于主机装置时由作业者把持的把手部发挥功能。在第二下壁部42的+x方向侧的端部设有用于将半导体存储装置1相对于主机装置固定或者定位的一个以上的孔h。

[0070]

第一上壁部51相对于第二下壁部42位于-x方向侧且+z方向侧。第一上壁部51具有板状的壁主体51a和一对支承部51b。一对支承部51b设于壁主体51a的-z方向侧的表面。一对支承部51b设于第一上壁部51的-x方向侧的端部。一对支承部51b在y方向上分开位于第一上壁部51的两端部。一对支承部51b从壁主体51a向-z方向突出。一对支承部51b与基板21的第一端部21e1抵接。在一对支承部51b分别设有供固定部件80通过的插通孔51h。

[0071]

第三连接部61以及第四连接部62在y方向上配置于第一部件m1的第一侧壁33与第二侧壁34之间。第三连接部61例如位于第二部件m2的-y方向侧的端部。第三连接部61连接第一上壁部51的-y方向侧的端部和第二下壁部42的-y方向侧的端部。另一方面,第四连接部62例如位于第二部件m2的+y方向侧的端部。第四连接部62连接第一上壁部51的+y方向侧的端部和第二下壁部42的+y方向侧的端部。在y方向上,在第三连接部61与第四连接部62之间配置上述基板单元20。

[0072]

在本实施方式中,第三连接部61以及第四连接部62分别以从第一上壁部51的+x方向侧的端部朝向第二下壁部42的-x方向侧的端部的方式相对于x方向倾斜地延伸。x方向上的第三连接部61以及第四连接部62各自的长度l2比x方向上的第一侧壁33以及第二侧壁34各自的长度l1(参照图6)短。从另一观点来看,x方向上的第三连接部61以及第四连接部62各自的宽度w(例如最大宽度)比x方向上的第一侧壁33以及第二侧壁34各自的长度l1短。在本实施方式中,y方向上的第三连接部61以及第四连接部62各自的厚度t3比z方向上的第二下壁部42的厚度t4(参照图7,例如壁主体42a的厚度)薄。

[0073]

图8是用于说明第二部件m2相对于第一部件m1的安装方法的图。在本实施方式中,第二部件m2以相对于第一部件m1斜向倾斜的姿势插入一侧壁33与第二侧壁34之间。然后,如图8中的箭头a所示,使第二部件m2相对于第一部件m1转动,以使第一上壁部51与第一下壁部41平行,并且第二下壁部42与第二上壁部52平行。由此,组合第一部件m1与第二部件m2而形成壳体10。

[0074]

<3.4壳体与基板单元的关系>

[0075]

图9是沿着图1中所示的半导体存储装置1的f9-f9线的剖面图。如图9所示,第一下壁部41从-z方向侧面向控制器23以及电力转换部件24。第一下壁部41使热传导性部件71a(例如热传导性片材)夹设在其间,与控制器23连接。第一下壁部41使热传导性部件71b(例如热传导性片材)夹设在其间,与电力转换部件24连接。另一方面,第二下壁部42从-z方向侧面向多个第一半导体存储器部件27a。第二下壁部42使热传导性部件71c(例如热传导性片材)夹设在其间,与多个第一半导体存储器部件27a连接。另外,也可以省略热传导性部件71a、71b、71c中的一个以上。

[0076]

第一上壁部51从+z方向侧面向电源电路部件25。第一上壁部51使热传导性部件71d(例如热传导性片材)夹设在其间,与电源电路部件25连接。另一方面,第二上壁部52从+z方向侧面向多个第二半导体存储器部件27b。第二上壁部52使热传导性部件71e(例如热传导性片材)夹设在其间,与多个第二半导体存储器部件27b连接。另外,也可以省略热传导性部件71d、71e中的一个以上。

[0077]

在本实施方式中,下壁31在x方向上在第一下壁部41与第二下壁部42之间具有第一间隙s1。第一间隙s1的长度方向沿着y方向(参照图5)。第一间隙s1例如在y方向上遍及第二部件m2的整个宽度而设置。第一间隙s1抑制热量从第一下壁部41朝向第二下壁部42的传导。第一间隙s1是热传导率比第一下壁部41的热传导率低的部分。第一间隙s1是“第一部分”的一个例子。

[0078]

同样,上壁32在x方向上在第一上壁部51与第二上壁部52之间具有第二间隙s2。第二间隙s2的长度方向沿着y方向(参照图5)。第二间隙s2例如在y方向上遍及第二部件m2的整个宽度而设置。第二间隙s2抑制热量从第一上壁部51朝向第二上壁部52的传导。第二间

隙s2是热传导率比第一上壁部51的热传导率低的部分。第二间隙s2是“第二部分”的一个例子。

[0079]

在本实施方式中,第一间隙s1以及第二间隙s2在壳体10的外部露出。在壳体10的外部流动的空气能够通过第一间隙s1以及第二间隙s2流入壳体10内。在本实施方式中,通过设有第一间隙s1以及第二间隙s2,能够避免组装壳体10时的第一部件m1与第二部件m2的干扰。即,通过设有第一间隙s1以及第二间隙s2,第二部件m2以相对于第一部件m1斜着倾斜的姿势组合,之后,能够使第二部件m2相对于第一部件m1转动。

[0080]

如图9所示,壳体10在x方向上,具有第一端部10e1和与第一端部10e1相反的第二端部10e2。第一端部10e1是-x方向侧的端部。第二端部10e2是+x方向侧的端部。上述的第一间隙s1(即第一下壁部41与第二下壁部42的边界部)在x方向上位于比壳体10的第一端部10e1以及第二端部10e2更靠近壳体10的中央部的位置。同样,上述的第二间隙s2(即第一上壁部51与第二上壁部52的边界部)在x方向上位于比壳体10的第一端部10e1以及第二端部10e2更靠近壳体10的中央部的位置。

[0081]

图10是沿着图9中所示的半导体存储装置1的f10-f10线的剖面图。在本实施方式中,第二下壁部42在y方向配置于第一侧壁33与第二侧壁34之间。而且,在y方向上在第二下壁部42与第一侧壁33之间设有第三间隙s3。在y方向上在第二下壁部42与第二侧壁34之间设有第四间隙s4。

[0082]

图11是表示的壳体10的下壁31的一部分仰视图。第三间隙s3以及第四间隙s4与第一间隙s1连通。第三间隙s3以及第四间隙s4各自的长度方向沿着x方向。第三间隙s3以及第四间隙s4在壳体10的外部露出。在壳体10的外部流动的空气能够通过第三间隙s3以及第四间隙s4流入壳体10内。

[0083]

如图11所示,在本实施方式中,第三连接部61的一部分相对于第二下壁部42的-y方向侧的端部向-y方向侧突出地设置。由此,在确保收容基板单元20的收容空间较宽的同时,确保第三连接部61的强度。为了避免从第二下壁部42突出的第三连接部61与第一侧壁33干扰,第三间隙s3由设于第一侧壁33的凹陷u3形成。同样,第四连接部62的一部分相对于第二下壁部42的+y方向侧的端部向+y方向侧突出地设置。由此,在确保收容基板单元20的收容空间较宽的同时,确保第四连接部62的强度。为了避免从第二下壁部42突出的第四连接部62干扰第二侧壁34,第四间隙s4由设于第二侧壁34的凹陷u4形成。

[0084]

同样,第一上壁部51在y方向上配置于第一侧壁33与第二侧壁34之间(参照图5)。而且,在y方向上,在第一上壁部51与第一侧壁33之间设有第五间隙s5。在y方向上,在第一上壁部51与第二侧壁34之间设有第六间隙s6。第五间隙s5以及第六间隙s6例如具有与第三间隙s3以及第四间隙s4类似的形状。即,第五间隙s5以及第六间隙s6与第二间隙s2连通。第五间隙s5以及第六间隙s6各自的长度方向沿着x方向。第五间隙s5以及第六间隙s6在壳体10的外部露出。在壳体10的外部流动的空气能够通过第五间隙s5以及第六间隙s6流入壳体10内。

[0085]

在本实施方式中,第三连接部61的一部分相对于第一上壁部51的-y方向侧的端部向-y方向侧突出地设置。由此,在确保收容基板单元20的收容空间较宽的同时,确保第三连接部61的强度。为了避免从第一上壁部51突出的第三连接部61与第一侧壁33干扰,第五间隙s5由设于第一侧壁33的凹陷u5形成。第四连接部62的一部分相对于第一上壁部51的

+y方向侧的端部向+y方向侧突出地设置。由此,在确保收容基板单元20的收容空间较宽的同时,确保第四连接部62的强度。为了避免从第一上壁部51突出的第四连接部62与第二侧壁34干扰,第六间隙s6由设于第二侧壁34的凹陷u6形成。凹陷u5以及凹陷u6的形状例如与图11所示的凹陷u3以及凹陷u4相同。

[0086]

<4.固定部件>

[0087]

返回图1,对多个固定部件80进行说明。多个固定部件80固定上述的第一部件m1与第二部件m2。在本实施方式中,多个固定部件80相对于第一部件m1以及第二部件m2共同紧固固定基板21。多个固定部件80例如包括多个第一固定部件80a和多个第二固定部件80b。

[0088]

各第一固定部件80a穿过第一上壁部51的支承部51b的插通孔51h以及基板21的插通孔21ha,卡合于第一下壁部41的支承部41b的卡合孔41h。由此,第一上壁部51与第一下壁部41被固定,并且基板21被夹持固定在第一上壁部51的支承部51b与第一下壁部41的支承部41b之间。

[0089]

各第二固定部件80b穿过第二上壁部52的支承部52b的插通孔52h以及基板21的插通孔21ha,卡合于第二下壁部42的支承部42b的卡合孔42h。由此,第二上壁部52与第二下壁部42被固定,并且基板21被夹持固定在第二上壁部52的支承部52b与第二下壁部42的支承部42b之间。

[0090]

这里,对基板单元20的安装方法的一个例子进行说明。基板单元20例如在第二部件m2以相对于第一部件m1斜着倾斜的姿势插入的状态(图8中所示的状态)下,插入第一部件m1与第二部件m2之间。在基板单元20中,例如定位销41c(参照图6)插入基板21的插通孔21hb,止转销42c(参照图7)插入基板21的插通孔21hc,由此进行基板单元20的定位,并且抑制基板单元20的旋转。

[0091]

在该状态下,通过使第二部件m2相对于第一部件m1向图8中的箭头a的方向转动,基板单元20被夹在第一部件m1与第二部件m2之间。在本实施方式中,基板21的第一端部21e1被夹在第一下壁部41的支承部41b与第一上壁部51的支承部51b之间。而且,基板21的第二端部21e2被夹在第二下壁部42的支承部42b与第二上壁部52的支承部52b之间。通过在该状态下将多个固定部件80安装于壳体10,将基板单元20固定于壳体10。另外,基板单元20的安装方法并不限定于上述例。例如,也可以在将基板单元20安装于第二部件m2之后,将第二部件m2安装于第一部件m1。

[0092]

<5.作用>

[0093]

如上述那样,控制器23以及电力转换部件24例如经由热传导性部件71a、71b而与第一下壁部41连接。因此,从控制器23以及电力转换部件24产生的热量的一部分经由热传导性部件71a、71b向第一下壁部41传导。因此,第一下壁部41的温度上升。然而,由于第一下壁部41与第二下壁部42未一体地形成,因此从控制器23以及电力转换部件24传导至第一下壁部41的热量难以从第一下壁部41向第二下壁部42传导。因此,相比于第一下壁部41与第二下壁部42为一体的情况,第二下壁部42的温度不易上升。其结果,能够抑制耐热性比控制器23以及电力转换部件24的耐热性低的半导体存储器部件27(例如第一半导体存储器部件27a)成为高温。

[0094]

这里,从控制器23以及电力转换部件24传导至第一下壁部41的热量的一部分经由第一侧壁33以及第二侧壁34向第二上壁部52传导。然而,从第一下壁部41经由第一侧壁33

以及第二侧壁34向第二上壁部52传导的热量少于第一下壁部41与第二下壁部42一体地形成的情况下从壁31经由第一侧壁33以及第二侧壁34向上壁32传导的热量。因此,可抑制半导体存储器部件27(例如第二半导体存储器部件27b)成为高温。

[0095]

同样,电源电路部件25例如经由热传导性部件71d而与第一上壁部51连接。因此,从电源电路部件25产生的热量的一部分经由热传导性部件71d向第一上壁部51传导。因此,第一上壁部51的温度上升。但是,由于第一上壁部51与第二上壁部52未一体地形成,因此从电源电路部件25向第一上壁部51传导的热量难以从第一上壁部51向第二上壁部52传导。因此,相比于第一上壁部51与第二上壁部52为一体的情况,第二上壁部52的温度不易上升。其结果,能够抑制耐热性比电源电路部件25的耐热性低的半导体存储器部件27(例如第二半导体存储器部件27b)成为高温。

[0096]

这里,从电源电路部件25传导至第一上壁部51的热量的一部分经由第三连接部61以及第四连接部62向第二下壁部42传导。然而,从第一上壁部51经由第三连接部61以及第四连接部62向第二下壁部42传导的热量少于第一上壁部51与第二上壁部52一体地形成的情况下从上壁32经由第一侧壁33以及第二侧壁34向下壁31传导的热量。因此,可抑制半导体存储器部件27(例如第一半导体存储器部件27a)成为高温。

[0097]

<6.优点>

[0098]

在本实施方式中,壳体10具有:相对于基板21位于-z方向侧且面向基板21的第一区域r1的第一下壁部41;相对于基板21位于-z方向侧且面向基板21的第二区域r2的第二下壁部42;相对于基板21位于+z方向侧且面向基板21的第一区域r1的第一上壁部51;以及相对于基板21位于+z方向侧且面向基板21的第二区域r2的第二上壁部52。第一下壁部41以及第二上壁部52由第一部件m1形成。第二下壁部42以及第一上壁部51由第二部件m2形成。即,第一下壁部41与第二下壁部42形成为能够相互分离。另外,第一上壁部51与第二上壁部52形成为能够相互分离。根据这样的构成,相比于第一下壁部41与第二下壁部42为一体的情况,可抑制热量从第一下壁部41向第二下壁部42的传导,相比于第一上壁部51与第二上壁部52为一体的情况,可抑制热量从第一上壁部51向第二上壁部52的传导。由此,能够抑制半导体存储器部件27的温度上升。其结果,能够实现半导体存储装置1的可靠性的提高。此外,根据上述构成,与第一下壁部41、第二下壁部42、第一上壁部51以及第二上壁部52由不同的部件形成的情况相比,能够减少部件数量,提高壳体10的刚性。从该观点来看,也能够实现半导体存储装置1的可靠性的提高。

[0099]

在本实施方式中,壳体10在第一下壁部41与第二下壁部42之间具有热传导率比第一下壁部41的热传导率低的第一部分。根据这样的构成,能够进一步抑制热量从第一下壁部41向第二下壁部42的传导。

[0100]

在本实施方式中,上述第一部分是设于第一下壁部41与第二下壁部42之间的第一间隙s1。根据这样的构成,能够进一步抑制热量从第一下壁部41向第二下壁部42的传导。另外,在将半导体存储装置1设于向壳体10的周围供给冷却空气的环境的情况下,也能够期待冷却空气的一部分从第一间隙s1流入壳体10内。由此,能够进一步抑制半导体存储器部件27的温度上升。

[0101]

在本实施方式中,壳体10在第一上壁部51与第二上壁部52之间具有热传导率比第一上壁部51的热传导率低的第二部分。根据这样的构成,能够进一步抑制热量从第一上壁

部51向第二上壁部52的传导。

[0102]

在本实施方式中,第一部件m1具有分开设置在壳体10的y方向的两端部、且分别连接第一下壁部41与第二上壁部52的第一侧壁33以及第二侧壁34。第二部件m2具有在y方向上配置于第一侧壁33与第二侧壁34之间、且分别连接第二下壁部42与第一上壁部51的第三连接部61以及第四连接部62。根据这样的构成,能够通过相对较简单的构成连接第一下壁部41与第二上壁部52,连接第二下壁部42与第一上壁部51。其结果,容易确保壳体10的内部空间较宽。

[0103]

在本实施方式中,第一侧壁33以及第二侧壁34在壳体10的外部露出。根据这样的构成,在将半导体存储装置1设置在向壳体10的周围供给冷却空气的环境的情况下,连接第一下壁部41与第二上壁部52的第一侧壁33以及第二侧壁34被冷却空气冷却。因此,能够进一步抑制热量从第一下壁部41向第二上壁部52的传导。

[0104]

在本实施方式中,y方向上的第一侧壁33的厚度t2比z方向上的第一下壁部41的厚度t1薄。根据这样的构成,与第一侧壁33较厚的情况相比热量难以在第一侧壁33中传导。因此,能够进一步抑制热量从第一下壁部41向第二上壁部52的传导。

[0105]

在本实施方式中,x方向上的第三连接部61的长度l2比x方向上的第一侧壁33的长度l1短。即,将难以期待基于供给到壳体10的周围的冷却空气的冷却的第三连接部61形成得相对较小。根据这样的构成,由于第三连接部61相对较小,因此热量难以在第三连接部61中传导。因此,能够进一步抑制热量从第一上壁部51向第二下壁部42的传导。

[0106]

在本实施方式中,y方向上的第三连接部61的厚度t3比z方向上的第二下壁部42的厚度t4薄。根据这样的构成,与第三连接部61较厚的情况相比,热量难以在第三连接部61中传导。因此,能够进一步抑制热量从第一上壁部51向第二下壁部42传导。

[0107]

在本实施方式中,壳体10具有在y方向上设于第二部件m2与第一侧壁33之间且在壳体10的外部露出的第三间隙s3。根据这样的构成,在将半导体存储装置1设置在向壳体10的周围供给冷却空气的环境的情况下,能够期待冷却空气的一部分从第三间隙s3流入壳体10内。由此,能够进一步抑制半导体存储器部件27的温度上升。

[0108]

在本实施方式中,第三间隙s3的长度方向为x方向。根据这样的构成,在将半导体存储装置1设置在沿x方向向壳体10的周围供给冷却空气的环境的情况下,能够期待更多的冷却空气从第三间隙s3流入壳体10内。

[0109]

在本实施方式中,第一下壁部41与第二下壁部42的边界部在x方向上位于比壳体10的第一端部10e1以及第二端部10e2更靠近壳体10的中央部的位置。第一上壁部51与第二上壁部52的边界部在x方向上位于比壳体10的第一端部10e1以及第二端部10e2更靠近壳体10的中央部的位置。根据这样的构成,与上述边界部位于壳体10的第一端部10e1或者第二端部10e2的附近的情况相比,例如在图8所示那样的伴随着转动作业的组装作业中,能够提高组装作业的稳定性。

[0110]

在本实施方式中,壳体10的内表面具有避开电容器28的第二凹陷u2。第二凹陷u2遍及第一下壁部41与第二下壁部42而设置。根据这样的构成,第一下壁部41与第二下壁部42的彼此相邻的部分的一部分形成得较薄,能够进一步抑制热量从第一下壁部41向第二下壁部42的传导。

[0111]

在本实施方式中,基板21被夹持固定在第一下壁部41与第一上壁部51之间,并且

被夹持固定在第二下壁部42与第二上壁部52之间。根据这样的构成,在第一下壁部41与第二下壁部42不为一体、且第一上壁部51与第二上壁部52不为一体的构成中,能够稳定地固定基板21。

[0112]

(第二实施方式)

[0113]

接下来,对第二实施方式进行说明。在第二实施方式中,除以下说明以外的构成与第一实施方式的构成相同。

[0114]

图12是分解表示第二实施方式的壳体10a立体图。在本实施方式中,壳体10a包括第一部件m1、第三部件m3a以及第四部件m4a。

[0115]

第一部件m1与第一实施方式相同,包括第一下壁部41、第二上壁部52、第一侧壁33以及第二侧壁34。第三部件m3a包括第二下壁部42。第四部件m4包括第一上壁部51。即在本实施方式中,第二下壁部42和第一上壁部51由相互不同的多个部件形成。第三部件m3a(即第二下壁部42)和第四部件m4a(即第一上壁部51)分别相对于第一部件m1安装。在本实施方式中,第一下壁部41是“第一壁部”的一个例子。第二下壁部42是“第二壁部”的一个例子。第一上壁部51是“第三壁部”的一个例子。第二上壁部52是“第四壁部”的一个例子。

[0116]

根据这样的构成,也能够抑制热量从第一下壁部41向第二下壁部42的传导以及热量从第一上壁部51向第二上壁部52的传导。其结果,能够实现半导体存储装置1的可靠性的提高。

[0117]

(第三实施方式)

[0118]

接下来,对第三实施方式进行说明。在第三实施方式中,除以下说明以外的构成与第一实施方式的构成相同。

[0119]

图13是分解表示第三实施方式的壳体10b立体图。在本实施方式中,壳体10b包括第五部件m5b、第六部件m6b以及第二部件m2。

[0120]

第二部件m2与第一实施方式相同,包括第一上壁部51、第二下壁部42、第三连接部61以及第四连接部62。第五部件m5b包括第一下壁部41、作为第一侧壁33的一部分的第一部分33a以及作为第二侧壁34的一部分的第一部分34a。第六部件m6b包括第二上壁部52、作为第一侧壁33的其余部分的第二部分33b以及作为第二侧壁34的其余部分的第二部分34b。即在本实施方式中,第一下壁部41和第二上壁部52由相互不同的多个部件形成。第五部件m5b(即第一下壁部41)和第六部件m6b(即第二上壁部52)分别相对于第二部件m2安装。在本实施方式中,第一上壁部51是“第一壁部”的一个例子。第二上壁部52是“第二壁部”的一个例子。第一下壁部41是“第三壁部”的一个例子。第二下壁部42是“第四壁部”的一个例子。

[0121]

根据这样的构成,也能够抑制热量从第一下壁部41向第二下壁部42的传导以及热量从第一上壁部51向第二上壁部52的传导。其结果,能够实现半导体存储装置1的可靠性的提高。

[0122]

(第四实施方式)

[0123]

接下来,对第四实施方式进行说明。在第四实施方式中,除以下说明以外的构成与第一实施方式的构成相同。

[0124]

图14是分解表示第四实施方式的壳体10c立体图。在本实施方式中,壳体10c包括第七部件m7c、第八部件m8c、第九部件m9c以及第十部件m10c。

[0125]

第七部件m7c包括第一下壁部41、作为第一侧壁33的一部分的第一部分33a以及作

为第二侧壁34的一部分的第一部分34a。第八部件m8c包括第二下壁部42。第九部件m9c包括第一上壁部51。第十部件m10c包括第二上壁部52、作为第一侧壁33的其余部分的第二部分33b以及作为第二侧壁34的其余部分的第二部分34b。即在本实施方式中,第一下壁部41、第二下壁部42、第一上壁部51以及第二上壁部52由相互不同的多个部件形成。在本实施方式中,第一下壁部41是“第一壁部”的一个例子。第二下壁部42是“第二壁部”的一个例子。第一上壁部51是“第三壁部”的一个例子。第二上壁部52是“第四壁部”的一个例子。

[0126]

根据这样的构成,能够抑制热量从第一下壁部41向第二下壁部42的传导以及热量从第一上壁部51向第二上壁部52的传导。其结果,能够实现半导体存储装置1的可靠性的提高。

[0127]

以上,对几个实施方式进行了说明,但实施方式不限定于上述的例子并。例如,也可以代替遍及第一下壁部41以及第二下壁部42形成用于避开电子部件(例如电容器28)的第二凹陷u2或在其基础上,遍及第一上壁部51以及第二上壁部52形成相同的凹陷。在上述实施方式中,在基板21的第一区域r1安装有发热部件(控制器23等),在基板21的第二区域r2安装有半导体存储器部件27。代替于此,也可以在基板21的第一区域r1安装半导体存储器部件27,在基板21的第二区域r2安装发热部件(控制器23等)。

[0128]

根据以上说明的至少一个的实施方式,半导体存储装置的壳体具有:在作为基板的厚度方向的第一方向上上相对于所述基板位于第一侧且面向所述基板的第一区域的第一壁部;在所述第一方向上相对于所述基板位于所述第一侧且面向所述基板的第二区域的第二壁部;在所述第一方向上相对于所述基板位于与所述第一侧相反的一侧即第二侧且面向所述第一区域的第三壁部;以及在所述第一方向上相对于所述基板位于所述第二侧且面向所述第二区域的第四壁部。所述第一壁部由第一部件形成。所述第二壁部由与所述第一部件不同的部件形成。所述第三壁部由第二部件形成。所述第四壁部由与所述第二部件不同的部件形成。根据这样的构成,能够实现半导体存储装置的可靠性的提高。

[0129]

对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内能够进行各种省略、替换、变更。这些实施方式及其变形包括在发明的范围或主旨中,同样包括在权利要求书所记载的发明及其等效的范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1