半导体结构的制作方法及半导体结构与流程

1.本公开涉及半导体技术领域,尤其涉及一种半导体结构的制作方法及半导体结构。

背景技术:

2.随着dram(dynamic random access memory)尺寸的不断缩小,半导体器件的导电接触垫的图形也日益精细化。然而,由于光刻工艺的限制,采用相关技术形成的导电接触垫精度不能满足需求。

技术实现要素:

3.本公开提供一种半导体结构的制作方法及半导体结构,以改善半导体结构的性能。

4.根据本公开的第一个方面,提供了一种半导体结构的制作方法,包括:

5.提供衬底;

6.在衬底上形成导电层;

7.在导电层上依次形成底部掩膜结构、中间掩膜结构和顶部图案化掩膜结构;

8.利用顶部图案化掩膜结构在底部掩膜结构中形成第一图案结构;

9.在第一图案结构上形成第一掩膜结构,在第一掩膜结构中形成第二图案结构,利用第二图案结构刻蚀第一图案结构形成第三图案化结构;

10.以第三图案化结构刻蚀导电层,形成多个接触垫结构;

11.其中,第一图案结构包括多条沿第一方向延伸的第一线条图案,第二图案结构包括多条沿第二方向延伸的第二线条图案,第一方向与第二方向不同。

12.在本公开的一个实施例中,顶部图案化掩膜结构包括在中间掩膜结构上依次形成的硬掩膜层和顶部图案;

13.以顶部图案为掩膜刻蚀硬掩膜层,形成第四图案结构,第四图案结构包括多条沿第一方向延伸的第三线条图案;

14.第四图案结构通过第一自对准工艺形成第一图案结构。

15.在本公开的一个实施例中,第一自对准工艺包括sadp工艺、sarp工艺、saqp工艺、saop工艺中的一种或多种。

16.在本公开的一个实施例中,第三线条图案的周期间距大于或等于第一线条图案的周期间距。

17.在本公开的一个实施例中,形成第一图案结构包括:

18.在中间掩膜结构内形成第五图案结构,第五图案结构包括多条沿第一方向延伸的第四线条图案;

19.利用第五图案结构刻蚀底部掩膜结构形成第一图案结构。

20.在本公开的一个实施例中,相邻第四线条图案的高度不相等。

21.在本公开的一个实施例中,顶部图案包括多条沿第一方向延伸的顶部线条图案,第四线条图案的周期间距小于或等于顶部线条图案的周期间距。

22.在本公开的一个实施例中,第四线条图案的周期间距等于第一线条图案的周期间距。

23.在本公开的一个实施例中,在第一掩膜结构中形成第二图案结构包括,

24.在第一掩膜结构上形成第六图案结构,第六图案结构包括多条沿第二方向延伸的第五线条图案;以第六图案结构为掩膜刻蚀第一掩膜结构,第六图案结构通过第二自对准工艺形成第二图案结构。

25.在本公开的一个实施例中,第二自对准工艺包括sadp工艺、sarp工艺、saqp工艺、saop工艺中的一种或多种。

26.在本公开的一个实施例中,第五线条图案的周期间距大于或等于第二线条图案的周期间距。

27.在本公开的一个实施例中,第三图案化结构包括方形、菱形、平行四边形中的一种或多种。

28.在本公开的一个实施例中,第一线条图案的周期间距等于第二线条图案的周期间距。

29.在本公开的一个实施例中,多个第一线条图案的高度均相等。

30.根据本公开的第二个方面,提供了一种半导体结构,包括由上述的半导体结构的制作方法获得的半导体结构。

31.本公开实施例的半导体结构的制作方法在衬底上依次形成导电层、底部掩膜结构、中间掩膜结构和顶部图案化掩膜结构,并通过中间掩膜结构和顶部图案化掩膜结构在底部掩膜结构中形成第一图案结构,利用在第一图案结构上形成的第一掩膜结构形成第二图案结构,并利用第二图案结构在第一图案结构上形成第三图案化结构,从而可以根据第三图案化结构刻蚀导电层,以此形成多个高精度的接触垫结构,从而改善形成的半导体结构性能。

附图说明

32.通过结合附图考虑以下对本公开的优选实施方式的详细说明,本公开的各种目标,特征和优点将变得更加显而易见。附图仅为本公开的示范性图解,并非一定是按比例绘制。在附图中,同样的附图标记始终表示相同或类似的部件。其中:

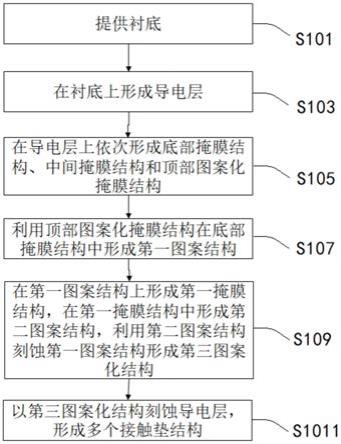

33.图1是根据一示例性实施方式示出的一种半导体结构的制作方法的流程示意图;

34.图2是根据一示例性实施方式示出的一种半导体结构的制作方法获得顶部图案的俯视结构示意图;

35.图3是根据一示例性实施方式示出的一种半导体结构的制作方法获得顶部图案的剖面结构示意图;

36.图4是根据一示例性实施方式示出的一种半导体结构的制作方法获得第三线条图案的俯视结构示意图;

37.图5是根据一示例性实施方式示出的一种半导体结构的制作方法获得第三线条图案的剖面结构示意图;

38.图6是根据一示例性实施方式示出的一种半导体结构的制作方法获得第一侧壁间隔层的俯视结构示意图;

39.图7是根据一示例性实施方式示出的一种半导体结构的制作方法获得第一侧壁间隔层的剖面结构示意图;

40.图8是根据一示例性实施方式示出的一种半导体结构的制作方法获得第一覆盖层的俯视结构示意图;

41.图9是根据一示例性实施方式示出的一种半导体结构的制作方法获得第一覆盖层的剖面结构示意图;

42.图10是根据一示例性实施方式示出的一种半导体结构的制作方法获得第四线条图案的俯视结构示意图;

43.图11是根据一示例性实施方式示出的一种半导体结构的制作方法获得第四线条图案的剖面结构示意图;

44.图12是根据一示例性实施方式示出的一种半导体结构的制作方法获得第一线条图案的俯视结构示意图;

45.图13是根据一示例性实施方式示出的一种半导体结构的制作方法获得第一线条图案的剖面结构示意图;

46.图14是根据一示例性实施方式示出的一种半导体结构的制作方法获得第五线条图案的俯视结构示意图;

47.图15是根据一示例性实施方式示出的一种半导体结构的制作方法获得第五线条图案的剖面结构示意图;

48.图16是根据一示例性实施方式示出的一种半导体结构的制作方法获得第二侧壁间隔层的俯视结构示意图;

49.图17是根据一示例性实施方式示出的一种半导体结构的制作方法获得第二侧壁间隔层的剖面结构示意图;

50.图18是根据一示例性实施方式示出的一种半导体结构的制作方法获得第二覆盖层的俯视结构示意图;

51.图19是根据一示例性实施方式示出的一种半导体结构的制作方法获得第二覆盖层的剖面结构示意图;

52.图20是根据一示例性实施方式示出的一种半导体结构的制作方法获得第二线条图案的俯视结构示意图;

53.图21是根据一示例性实施方式示出的一种半导体结构的制作方法获得第二线条图案的剖面结构示意图;

54.图22是根据一示例性实施方式示出的一种半导体结构的制作方法获得第三图案化结构的俯视结构示意图;

55.图23是根据一示例性实施方式示出的一种半导体结构的制作方法获得第三图案化结构的剖面结构示意图;

56.图24是根据一示例性实施方式示出的一种半导体结构的制作方法获得接触垫结构的俯视结构示意图;

57.图25是根据一示例性实施方式示出的一种半导体结构的制作方法获得接触垫结

构的剖面结构示意图。

58.附图标记说明如下:

59.10、衬底;20、导电层;21、接触垫结构;30、底部掩膜结构;31、第二开口;32、第三开口;33、第五硬掩膜层;34、第六硬掩膜层;35、第七硬掩膜层;36、第三图案化结构;40、中间掩膜结构;41、第一开口;42、第三硬掩膜层;43、第四硬掩膜层;50、顶部图案化掩膜结构;51、第一硬掩膜层;52、第二硬掩膜层;53、顶部图案;531、第一光刻胶开口;54、第一开孔;541、第一侧壁间隔层;542、第一覆盖层;60、第一掩膜结构;61、第一旋涂硬掩膜层;62、第八硬掩膜层;63、第二旋涂硬掩膜层;64、第九硬掩膜层;65、第五线条图案;651、第二光刻胶开口;66、第二开孔;661、第二侧壁间隔层;662、第二覆盖层;331、第一线条图案;663、第二线条图案;521、第三线条图案;431、第四线条图案。

具体实施方式

60.体现本公开特征与优点的典型实施例将在以下的说明中详细叙述。应理解的是本公开能够在不同的实施例上具有各种的变化,其皆不脱离本公开的范围,且其中的说明及附图在本质上是作说明之用,而非用以限制本公开。

61.在对本公开的不同示例性实施方式的下面描述中,参照附图进行,附图形成本公开的一部分,并且其中以示例方式显示了可实现本公开的多个方面的不同示例性结构、系统和步骤。应理解的是,可以使用部件、结构、示例性装置、系统和步骤的其他特定方案,并且可在不偏离本公开范围的情况下进行结构和功能性修改。而且,虽然本说明书中可使用术语“之上”、“之间”、“之内”等来描述本公开的不同示例性特征和元件,但是这些术语用于本文中仅出于方便,例如根据附图中的示例的方向。本说明书中的任何内容都不应理解为需要结构的特定三维方向才落入本公开的范围内。

62.本公开的一个实施例提供了一种半导体结构的制作方法,请参考图1至图25,半导体结构的制作方法包括:

63.s101,提供衬底10;

64.s103,在衬底10上形成导电层20;

65.s105,在导电层20上依次形成底部掩膜结构30、中间掩膜结构40和顶部图案化掩膜结构50;

66.s107,利用顶部图案化掩膜结构50在底部掩膜结构30中形成第一图案结构;

67.s109,在第一图案结构上形成第一掩膜结构60,在第一掩膜结构60中形成第二图案结构,利用第二图案结构刻蚀第一图案结构形成第三图案化结构36;

68.s1011,以第三图案化结构36刻蚀导电层20,形成多个接触垫结构21;

69.其中,第一图案结构包括多条沿第一方向延伸的第一线条图案331,第二图案结构包括多条沿第二方向延伸的第二线条图案663,第一方向与第二方向不同。

70.本公开一个实施例的半导体结构的制作方法在衬底10上依次形成导电层20、底部掩膜结构30、中间掩膜结构40和顶部图案化掩膜结构50,并通过中间掩膜结构40和顶部图案化掩膜结构50在底部掩膜结构30中形成第一图案结构,利用在第一图案结构上形成的第一掩膜结构60形成第二图案结构,并利用第二图案结构在第一图案结构上形成第三图案化结构36,从而可以根据第三图案化结构36刻蚀导电层20,以此形成多个高精度的接触垫结

构21,从而改善形成的半导体结构性能。

71.需要说明的是,由于导电层20上形成有底部掩膜结构30、中间掩膜结构40和顶部图案化掩膜结构50,从而可以利用顶部图案化掩膜结构50对中间掩膜结构40进行图像化,然后利用中间掩膜结构40对底部掩膜结构30进行图像化,从而形成较高精度的第一图案结构,即多条沿第一方向延伸的第一线条图案331。相比于相关技术中利用类似顶部图案化掩膜结构直接在底部掩膜结构上进行形成线条图案,本实施例中由于中间掩膜结构40的存在可以避免直接在底部掩膜结构30上图案化而引发的各类问题,例如出现尖角、平整度无法保证等。而本实施例中,即使会出现上述问题也是在中间掩膜结构40上形成,后续通过去除中间掩膜结构40即可克服上述问题,以此保证第一图案结构的制作精度,从而来提升后续形成第三图案化结构36的精度,从而可以根据第三图案化结构36刻蚀处多个高精度的接触垫结构21,从而改善形成的半导体结构性能。

72.在一些实施例中,衬底10可以包括由含硅材料形成的部分。衬底10可以由任何合适的材料形成,例如,包括硅、单晶硅、多晶硅、非晶硅、硅锗、单晶硅锗、多晶硅锗以及碳掺杂硅中的至少一种。导电层20的材料包括但不限于钨(w)。

73.在一些实施例中,利用顶部图案化掩膜结构50在中间掩膜结构40上形成多个第一开口41,并利用第一开口41刻蚀底部掩膜结构30,以形成多个第二开口31,以此形成第一图案结构,即形成多条沿第一方向延伸的第一线条图案331。

74.在形成有第一开口41的底部掩膜结构30上形成第一掩膜结构60和多条沿第二方向延伸的第五线条图案65,并利用第一掩膜结构60在底部掩膜结构30上形成与多个第二开口31相交叉的多个第三开口32,以此形成了第三图案化结构36,即多个独立的第三图案化结构36。利用第二开口31和第三开口32刻蚀导电层20,从而在衬底10上形成多个接触垫结构21。

75.在一个实施例中,顶部图案化掩膜结构50包括在中间掩膜结构40上依次形成的硬掩膜层和顶部图案53;以顶部图案53为掩膜刻蚀硬掩膜层,形成第四图案结构,第四图案结构包括多条沿第一方向延伸的第三线条图案521;第四图案结构通过第一自对准工艺形成第一图案结构,以此保证在形成第一图案结构的过程中不会出现对准不好的问题,从而提高了形成的多个第一线条图案331的精度。

76.结合图2和图3所示,顶部图案化掩膜结构50的硬掩膜层包括第一硬掩膜层51和第二硬掩膜层52,即顶部图案化掩膜结构50包括在中间掩膜结构40上依次形成的第一硬掩膜层51、第二硬掩膜层52以及顶部图案53,顶部图案53可以是第一光刻胶层,第一光刻胶层具有第一光刻胶开口531,利用第一光刻胶开口531刻蚀第二硬掩膜层52和第一硬掩膜层51,以形成多个第一开孔54,第一开孔54暴露中间掩膜结构40,即形成了包括多条沿第一方向延伸的第三线条图案521的第四图案结构,如图4和图5所示。

77.在一个实施例中,第一自对准工艺可以包括sadp(self-aligned double patterning,自对准双重构图)工艺、sarp(self-aligned reverse patterning,自对准反相构图)工艺、saqp工艺(self-aligned quadruple patterning,自对准四重图案化)、saop工艺(self-aligned octuple patterning)中的一种或多种,以此获得高精度的第一图案结构。

78.需要说明的是,对于上述第一自对准工艺的具体制作步骤本实施例中不作限定,

可以参考相关技术中的工艺。

79.在一些实施例中,第一自对准工艺可以包括:

80.在第一开孔54的侧壁形成第一侧壁间隔层541,如图6和图7所示,第一侧壁间隔层541覆盖中间掩膜结构40,并埋覆第三线条图案521。

81.在第一开孔54内形成第一覆盖层542,第一覆盖层542暴露第一侧壁间隔层541的顶端,如图8、图9所示。

82.在一些实施例中,第一开孔54的侧壁可以是平面,如图5至图9所示。

83.在一些实施例中,第一硬掩膜层51可以为旋涂硬硬掩膜层(soh)。第二硬掩膜层52可以采用氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等。第一覆盖层542可以为电介质层(ox)。第一覆盖层542可以为旋涂硬硬掩膜层(soh)。

84.在一个实施例中,第三线条图案521的周期间距大于或等于第一线条图案331的周期间距。

85.第三线条图案521的周期间距可以等于第一线条图案331的周期间距,从而可以以第三线条图案521为掩膜,获得与第三线条图案521数量相一致的第一线条图案331。或者,第三线条图案521的周期间距可以大于第一线条图案331的周期间距,根据第三线条图案521利用sadp工艺、sarp工艺、saqp工艺、saop工艺中的一种或多种获得第一线条图案331。

86.在一个实施例中,底部掩膜结构30包括依次形成于导电层20上的第五硬掩膜层33、第六硬掩膜层34以及第七硬掩膜层35。中间掩膜结构40包括依次形成于底部掩膜结构30上的第三硬掩膜层42和第四硬掩膜层43。第五硬掩膜层33可以为电介质层(ox),第六硬掩膜层34可以采用氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等,第七硬掩膜层35可以为非晶碳层(acl)。

87.在一些实施例中,第一自对准工艺还可以包括:利用第一侧壁间隔层541的顶端蚀刻第一侧壁间隔层541和中间掩膜结构40,以形成第一开口41,如图10至图11所示。第一开口41贯穿中间掩膜结构40以暴露底部掩膜结构30。其中,图9的结构形成第一开口41后形成如图11所示的结构。

88.在一些实施例中,第一侧壁间隔层541覆盖第一开孔54暴露的第四硬掩膜层43的全部上表面,以在形成第一开口41后,第四硬掩膜层43上保留部分的第一侧壁间隔层541。

89.在一些实施例中,底部掩膜结构30包括第五硬掩膜层33,第一自对准工艺还可以包括:利用第一开口41刻蚀第五硬掩膜层33,以形成第二开口31,如图12和图13所示,即形成了多个第一线条图案331。形成第二开口31,并去除底部掩膜结构30上的所有结构之后,从而形成了多个第一线条图案331。后续以第二开口31作为对准标记用于形成多个接触垫结构21。

90.在一些实施例中,第二开口31贯穿第五硬掩膜层33。第五硬掩膜层33可以为电介质层(ox)。

91.在一个实施例中,第三硬掩膜层42可以为旋涂硬硬掩膜层(soh),第四硬掩膜层43可以为电介质层(ox)。以电介质层(ox)作为阻挡层,对旋涂硬硬掩膜层(soh)进行化学蚀刻,从而方便关键尺寸的控制,以得到高精度的第一线条图案331。

92.在一个实施例中,形成第一图案结构包括:在中间掩膜结构40内形成第五图案结构,第五图案结构包括多条沿第一方向延伸的第四线条图案431;利用第五图案结构刻蚀底

部掩膜结构30形成第一图案结构,从而可以使得第四线条图案431与第一线条图案331一一相对应,从而可以通过控制第四线条图案431来获得高精度的第一线条图案331。

93.在一个实施例中,如图11所示,相邻第四线条图案431的高度不相等,而在利用第四线条图案431形成第一线条图案331后可以将第四线条图案431进行去除,从而保留第一线条图案331。

94.需要说明的是,相比于相关技术中利用类似顶部图案化掩膜结构直接在底部掩膜结构上进行形成线条图案,线条图案可能存在高度不平整的问题,而本实施例中由于中间掩膜结构40的存在,形成的是高度不同的第四线条图案431,将第四线条图案431进行去除后可以保证第一线条图案331的平整度。

95.在一个实施例中,多个第一线条图案331的高度均相等,从而可以保证后续形成第三图案化结构36的结构精度。

96.在一个实施例中,顶部图案53包括多条沿第一方向延伸的顶部线条图案,第四线条图案431的周期间距小于或等于顶部线条图案的周期间距。

97.顶部图案53的顶部线条图案的周期间距可以等于第四线条图案431的周期间距,从而可以根据顶部线条图案获得数量与顶部线条图案相一致的第四线条图案431。或者,顶部图案53的顶部线条图案的周期间距可以大于第四线条图案431的周期间距,根据顶部图案53的顶部线条图案后期可以利用sadp工艺、sarp工艺、saqp工艺、saop工艺中的一种或多种获得第四线条图案431。

98.在一个实施例中,第四线条图案431的周期间距等于第一线条图案331的周期间距,即可以根据第四线条图案431直接蚀刻底部掩膜结构30形成第一图案结构。

99.在一个实施例中,在第一掩膜结构60中形成第二图案结构包括,在第一掩膜结构60上形成第六图案结构,第六图案结构包括多条沿第二方向延伸的第五线条图案65;以第六图案结构为掩膜刻蚀第一掩膜结构60,第六图案结构通过第二自对准工艺形成第二图案结构,以此保证在形成第二图案结构的过程中不会出现对准不好的问题,从而提高形成多个第二线条图案663的精度。

100.结合图14和图15所示,第一掩膜结构60包括在底部掩膜结构30上依次形成第一旋涂硬掩膜层61、第八硬掩膜层62、第二旋涂硬掩膜层63、第九硬掩膜层64,第九硬掩膜层64上形成第五线条图案65,第五线条图案65可以为第二光刻胶层,第二光刻胶层具有第二光刻胶开口651,利用第二光刻胶开口651刻蚀第二旋涂硬掩膜层63和第九硬掩膜层64,以形成多个第二开孔66,并在第二开孔66的侧壁形成第二侧壁间隔层661,如图16和图17所示,第二侧壁间隔层661覆盖第八硬掩膜层62。在第二开孔66内形成第二覆盖层662,如图18和图19所示。

101.第一旋涂硬掩膜层61可以为旋涂硬硬掩膜层(soh),第八硬掩膜层62可以为电介质层(ox),第二旋涂硬掩膜层63可以为旋涂硬硬掩膜层(soh),第九硬掩膜层64可以采用氮化硅(sin)、氮氧化硅(sion)、氮碳化硅(sicn)等。第二侧壁间隔层661可以为电介质层(ox),第二覆盖层662可以为旋涂硬硬掩膜层(soh)。

102.在一个实施例中,第二自对准工艺包括sadp工艺、sarp工艺、saqp工艺、saop工艺中的一种或多种,以获得高精度的第二图案结构。

103.需要说明的是,对于上述第二自对准工艺的具体步骤本实施例中不作限定,可以

参考相关技术中的工艺。第一自对准工艺可以与第二自对准工艺相一致,或者,第一自对准工艺可以与第二自对准工艺不相一致。

104.在一个实施例中,第五线条图案65的周期间距大于或等于第二线条图案663的周期间距。

105.第五线条图案65的周期间距可以等于第二线条图案663的周期间距,从而可以以第五线条图案65为掩膜获得数量与第五线条图案65相一致的第二线条图案663。或者,第五线条图案65的周期间距大于第二线条图案663的周期间距,根据第六图案结构利用sadp工艺、sarp工艺、saqp工艺、saop工艺中的一种或多种获得第二线条图案663。

106.利用第二侧壁间隔层661在第一掩膜结构60内形成第二开孔66,从而形成了图20和图21所示的结构,即形成了多个第二线条图案663。根据多个第二线条图案663在底部掩膜结构30上形成与多个第二开口31相交叉的多个第三开口32,以此形成了第三图案化结构36,即多个独立的第三图案化结构36,如图22和图23所示。最后可以利用第二开口31和第三开口32刻蚀导电层20,从而在衬底10上形成多个接触垫结构21,如图24和图25所示。

107.在一个实施例中,第一掩膜结构60包括的膜层数量和第五线条图案65的膜层数量之和与中间掩膜结构40和顶部图案化掩膜结构50包括的膜层数量之和相一致。第一掩膜结构60和第五线条图案65依次形成于底部掩膜结构30上的膜层材料与中间掩膜结构40和顶部图案化掩膜结构50依次形成于底部掩膜结构30上的膜层材料相一致。

108.在一些实施例中,第二开口31和第三开口32均为直线型开口,可以提高制作效率,且可以保证后续形成第三图案化结构36的结构精度。第二开口31和第三开口32之间的夹角可以为锐角。在某些实施例中,不排除第二开口31和第三开口32之间的夹角可以为直角。

109.在一个实施例中,第三图案化结构36包括方形、菱形、平行四边形中的一种或多种。

110.在一个实施例中,第一线条图案331的周期间距等于第二线条图案663的周期间距,以此保证第三图案化结构36的结构精度,从而形成多个高精度的接触垫结构21。

111.本公开的半导体结构的制作方法涉及集成电路以及电子元器件的制造,通过调整半导体结构的制作过程,用来改进制程可调节性和易于监控性,利用改变膜层结构来优化流程,应用于先进dram生产中,使得制程更优化,从而可以获得高精度的半导体结构。

112.本公开的一个实施例还提供了一种半导体结构,包括由上述的半导体结构的制作方法获得的半导体结构。

113.本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本公开旨在涵盖本发明的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和示例实施方式仅被视为示例性的,本公开的真正范围和精神由所附的权利要求指出。

114.应当理解的是,本公开并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本公开的范围仅由所附的权利要求来限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1