静电放电保护GGNMOS结构的制作方法

静电放电保护ggnmos结构

技术领域

1.本技术涉及半导体集成芯片的esd保护电路设计技术领域,具体涉及一种静电放电保护ggnmos结构。

背景技术:

2.随着半导体集成电路的制造工艺的特征尺寸越来越小,芯片单元的尺寸也越来越小,芯片的抗静电能力越来越变得重要。静电放电对ic芯片破坏性的影响更加显著。静电往往会导致半导体组件以及计算机系统等形成一种永久性毁坏,因而影响集成电路的电路功能,而使电子产品工作不正常,所以必须设计一些保护措施或者功能来保护芯片不受静电放电现象的破坏。

3.芯片上的静电放电(electrostatic discharge,esd)保护器件的设计需要考虑两个方面的问题:一是esd保护器件要能够泄放大电流;二是esd保护器件要能在芯片受到esd冲击时将芯片引脚端电压箝制在安全的低电压水平。而基于上述设计考虑,用作esd保护的器件主要有:二极管、ggnmos(gate ground nmos,栅接地的nmos)、gdpmos(栅极接到漏端的pmos)、可控硅整流器(silicon controlled rectifier,scr)等。其中,scr有单向、双向、可关断和光控几种类型,它具有体积小、重量轻、效率高、寿命长、控制方便等优点,被广泛用于可控整流、调压、逆变以及无触点开关等各种自动控制和大功率的电能转换的场合,scr常用作esd保护器件,特别是高压的esd保护应用,scr有面积小、esd能力高的优势。

4.目前,带有p ring(环形p型重掺杂区、位于所述环形p型重掺杂区底部的环形p型阱区)、n ring(环形n型重掺杂区、位于所述环形n型重掺杂区底部的环形p型阱区)的常规的静电放电保护ggnmos器件通常包括:drain(漏极,实际为n型重掺杂区)、n ring、p ring、bulk(体区)、source(源极,实际为n型重掺杂区)、gate(栅极)、p型阱区和n型阱区等等,其中,source,drain(漏极,实际为n型重掺杂区)、n ring短接形成anode(阳极)端,p ring、bulk(体区)、source(源极,实际为n型重掺杂区)、gate(栅极)短接形成cathode(阴极)端。当esd电压加到anode端时,由drain、p型阱区、source形成的npn打开,形成主要的esd电流泄放通道,但是这种常规的静电放电保护ggnmos器件的鲁棒性较差,要想达到较高的防护等级需要消耗较大的芯片面积。

技术实现要素:

5.本技术提供了一种静电放电保护ggnmos结构,可以解决常规的静电放电保护ggnmos器件的鲁棒性较差、消耗较大的芯片面积中的至少一个问题。

6.一方面,本技术实施例提供了一种静电放电保护ggnmos结构,包括:衬底、深隔离结构、环形n型阱区、第一p型阱区、第二p型阱区、第一n型重掺杂区、第二n型重掺杂区、第三n型重掺杂区、第一栅氧化层、第二栅氧化层、第一环形p型重掺杂区、第二环形p型重掺杂区、第三环形p型重掺杂区、环形n型重掺杂区和多个浅隔离结构;

7.其中,所述深隔离结构覆盖所述衬底,所述环形n型阱区、所述第一p型阱区和所述

第二p型阱区均位于所述深隔离结构上,所述环形n型阱区包围所述第一p型阱区,所述第二p型阱区包围所述环形n型阱区;

8.所述第一n型重掺杂区、所述第二n型重掺杂区和所述第三n型重掺杂区间隔设置于所述第一p型阱区中且靠近所述第一p型阱区的上表面,所述第一栅氧化层覆盖所述第一n型重掺杂区和所述第二n型重掺杂区之间的所述第一p型阱区的表面,所述第二栅氧化层覆盖所述第二n型重掺杂区和所述第三n型重掺杂区之间的所述第一p型阱区的表面;

9.所述第一环形p型重掺杂区位于所述第一p型阱区中且包围所述第一n型重掺杂区、所述第二n型重掺杂区和所述第三n型重掺杂区,所述第二环形p型重掺杂区位于所述环形n型阱区中且包围所述第一环形p型重掺杂区,所述环形n型重掺杂区位于所述环形n型阱区中且包围所述第二环形p型重掺杂区,所述第三环形p型重掺杂区位于所述第二p型阱区中且包围所述环形n型重掺杂区;

10.所述第一环形p型重掺杂区与所述第一n型重掺杂区、所述第三n型重掺杂区之间、所述第一环形p型重掺杂区与所述第二环形p型重掺杂区之间以及所述环形n型重掺杂区与所述第三环形p型重掺杂区之间均设置一所述浅隔离结构;

11.其中,所述第二n型重掺杂区、所述第二环形p型重掺杂区和所述环形n型重掺杂区均连接至外部电源的阳极;所述第一n型重掺杂区、所述第三n型重掺杂区、所述第一栅氧化层、所述第二栅氧化层、所述第一环形p型重掺杂区和所述第三环形p型重掺杂区均连接至外部电源的阴极。

12.可选的,在所述的静电放电保护ggnmos结构中,在所述环形n型阱区中,所述环形n型重掺杂区和所述第二环形p型重掺杂区直接横向接触。

13.可选的,在所述的静电放电保护ggnmos结构中,在所述环形n型阱区中,所述环形n型重掺杂区和所述第二环形p型重掺杂区之间具有一定的间隔。

14.可选的,在所述的静电放电保护ggnmos结构中,所述环形n型重掺杂区和所述第二环形p型重掺杂区之间的间隔中设置一所述浅隔离结构以对所述环形n型重掺杂区和所述第二环形p型重掺杂区进行隔离。

15.可选的,在所述的静电放电保护ggnmos结构中,所述静电放电保护ggnmos结构还包括:环形阻挡层,所述环形阻挡层覆盖所述环形n型重掺杂区和所述第二环形p型重掺杂区之间的所述环形n型阱区的表面。

16.可选的,在所述的静电放电保护ggnmos结构中,所述深隔离结构包括:深n型阱区,所述深n型阱区位于所述衬底中且靠近所述衬底的上表面,所述环形n型阱区和所述第一p型阱区均位于所述深n型阱区上,所述第二p型阱区位于所述衬底上。

17.可选的,在所述的静电放电保护ggnmos结构中,所述深隔离结构包括:n型埋层、环形p型埋层和外延层,其中,所述n型埋层和所述环形p型埋层均位于所述衬底上,所述环形p型埋层包围所述n型埋层,所述外延层覆盖所述n型埋层的部分表面,所述第一p型阱区覆盖所述外延层,所述环形n型阱区覆盖所述n型埋层的剩余表面,所述第二p型阱区覆盖所述环形p型埋层。

18.可选的,在所述的静电放电保护ggnmos结构中,所述外延层的导电类型为p型或者n型。

19.可选的,在所述的静电放电保护ggnmos结构中,所述衬底的导电类型为p型。

20.可选的,在所述的静电放电保护ggnmos结构中,所述静电放电保护ggnmos结构还包括:第一阻挡隔离层和第二阻挡隔离层,所述第一阻挡隔离层覆盖所述第二n型重掺杂区和所述第一栅氧化层之间的第一p型阱区的表面,所述第二阻挡隔离层覆盖所述第二n型重掺杂区和所述第二栅氧化层之间的第一p型阱区的表面。

21.本技术技术方案,至少包括如下优点:

22.(1)本技术通过在所述第一环形p型重掺杂区的外围设置所述第二环形p型重掺杂区,使得所述第二环形p型重掺杂区、所述环形n型阱区、所述第一p型阱区和所述第一n型重掺杂区(pnpn结构)形成一scr泄放电流通道,以及使得所述第二环形p型重掺杂区、所述环形n型阱区、所述第一p型阱区和所述第三n型重掺杂区(pnpn结构)也形成一scr泄放电流通道,从而在ggnmos结构的内部构成两个scr泄放电流通道,从而提高静电放电保护ggnmos结构的鲁棒性。

23.(2)本技术中,利用所述第二环形p型重掺杂区、所述环形n型阱区和所述第一p型阱区分别与所述第一n型重掺杂区、所述第三n型重掺杂区形成scr泄放电流通道,使得本技术提供的静电放电保护ggnmos结构在不占用较大的芯片面积的同时就能达到较高的防护等级,符合集成电路的小尺寸的要求,拓宽了所述静电放电保护ggnmos结构的应用领域。

附图说明

24.为了更清楚地说明本技术具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

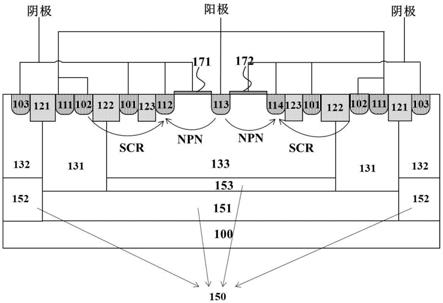

25.图1是本发明实施例一的静电放电保护ggnmos结构的剖视图;

26.图2是本发明实施例一的静电放电保护ggnmos结构的俯视图;

27.图3是本发明实施例二的静电放电保护ggnmos结构的剖视图;

28.图4是本发明实施例三的静电放电保护ggnmos结构的剖视图;

29.图5是本发明实施例三的静电放电保护ggnmos结构的俯视图;

30.图6是本发明实施例四的静电放电保护ggnmos结构的剖视图;

31.图7是本发明实施例四的静电放电保护ggnmos结构的俯视图;

32.其中,附图标记说明如下:

33.100-衬底,101-第一环形p型重掺杂区,102-第二环形p型重掺杂区,103-第三环形p型重掺杂区,111-环形n型重掺杂区,112-第一n型重掺杂区,113-第二n型重掺杂区,114-第三n型重掺杂区,121-浅隔离结构,122-浅隔离结构,123-浅隔离结构,124-浅隔离结构,131-环形n型阱区,132-第二p型阱区,133-第一p型阱区,241-深n型阱区,150-深隔离结构,151-n型埋层,152-环形p型埋层,153-外延层,171第一栅氧化层,172-第二栅氧化层,181-环形阻挡层。

具体实施方式

34.下面将结合附图,对本技术中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本技术的一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普

通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本技术保护的范围。

35.在本技术的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

36.在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电气连接;可以是直接相连,也可以通过中间媒介间接相连,还可以是两个元件内部的连通,可以是无线连接,也可以是有线连接。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本技术中的具体含义。

37.此外,下面所描述的本技术不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

38.实施例一

39.本技术实施例提供了一种静电放电保护ggnmos结构,请参考图1和图2,图1是本发明实施例一的静电放电保护ggnmos结构的剖视图,图2是本发明实施例一的静电放电保护ggnmos结构的俯视图。所述静电放电保护ggnmos结构包括:衬底100、深隔离结构150、环形n型阱区131、第一p型阱区133、第二p型阱区132、第一n型重掺杂区112、第二n型重掺杂区113、第三n型重掺杂区114、第一栅氧化层171、第二栅氧化层172、第一环形p型重掺杂区101、第二环形p型重掺杂区102、第三环形p型重掺杂区103、环形n型重掺杂区111和多个浅隔离结构121/122/123。

40.其中,所述深隔离结构150覆盖所述衬底100,所述环形n型阱区131、所述第一p型阱区133和所述第二p型阱区132均位于所述深隔离结构150上,所述环形n型阱区131包围所述第一p型阱区133,所述第二p型阱区132包围所述环形n型阱区131。

41.进一步的,所述第一n型重掺杂区112、所述第二n型重掺杂区113和所述第三n型重掺杂区114间隔设置于所述第一p型阱区133中且所述第一n型重掺杂区112的上表面、所述第二n型重掺杂区113的上表面和所述第三n型重掺杂区114的上表面均与所述第一p型阱区133的上表面齐平,所述第一栅氧化层171覆盖所述第一n型重掺杂区112和所述第二n型重掺杂区113之间的所述第一p型阱区133的表面,所述第二栅氧化层172覆盖所述第二n型重掺杂区113和所述第三n型重掺杂区114之间的所述第一p型阱区133的表面。

42.其中,所述第一环形p型重掺杂区101位于所述第一p型阱区133中且所述第一环形p型重掺杂区101的上表面与所述第一p型阱区133的上表面齐平,并且所述第一环形p型重掺杂区101包围所述第一n型重掺杂区112、所述第二n型重掺杂区113和所述第三n型重掺杂区114;所述第二环形p型重掺杂区102位于所述环形n型阱区131中且所述第二环形p型重掺杂区102的上表面与所述环形n型阱区131的上表面齐平,并且所述第二环形p型重掺杂区102包围所述第一环形p型重掺杂区101;所述环形n型重掺杂区111位于所述环形n型阱区131中且所述环形n型重掺杂区111的上表面与所述环形n型阱区131的上表面齐平,并且所述环形n型重掺杂区111包围所述第二环形p型重掺杂区102;所述第三环形p型重掺杂区103

位于所述第二p型阱区132中且所述第三环形p型重掺杂区103的上表面与所述第二p型阱区132的上表面齐平,并且所述第三环形p型重掺杂区103包围所述环形n型重掺杂区111。

43.进一步的,所述第一环形p型重掺杂区101与所述第一n型重掺杂区112、所述第三n型重掺杂区114之间设置一所述浅隔离结构123;所述第一环形p型重掺杂区101与所述第二环形p型重掺杂区102之间设置一所述浅隔离结构122;以及所述环形n型重掺杂区111与所述第三环形p型重掺杂区103之间也设置一所述浅隔离结构121。

44.其中,所述第二n型重掺杂区113、所述第二环形p型重掺杂区102和所述环形n型重掺杂区111均连接至外部电源的阳极;所述第一n型重掺杂区112、所述第三n型重掺杂区114、所述第一栅氧化层171、所述第二栅氧化层172、所述第一环形p型重掺杂区101和所述第三环形p型重掺杂区103均连接至外部电源的阴极。

45.在本实施例中,在所述环形n型阱区131中,所述环形n型重掺杂区111和所述第二环形p型重掺杂区102直接横向接触。

46.优选的,所述衬底100的导电类型为p型。

47.较佳的,所述静电放电保护ggnmos结构还可以包括:第一阻挡隔离层和第二阻挡隔离层(未图示),所述第一阻挡隔离层覆盖所述第二n型重掺杂区113和所述第一栅氧化层171之间的第一p型阱区133的表面,所述第二阻挡隔离层覆盖所述第二n型重掺杂区113和所述第二栅氧化层172之间的第一p型阱区133的表面。

48.进一步的,所述深隔离结构150可以包括:n型埋层151、环形p型埋层152和外延层153,其中,所述n型埋层151和所述环形p型埋层152均位于所述衬底100上,所述环形p型埋层152包围所述n型埋层151,所述外延层153覆盖所述n型埋层151的部分表面,所述第一p型阱区133覆盖所述外延层153,所述环形n型阱区131覆盖所述n型埋层151的剩余表面,所述第二p型阱区132覆盖所述环形p型埋层152。其中,所述外延层153的导电类型可以为p型,也可以为n型。

49.在实施例一中,所述第一n型重掺杂区112、所述第一p型阱区133和所述第二n型重掺杂区113构成npn三极管,所述第三n型重掺杂区114、所述第一p型阱区133和所述第二n型重掺杂区113构成npn三极管。所述第二环形p型重掺杂区102、所述环形n型阱区131、所述第一p型阱区133和所述第一n型重掺杂区112(pnpn结构)形成一scr泄放电流通道,所述第二环形p型重掺杂区102、所述环形n型阱区131、所述第一p型阱区133和所述第三n型重掺杂区114(pnpn结构)也形成一scr泄放电流通道。本技术通过在所述第一环形p型重掺杂区101的外围设置所述第二环形p型重掺杂区102,使得ggnmos结构的内部构成两个scr泄放电流通道,提高了静电放电保护ggnmos结构的鲁棒性。

50.进一步的,本技术中,利用所述第二环形p型重掺杂区、所述环形n型阱区和所述第一p型阱区分别与所述第一n型重掺杂区、所述第三n型重掺杂区形成scr泄放电流通道,使得本技术提供的静电放电保护ggnmos结构在不占用较大的芯片面积的同时就能达到较高的防护等级,符合集成电路的小尺寸的要求,拓宽了所述静电放电保护ggnmos结构的应用领域。

51.实施例二

52.请参考图3,图3是本发明实施例二的静电放电保护ggnmos结构的剖视图,在实施例二中,所述深隔离结构150可以为深n型阱区241,所述深n型阱区241位于所述衬底100中

且靠近所述衬底100的上表面,所述环形n型阱区131和所述第一p型阱区133均位于所述深n型阱区241上,所述第二p型阱区132位于所述衬底100上。

53.实施例三

54.请参考图4和图5,图4是本发明实施例三的静电放电保护ggnmos结构的剖视图,图5是本发明实施例三的静电放电保护ggnmos结构的俯视图,在所述环形n型阱区131中,所述环形n型重掺杂区111和所述第二环形p型重掺杂区102之间具有一定的间隔。

55.在实施例三中,所述环形n型重掺杂区111和所述第二环形p型重掺杂区102之间的间隔中设置一所述浅隔离结构124以对所述环形n型重掺杂区111和所述第二环形p型重掺杂区102进行隔离。

56.实施例四

57.请参考图6和图7,图6是本发明实施例四的静电放电保护ggnmos结构的剖视图,图7是本发明实施例四的静电放电保护ggnmos结构的俯视图,在所述环形n型阱区131中,所述环形n型重掺杂区111和所述第二环形p型重掺杂区102之间具有一定的间隔。

58.在实施例四中,所述静电放电保护ggnmos结构还包括:环形阻挡层181,所述环形阻挡层181覆盖所述环形n型重掺杂区111和所述第二环形p型重掺杂区102之间的所述环形n型阱区131的表面,所述环形阻挡层181能够对所述环形n型重掺杂区111和所述第二环形p型重掺杂区102起到隔离的作用。

59.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

60.需要说明的是,本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可,此外,各个实施例之间不同的部分也可互相组合使用,本发明对此不作限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1