半导体装置的制造方法与流程

1.本发明实施例是有关于半导体装置的制造方法,特别是有关于三维存储 器装置的制造方法。

背景技术:

2.半导体存储器被使用于电子装置的集成电路之中,一些范例包含收音 机、电视、移动电话、个人计算机装置。半导体存储器包含两种主要类别。 一个类别是易失性存储器,而另一类别为非易失性存储器。易失性存储器包 含随机存取存储器(random access memory:ram),其可以更进一步分为两个 子类别,静态随机存取存储器(static random access memory:sram)以及动态 随机存取存储器(dynamic random access memory:dram)。静态随机存取存 储器以及动态随机存取存储器两者为易失性的,因为当其没有接收电源时, 其所存储的数据就会遗失。

3.而在另一方面,非易失性存储器可以保留存储于非易失性存储器上的数 据。非易失性存储器的一种为铁电随机存取存储器(ferroelectric random accessmemory:feram或者fram)。铁电随机存取存储器的优点为其快速的写入 /读取速率以及小尺寸。

技术实现要素:

4.本发明实施例提供一种半导体装置的制造方法,包含在多层堆叠中蚀刻 第一沟槽以及第二沟槽,多层堆叠包含交替的介电层以及牺牲层;通过以导 电材料取代牺牲层以形成字元线;在第一沟槽中形成第一晶体管,第一晶体 管包含第一通道隔离结构;以及在第二沟槽中形成相邻于第一通道切割插塞 的第二晶体管,其中第一通道切割插塞沿着线段覆盖第一通道隔离结构,此 线段平行于第一通道切割插塞的中线。

5.本发明实施例亦提供另一种半导体装置的制造方法,包含形成第一介电 材料以及牺牲材料的交替堆叠;在第一介电材料以及牺牲材料的交替堆叠中 蚀刻第一沟槽以及第二沟槽;在第一沟槽以及第二沟槽之间形成第一字元 线;沿着第一沟槽以及第二沟槽的侧壁沉积电荷捕捉材料;沉积相邻于电荷 捕捉材料的通道材料;在第一沟槽中形成第一隔离结构;沿着该第二沟槽的 侧壁移除该通道材料的部分以及该电荷捕捉材料的部分;以及在第二沟槽中 形成第一通道切割结构,且第一通道切割结构相邻于第一字元线,第一通道 切割结构的中线对准第一隔离结构的中线。

6.本发明实施例提供一种半导体装置,包含第一存储器单元,包含:第一 电荷捕捉条(charge trapping strip),从基板向外延伸;第一通道层,相邻于第 一电荷捕捉条的第一侧;以及第一通道隔离结构,与第一通道层在相对于第 一电荷捕捉条的一侧上邻接;第二存储器单元,包含:第二电荷捕捉条,从 基板向外延伸;以及第二通道层,相邻于第二电荷捕捉条的第一侧;第一字 元线,设置于第一电荷捕捉条的第二侧以及第二电荷捕捉条的第二侧之间, 并且与第一电荷捕捉条的第二侧以及第二电荷捕捉条的第二侧电性耦接;以 及第一通道切割结构,相邻于第二存储器单元,其中第一通道切割结构的第 一部分在第一

方向对准第一通道隔离结构的第二部分,第一方向平行于第一 通道切割结构的侧壁。

附图说明

7.本公开的各项层面在以下的实施方式搭配附带的图示一同阅读会有最 好的理解。需要强调的是,依据产业的标准惯例,许多特征并没有按比例描 绘。事实上,为了讨论的清晰度,许多特征的尺寸可为任意的增加或缩减。

8.图1a、图1b、图2a、图2b、图3a、图3b、图4a、图4b、图5a、 图5b、图6a、图6b、图7a、图7b、图8a、图8b、图9a、图9b、图10a、 图10b、图10c、图11a、图11b、图11c、图12a、图12b、图13a、图 13b、图13c、图14a、图14b、图15a、图15b、图15c、图15d为根据 一些实施例制造一存储器阵列的中间阶段的一些图示。

9.图16a至图16c描绘在图15a至图15d中所示的中间结构之上的一位 元线互连结构的构造以及在中间结构之下的一源极线互连结构的构造的一 些图示。

10.图17为根据一些实施例中该存储器阵列的一电路图。

11.图18为根据一些实施例中一随机存取存储器的一方框图。

12.图19a至图19c为根据一些实施例中一存储器阵列的一些图示。

13.图20a以及图20b为根据一些实施例中一存储器阵列的俯视图。

14.其中,附图标记说明如下:

15.100:第一存储器阵列

16.101:基板

17.103:多层堆叠

18.103a:第一介电层

19.103b:第二介电层

20.201:第一沟槽

21.301:第一导电特征

22.303:介电间隔物

23.301a:种子层

24.501,wl:字元线

25.601:铁电条

26.601a:铁电条顶部

27.601b:铁电条底部

28.603:半导体条

29.603a:半导体条顶部

30.603b:半导体条底部

31.605:介电条

32.801:第一层间介电质

33.901:源极/漏极开口

34.1001,c:通道隔离结构

35.1101:第二层间介电质

36.1103:通道切割开口

37.1201,cut:通道切割插塞

38.1301:中线

39.1401:导电材料

40.1501,bl:位元线

41.1503,sl:源极线

42.1505:虚线

43.1505a:第一虚线

44.1505b:第二虚线

45.1507:第一存储器单元

46.1509:导电通孔

47.1511:薄膜晶体管

48.1601:第一互连结构

49.1603:第一金属化图案

50.1605:第一介电材料

51.1607:第一导孔

52.1609:第一金属线

53.1611:第二导孔

54.1613:位元线内连结构

55.1615:第二互连结构

56.1617:第二金属化图案

57.1619:第二介电材料

58.1621:第三导孔

59.1623:第三金属线

60.1625:第四导孔

61.1627:源极线内连结构

62.1800:随机存取存储器

63.1801:列解码器

64.1803:行解码器

65.1900:第二存储器阵列

66.1901:通道间隔物

67.1903:第二存储器单元

68.2000:第三存储器阵列

69.2001:区域

70.2003:虚线

71.d:漏极区/位元线

72.d1:第一方向

73.d2:第二方向

74.h1:第一高度

75.s:源极区/源极线

76.s1:分离距离

77.t1:第一厚度

78.t2:第二厚度

79.t3:第三厚度

80.l1:第一长度

81.l2:第二长度

82.l3:第三长度

83.l4:第四长度

84.l6:第六长度

85.l7:第七长度

86.w1:宽度

具体实施方式

87.以下公开内容提供了用于实施所提供标的的不同特征的许多不同实施 例或实例。以下描述了部件以及布置等的特定实例以简化本公开内容。当然, 所述仅仅是实例,而并不旨在为限制性的。例如,在以下描述中在第二特征 上方或之上形成第一特征可以包括第一特征和第二特征形成为直接接触的 实施例,并且亦可以包括可以在第一特征与第二特征之间形成额外特征,使 得第一特征和第二特征可以不直接接触的实施例。另外,本公开可以在各种 实例中重复参考数字及/或字母。该重复是为了简单和清楚的目的,并且本身 并不代表所论述的各种实施例及/或配置之间的关系。

88.在空间上相对的用语,例如“之下”,“下部”,“下方”,“上方”,

ꢀ“

之上”等,如图式所描绘,可用以使本公开更容易地描述一个特征与另一 特征之间的关系。空间相对术语意在除了涵盖装置在图式所描述的取向,亦 涵盖在操作当中或使用当中的装置的不同取向。设备可以以其他方式取向(旋 转90度或在其他方向上),并且可以类似地相应解释在此使用的空间相对描 述词。

89.图1a至图20b根据一些实施例,为许多存储器阵列的制造中的中间阶 段的一些图示。描绘了许多存储器阵列的部分。一些特征,例如字元线的阶 梯配置,为了描绘的清晰度,并没有在每个图式中展示。图1a、图2a、图 3a、图4a、图5a、图6a、图7a、图8a、图9a、图10a、图11a、图12a、 图13a、图14a、图15a、图16b、图19a、以及图20a为许多存储器阵列 的俯视图。图1b、图2b、图3b、图4b、图5b、图6b、图7b、图8b、图 9b、图10b、图11b、图12b、图13b、图14b、图15b、以及图16a为许 多存储器阵列的剖面图。图10c、图11c、图13c、图15c、图16c、图19c、 以及图20b为在俯视图中的一强调区域的放大图。图15d以及图19b为根 据一些实施例中许多存储器阵列的三维图。图17为根据一些实施例中第一 存储器阵列100的电路图。图18为根据一些实施例中存储器阵列的方框图。

90.在图1a以及图1b中,提供基板101以制造一第一存储器阵列100。基 板101可为一半导体基板,例如块状(bulk)半导体、半导体在绝缘体上 (semiconductor on insulator;soi)基板,或者类似的半导体,且可受掺杂(例 如,以p型或者n行掺杂物),或者没受掺杂。基板101可为一晶圆,例如一 硅晶圆。一般而言,半导体在绝缘体上(soi)基板为形成在一绝缘层上的半导 体材料层。举例而言,绝缘层可为埋入氧化层(buried oxide(box)

end of line)直接于基板101(例如半导体基板)上形成,但这仅是描述 性而非意旨对实施例有所限制。相反地,第一存储器阵列100亦可在前段制 程或者是后段制程(back end of line)的其中之一之中形成,且可形成为嵌入式 存储器阵列或者是单独结构。第一存储器阵列100的任何合适的形成方法皆 可以使用,且所有的形成方法都完全意旨为涵盖于实施例的范围内。

95.图2a至图15d(图2a、图2b、图3a、图3b、图4a、图4b、图5a、 图5b、图6a、图6b、图7a、图7b、图8a、图8b、图9a、图9b、图10a、 图10b、图11a、图11b、图12a、图12b、图13a、图13b、图14a、图 14b、图15a、图15b、图15c、图15d)描绘一个制程,其中在多层堆叠103 中图案化以形成沟槽,并在在沟槽内形成薄膜晶体管(tfts),如以下的详细 内容所述。在一些实施例中,使用单一图案化制程以形成薄膜晶体管。然而, 亦可使用双重图案化制程。例如,多重图案化制程可为双重图案化制程、四 重图案化制程、或者类似的制程。图2a至图15d描绘一单一图案化制程。 在单一图案化制程中,是以第一蚀刻制程在多层堆叠103中图案化出第一沟 槽201(参见图2a以及图2b),而薄膜晶体管的部件是形成在第一沟槽201 中。

96.特别而言,图2a以及图2b描绘在多层堆叠103中形成的第一沟槽201。 在所绘的实施例中,第一沟槽201延伸穿过多层堆叠103并且曝露出基板 101。在另一实施例中,第一沟槽201延伸穿过多层堆叠103的一些层,但 不是所有的层。形成第一沟槽201的操作可利用合适的微影技术以及蚀刻技 术,例如对多层堆叠103有选择性的蚀刻制程(例如,对第一介电层103a以 及第二介电层103b的介电材料的蚀刻速率比对基板101的材料的蚀刻速率 更快)。此蚀刻可为任何合适的蚀刻制程,例如反应式离子蚀刻(reactive ionetch;rie)、中性粒子束蚀刻(neutral beam etch;nbe)、类似的蚀刻制程、或 者前述的组合。蚀刻可为非等向性的(anisotropic)。在基板101为碳化硅 (silicon carbide)所形成的实施例中,第一介电层103a是以氧化硅(silicon oxide)所形成,以及第二介电层103b是以氮化硅(silicon nitride)所形成,第 一沟槽201可由利用氟(fluorine)基气体(例如六氟丁二烯;c4f6)混合氢气(h2) 或者氧气(o2)的干蚀刻所形成。

97.多层堆叠103的一部分设置在每一对第一沟槽201之间。多层堆叠103 的每一部分可具有在大约50纳米至大约500纳米的范围之内的一宽度 w1(例如大约240纳米),以及具有图1a以及图1b所述的第一高度h1。进 一步而言,多层堆叠103的每一部分由一分离距离s1所隔开,分离距离s1 可在大约50纳米至大约200纳米(例如大约80纳米)的范围之内。多层堆叠 103的每一部分的高宽比(aspect ratio;ar)为多层堆叠103的此一部分的第 一高度h1对其最窄特征的宽度的比值,此宽度在这个制程操作中为宽度 w1。根据一些实施例,当形成第一沟槽201时,多层堆叠103的每一部分 的高宽比在大约5至大约15的范围内。形成高宽比大于大约5的多层堆叠 103的每一部分使得第一存储器阵列100可具有足够的存储器单元密度。形 成高宽比小于大约15的多层堆叠103的每一部分可帮助多层堆叠103在后 续的制程中避免扭转或者崩塌。

98.图3a以及图3b是根据一些实施例,描绘在第一沟槽201中形成第一导 电特征301以及介电间隔物303。形成第一导电特征301可在一开始先扩张 第一沟槽201。具体而言,由第一沟槽201所曝露的第二介电层103b的侧 壁的部分被移除或者凹陷(recessed)。此移除可由合适的蚀刻制程所形成,例 如选择性地蚀刻第二介电层103b的材料的蚀刻制程(例如,选择性蚀刻第二 介电层103b的材料的速率大于选择性蚀刻第一介电层103a以及基板

101的材料的速率)而仰赖在图式中没有分开描绘的结构来支撑多层堆叠103的剩余部分。此蚀刻可以为等向性的。在基板101是由碳化硅所形成的实施例中,第一介电层103a可由氧化硅所形成,而第二介电层103b可由氮化硅所形成。可由利用磷酸(phosphoricacid;h3po4)的湿蚀刻进行移除。然而,任何合适的蚀刻制程,例如干选择性蚀刻,亦可以被利用。

99.一旦该部分被移除后,形成第一导电特征301以填充第一沟槽201及/或将第一沟槽201过量填充。每一个第一导电特征301可包含一个或者多个层,例如种子层(seedlayer)、粘着层、阻障层、扩散层、以及填充层、以及类似的层。在一些实施例中,每一个第一导电特征301包含种子层301a(或者粘着层)以及主层301b,虽然在其他实施例中,可以省略种子层301a。种子层301a由一第一导电材料所形成,此第一导电材料可被用以帮助后续沉积的材料的成长或者附着,且第一导电材料可为氮化钛(titaniumnitride)、氮化钽(tantalumnitride)、钛(titanium)、钽(tantalum)、钼(molybdenum)、钌(ruthenium)、铑(rhodium)、铪(hafnium)、铱(iridium)、铌(niobium)、铼(rhenium)、钨(tungsten)、前述的组合、前述的氧化物、或者类似的材料。主层301b可由第二导电材料所形成,例如金属,例如钨、钴(cobalt)、铝(aluminum)、镍(nickel)、铜(copper)、银(silver)、金(gold)、钼、钌、氮化钼(molybdenumnitride)、前述的合金、或者类似的金属。种子层301a的材料为一种与第一介电层103a的材料有良好的附着力(adhesion)的材料,而主层301b材料为一种与种子层301a的材料有良好的附着力的材料。在第一介电层103a的材料为例如氧化硅的氧化物所形成的实施例中,种子层301a可由氮化钛所形成,而主层301b可由钨所形成。种子层301a以及主层301b可各别由一合适的沉积制程所形成,例如化学气相沉积、原子层沉积、或者类似的制程以局部或者完全填充第一沟槽201。

100.在主层301b并不完全填充第一沟槽201的实施例中,一旦在第一沟槽201沉积主层301b之后,以介电材料形成介电间隔物303,并且沉积介电间隔物303以填充第一沟槽201的剩余空间及/或将第一沟槽201的剩余空间过量填充。合适的介电材料包含氧化物(例如氧化硅、氧化铝(aluminumoxide))、氮化物(例如氮化硅;碳化物,例如碳化硅)、类似的材料或者前述的组合(例如氮氧化硅、碳氧化硅、碳氮化硅、或者类似的材料)。介电间隔物303的材料可由合适的沉积制程所形成,例如原子层沉积、化学气相沉积、可流动的化学气相沉积(flowablecvd;fcvd)、或者类似的制程。介电间隔物303的材料亦可对第一介电层103a的第一介电材料具有高蚀刻选择性。在第一介电层103a由例如氧化硅的氧化物所形成的实施例中,介电间隔物303的材料可由例如氮化硅的氮化物所形成。亦可使用相互具有合适的高蚀刻选择性的介电材料的其他组合。

101.一旦沉积了介电间隔物303以填充第一沟槽201及/或将第一沟槽201过量填充,可平坦化介电间隔物303以及第一导电特征301以移除在第一沟槽201外的多余材料。在一实施例,可利用例如化学机械研磨(chemicalmechanicalplanarization;cmp)制程来平坦化介电间隔物303以及第一导电特征301。然而,亦可利用任何合适的平坦化制程,例如研磨制程。介电间隔物303提供坚固的结构以及帮助第一导电特征301避免在平坦化当中弯折。介电间隔物303在此亦可被称为隔离层或者牺牲层(虚置层)。

102.图4a以及图4b描绘介电间隔物303从第一沟槽201被移除。在介电间隔物303由例如氮化硅的氮化物所形成,而第一介电层103a由例如氧化硅的氧化物所形成的实施例中,

介电间隔物303可由利用磷酸的湿蚀刻所移除。然而任何合适的蚀刻制程,例如干选择性蚀刻,亦可以被用以移除介电间隔物303的材料。

103.除此之外,虽然在上面描绘单一图案化制程以形成第一导电特征301,亦可利用多重图案化制程,并且全部的如前述的图案化制程皆在实施例的范围之内。例如,亦可使用多重图案化制程,并且在此实施例中,一旦以第一蚀刻制程在多层堆叠103中图案化出第一沟槽201,就于第一沟槽201中形成第一导电特征301的第一子集的部件。接着,利用第二蚀刻制程在第一导电特征301的第一子集之间的多层堆叠103中图案化出第二沟槽,并且在第二沟槽中形成一导电特征301的第二子集。以多重图案化制程形成第一导电特征301允许以低图案密度执行每一个图案化制程,其可帮助减少缺陷而仍允许第一存储器阵列100具有足够的存储器单元密度,且亦帮助避免高宽比变得过高以及避免造成结构不稳定性的问题。

104.图5a以及图5b描绘在形成字元线501的过程中通过移除第一导电特征301的多余部分以及曝露第一介电层103a的回蚀制程。在一实施例中,可利用例如非等向性蚀刻制程执行回蚀制程。然而,可利用任何合适的蚀刻制程。

105.在一实施例中,执行回蚀制程直到第一导电特征301中未被第一介电层103a所覆盖的材料被移除。因此,第一导电特征301的剩余材料与第一介电层103a的剩余部分具有相似的宽度(例如80纳米)。然而,可利用任何合适的尺寸。

106.图6a以及图6b描绘在第一沟槽201中形成薄膜晶体管薄膜堆叠。具体而言,在每一个第一沟槽201中形成一个或者两个铁电条(ferroelectricstrips)601、一半导体条(semiconductorstrip)603、以及介电条(dielectricstrip)605。在本实施例中,在第一沟槽201中没有形成其他层。

107.铁电条601为数据存储层,其可由施加横跨铁电条601的合适的电压差在一个或者两个不同方向极化。依据铁电条601的一特定区域的极化方向,相应的薄膜晶体管1511(在图6a至图6b中未图示,但后续将分别在图15a至图15d更进一步作描绘以及叙述)的临界电压会变动且可以存储一数字数值(例如0或者1)。例如,当铁电条601的一区域具有第一电性极化方向,相应的薄膜晶体管1511可具有相对低的临界电压,且当铁电条601的该区域具有第二电性极化方向,相应的薄膜晶体管1511可具有相对高的临界电压。两个临界电压之间的差异可被称为临界电压偏移。一个较大的临界电压偏移可以使得读取所存储的数字数值更为容易(例如,更不容易出错)。

108.铁电条601可由合适的铁电材料或者其他电荷捕捉材料所形成以存储数字数值,例如锆酸铪(hafniumzirconiumoxide;hfzro)、氧化铪铝(hafniumaluminumoxide;hfalo)、氧化锆(zirconiumoxide;zro)、掺杂镧(lanthanum;la)、硅、铝、或者类似的材料的氧化铪(hafniumoxide;hfo);未经掺杂的氧化铪;或者类似的材料。铁电条601的材料可由合适的沉积制程例如原子层沉积、化学气相沉积、物理气相沉积(physicalvapordeposition;pvd)、或者类似的沉积制程所形成。铁电条601或者其他电荷捕捉材料亦可在此称为数据存储条、数据存储材料、电荷捕捉材料、电荷捕捉条、存储器材料、及/或存储器条。

109.半导体条603为薄膜晶体管1511(在图6a至图6b中未图示,但后续将分别在图15a至图15d更进一步作描绘以及叙述)提供通道区。例如,当通过对应的字元线501进行施加

一合适的电压(例如,高于相应的薄膜晶体管 1511的各自临界电压(v

th

))时,半导体条603中相交于字元线501的区域可 允许电流从位元线1501流至源极线1503(在图6a至图6b中未图示,但后 续将分别在图15a至图15d更进一步作描绘以及叙述)。

110.在一实施例中,半导体条603由合适的半导体材料所形成,以提供薄膜 晶体管的通道区,例如氧化锌(zinc oxide;zno)、氧化钨铟(indium tungstenoxide;inwo)、氧化锌镓铟(indium gallium zinc oxide;ingazno)、氧化锌铟 (indium zinc oxide;inzno)、氧化锡铟(indium tin oxide;ito)、氧化锡锌镓 铟(indium gallium zinc tin oxide;igzto)、多晶硅、非晶硅、或者类似的材 料。半导体条603的材料可由合适的沉积制程例如原子层沉积、化学气相沉 积、物理气相沉积、或者类似的沉积制程所形成。半导体条603在此亦可称 为半导体材料条、通道材料条、通道层、及/或通道材料。

111.介电条605由介电材料所形成。合适的介电材料包含氧化物(例如氧化硅 以及氧化铝)、氮化物(例如氮化硅)、碳化物(例如碳化硅)、类似的材料或者 前述的组合(例如氮氧化硅、碳氧化硅、碳氮化硅、或者类似的材料)。介电 条605的材料可由合适的沉积制程所形成,例如原子层沉积、化学气相沉积、 可流动的化学气相沉积(fcvd)、或者类似的制程。

112.图7a以及图7b是根据一些实施例,描绘沿着介电层以及半导体层的水 平部分进行非等向性蚀刻移除介电层以及半导体层,因而曝露沿着在第一沟 槽201的底部的铁电条601的水平部分。在第一沟槽201剩余的铁电条层、 半导体层、以及介电层的部分分别形成铁电条601、半导体条603、以及介 电条605。

113.图8a以及图8b根据一些实施例,描绘沉积第一层间介电质801,以填 充第一沟槽201及/或将第一沟槽201过量填充。可利用适合形成介电条605 的任何材料来形成第一层间介电质801。介电条605以及第一层间介电质801 之间的界面以虚线代表。虽然界面在所绘的实施例中展示,根据介电条605 以及第一层间介电质801的材料,介电条605以及第一层间介电质801之间 可能存在界面,也可能不存在界面。在一些实施例中,在例如可流动的化学 气相沉积的制程中利用二氧化硅填充材料来形成第一层间介电质801。然而, 可以使用任何合适的介电材料以及沉积制程。一旦沉积第一层间介电质801 完成了,可利用例如化学机械研磨的制程来平坦化第一层间介电质801。

114.图9a以及图9b描绘通过第一层间介电质801形成源极/漏极开口901, 以及曝露位在源极/漏极开口901底部的铁电条601以及半导体条603。源极 /漏极开口901进一步延伸通过第一介电层103a以及第二介电层103b的任 何剩余部分。可利用合适的微影技术以及蚀刻技术来形成源极/漏极开口901。 源极/漏极开口901设置在将形成薄膜晶体管的源极/漏极区的位置上。例如, 可以成对的方式形成源极/漏极开口901,在对应的漏极区(例如标记“d”) 之中以及对应的源极区(例如标记“s”)之中曝露每一个半导体条603。

115.图10a至图10c是根据一些实施例,描绘通道隔离结构1001的拉回(pullback)制程与形成。可利用合适的微影技术以及蚀刻技术来执行拉回制程 以移除第一层间介电质801的材料。因此,在一些实施例中,第一层间介电 质801的剩余部分形成通道隔离结构1001。通道隔离结构1001是形成在将 形成的薄膜晶体管的通道区的位置上。因此,通道隔离结构1001(例如在图 10a中所标注的“c”)可形成于沿着第一沟槽201的侧壁设置的半导体条603 之间且相应的漏极区以及相应的源极区(在图9a所示)之间的位置上。在一些 实施例中,通道隔离结构1001具有在大约20纳米至大约1000纳米之间的 一第二长度l2。然而,可以使用

任何合适的长度。第二长度l2在此可称为 所形成的装置的栅极长度。栅极长度可取决于所形成的装置所期望的目的及 /或功能。

116.图10a至图10c是根据一些实施例,进一步描绘拉回制程在与第一介电 层103a的最顶层的共面表面中,重新曝露出半导体条603的顶部(例如,标 注为半导体条顶部603a)以及铁电条601的顶部(例如,标注为铁电条顶部 601a)。除此之外,在一些实施例中,半导体条603的底部(例如,标注为半 导体条底部603b)以及铁电条601的底部(例如,标注为铁电条底部601b)可 曝露于通道隔离结构1001之间的第一沟槽201的底部。

117.图11a至图11c是根据一些实施例,描绘一第二层间介电质1101以及 通过第二层间介电质1101的通道切割开口1103的形成。可利用适合形成第 一层间介电质801的任何材料来形成第二层间介电质1101。然而,为第二层 间介电质1101所选的材料可具有蚀刻选择性不同于为第一层间介电质801 所选的材料的蚀刻选择性。例如,在使用氧化物材料(例如二氧化硅)作为第 一层间介电质801以及因此作为通道隔离结构1001的实施例中,可在制程 中(例如可流动的化学气相沉积)由氮化物(例如氮化硅填充材料)形成第二层 间介电质1101。第二层间介电质1101可形成在通道隔离结构1001上第二层 间介电质1101并且填充第一沟槽201及/或将第一沟槽201过量填充。然而, 可以利用任何合适的介电材料以及沉积制程。

118.一旦沉积了第二层间介电质1101,可利用制程如化学机械研磨来平坦化 第二层间介电质1101,而通道切割开口1103在此形成。可利用合适的微影 技术以及蚀刻技术以移除第二层间介电质1101的材料,以通过第二层间介 电质1101形成通道切割开口1103的图案。根据一些实施例,通过通道切割 开口1103的图案曝露了铁电条底部601b、半导体条底部603b、以及半导体 条顶部603a。通道切割开口1103设置在将形成的薄膜晶体管之间的位置。

119.图12a以及图12b是根据一些实施例,描绘通道切割插塞(cut channelplug)1201的形成。在一些实施例中,可形成介电填充材料以填充通道切割开 口1103及/或将通道切割开口1103过量填充。可利用适合形成第二层间介电 质1101的任何介电材料来形成介电填充材料。然而,为介电填充材料所选 的材料可具有蚀刻选择性不同于为第二层间介电质1101所选的材料的蚀刻 选择性。例如,在为第二层间介电质1101选择氮化硅的实施例中,可利用 氧化硅在例如可流动的化学气相沉积的制程中形成填充材料。一旦形成了介 电填充材料,利用合适的平坦化制程,例如化学机械研磨、回蚀制程、前述 的组合、或者类似的制程以平坦化介电填充材料以及第二层间介电质1101。 因此,通道切割插塞1201的顶部(例如,在图12a中标注为“cut”)曝露于 第二层间介电质1101的平面表面。通道切割插塞1201在此亦可称为通道切 割结构(cut channel structure)。在一些实施例中,通道切割插塞1201具有在 大约20纳米至大约1000纳米之间的第三长度l3(在图12a以及图12b中未 图示,但描绘于图13c中)。根据一些实施例,第三长度l3可大约相同于第 二长度l2。然而,可以使用任何合适的长度。第三长度l3在此可称为两个 相邻装置之间的一隔离空间。隔离空间可取决于所形成的装置所期望的设计 的目的及/或功能。

120.图13a以及图13b是根据一些实施例,描绘第二层间介电质1101的移 除。在一些实施例中,移除制程利用一前驱物,其对第二层间介电质1101 的材料具有选择性,而相对而言对通道隔离结构1001以及通道切割插塞1201 的材料不具选择性。例如,在第二层间介电

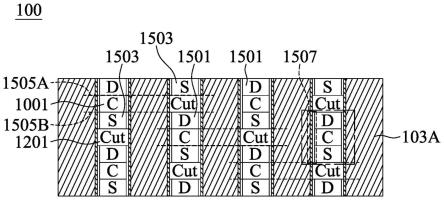

质1101为氮化硅所形成,而通 道隔离结构1001以及通道切割插塞1201为氧化硅所形成的实施例中,可由 利用磷酸的湿蚀刻移除第二层间介电质1101。然而,亦可以利用任何合适的 蚀刻制程,例如干选择性蚀刻。因此,在一些实施例中,通道隔离结构1001 的侧壁以及通道切割插塞1201的侧壁是曝露于第一沟槽201中。

121.图13a以及图13b根据一些实施例,进一步描绘该移除操作,重新曝露 半导体条603的顶部(例如,标注为半导体条顶部603a)以及铁电条601的顶 部(例如,标注为铁电条顶部601a)。除此之外,半导体条603的底部(例如, 标注为半导体条底部603b)以及铁电条601的底部(例如,标注为铁电条底部 601b)在第一沟槽201的底部于对应的漏极区(例如标记“d”)以及对应的源 极区(例如标记“s”)的位置亦重新曝露出来。

122.图13a进一步描绘通道隔离结构1001可对准或者覆盖在第一存储器阵 列100中的相邻薄膜晶体管的通道切割插塞1201。例如,在一些实施例中, 根据一些实施例,通道隔离结构1001可对准在第一存储器阵列100中的相 邻薄膜晶体管的通道切割插塞1201的中线1301。例如,在图13a所绘示的 实施例中,在通道隔离结构1001以及通道切割插塞1201的顶列中,穿过通 道隔离结构1001的主轴的中线1301对准穿过通道切割插塞1201的主轴的 中线1301。在其他实施例中,通道切割插塞1201沿着平行于通道切割插塞 1201的中线的一条线段覆盖通道隔离结构1001,或者通道切割插塞1201的 第一部分在平行于通道切割插塞1201的一侧壁的方向对准通道隔离结构 1001的第二部分。

123.进一步而言,在一些实施例中,通道切割插塞1201的第三长度l3与通 道隔离结构1001的第二长度l2大约相同。在此实施例中,第三长度l3对 第二长度l2的比值可在大约1:1之间。然而,可以利用任何合适的比值。 在一些实施例中,第三长度l3与第二长度l2大约相同以允许相邻的位元线 形成一致的间隔宽度(例如,参见图20a)。在此实施例中,位元线可形成在 将形成第一存储器阵列100中的相邻薄膜晶体管的源极区以及漏极区之上 (例如,参见图20a)。

124.图14a以及图14b是根据一些实施例,描绘一金属的沉积制程。金属的 沉积可为顺应性(conformal)沉积,虽然可利用任何合适的沉积制程。在一些 实施例中,根据一些实施例,金属沉积制程包含一个或者多个导电材料1401, 例如粘着层以及在第一沟槽201中的块状导电材料。合适的导电材料包含金 属(例如钨、钴、铝、镍、图、银、金、前述的合金)、氮化钛、氮化钽、前 述的组合、或者类似的材料。导电材料1401合适的沉积制程所形成,例如 原子层沉积或者化学气相沉积,以及合适的镀膜制程所形成,例如电镀或者 无电子镀膜制程,或者类似的制程。

125.图15a至图15d是根据一些实施例,描绘第一存储器阵列100的形成。 特别而言,图15a至图15d描绘,施加于导电材料1401的许多层上的一平 坦化制程,用以移除第一介电层103a的最顶层上的多余材料。平坦化制程 可为化学机械研磨、回蚀制程、前述的组合、或者类似的制程。剩余的导电 材料形成在第一沟槽201中的位元线1501以及源极线1503。

126.根据一些实施例,一个或者多个位元线1501以及源极线1503延伸穿过 第一介电层103a,并作为薄膜晶体管1511的源极/漏极区。位元线1501以 及源极线1503以成对的导电行(conductive columns)所形成,而每一个半导体 条603接触相应的位元线1501以及相应的源极线1503。每一个薄膜晶体管 1511包含一位元线1501、一源极线1503、一字元线501、以及半导体条603 与铁电条601中交错于字元线501的区域。每一个通道切割插塞1201

设置 在薄膜晶体管1511的位元线1501以及相邻的薄膜晶体管1511的源极线 1503之间。换句话说,一薄膜晶体管1511的位元线1501以及相邻的薄膜晶 体管1511的源极线1503设置在每一个通道切割插塞1201的相反(opposing) 侧上。因此,每一个通道切割插塞1201实体上分开以及电性隔离相邻的薄 膜晶体管1511。

127.图15b根据一些实施例,亦描绘形成穿过基板101的导电通孔1509。 导电通孔1509为了穿过基板101作外部连接,电性耦接了位元线1501及/ 或源极线1503。根据一些实施例,在形成位元线1501以及源极线1503之后 可形成导电通孔1509。在此实施例中,可通过在一开始形成穿过在基板101 的背侧的开口,形成导电通孔1509。在此实施例中,可对基板101执行选择 性(optional)的薄化制程,以在形成开口之前将基板101薄化至一理想的厚度。 开口可在导电通孔1509的理想位置中形成,利用合适的微影技术以及蚀刻 技术以移除基板101的材料以及曝露在开口的底部的铁电条601。一旦铁电 条601曝露出来了,可利用非等向性蚀刻移除铁电条601,并曝露在开口的 底部的位元线1501及/或源极线1503。接着,可在开口形成导电通孔1509 以通过基板101电性耦接位元线1501及/或源极线1503,并接着利用例如化 学机械研磨制程平坦化导电通孔1509。

128.在其他实施例中,可在形成位元线1501及/或源极线1503时形成导电通 孔1509。在此实施例中,可利用非等向性蚀刻以在形成第二层间介电质1101 之前,移除在第一沟槽201底部的铁电条601的水平部分。例如,如上面有 关于图7a以及图7b所述,在非等向性蚀刻当中,可移除在第一沟槽201 底部的铁电条601的水平部分。在另一个范例中,如上面有关于图13a以及 图13b所述,在移除第二层间介电质1101之后的非等向性蚀刻中,可移除 在第一沟槽201底部的铁电条601的水平部分。一旦移除了在第一沟槽201 底部的铁电条601的水平部分,可继续非等向性蚀刻以在基板101中的理想 的导电通孔1509的位置形成开口。在此实施例中,基板101中的开口为在 源极/漏极区中的第一沟槽201的延伸。因此,如上面有关于图14a以及图 14b所述,导电通孔1509是在导电材料1401的金属沉积过程当中,形成在 位元线1501及/或源极线1503的底部部分。

129.在还有其他的实施例中,在基板101上形成多层堆叠103之前,在基板 101中形成导电通孔1509。在此实施例中,可在基板101之中导电通孔1509 的理想位置上形成开口,但是开口不会穿过基板101。一旦在基板101之中 形成开口,可执行金属沉积以在基板101的开口中形成导电通孔1509。如上 所述,可利用任何导电材料1401及/或适合形成位元线1501及/或源极线1503 的制程以形成导电通孔1509。一旦形成后,可利用平坦化制程以移除任何在 开口之外的导电材料1401。因此,导电通孔1509曝露于基板101的平面表 面,而多层堆叠103是形成在所曝露的导电通孔1509以及基板101上。在 此实施例中,如上面有关于图13a以及图13b所述,在移除第二层间介电质 1101之后,移除第一沟槽201底部的铁电条601。一旦移除了铁电条601, 则可曝露在第一沟槽201底部的导电通孔1509。因此,位元线1501及/或源 极线1503形成于导电通孔1509之上,并且电性耦接至导电通孔1509。

130.根据一些实施例,可执行背侧薄化制程以移除基板101的多余材料,以 及曝露在基板101的背侧的导电通孔1509。因此,可曝露导电通孔1509以 对基板101的背侧进行更进一步的制程,并电性连接至下方的电路。

131.更进一步,图15a以及图15c是根据一些实施例,描绘薄膜晶体管1511 的第一存储器单元1507(例如单位单元(unit cell)。除此之外,在某些实施例 中,虚线1505(例如

1505a与1505b)是表示通道隔离结构1001覆盖或者对 准相邻列的薄膜晶体管1511的通道切割插塞1201。例如,在图15a的描绘 的实施例中,第一虚线1505a绘示通道隔离结构1001的第一边缘对准在相 邻的存储器单元中的通道切割插塞1201的第一边缘。图15a进一步描绘第 二虚线1505b,其绘示通道隔离结构1001的第二边缘对准在相邻的存储器 单元中的通道切割插塞1201的第二边缘。因此,薄膜晶体管1511的通道区 与第一存储器阵列100的相邻第一存储器单元1507之间的隔离区相互交错。

132.图16a、图16b、以及图16c是根据一些实施例,描绘分别在第一存储 器阵列100之上形成第一互连结构1601、在第一存储器阵列100之下形成第 二互连结构1615、以及第一存储器阵列100的单一存储器单元的形成。特别 而言,图16a绘示设置于第一存储器阵列100之上的第一互连结构1601与 设置于第一存储器阵列100之下的第二互连结构1615的剖面图。图16b描 绘在图16a中所描绘的结构在第一金属化图案1603的层级的俯视图,第一 金属化图案1603延伸于第一方向d1且字元线501(标记为“wl”)延伸于第 二方向d2。为了绘示的清晰度,位元线1501(标记为“d”),以及源极线1503(标 记为“s”),并且图16c描绘在图16b中所示的第一存储器阵列100的单位 单元。

133.第一互连结构1601可包含在第一介电材料1605中的第一金属化图案 1603。第一介电材料1605可包含一个或者多个介电材料,例如一个或者多 个低介电系数(low-k;lk)或者极低介电系数(extra low-k;elk)介电材料的 层。第一金属化图案1603可为形成于一个或者多个介电层中的金属内连结 构(interconnects)(例如,金属线以及导孔(亦可为导电通孔)。可由镶嵌制程来 形成第一互连结构1601,例如单镶嵌制程、双镶嵌制程,或者类似的制程。

134.在所绘示的一特定实施例中,第一互连结构1601的第一金属化图案1603 包含接触位元线1501的第一导孔1607(例如第一导孔(via0))、第一金属线 1609(例如,第一顶部金属线)、第二导孔1611(例如,第二导孔(via1))、以及 电性耦接至位元线1501的位元线内连结构1613。位元线内连结构1613亦可 在此称为第二金属线或者第二顶部金属线。前述部件的形成方法为沉积第一 介电材料1605的一部份(为了清楚起见而不在图16b以及图16c中分开描 绘)、在第一介电材料1605的一部份中形成图案、以一个或者多个导电材料 填充这些图案、以及平坦化第一介电材料1605与导电材料。然而,可利用 任何合适的导孔以及导电线数量,并且所有此连接层都完全意旨为包含在实 施例的范围内。

135.图16a是根据一些实施例,进一步描绘第二互连结构1615的构造。在 所绘的一特定实施例中,第二互连结构1615的第二金属化图案1617包含接 触源极线1503的第三导孔1621(例如第三导孔(via3))、第三金属线1623(例 如第一底部金属线)、第四导孔1625(例如第四导孔(via4))、以及电性耦接至 源极线1503的源极线内连结构1627。前述部件的形成方法为沉积第二介电 材料1619的一部份(为了清楚起见而不在图16b以及第16c途中分开描绘)、 在第二介电材料1619的一部份中形成图案、以一个或者多个导电材料填充 这些图案、以及平坦化第一介电材料1605与导电材料。然而,可利用任何 合适的导孔以及导电线数量,并且所有此连接层都完全意旨为包含在实施例 的范围内。

136.现在参考图16b,在一些实施例中,虚线1505描绘相邻的第一存储器单 元1507之间的通道切割插塞1201覆盖相邻的第一存储器单元1507的通道 隔离结构1001或者对准相邻的第一存储器单元1507的通道隔离结构1001。 根据一些实施例,通过形成具有第二长度

l2的通道隔离结构1001以及形成 具有第三长度l3的通道切割插塞1201,可以达成前述的对准。如上所述, 第二长度l2对第三长度l3的比值在理想的比值以内。换句话说,通道隔离 结构1001的位置交错相邻的第一存储器单元1507的通道切割插塞1201的 位置。因此,相邻的位元线1501连接至位元线内连结构1613的不同不同位 元线1501,当其共用的字元线501导通(activated)时能帮助避免相邻的位元 线1501短路。相似地,相邻的源极线1503连接至源极线内连结构1627的 不同位元线1501,当其共用的字元线501导通(activated)时能帮助避免相邻 的源极线1503短路。此配置允许在覆盖在上方的第一金属化图案1603之中 有笔直的导电段(例如第一金属线1609)。相似地,此配置允许在位于上方的 第二金属化图案1617之中有笔直的导电段(例如第三金属线1623)。可以看 出,由于下方的连接以交错的形式所形成,可以设置位元线内连结构1613 以及源极线内连结构1627为直线构造而不需要侧向内连结构。此对准大幅 增加位元线内连结构1613以及在金属化层之中的源极线内连结构1627的线 密度。

137.图17为第一存储器阵列100的电路图。在一实施例中,每一个第一存 储器单元1507为包含薄膜晶体管1511的其中之一的快闪存储器单元。每一 个薄膜晶体管1511的栅极电性连接至各自的字元线501,每一个薄膜晶体管 1511的第一源极/漏极区电性连接至各自的位元线1501,以及每一个薄膜晶 体管1511的第二源极/漏极区电性连接至各自的源极线1503(源极线1503电 性连接至接地)。在第一存储器阵列100的相同列之中的第一存储器单元1507 共享共用的字元线501,而在第一存储器阵列100的相同行之中的第一存储 器单元1507共享共用的位元线1501与共用的源极线1503。

138.为了在一特定的第一存储器单元1507中执行写入操作,将写入电压施 加于铁电条601中对应于第一存储器单元1507的一区域。例如,可以对对 应于第一存储器单元1507的字元线501、位元线1501、以及源极线1503施 加合适的电压的做法以施加写入电压。通过将写入电压施加于铁电条601的 该区域,铁电条601的区域的极化方向可以被改变。因此,对应的薄膜晶体 管1511的对应的临界电压可从一低临界电压转变成一高临界电压(或者反之 亦然),使得一数字数值可以存储于第一存储器单元1507中。由于字元线501 以及位元线1501在第一存储器阵列100中相交错,可以选取以及写入个别 的第一存储器单元1507。

139.为了在一特定的第一存储器单元1507中执行读取操作,将读取电压(在 低临界电压以及高临界电压之间的电压)施加于对应于第一存储器单元1507 的字元线501。根据铁电条601的对应区域的极化方向,第一存储器单元1507 的薄膜晶体管1511可能会被开启,或者可能不会被开启。因此,位元线1501 通过源极线1503可能会放电,也可能不会放电(例如放电至接地),使得存储 于第一存储器单元1507的数字数值可被确定。由于字元线501以及位元线 1501在第一存储器阵列100中相交错,可以选取以及读取个别的第一存储器 单元1507。

140.图18为根据一些实施例中的随机存取存储器1800的方框图。随机存取 存储器1800包含第一存储器阵列100、列解码器1801、以及行解码器1803。 第一存储器阵列100、列解码器1801、以及行解码器1803可各别为同一个 半导体晶粒(semiconductor die)的一部分,或者可为不同半导体晶粒的部分。 例如,第一存储器阵列100可为第一半导体晶粒的部分,而列解码器1801、 以及行解码器1803可为第二半导体晶粒的部分。

141.第一存储器阵列100包含第一存储器单元1507、字元线501、以及位元 线1501。第一存储器单元1507配置为列与行。字元线501以及位元线1501 电性连接至第一存储器单元1507。字元线501为沿着第一存储器单元1507 的多个列延伸的导线。位元线1501为沿着第一存储器单元1507的多个行延 伸的导线。

142.例如,列解码器1801可为静态互补式金属氧化物半导体(cmos)解码器、 伪n型金属氧化物半导体(pseudo-nmos)解码器、或者类似的解码器。在 操作中,列解码器1801通过启动一列的字元线501,在第一存储器阵列100 的该列中选取理想的第一存储器单元1507。例如,行解码器1803可为静态 互补式金属氧化物半导体解码器、伪n型金属氧化物半导体解码器、或者 类似的解码器,且可以包含写入驱动器、感测放大器、前述的组合、或者类 似的元件。在操作当中,行解码器1803从在所选的列之中的第一存储器阵 列100的多个行,选取所要的第一存储器单元1507的位元线1501,以及从 有位元线1501的所选的第一存储器单元1507读取数据或者将数据写入有位 元线1501的所选的第一存储器单元1507。

143.图19a至图19c是根据一些其他的实施例,描绘包含第二存储器单元 1903的第二存储器阵列1900。特别而言,图19a描绘第二存储器阵列1900 的俯视图。图19b是根据一些实施例,描绘第二存储器阵列1900的透视图。 图19c是根据一些实施例,描绘第二存储器阵列1900的单位单元(例如,第 二存储器单元1903)的放大图。

144.图19a以及图19c的第二存储器阵列1900相似于在图15a至图15d中 所绘的第一存储器阵列100,除了第二存储器阵列1900包含第二存储器单元 1903,而非第一存储器单元1507。第二存储器单元1903相似于第一存储器 单元1507,除了第二存储器单元1903包含可选用(optional)的通道间隔物 1901。可选用的通道间隔物1901在第一沟槽201中沿着半导体条603的侧 壁形成,并且沿着通道的长度延伸且延伸至薄膜晶体管1511的源极/漏极区。 因此,通道层、源极线以及位元线之间的高介电系数的层间介电层或者介电 物(氧化物)可通过缩小源极线以及位元线之间的面积可减少寄生电容。根据 一些实施例,通道间隔物1901形成为具有第四长度l4,其为大约30纳米以 及大约1500纳米之间。然而,可以利用任何合适的长度。根据一些实施例, 第四长度l4可相等于第二长度l2加上第六长度l6的一半。

145.根据一些实施例,通道间隔物1901是在利用回蚀制程以形成通道隔离 结构1001(描绘于图10a至图10c)之后以及在沉积导电材料1401(描绘于图14a以及图14b)之前形成。通道间隔物1901利用介电膜所形成,例如高介 电系数的介电材料、氧化物材料、前述的组合、或者类似的材料。高介电系 数的介电材料可具有介电系数(k)值大于大约7.0,且可包含金属氧化物或者 铪(hf)、铝(al)、锆(zr)、镧(la)、镁(mg)、钡(ba)、钛(ti)、铅(pb)的硅化物、 前述的多层、或者前述的组合。介电膜可被顺应性地沉积在描绘的结构上, 例如通过等离子体增强化学气相沉积(plasma-enhanced cvd;pecvd)、原子 层沉积(ald)、分子束沉积(molecular-beam deposition;mbd)、或者另一个 沉积技术。在一实施例中,利用高介电系数的介电材料形成通道间隔物1901, 例如在原子层沉积制程中的氧化铪(hfo)。然而,可以利用任何合适的材料 以及制程。因此,介电膜形成于图10a至图10c中所绘的结构的通道隔离结 构1001、半导体条603、及/或铁电条601的曝露表面之上。

146.根据一些实施例,可一开始在第一沟槽201中沉积介电膜,以及在通道 隔离结构1001、半导体条603、及/或铁电条601的曝露表面之上沉积介电膜, 以形成可选的通道间隔

物1901。一旦沉积后,利用合适的微影技术以及蚀刻 技术图案化此介电膜以移除介电膜的材料。因此,根据一些实施例,介电膜 的剩余部分形成可选的通道间隔物1901。

147.在其他实施例中,通过一开始在可选的通道间隔物1901的理想位置形 成在第二层间介电质1101中的开口,来形成可选的通道间隔物1901。一旦 图案化第二层间介电质1101以在理想的位置有开口,介电膜可沉积在开口 中以及在第二层间介电质1101之上。在此实施例中,可利用相似于如上面 有关于图13a至图13c所述的回蚀制程及/或平坦化制程,以移除沿着半导 体条603的水平部分的介电膜的水平部分。回蚀制程及/或平坦化制程重新曝 露半导体条603的顶部(例如,标注为半导体条顶部603a)以及铁电条601的 顶部(例如,标注为铁电条顶部601a)。除此之外,铁电条601的底部(例如, 标注为铁电条底部601b)在第一沟槽201的底部于对应的漏极区(例如标记

ꢀ“

d”)以及对应的源极区(例如标记“s”)的位置进行重新曝露。在此实施例 中,介电膜的剩余部分形成沿着第一沟槽201的侧壁以及相邻于半导体条603 的可选的通道间隔物1901。在此实施例中,通道间隔物1901在形成如图11a 至图11c所绘的通道切割插塞1201的开口之前且在形成如图12a以及图 12b所绘的通道切割插塞1201之后形成。

148.图20a以及图20b是根据一些实施例,描绘第三存储器阵列2000。第 三存储器阵列2000相似于图16a至图16c所绘的第一存储器阵列100,除 了通道隔离结构1001以及通道切割插塞1201以不同长度形成。特别而言, 图20a为第三存储器阵列2000的俯视图,且相似于图16b的俯视图。图20b 为由在第20a中的虚线所标示(highlighted)的第三存储器阵列200的一区域 2001的放大图。在此实施例中,通道隔离结构1001的中线对准通道切割插 塞1201的中线,如虚线2003所示。例如,通道隔离结构1001的中线沿第 一方向d1在对应的第三存储器阵列2000的列中对准通道切割插塞1201的 中线。进一步而言,根据一些实施例,位元线1501以及源极线1503的间距 以及位置亦可沿第一方向d1在对应的第三存储器阵列2000的列作对准。因 此,通道隔离结构1001沿第一方向d1在对应的第三存储器阵列2000的列 交错通道切割插塞1201。

149.根据一些实施例,以大约20纳米以及大约1000纳米之间的第六长度l6 形成通道隔离结构1001。进一步而言,可以大约20纳米以及大约1000纳米 之间的第七长度l7形成通道切割插塞1201。然而可以利用任何合适的长度。 根据一些实施例,第七长度l7对第六长度l6的比值可为大约1:1之间。 然而,可以利用任何合适的比值。在一些实施例中,第七长度l7可为大约 相等于第六长度l6以允许相邻的位元线以一致的间距(space)宽度形成(例 如,参见图20a)。在此实施例中,位元线可形成在所形成的第一存储器阵列 100中的相邻的薄膜晶体管的源极区以及漏极区之上(例如,参见图20a)。

150.通过利用以上所描述的制程,可形成一个三维阵列,其具有通道隔离结 构,对准相邻存储器单元的通道切割插塞。因此,提供三维存储器阵列具有 松弛的(relaxed)位元线1501以及源极线1503间距,其通道隔离结构对准横 跨三维存储器阵列的相邻存储器单元的通道切割插塞,并且与通道切割插塞 交错。此对准与交错可防止位元线内连结构(interconnects)以及源极线内连结 构有布线阻塞,并且允许字元线的两侧皆能随机存取存储器单元。特别的是, 通道隔离结构以及相邻存储器单元的通道切割插塞,可以其中线相互对准及 /或具有相同的长度来形成。因此,为了形成高密度存储器单元,及/或为了 对金属线提供了电阻/电容最佳化而提供了大的空间,且允许每个存储器单元 的随机存取。

及第一通道切割结构,相邻于第二存储器单元,其中第一通道切割结构的第 一部分在第一方向对准第一通道隔离结构的第二部分,第一方向平行于第一 通道切割结构的侧壁。

156.在一些实施例中,第一通道隔离结构的长度相等于第一通道切割结构的 长度。在一些实施例中,第一存储器单元进一步包含源极线,源极线与第一 通道层在相对于第一电荷捕捉条的一侧上邻接,并且耦接至第一通道层;以 及第二存储器单元进一步包含位元线,位元线与第二通道层在相对于第二电 荷捕捉条的一侧上邻接,并且耦接至第二通道层,第一存储器单元的源极线 对准第二存储器单元的位元线。在一些实施例中,第一通道切割结构的长度 不同于第一通道隔离结构的长度。在一些实施例中,第一存储器单元进一步 包含通道间隔物,设置在第一通道层以及第一通道隔离结构之间。在一些实 施例中,第一通道切割结构的中线对准第一通道隔离结构的中线。

157.前述内容概述了几个实施例的特征。本领域技术人员应该理解,他们可 以容易地将本公开用作设计的基础或修改其他制程和结构以实现与本文介 绍的实施例相同的目的和/或实现相同的优点。本领域技术人员还应该认知 到,等效的构造不脱离本公开的精神和范围,并且在不脱离本公开的精神和 范围的情况下,它们可以进行各种改变,替换和变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1