半导体结构及其形成方法、以及晶圆切割方法与流程

本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法、以及晶圆切割方法。

背景技术:

1、在半导体芯片封装工艺中,需要对芯片进行切割,切割过程在切割道中进行。切割的机械力可能导致边缘处形成微小裂痕,尤其是接近边角处。所形成的裂痕可能会朝向集成电路的中心电路区域推进而造成其中的电路区域毁坏。为了保护电路区域,一般会在集成电路芯片上介于电路区域以及其切割道之间,配置芯片密封环(seal ring),传统的密封环一般采用多层金属层叠加,通常为双密封环(内外共两圈)或单密封环(仅一圈)。芯片密封环可以防止任何裂痕侵入集成电路内部的电路区域。

2、然而,随着芯片尺寸的变小,芯片与芯片间的切割道尺寸也逐步缩小,切割道尺寸的缩小给后段的切割(die saw)工艺带来了严峻的挑战。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体结构及其形成方法、以及晶圆切割方法,有利于进一步半导体结构的性能。

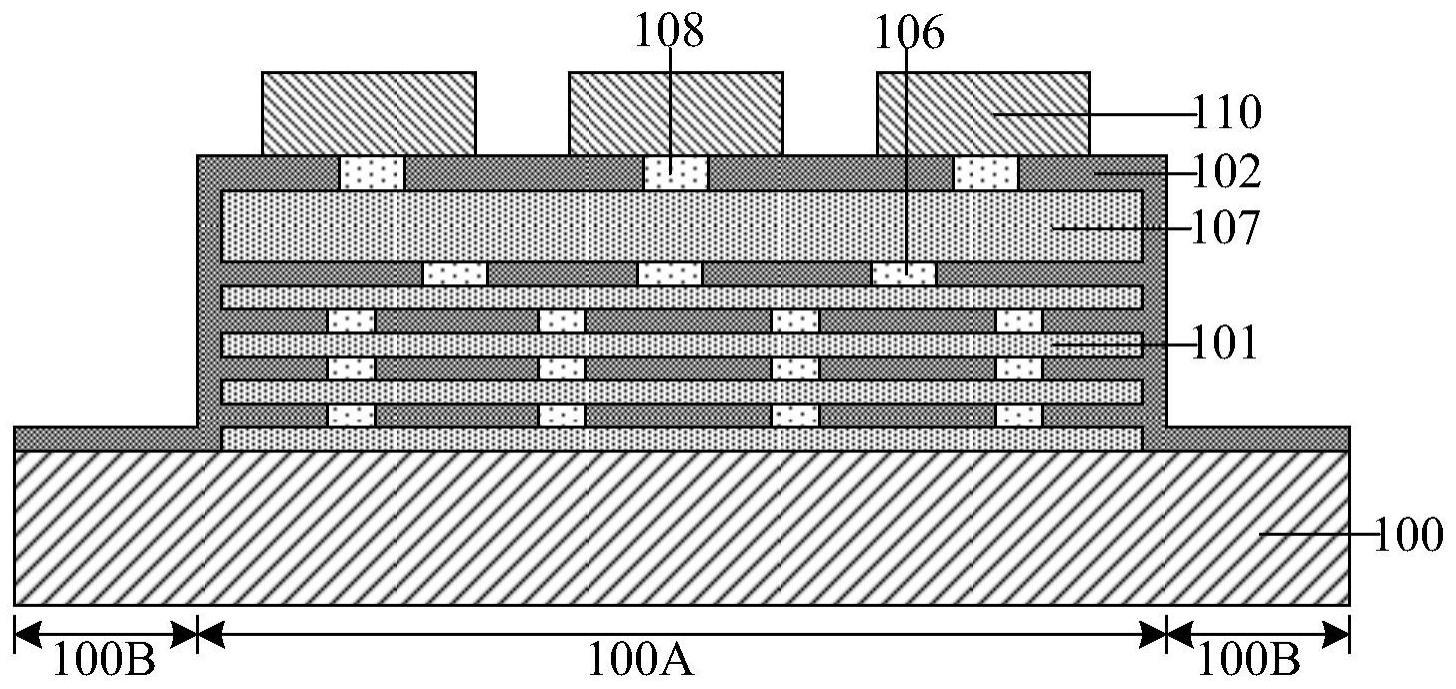

2、为解决上述问题,本发明实施例提供一种半导体结构,包括:基底,所述基底包括切割道区和器件区;互连结构,位于所述切割道区和器件区的所述基底的顶部,且最顶层的所述互连结构为顶部互连结构;多个缓冲互连结构,分立于所述顶部互连结构的顶部,多个所述缓冲互连结构沿相对应顶部互连结构的延伸方向排布,所述缓冲互连结构与所述顶部互连结构相电连接。

3、相应的,本发明实施例还提供一种半导体结构的形成方法,包括:提供基底,所述基底包括切割道区,在所述切割道区中,所述基底顶部形成有互连结构,且最顶层的互连结构为顶部互连结构;在所述顶部互连结构的顶部形成多个分立的缓冲互连结构,多个所述缓冲互连结构沿相对应顶部互连结构的延伸方向排布,所述缓冲互连结构与所述顶部互连结构相电连接。

4、相应的,本发明实施例还提供一种晶圆切割方法,包括:提供待切割的器件晶圆,所述器件晶圆包括利用本发明实施例提供的半导体结构;在所述切割道区中,从所述缓冲互连结构的一侧,沿所述切割道区的延伸方向对所述切割道区中的缓冲互连结构、互连结构和基底进行切割,将所述器件晶圆分割成多个芯片。

5、与现有技术相比,本发明实施例的技术方案具有以下优点:

6、本发明实施例提供一种半导体结构的形成方法,在所述顶部互连结构的顶部形成多个分立的缓冲互连结构,多个所述缓冲互连结构沿相对应顶部互连结构的延伸方向排布,后续在对切割道区的缓冲互连结构、互连结构和基底进行切割的过程中,由于多个缓冲互连结构呈分段式,即相邻缓冲互连结构之间具有空间间隔,所述缓冲互连结构产生的拉伸应力的连续性被阻断,并且产生的拉伸应力较小,降低了所述缓冲互连结构与切割道区周围的各个膜层结构(例如:密封环)相短接的概率,从而提高了所述半导体结构的性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述缓冲互连结构与所述顶部互连结构为一体式结构;

3.如权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括:第一钝化层,所述第一钝化层覆盖所述顶部互连结构;

4.如权利要求3所述的半导体结构,其特征在于,所述互连插塞的材料包括铝和氮化钽中的一种或两种。

5.如权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括:第二钝化层,覆盖所述缓冲互连结构和顶部互连结构。

6.如权利要求5所述的半导体结构,其特征在于,所述基底还包括位于所述切割道区和器件区之间的密封区;

7.如权利要求1所述的半导体结构,其特征在于,所述缓冲互连结构的材料包括铝和氮化钽中的一种或两种。

8.如权利要求1所述的半导体结构,其特征在于,沿相对应的所述顶部互连结构的延伸方向,相邻所述缓冲互连结构之间等间距排布。

9.如权利要求1所述的半导体结构,其特征在于,沿相对应的所述顶部互连结构的延伸方向,相邻所述缓冲互连结构之间的距离为70μm至140μm。

10.如权利要求1所述的半导体结构,其特征在于,所述缓冲互连结构沿相对应的所述顶部互连结构延伸方向上的尺寸为50μm至70μm。

11.如权利要求6所述的半导体结构,其特征在于,所述密封环与所述互连结构和缓冲互连结构在平行于所述基底表面的方向上相间隔的距离为4μm至10μm。

12.一种半导体结构的形成方法,其特征在于,包括:

13.如权利要求12所述的半导体结构的形成方法,其特征在于,在所述顶部互连结构的顶部形成多个分立的缓冲互连结构的步骤包括:在所述顶部互连结构的顶部形成缓冲互连材料层;对所述缓冲互连材料层进行图形化处理,在所述顶部互连结构的顶部形成多个分立的缓冲互连结构。

14.如权利要求12所述的半导体结构的形成方法,其特征在于,在所述顶部互连结构的顶部形成多个分立的缓冲互连结构的步骤包括:对部分厚度的顶部互连结构进行图形化处理,形成多个凸立于剩余所述顶部互连结构顶部的缓冲互连结构。

15.如权利要求13所述的半导体结构的形成方法,其特征在于,提供基底的步骤中,所述基底的顶部还形成有覆盖所述顶部互连结构的第一钝化层;

16.如权利要求12所述的半导体结构的形成方法,其特征在于,在形成所述缓冲互连结构之后,还包括:形成覆盖所述缓冲互连结构和顶部互连结构的第二钝化层。

17.如权利要求16所述的半导体结构的形成方法,其特征在于,提供基底的步骤中,所述基底还包括位于切割道区两侧的密封区;

18.如权利要求13或14所述的半导体结构的形成方法,其特征在于,所述图形化处理的工艺包括干法刻蚀工艺。

19.一种晶圆切割方法,其特征在于,包括:

技术总结

一种半导体结构及其形成方法,以及晶圆切割方法,形成方法包括:提供基底,所述基底包括切割道区,在所述切割道区中,所述基底顶部形成有互连结构,且最顶层的互连结构为顶部互连结构;在所述顶部互连结构的顶部形成多个分立的缓冲互连结构,多个所述缓冲互连结构沿相对应顶部互连结构的延伸方向排布,所述缓冲互连结构与所述顶部互连结构相电连接。由于多个缓冲互连结构呈分段式,即相邻缓冲互连结构之间具有空间间隔,所述缓冲互连结构产生的拉伸应力的连续性被阻断,并且产生的拉伸应力较小,降低了所述缓冲互连结构与切割道区周围的各个膜层结构(例如:密封环)相短接的概率,从而提高了所述半导体结构的性能。

技术研发人员:黄婷婷,王亚平,费春潮,朱雅莉

受保护的技术使用者:中芯国际集成电路制造(上海)有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!