晶体管制备方法及晶体管

本发明涉及半导体,尤其涉及一种晶体管制备方法及晶体管。

背景技术:

1、p沟道氮化镓基增强型晶体管是搭建氮化镓基cmos平台中不可或缺的重要单元。目前常见的p沟道氮化镓基增强型晶体管,一般是采用p-氮化镓/氮化镓铝/氮化镓,并通过深度刻蚀栅槽来耗尽栅下空穴,刻蚀截面与氮化镓铝间的距离往往在10nm左右,然而耗尽栅下空穴的同时,由于刻蚀截面与空穴沟道距离过近,界面态散射会严重影响栅下空穴的迁移率,从而影响晶体管的输出电流。

技术实现思路

1、本发明提供的晶体管制备方法及晶体管,能够通过背栅调制来实现空穴的耗尽,从而完成对阈值电压的调制,避免对栅槽的深度刻蚀,提高栅下空穴的迁移率。

2、第一方面,本发明提供一种晶体管制备方法,包括:

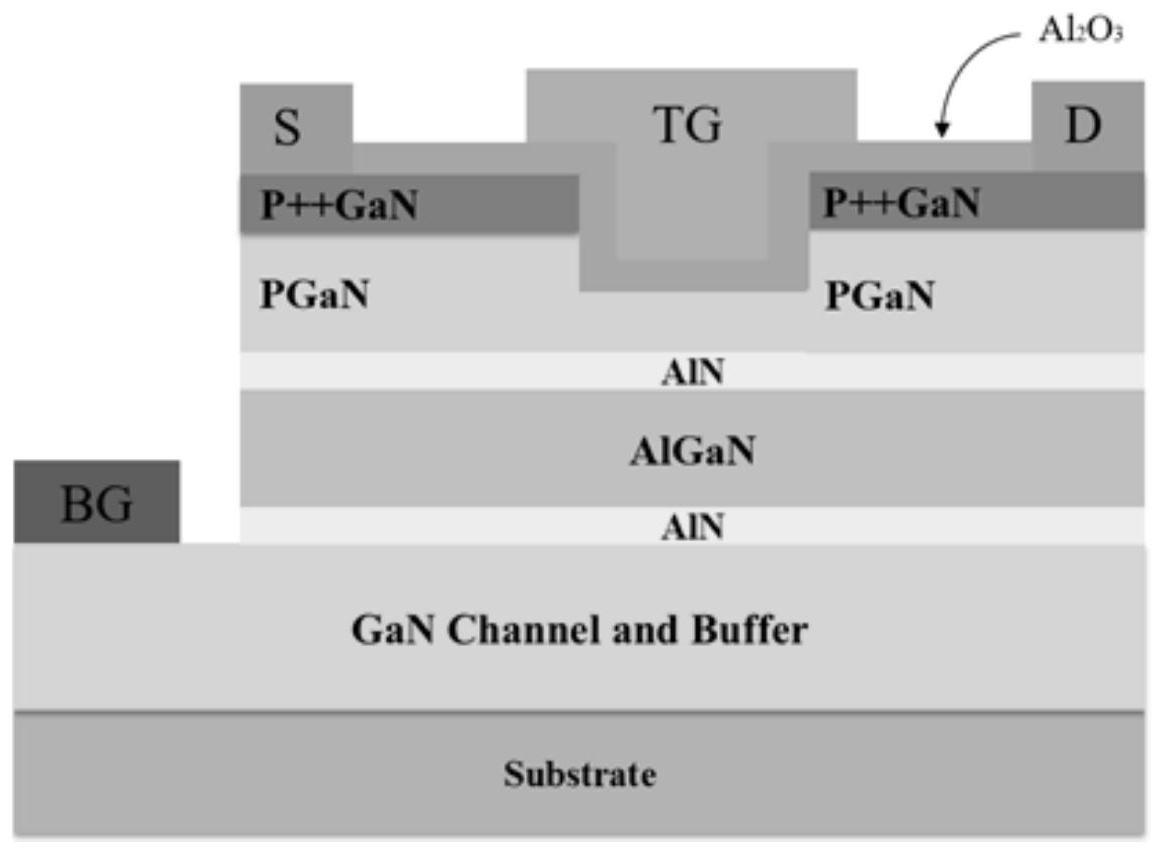

3、提供一个叠层结构,所述叠层结构包括从下向上依次设置的基板、氮化镓沟道层、第一氮化铝膜层、氮化镓铝势垒层、第二氮化铝膜层、p型氮化镓膜层以及重掺杂p型氮化镓膜层;

4、对所述叠层结构的第一区域刻蚀至氮化镓沟道层,并在所述氮化镓沟道层形成背栅电极;

5、在所述叠层结构的第二区域形成间隔设置的源漏电极;

6、对所述源漏电极之间的第三区域刻蚀至p型氮化镓膜层之内,并在所述刻蚀区域形成栅电极。

7、可选地,在提供一叠层结构之后,还包括:在所述叠层结构形成钝化层,所述钝化层的材料包括氧化铝或氧化硅中的一种或两种;

8、在所述叠层结构的第二区域形成间隔设置的源漏电极之前还包括,将所述源漏电极对应的区域进行刻蚀,以去除表面钝化处理形成的膜层。

9、可选地,所述氮化镓铝势垒层中,铝的含量为10%~30%。

10、可选地,p型氮化镓膜层为采用镁掺杂的p型氮化镓膜层,其中,镁的浓度为3e+19cm-3~5e+19cm-3;

11、所述重掺杂p型氮化镓膜层为采用镁掺杂的p型氮化镓膜层,其中,镁的浓度为1e+20cm-3~3e+20cm-3。

12、可选地,所述源漏电极包括镍金叠层,其中,镍膜层与所述p型氮化镓层接触。

13、可选地,所述栅电极为镍金叠层、铂钛金叠层、铝镍金叠层或氮化钛膜层中的其中一种。

14、可选地,所述基板包括硅、碳化硅、蓝宝石或者氮化镓材料中的一种或几种。

15、可选地,对所述源漏电极之间的第三区域刻蚀至p型氮化镓膜层之内后,包括:在刻蚀形成的凹槽的底面、侧壁以及重掺杂p型氮化镓膜层表面形成栅介质。

16、可选地,在所述叠层结构的第二区域形成间隔设置的源漏电极之后还包括:采用550℃~600℃的温度在氧气氛围或空气氛围中进行热退火。

17、第二方面,本发明提供一种晶体管,包括:

18、基板,

19、沟道层,设置在基板上,所述沟道层具有第一区域和第二区域;

20、背栅电极,设置在所述沟道层的第一区域,并与所述沟道层的第一区域形成肖特基接触;

21、功能叠层,设置在所述沟道层的第二区域,所述功能叠层包括由下向上依次设置的第一氮化铝膜层、氮化镓铝势垒层、第二氮化铝膜层和p型氮化镓膜层;其中,所述p型氮化镓膜层上设置有凹槽,所述p型氮化镓膜层上表面被凹槽分割为源漏区域;

22、重掺杂p型氮化镓膜层,设置在所述源漏区域上;

23、源漏电极,分别设置在所述源漏区域的重掺杂p型氮化镓膜层上;

24、栅介质,覆盖所述重掺杂p型氮化镓膜层上表面、所述凹槽的底面和所述凹槽的侧壁;

25、栅电极,至少部分设置在所述凹槽内。

26、本发明提供的技术方案中,在氮化镓铝势垒层上制备背栅电极,通过背栅电极的电压偏置,能够完成对空穴的耗尽,实现了对阈值电压的调制。在本发明提供的技术方案中,不需要对栅槽进行深度刻蚀,减小了界面态散射对栅下空穴迁移率的影响,有效的提高了器件的输出电流,扩展了氮化镓基器件的应用。

技术特征:

1.一种晶体管制备方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,在提供一叠层结构之后,还包括:在所述叠层结构形成钝化层,所述钝化层的材料包括氧化铝或氧化硅中的一种或两种;

3.根据权利要求1所述的方法,其特征在于,所述氮化镓铝势垒层中,铝的含量为10%~30%。

4.根据权利要求1所述的方法,其特征在于,p型氮化镓膜层为采用镁掺杂的p型氮化镓膜层,其中,镁的浓度为3e+19cm-3~5e+19cm-3;

5.根据权利要求1所述的方法,其特征在于,所述源漏电极包括镍金叠层,其中,镍膜层与所述p型氮化镓层接触。

6.根据权利要求1所述的方法,其特征在于,所述栅电极为镍金叠层、铂钛金叠层、铝镍金叠层或氮化钛膜层中的其中一种。

7.根据权利要求1所述的方法,其特征在于,所述基板包括硅、碳化硅、蓝宝石或者氮化镓材料中的一种或几种。

8.根据权利要求1所述的方法,其特征在于,对所述源漏电极之间的第三区域刻蚀至p型氮化镓膜层之内后,包括:在刻蚀形成的凹槽的底面、侧壁以及重掺杂p型氮化镓膜层表面形成栅介质。

9.根据权利要求1所述的方法,其特征在于,在所述叠层结构的第二区域形成间隔设置的源漏电极之后还包括:采用550℃~600℃的温度在氧气氛围或空气氛围中进行热退火。

10.一种晶体管,其特征在于,包括:

技术总结

本发明提供一种晶体管制备方法,包括:提供一个叠层结构,所述叠层结构包括从下向上依次设置的基板、氮化镓沟道层、第一氮化铝膜层、氮化镓铝势垒层、第二氮化铝膜层、P型氮化镓膜层以及重掺杂P型氮化镓膜层;对所述叠层结构的第一区域刻蚀至氮化镓沟道层,并在所述氮化镓沟道层形成背栅电极;在所述叠层结构的第二区域形成间隔设置的源漏电极;对所述源漏电极之间的第三区域刻蚀至P型氮化镓膜层之内,并在所述刻蚀区域形成栅电极。本发明提供的晶体管制备方法及晶体管,能够通过背栅调制来实现栅下空穴的耗尽,从而完成对阈值电压的调制,避免对栅槽的深度刻蚀,提高栅下空穴的迁移率。

技术研发人员:蒋其梦,王宇豪,黄森,王鑫华,刘新宇

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!