半导体装置的形成方法与流程

1.本发明实施例是有关于半导体技术,且特别是有关于半导体装置及其形成方法。

背景技术:

2.场效晶体管(field-effect transistor,fet)为使用电场来控制电流的流动的晶体管的类型。场效晶体管包含三个端子:源极、栅极和漏极。在操作中,场效晶体管通过对栅极施加电压来控制电流的流动,进而改变漏极与源极之间的导电性。一种常用类型的场效晶体管为金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)。可使用金属氧化物半导体场效晶体管例如作为电信号的开关(例如射频(radio frequency,rf)开关)、作为电信号的放大器(例如低噪声放大器(low-noise amplifier,lna))或在互补式金属氧化物半导体(complementary metal oxide semiconductor,cmos)逻辑(例如静态随机存取存储器(static random access memory,sram)以及其他类型的存储器装置)中,以及其他范例。

技术实现要素:

3.在一些实施例中,提供半导体装置的形成方法,此方法包含在外延区上方形成通过介电层到达间隙壁的开口;在开口的底部的间隙壁上及沿开口的侧壁的间隙壁上形成层,其中通过在间隙壁上沉积前驱物,并以等离子体处理前驱物来形成层,其中层减少开口沿第一方向的第一宽度,第一方向大致垂直于介电层,且其中前驱物从开口的侧壁移除材料,以增加开口沿第二方向的第二宽度,第二方向大致平行于介电层;以及蚀刻通过在开口的底部的层以及间隙壁,以到达外延区。

4.在一些实施例中,提供半导体装置的形成方法,此方法包含形成凹口,凹口通过半导体装置的第一层的一部分、相邻于第一层的半导体装置的第二层的一部分,并进入第一层和第二层下方的半导体装置的基底的一部分中,其中凹口包含对应第一层的第一组侧壁和对应第二层的第二组侧壁;在凹口中的第一层的第一组侧壁上形成第三层,其中使用前驱物来形成第三层,其中前驱物与第一层的第一材料和氮等离子体的组合反应,以在凹口中的第一层的第一组侧壁上形成第三层,其中第三层减少凹口在第一组侧壁之间的第一宽度,且其中前驱物与第二层的第二材料反应,以蚀刻凹口中的第二层的第二组侧壁,这增加了凹口在第二组侧壁之间的第二宽度;以及在第三层上方以介电材料填充凹口。

5.在另外一些实施例中,提供半导体装置,半导体装置包含第一主动区和第二主动区,位于半导体装置的基底上沿第一方向延伸;鳍切割隔离区,位于第一主动区与第二主动区之间;源极或漏极区,位于第一主动区和第二主动区中;接点,电性连接至源极或漏极区;浅沟槽隔离层,相邻于第一主动区和第二主动区;第一栅极区和第二栅极区,沿垂直于第一方向的第二方向延伸;栅极切割隔离区,位于第一栅极区与第二栅极区之间;以及以下至少一者:第一氮化硼层,位于接点及与接点有关联的间隙壁之间;第二氮化硼层,位于第一鳍切割隔离区与第一主动区之间以及鳍切割隔离区与第二主动区之间;或第三氮化硼层,位

于栅极切割隔离区与第一栅极区之间以及栅极切割隔离区与第二栅极区之间。

附图说明

6.根据以下的详细说明并配合所附图式可以更加理解本发明实施例。应注意的是,根据本产业的标准惯例,图示中的各种部件(feature)并未必按照比例绘制。事实上,可能任意的放大或缩小各种部件的尺寸,以做清楚的说明。

7.图1为可进行本文描述的系统及/或方法的范例环境的图式。

8.图2为本文描述的范例半导体装置的图式。

9.图3为本文描述的范例存储器单元的图式。

10.图4为关于本文描述形成半导体装置的范例制程的流程图。

11.图5a-图5e、图6a-图6e、图7a-图7f和图8a-图8d为本文描述的范例实施例的图式。

12.图9为图1的一个或多个装置的范例组件的图式。

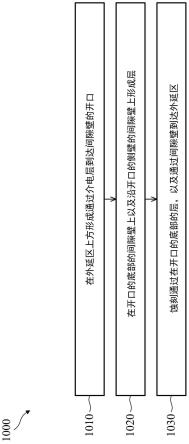

13.图10和图11为关于本文描述形成半导体装置的范例制程的流程图。

14.图12为本文描述的范例实施例的图式。

15.其中,附图标记说明如下:

16.100:环境

17.102:沉积工具

18.104:曝光工具

19.106:显影工具

20.108:蚀刻工具

21.110:平坦化工具

22.112:镀覆工具

23.114:晶圆/晶粒转移工具

24.200:半导体装置

25.202,502,602,702:基底

26.204,722:鳍结构

27.206:盖层

28.208,606:介电层

29.210:中间接触蚀刻停止层

30.212:氧化层

31.214,724:外延区

32.216:源极或漏极接点

33.218,728:栅极

34.220,222:间隙壁

35.224:源极或漏极互连线

36.226:栅极互连线

37.228:对接接点

38.300:存储器单元

39.302a,302b:通道栅极晶体管

40.304a,304b:上拉晶体管

41.306a,306b:下拉晶体管

42.308:字元线

43.310a,310b:位元线

44.312:正电源供应节点

45.314:电源供应节点

46.400,1000,1100:制程

47.402,404,406,408,410,412,414,416,418,420,422,424,426,428,430,432,434,436,438,1010,1020,1030,1110,1120,1130:方框

48.500,600,700,800,1200:范例实施例

49.504:主动区层

50.506:浅沟槽隔离层

51.508,608,712:俯视图

52.510,512,610,612,714,716:剖面示意图

53.514,614,730,812:凹口

54.516,616,732:层

55.518:切割主动区

56.604:多晶硅层

57.618:切割多晶硅区

58.704:层间介电层

59.706:牺牲层结构

60.708:间隙壁

61.710:切割金属漏极区

62.718,720:硬遮罩层

63.726:底部对比加强层

64.734:开口

65.736:硅化物层

66.738:源极或漏极接点

67.802,1204:氧化层

68.804,1202:氮化层

69.806:氯化硼

70.808:氧

71.810:氮

72.814:氧氯化硼

73.816:氮-硼键

74.820:氮等离子体

75.822:氮化硼层

76.900:装置

77.910:汇流排

78.920:处理器

79.930:存储器

80.940:存储组件

81.950:输入组件

82.960:输出组件

83.970:通信组件

84.1206:六氟化钨

85.1208:四氟氧化钨

86.1210:氢氟酸

87.1212:氢氟烃

88.w1,w2,w3,w4:宽度

具体实施方式

89.要了解的是以下的公开内容提供许多不同的实施例或范例,以实施提供的主体的不同部件。以下叙述各个构件及其排列方式的特定范例,以求简化公开内容的说明。当然,这些仅为范例并非用以限定本发明。例如,元件的尺寸不限于本公开的一实施方式的范围或数值,但可取决于元件的处理条件及/或要求性质。此外,在随后描述中在第二部件上方或在第二部件上形成第一部件包括第一及第二部件形成为直接接触的实施例,以及亦可包括额外部件可形成在第一及第二部件之间,使得第一及第二部件可不直接接触的实施例。此外,公开内容中不同范例可能使用重复的参考符号及/或用字。这些重复符号或用字是为了简化与清晰的目的,并非用以限定各个实施例及/或所述外观结构之间的关系。

90.再者,为了方便描述图式中一元件或部件与另一(复数)元件或(复数)部件的关系,可使用空间相关用语,例如“在...之下”、“下方”、“下部”、“在...之上”、“上部”及类似的用语。除了图式所绘示的方位之外,空间相关用语也涵盖装置在使用或操作中的不同方位。所述装置也可被另外定位(例如,旋转90度或者位于其他方位),并对应地解读所使用的空间相关用语的描述。

91.可以各种物理实施例实现场效晶体管(field-effect transistor,fet)。作为范例,可将场效晶体管实现作为二维平面晶体管,其中源极和漏极通过通道隔开,且栅极位于通道上方(例如正上方及在通道的顶部上)以及源极和漏极之上(例如高于源极和漏极,但是不需要在源极和漏极上方或源极和漏极的顶部上)。作为另一范例,可将场效晶体管实现作为三维晶体管,例如鳍式场效晶体管或纳米结构晶体管(例如纳米线晶体管、纳米片晶体管、全绕式栅极晶体管、多桥接通道晶体管、纳米带晶体管等)。鳍式场效晶体管可包含作为通道的鳍,此通道允许栅极(例如金属栅极(metal gate,mg))环绕通道的三个面,进而能够增加对通道的控制(进而实现对鳍式场效晶体管的开关)。源极/漏极接点(例如金属漏极(metal drain,md)接点)形成于栅极的两侧鳍的周围,栅极控制通道,以能够或阻挡电流的流动从源极通过鳍到达漏极。

92.随着晶体管尺寸持续缩小,出现了与鳍式场效晶体管和其他类型的晶体管有关的各种半导体制造挑战。在一些情况中,蚀刻能力可能不支持缩小鳍式场效晶体管的金属漏极的x方向尺寸(例如沿鳍式场效晶体管的栅极方向的金属漏极宽度)和增加金属漏极的y

方向尺寸(例如沿鳍式场效晶体管的鳍方向的金属漏极宽度)。在一些情况中,鳍式场效晶体管的主动区的端对端能力及蚀刻能力可能不支持缩小主动区的x方向尺寸或增加主动区的y方向尺寸。在一些情况中,鳍式场效晶体管的多晶区(例如多晶硅区或其他类型的多晶区)的端对端能力及蚀刻能力可能不支持缩小多晶区的x方向尺寸或增加多晶区的y方向尺寸。

93.本文描述的一些实施例提供用于缩小鳍式场效晶体管(及/或其他类型的半导体晶体管)的一个或多个尺寸及/或增加鳍式场效晶体管的一个或多个尺寸的各种半导体结构及技术。在本文描述的各种实施例中,可使用氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)(例如氧化硼(b2o3))、氟碳(c

xfy

)聚合物、碳化钨(wc

x

)及/或其他材料,以通过选择性沉积来缩小鳍式场效晶体管的一个或多个x方向尺寸,而通过蚀刻来增加或扩大鳍式场效晶体管的一个或多个y方向尺寸。举例来说,鳍式场效晶体管的金属漏极的x方向尺寸、鳍式场效晶体管的主动区的x方向尺寸及/或鳍式场效晶体管的多晶区的x方向尺寸可通过选择性沉积氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)(例如氧化硼(b2o3))、氟碳(c

xfy

)聚合物、碳化钨(wc

x

)及/或其他材料来增加。此选择性沉积通过蚀刻可允许鳍式场效晶体管的一个或多个y方向尺寸增加。

94.以此方式,使用本文描述的技术缩小鳍式场效晶体管的一个或多个x方向尺寸可允许缩小互补式金属氧化物半导体逻辑装置尺寸(例如,静态随机存取存储器装置及/或其他类型的存储器装置的单元尺寸)。再者,使用本文描述的技术增加鳍式场效晶体管的一个或多个y方向尺寸可允许扩大各种半导体制程裕度,其可增加半导体制造品质以及半导体制造产率。

95.图1为可进行本文描述的系统及/或方法的范例环境100的图式。环境100可包含多个半导体加工工具以及晶圆/晶粒转移工具114。多个半导体加工工具可包含沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112及/或其他类型的半导体加工工具。包含在范例环境100中的工具可被包含在半导体清洁室、半导体代工厂、半导体加工设施及/或制造设施等。

96.沉积工具102为半导体加工工具,此半导体加工工具包含半导体加工腔体及能够在基底上沉积各种类型材料的一个或多个装置。在一些实施例中,沉积工具102包含旋涂工具,此旋涂工具能够在基底(例如晶圆)上沉积光阻层。在一些实施例中,沉积工具102包含化学气相沉积(chemical vapor deposition,cvd)工具,例如等离子体辅助化学气相沉积(plasma-enhanced cvd,pecvd)工具、高密度等离子体化学气相沉积(high-density plasma cvd,hdp-cvd)工具、次常压化学气相沉积(sub-atmospheric cvd,sacvd)工具、原子层沉积(atomic layer deposition,ald)工具、等离子体辅助原子层沉积(plasma-enhanced ald,peald)工具或其他类型的化学气相沉积工具。在一些实施例中,沉积工具102包含物理气相沉积(physical vapor deposition,pvd)工具,例如溅镀工具或其他类型的物理气相沉积工具。在一些实施例中,范例环境100包含多个类型的沉积工具102。

97.曝光工具104为半导体加工工具,此半导体加工工具能够将光阻层暴露于辐射源,例如紫外光(ultraviolet light,uv)源(例如深紫外光源、极紫外光(extreme uv light,euv)源及/或类似物)、x射线源、电子束(electron beam,e-beam)源及/或类似物。曝光工具104可将光阻层暴露于辐射源,以将光罩的图案转移至光阻层。此图案可包含用于形成一个

或多个半导体装置的一个或多个半导体装置层图案,可包含用于形成半导体装置的一个或多个结构的图案,可包含用于蚀刻半导体装置的各部分的图案及/或类似物。在一些实施例中,曝光工具104包含扫描器、步进机或类似的曝光工具。

98.显影工具106为半导体加工工具,此半导体加工工具能够将已暴露于辐射源的光阻层显影,以显影从曝光工具104转移至光阻层的图案。在一些实施例中,显影工具106通过移除光阻层的未暴露部分来将图案显影。在一些实施例中,显影工具106通过移除光阻层的暴露部分来将图案显影。在一些实施例中,显影工具106通过使用化学显影剂溶解光阻层的暴露或未暴露部分来将图案显影。

99.蚀刻工具108为半导体加工工具,此半导体加工工具能够蚀刻基底、晶圆或半导体装置的各种类型的材料。举例来说,蚀刻工具108可包含湿蚀刻工具、干蚀刻工具及/或类似物。在一些实施例中,蚀刻工具108包含填充蚀刻剂的腔体,且基底放置于此腔体中一段特定时间,以移除基底的一个或多个部分的特定量。在一些实施例中,蚀刻工具108可使用等离子体蚀刻或等离子体辅助蚀刻来蚀刻基底的一个或多个部分,等离子体蚀刻或等离子体辅助蚀刻可涉及使用离子化气体来等向性或方向性蚀刻此一个或多个部分。

100.平坦化工具110为半导体加工工具,此半导体加工工具能够研磨或平坦化晶圆或半导体装置的各层。举例来说,平坦化工具110可包含化学机械平坦化(chemical mechanical planarization,cmp)工具及/或研磨或平坦化沉积或镀覆材料的层或表面的其他类型的平坦化工具。平坦化工具110可结合化学及机械力(例如化学蚀刻及免研磨剂抛光)来研磨或平坦化半导体装置的表面。平坦化工具110可结合研磨垫和保持环(例如一般具有比半导体装置更大的直径)来使用研磨剂和腐蚀性化学研磨浆。研磨垫和半导体装置可通过动态研磨头压在一起,并通过保持环固定就位。动态研磨头可以不同的旋转轴旋转,以移除材料,并平整半导体装置的任何不规则表面形貌,使半导体装置平坦或呈平面。

101.镀覆工具112为半导体加工工具,此半导体加工工具能够以一种或多种金属镀覆基底(例如晶圆、半导体装置及/或类似物)或基底的一部分。举例来说,镀覆工具112可包含铜电镀装置、铝电镀装置、镍电镀装置、锡电镀装置、化合物材料或合金(例如锡银、锡铅及/或类似物)电镀装置及/或用于一种或多种其他类型的导电材料、金属及/或类似类型的材料的电镀装置。

102.晶圆/晶粒转移工具114包含移动机器人、机械手臂、有轨电车或轨道车、高架式起吊输送(overhead hoist transport,oht)系统、自动化物料配送系统(automated materially handling system,amhs)及/或用于在半导体加工工具之间及/或到达或从其他位置(例如晶圆架、储藏室及/或类似位置)运输晶圆及/或晶粒的其他类型的装置。在一些实施例中,晶圆/晶粒转移工具114可为被配置以特定路径移动及/或可半自动或自动操作的编程装置。

103.图1显示的装置数量和排列是作为一个或多个范例。相较于图1的所示的装置,实际上可具有额外装置、较少装置、不同装置或不同排列的装置。再者,图1中所示的两个或更多个装置可以在单一个装置中实现,或者图1所示的单一个装置可实现为多个分布式装置。额外地或替代地,环境100的一组装置(例如一个或多个装置)可进行一个或多个被描述为由环境100的另一组装置进行的功能。

104.图2为本文描述的范例半导体装置200的图式。半导体装置200包含例示性的存储

transistor,6t)静态随机存取存储器(sram)单元的范例。存储器单元300可被包含在半导体装置200及/或其他半导体装置中。

112.如图3所示,存储器单元300包含通道栅极晶体管302a和302b、上拉晶体管304a和304b以及下拉晶体管306a和306b。通道栅极晶体管302a和302b包含n型金属氧化物半导体(n-type metal-oxide semiconductor,nmos)晶体管或p型金属氧化物半导体(p-type metal-oxide semiconductor,pmos)晶体管。上拉晶体管304a和304b包含p型金属氧化物半导体晶体管。下拉晶体管306a和306b包含n型金属氧化物半导体晶体管。在一些实施例中,通道栅极晶体管302a和302b、上拉晶体管304a和304b及/或下拉晶体管306a和306b包含本文描述的鳍式场效晶体管。在一些实施例中,通道栅极晶体管302a和302b、上拉晶体管304a和304b及/或下拉晶体管306a和306b包含其他类型的晶体管,例如全绕式栅极晶体管及/或平面晶体管等。

113.通道栅极晶体管302a和302b通过用以选择或启动存储器单元300的字元线(word-line,wl)308控制。上拉晶体管304a和304b以及下拉晶体管306a和306b以锁存配置电性连接,以存储一个或多个电子位元信息。存储位元可写入位元线(bit lines,bl)310a和310b或从位元线310a和310b读取。存储器单元通过正电源供应节点(v

cc

或v

dd

)312和电源供应节点(v

ss

)314供电,电源供应节点314可包含电性接地。

114.如上所述,提供图3作为范例。其他范例可不同于参考图3的描述。

115.图4为关于本文描述形成半导体装置的范例制程400的流程图。半导体装置可包含半导体装置200、存储器单元300及/或包含多个晶体管的其他半导体装置。在一些实施例中,本文描述的一个或多个技术可作为(或作为一部分)连结图4描述的一个或多个操作来进行。

116.在一些实施例中,图4的一个或多个制程方框可通过一个或多个半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)来进行。额外地或替代地,图4的一个或多个制程方框可通过装置(例如装置900(图9),例如处理器920、存储器930、存储组件940、输入组件950、输出组件960及/或通信组件970)的一个或多个组件来进行。

117.如图4所示,制程400包含形成半导体装置的主动区(或多个主动区)(方框402)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在半导体装置200的基底202中形成主动区(或多个主动区)。主动区可包含形成于基底202中的多个鳍结构204。

118.如图4所示,制程400包含在主动区之间形成浅沟槽隔离(shallow trench isolation,sti)区(方框404)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在半导体装置200的多个鳍结构204之间形成浅沟槽隔离区。浅沟槽隔离区包含在主动区或鳍结构204之间提供电性隔离的介电区。

119.再者,如图4所示,制程400包含在半导体装置的一个或多个主动区中形成一个或多个切割主动区(cut active region)(方框406)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在半导体装置200中形成一个或多个切割主动区。切割主动区可包含半导体装置200

的鳍结构204的切割鳍区。在一些实施例中,一个或多个切割主动区基于与图5a-图5e连结描述的一个或多个技术及/或基于本文描述的其他技术形成。

120.再者,如图4所示,制程400包含鳍形成操作(方框408)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可进行鳍形成操作,以回蚀刻浅沟槽隔离层。浅沟槽隔离层的回蚀刻缩小浅沟槽隔离层的高度,浅沟槽隔离层的回蚀刻暴露了半导体装置200的主动区或鳍结构204的一部分。

121.再者,如图4所示,制程400包含形成虚设多晶图案(方框410)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的虚设多晶图案。虚设多晶图案包含形成半导体装置200的多个多晶硅层或多晶硅区作为形成半导体装置200的栅极218的一部分。多晶硅层形成于主动区或鳍结构204的一部分上方以及浅沟槽隔离层的一部分上方。多晶硅层在大致垂直于主动区和浅沟槽隔离层的方向延伸。在一些实施例中,形成多晶硅层,以作为在形成栅极218(可包含金属栅极)之前用于中间加工操作的虚设层。此被称为栅极后制制程,其中先形成虚设多晶硅层(例如虚设多晶硅栅极),且可持续加工直到沉积层间介电(interlayer dielectric,ild)层。接着,移除虚设多晶硅层,并以金属栅极取代虚设多晶硅层。

122.再者,如图4所示,制程400包含在半导体装置的一个或多个多晶硅层中形成一个或多个切割多晶硅区(方框412)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在半导体装置200中形成一个或多个切割多晶硅区。在一些实施例中,半导体装置200或存储器单元300的多个p型金属氧化物半导体及/或n型金属氧化物半导体装置共用一个或多个多晶硅层。因此,进行操作,以将一个或多个多晶硅层分隔为多个不连接的区段,使得每个p型金属氧化物半导体装置及/或n型金属氧化物半导体装置在元件格中为具有各自多晶硅层区段的独立装置。因此,使用切割多晶硅区,以将多个装置共用的多晶硅层切割为隔开的部分。在一些实施例中,一个或多个切割多晶硅区基于与图6a-图6e连结描述的一个或多个技术及/或基于本文描述的其他技术形成。

123.再者,如图4所示,制程400包含形成半导体装置的间隙壁(方框414)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的间隙壁220和222。

124.再者,如图4所示,制程400包含进行主动区的应变源极漏极(ssd)蚀刻,以在主动区的一部分中形成凹口(方框416)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可进行应变源极漏极蚀刻,以在半导体装置200的主动区或鳍结构204中形成凹口。

125.再者,如图4所示,制程400包含通过外延成长形成半导体装置的外延区(方框418)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的外延区214。外延区214可形成于半导体装置200的主动区或鳍结构204中的凹口中,且通过外延成长从凹口成长出来。形成外延区214作为半导体装置200的源极或漏极区。

126.再者,如图4所示,制程400包含形成半导体装置的接触蚀刻停止层(contact etch stop layer,cesl)(方框420)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的接触蚀刻停止层。接触蚀刻停止层包含氮化硅(si

x

ny)、氮氧化硅(sion)及/或其他合适的材料。接触蚀刻停止层提供作为形成到达外延区214的源极或漏极接点216时的蚀刻停止层。

127.再者,如图4所示,制程400包含形成半导体装置的层间介电(interlayer dielectric,ild)层(或层间介电区)(方框422)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在半导体装置200的多个多晶硅层之间形成层间介电区。层间介电区提供半导体装置200的多晶硅层之间的电性隔离。

128.再者,如图4所示,制程400包含移除与多晶硅层相关联的硬遮罩(方框424)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可从半导体装置200移除与多晶硅层(例如虚设多晶硅栅极)相关联的硬遮罩。

129.再者,如图4所示,制程400包含虚设多晶和介电移除操作(方框426)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可从半导体装置200移除多晶硅层(例如虚设多晶硅栅极)和相关联的介电层。如上所述,在一些实施例中,多晶硅层(或虚设多晶硅栅极)在形成半导体装置200的金属栅极(例如栅极218)之前作为占位结构。因此,进行虚设多晶和介电移除操作,使得栅极218可在后续加工操作中形成。

130.再者,如图4所示,制程400包含形成半导体装置的栅极(例如金属栅极)(方框428)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的栅极218。

131.再者,如图4所示,制程400包含形成半导体装置的源极/漏极接点(例如金属漏极)(方框430)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的源极或漏极接点216。形成源极或漏极接点216,以电性连接外延区214。在一些实施例中,源极或漏极接点216基于与图7a-图7f连结描述的一个或多个技术及/或基于本文描述的其他技术形成。

132.再者,如图4所示,制程400包含形成半导体装置的互连线(方框432)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的互连线(源极或漏极互连线224、栅极互连线226和对接接点228)。形成连接至源极或漏极接点216(例如vd互连线或bct互连线)和连接至栅极218(例如vg互联线或bct互连线)的互连线。

133.再者,如图4所示,制程400包含形成半导体装置的后段(back end of line,beol)金属层(方框434)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成电性连接至半导体装置200的源极或漏极互连线224、栅极互连线226和对接接点228的后段金属层(例如m0和

m1)。

134.再者,如图4所示,制程400包含形成半导体装置的保护层(方框436)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成半导体装置200的保护层。保护层可包含保护半导体装置200的电路和金属层的介电层及/或其他类型的绝缘层。

135.再者,如图4所示,制程400包含封装半导体装置(方框438)。举例来说,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可将半导体装置200封装为装置封装体。封装体可包含系统级封装(system in package,sip)、芯片封装(chip on package,cop)、封装上封装(package on package,pop)或其他类型的半导体封装。

136.虽然图4显示制程400的范例方框,但是在一些实施例中,相较于图4,制程400可包含额外的方框、较少的方框、不同的方框或不同排列的方框。额外地或替代地,可并行制程400的两个或更多个方框。

137.图5a-图5e为本文描述的范例实施例500的图式。范例实施例500包含在半导体装置(例如半导体装置200及/或存储器单元300等)中形成一个或多个切割主动区的范例。在一些实施例中,进行与图5a-图5e连结描述的操作,作为形成半导体装置的制程的一部分,例如连结图4所述的制程。在一些实施例中,进行与图5a-图5e连结描述的操作,作为连结图4描述的切割主动区操作(方框406)的一部分。

138.如图5a所示,半导体装置包含基底502(例如半导体装置200的基底202)、多个主动区层504(例如半导体装置200的鳍结构204)以及多个浅沟槽隔离层506。如半导体装置200的俯视图508所示,主动区层504和浅沟槽隔离层506沿第一方向(例如x方向)延伸。再者,主动区层504和浅沟槽隔离层506在半导体装置200中以交替图案排列。

139.图5a更显示在第一方向(例如x方向)沿主动区层504的半导体装置的一部分的剖面示意图510以及在第二方向(例如y方向)横跨主动区层504和多个浅沟槽隔离层506的剖面示意图512,第二方向大致垂直于第一方向。如剖面示意图510和512所示,主动区层504和浅沟槽隔离层506被包含在基底502上方及/或基底502上。

140.在一些实施例中,取决于制程能力和半导体装置尺寸参数,主动区层504沿主动区层504的短尺寸方向(例如沿y方向)的宽度在约5nm至约200nm的范围中。然而,主动区层504的宽度的其他数值也在本发明实施例的范围中。在一些实施例中,取决于制程能力和主动区层504之间的间隔,浅沟槽隔离层506沿浅沟槽隔离层506的短尺寸方向(例如沿y方向)的宽度在约8nm至约200nm的范围中。然而,浅沟槽隔离层506的宽度的其他数值也在本发明实施例的范围中。

141.再者,如图5a所示(例如在剖面示意图512中),浅沟槽隔离层506比主动区层504的高度更低或更短。在一些实施例中,形成浅沟槽隔离层506和主动区层504具有相同或相似的高度。之后,进行制程,以凹陷或回蚀刻浅沟槽隔离层506,以暴露主动区层504的一部分,如图5a的剖面示意图512所示。

142.如图5b所示,多个凹口514(或开口)形成通过一个或多个主动区层504的一部分以及通过多个浅沟槽隔离层506的一部分。在一些实施例中,凹口514形成于基底502的一部分中。凹口514包含半导体装置的切割主动区中将形成于其中的凹口。

143.在一些实施例中,使用光阻层中的图案来形成凹口514。在这些实施例中,沉积工具102在主动区层504上及浅沟槽隔离层506上形成光阻层。曝光工具104将光阻层暴露于辐射源,以将光阻层图案化。显影工具106将光阻层显影并移除光阻层的一部分,以暴露图案。蚀刻工具108蚀刻通过主动区层504的一部分、浅沟槽隔离层506的一部分,并进入基底502的一部分中,以形成凹口514。在一些实施例中,蚀刻操作包含等离子体蚀刻技术、湿化学蚀刻技术及/或其他类型的蚀刻技术。在一些实施例中,光阻移除工具移除光阻层的剩下部分(例如使用化学剥离剂、等离子体灰化及/或其他技术)。在一些实施例中,使用硬遮罩层用作基于图案形成凹口514的替代技术。

144.如图5c所示,层516形成于凹口514中。特别来说,层516沉积于凹口514的底表面上(例如凹口514中的基底502上)以及凹口514的侧壁部分的主动区层504上。换句话说,层516形成或成长于由主动区层504形成的凹口514的侧壁的部分上。沉积工具102通过化学气相沉积技术或蚀刻机中的原位沉积步骤、上述与图1连结的沉积技术及/或其他沉积技术来沉积层516。

145.如图5c的剖面示意图510所示,层516形成于由主动区层504形成的凹口514的侧壁的部分上导致凹口514在主动区层504的部分之间的宽度缩小。此主动区层504的部分之间的宽度缩小使得形成于半导体装置中的存储器单元的单元尺寸缩小,这能够增加半导体装置的存储器单元密度以及增加半导体装置的装置效能。

146.在一些实施例中,沿主动区层504的主动区层504的部分之间的凹口514的初始宽度w1在约12nm至约220nm之间的范围中,且在沉积层516之后,取决于制程能力,沿主动区层504的主动区层504的部分之间的凹口514的宽度w2在约10nm至约200nm之间的范围中,以实现半导体装置的存储器单元(或其他电路结构)的特定尺寸及/或减少相邻切割主动区之间桥接的风险。然而,初始宽度w1和在沉积层516之后的宽度w2的其他数值也在本发明实施例的范围中。在一些实施例中,层516的厚度在约1nm至约10nm之间的范围中,以足够减少初始宽度w1。

147.层516包含碳化钨(w

xcy

)、氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)、氟碳(c

xfy

)聚合物及/或其他能够沉积和成长于主动区层504上的其他材料。在一些实施例中,层516包含氮化硼(b

x

ny),且层516通过在基底502上及主动区层504上(包含凹口514的侧壁的部分,此部分包含主动区层504)沉积氯化硼(bcl3)形成。氯化硼键结至基底502和主动区层504的表面。接着,以氮(n2)等离子体处理基底502和主动区层504的表面,以形成层516(有时也被称为氮化硼层)。

148.在一些实施例中,层516包含碳化钨(wc

x

),碳化钨通过沉积氟化钨前驱物(例如六氟化钨(wf6)或其他氟化钨)形成。氟化钨与氢氟烃(ch

xfy

,例如二氟甲烷(ch2f2))反应,以形成碳化钨。碳化钨形成作为在主动区层504上的非挥发副产物沉积层。

149.如图5c的剖面示意图512所示,层516的沉积操作导致蚀刻包含浅沟槽隔离层506的凹口514的侧壁部分,以移除包含浅沟槽隔离层506的凹口514的侧壁部分的材料。在一些实施例中,氯化硼(bcl3)接触并与浅沟槽隔离层506的氧化物材料反应。氧化物材料的氧与氯化硼之间的反应导致形成挥发性副产物氧氯化硼(bclo),这反应导致凹口514的宽度在浅沟槽隔离层506之间增加。这增加了凹口514的y方向宽度(例如横跨主动区层504和浅沟槽隔离层506的凹口514的宽度),这增加了形成切割主动区的制程裕度。

150.在使用碳化钨的实施例中,wfx接触并与浅沟槽隔离层506的氧化物材料反应。氧化物材料的氧与wfx之间的反应导致形成挥发性副产物四氟氧化钨(tungsten(vi)oxytetrafluoride(wof4)),这反应导致凹口514的宽度在浅沟槽隔离层506之间增加。这增加了凹口514的y方向宽度(例如横跨主动区层504和浅沟槽隔离层506的凹口514的宽度),这增加了形成切割主动区的制程裕度。之后,在将切割材料沉积于凹口514中之前,移除形成于主动区层504上的碳化钨(例如通过蚀刻或其他移除技术),这是由于碳化钨为较差的介电材料。在使用氟碳(c

xfy

)聚合物的实施例中,由于氟碳(c

xfy

)聚合物为较好的介电材料,因此氟碳(c

xfy

)聚合物可保留在凹口514中。

151.在一些实施例中,凹口514横跨主动区层504且在浅沟槽隔离层506之间的初始宽度w3在约6nm至约205nm之间的范围中,在层516的沉积操作之后,取决于制程能力,凹口514横跨主动区层504且在浅沟槽隔离层506之间的宽度w4在约8nm至约215nm之间的范围中,以实现半导体装置的存储器单元(或其他电路结构)的特定尺寸及/或减少相邻切割主动区之间桥接的风险。然而,初始宽度w3和在沉积操作之后的宽度w4的其他数值也在本发明实施例的范围中。

152.如图5d所示,从主动区层504的顶表面移除层516的多余或剩余的材料。在一些实施例中,蚀刻工具108或平坦化工具110进行平坦化或研磨操作,以从主动区层504的顶表面移除层516的多余或剩余的材料。

153.如图5e所示,以介电层填充凹口514,以在半导体装置的层516上方的凹口514中形成多个切割主动区518。切割主动区518可被称为鳍切割区或鳍切割隔离区。介电层可包含氧化物、氮化物及/或其他类型的介电材料。在一些实施例中,沉积工具102通过化学气相沉积技术、等离子体辅助化学气相沉积技术、原子层沉积技术、以上连结图1描述的沉积技术及/或其他沉积技术来沉积介电层,以在凹口514中形成切割主动区518。层516被包含在沿相同方向延伸的切割主动区518(或鳍切割隔离区)与相邻主动区层504(或相邻主动区)之间(如俯视图508所示)。在一些实施例中,层516也被包含在切割主动区518(或鳍切割隔离区)下方(例如切割主动区518(或鳍切割隔离区)与基底502之间)。

154.如上所述,提供图5a-图5e作为范例。其他范例可不同于参考图5a-图5e的描述。

155.图6a-图6e为本文描述的范例实施例600的图式。范例实施例600包含在半导体装置(例如半导体装置200及/或存储器单元300等)中形成一个或多个切割多晶硅区的范例。在一些实施例中,进行与图6a-图6e连结描述的操作,作为形成半导体装置的制程的一部分,例如连结图4所述的制程。在一些实施例中,进行与图6a-图6e连结描述的操作,作为连结图4描述的切割多晶硅区操作(方框412)的一部分。

156.如图6a所示,半导体装置包含基底602(例如半导体装置200的基底202)、多个多晶硅层604(例如半导体装置200的栅极218或虚设栅极)以及多个介电层606(例如半导体装置200的介电层208及/或其他介电层)。介电层606包含含氧化物介电层或其他类型的介电层。如半导体装置的俯视图608所示,多晶硅层604和介电层606沿第一方向(例如y方向)延伸。再者,多晶硅层604和介电层606在半导体装置中以交替图案排列。

157.图6a更显示在第一方向(例如y方向)沿多晶硅层604的半导体装置的一部分的剖面示意图610以及在第二方向(例如x方向)横跨多晶硅层604和多个介电层606的剖面示意图612,第二方向大致垂直于第一方向。如剖面示意图610和612所示,多晶硅层604和介电层

606被包含在基底602上方及/或基底602上。在一些实施例中,多晶硅层604和介电层606形成于半导体装置的其他结构及/或层上,例如主动区层、浅沟槽隔离层及/或切割主动区等。

158.在一些实施例中,取决于制程能力和半导体装置尺寸参数,多晶硅层604沿多晶硅层604的短尺寸方向(例如沿x方向)的宽度在约8nm至约200nm的范围中。然而,多晶硅层604的宽度的其他数值也在本发明实施例的范围中。在一些实施例中,取决于制程能力和多晶硅层604之间的间隔,介电层606沿介电层606的短尺寸方向(例如沿x方向)的宽度在约15nm至约200nm的范围中。然而,介电层606的宽度的其他数值也在本发明实施例的范围中。

159.如图6b所示,多个凹口614(或开口)形成通过一个或多个多晶硅层604的一部分以及通过多个介电层606的一部分。在一些实施例中,凹口614形成于基底602的一部分中。凹口614包含半导体装置的切割多晶硅区中将形成于其中的凹口。

160.在一些实施例中,使用光阻层中的图案来形成凹口614。在这些实施例中,沉积工具102在多晶硅层604上及介电层606上形成光阻层。曝光工具104将光阻层暴露于辐射源,以将光阻层图案化。显影工具106将光阻层显影并移除光阻层的一部分,以暴露图案。蚀刻工具108蚀刻通过多晶硅层604的一部分、介电层606的一部分,并进入基底602的一部分中,以形成凹口614。在一些实施例中,蚀刻操作包含等离子体蚀刻技术、湿化学蚀刻技术及/或其他类型的蚀刻技术。在一些实施例中,光阻移除工具移除光阻层的剩下部分(例如使用化学剥离剂、等离子体灰化及/或其他技术)。在一些实施例中,使用硬遮罩层用作基于图案形成凹口614的替代技术。

161.如图6c所示,层616形成于凹口614中。特别来说,层616沉积于凹口614的底表面上(例如凹口614中的基底602上)以及凹口614的侧壁部分的多晶硅层604上。换句话说,层616形成或成长于由多晶硅层604形成的凹口614的侧壁的部分上。沉积工具102通过化学气相沉积技术或蚀刻机中的原位沉积步骤、上述与图1连结的沉积技术及/或其他沉积技术来沉积层616。

162.如图6c的剖面示意图610所示,层616形成于由多晶硅层604形成的凹口614的侧壁的部分上导致凹口614在多晶硅层604的部分之间的宽度缩小。此多晶硅层604的部分之间的宽度缩小使得形成于半导体装置中的存储器单元的单元尺寸缩小,这能够增加半导体装置的存储器单元密度以及增加半导体装置的装置效能。

163.在一些实施例中,沿多晶硅层604的多晶硅层604的部分之间的凹口614的初始宽度w1在约12nm至约220nm之间的范围中,且在沉积层616之后,取决于制程能力,沿多晶硅层604的多晶硅层604的部分之间的凹口614的宽度w2在约10nm至约200nm之间的范围中,以实现半导体装置的存储器单元(或其他电路结构)的特定尺寸及/或减少相邻切割多晶硅区之间桥接的风险。然而,初始宽度w1和在沉积层616之后的宽度w2的其他数值也在本发明实施例的范围中。在一些实施例中,层616的厚度在约1nm至约10nm之间的范围中,以足够减少初始宽度w1。

164.层616包含碳化钨(w

xcy

)、氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)、氟碳(c

xfy

)聚合物及/或其他能够沉积和成长于多晶硅层604上的其他材料。在一些实施例中,层616包含氮化硼(b

x

ny),且层616通过在基底602上及多晶硅层604上(包含凹口614的侧壁的部分,此部分包含多晶硅层604)沉积氯化硼(bcl3)形成。氯化硼键结至基底602和多晶硅层604的表面。接着,以氮(n2)等离子体处理基底602和多晶硅层604的表面,以形成层616(有时也被称

为氮化硼层)。

165.在一些实施例中,层616包含碳化钨(wc

x

),碳化钨通过沉积氟化钨前驱物(例如六氟化钨(wf6)或其他氟化钨)形成。氟化钨与氢氟烃(ch

xfy

,例如二氟甲烷(ch2f2))反应,以形成碳化钨。碳化钨形成作为在多晶硅层604上的非挥发副产物沉积层。

166.如图6c的剖面示意图612所示,层616的沉积操作导致蚀刻包含介电层606的凹口514的侧壁部分,以移除包含介电层606的凹口614的侧壁部分的材料。在一些实施例中,氯化硼接触并与介电层606的氧化物材料反应。氧化物材料的氧与氯化硼之间的反应导致形成挥发性副产物氧氯化硼(bclo),这反应导致凹口614的宽度在介电层606之间增加。这增加了凹口614的x方向宽度,其增加了形成切割多晶硅区的制程裕度。

167.在一些实施例中,wf

x

接触并与介电层606的氧化物材料反应。氧化物材料的氧与wf

x

之间的反应导致形成挥发性副产物四氟氧化钨(tungsten(vi)oxytetrafluoride(wof4)),这反应导致凹口614的宽度在介电层606之间增加。这增加了凹口614的x方向宽度(例如横跨多晶硅层604和介电层606的凹口614的宽度),这增加了形成切割多晶硅区的制程裕度。之后,在将切割材料沉积于凹口614中之前,移除形成于多晶硅层604上的碳化钨(例如通过蚀刻或其他移除技术),这是由于碳化钨为较差的介电材料。在使用氟碳(c

xfy

)聚合物的实施例中,由于氟碳(c

xfy

)聚合物为较好的介电材料,因此氟碳(c

xfy

)聚合物可保留在凹口614中。

168.在一些实施例中,凹口614横跨多晶硅层604且在介电层606之间的初始宽度w3在约10nm至约220nm之间的范围中,在层616的沉积操作之后,取决于制程能力,凹口614横跨多晶硅层604且在介电层606之间的宽度w4在约15nm至约225nm之间的范围中,以实现半导体装置的存储器单元(或其他电路结构)的特定尺寸及/或减少相邻切割多晶硅区之间桥接的风险。然而,初始宽度w3和在沉积操作之后的宽度w4的其他数值也在本发明实施例的范围中。

169.如图6d所示,从多晶硅层604的顶表面移除层616的多余或剩余的材料。在一些实施例中,蚀刻工具108或平坦化工具110进行平坦化或研磨操作,以从多晶硅层604的顶表面移除层616的多余或剩余的材料。

170.如图6e所示,以介电层填充凹口614,以在半导体装置的层616上方的凹口614中形成多个切割多晶硅区618。切割多晶硅区618可被称为栅极切割隔离区或栅极隔离区。介电层可包含氧化物、氮化物及/或其他类型的介电材料。在一些实施例中,沉积工具102通过化学气相沉积技术、等离子体辅助化学气相沉积技术、原子层沉积技术、以上连结图1描述的沉积技术及/或其他沉积技术来沉积介电层,以在凹口614中形成切割多晶硅区618(或栅极切割隔离区或栅极隔离区)。层616被包含在沿相同方向延伸的切割多晶硅区618(或栅极切割隔离区或栅极隔离区)与相邻多晶硅层604(或相邻多晶硅区)之间(如俯视图608所示)。在一些实施例中,层616也被包含在切割多晶硅区618(或栅极切割隔离区或栅极隔离区)下方(例如切割多晶硅区618(或栅极切割隔离区或栅极隔离区)与基底602之间)。

171.如上所述,提供图6a-图6e作为范例。其他范例可不同于参考图6a-图6e的描述。

172.图7a-图7f为本文描述的范例实施例700的图式。范例实施例700包含在半导体装置(例如半导体装置200及/或存储器单元300等)中形成一个或多个源极或漏极接点(源极或漏极接点216)的范例。在一些实施例中,进行与图7a-图7f连结描述的操作,作为形成半

导体装置的制程的一部分,例如连结图4所述的制程。在一些实施例中,进行与图7a-图7f连结描述的操作,作为连结图4描述的源极/漏极接点(md)形成操作(方框430)的一部分。

173.如图7a所示,半导体装置包含基底702(例如半导体装置200的基底202)、多个层间介电层704(例如半导体装置200的介电层208及/或其他介电层)、多个牺牲层结构(sacrificial layer structures,sac)706、多个间隙壁708以及多个切割金属漏极(cut metal drain,cmd)区710。

174.如半导体装置的俯视图712所示,层间介电层704、牺牲层结构706和间隙壁708沿第一方向(例如y方向)延伸。层间介电层704和牺牲层结构706在半导体装置中以交替图案排列,其中间隙壁708被包含在层间介电层704与牺牲层结构706之间。再者,如俯视图712所示,切割金属漏极区710大致垂直于层间介电层704、牺牲层结构706和间隙壁708之上及/或上方排列。切割金属漏极区710沿第二方向(例如x方向)延伸。切割金属漏极区710也可被称为接触端切割(contact end cut),且可用于蚀刻层间介电层704,以准备形成半导体装置的源极或漏极接点。

175.图7a更显示在第一方向(例如y方向)沿层间介电层704的半导体装置的一部分的剖面示意图714以及在第二方向(例如x方向)横跨层间介电层704和多个牺牲层结构706的剖面示意图716,第二方向大致垂直于第一方向。如剖面示意图714和716所示,层间介电层704、牺牲层结构706、间隙壁708和切割金属漏极区710被包含在基底602上方。在一些实施例中,层间介电层704、牺牲层结构706、间隙壁708和切割金属漏极区710形成于半导体装置的其他结构及/或层上,例如主动区层、浅沟槽隔离层及/或切割主动区等。

176.再者,如剖面示意图714和716所示,半导体装置包含用于蚀刻各层以形成半导体装置的一个或多个结构的一个或多个硬遮罩层718及/或720。切割金属漏极区710被包含在一个或多个硬遮罩层718及/或720上方及/或一个或多个硬遮罩层718及/或720上。鳍结构722(例如半导体装置200的鳍结构204)形成于基底702中,且外延区724(例如半导体装置200的外延区214)部分围绕鳍结构722。外延区724以底部对比加强层(bottom contrast enhancement layer,bcel)726作为衬垫,底部对比加强层726可包含聚合物和溶剂等。如剖面示意图716所示,牺牲层结构706被包含在栅极728上方及/或栅极728上。包含的牺牲层结构(sac)706用于制造外延区724,使得外延区724可较靠近栅极728(其允许包含在其中的半导体装置200的尺寸缩小)。牺牲层结构706可通过将层间介电层704图案化来制造。牺牲层结构706可包含氮化物,氮化物具有与层间介电层704具有好的蚀刻选择性。蚀刻选择性改善了外延区724的制程裕度。在一些实施例中,牺牲层结构706可包含栅极盖绝缘层。相邻的栅极728可通过切割多晶硅区618电性隔离。因此,被包含在切割多晶硅区618与栅极728之间、切割多晶硅区618与栅极728之间的层616(例如氮化硼层或相似类型的层),其中栅极728和另一个栅极728在相同方向延伸。

177.如图7b所示,将层间介电层704在切割金属漏极区710之间的部分向下蚀刻至外延区724上方的间隙壁708以及外延区724上的底部对比加强层726。蚀刻工具108通过一个或多个硬遮罩层718和720、切割金属漏极区710及/或形成于层间介电层704上方及/或层间介电层704上的光阻层中的图案来蚀刻凹口730(或开口)至层间介电层704的一部分中及/或通过层间介电层704的一部分。层间介电层704在切割金属漏极区710下方的剩下部分提供将形成于相邻凹口730中的源极或漏极接点之间的电性隔离。

178.如图7c所示,多个层732形成于凹口730中的侧壁和底表面上。特别来说,层732沉积于凹口730中的侧壁和底表面上的间隙壁708上。在一些实施例中,沉积工具102通过化学气相沉积技术、物理气相沉积技术、原子层沉积技术、以上连结图1描述的沉积技术及/或其他沉积技术来沉积层732。层732包含碳化钨(w

xcy

)、氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)、氟碳(c

xfy

)聚合物及/或其他能够沉积和成长于间隙壁708(间隙壁708包含氮化物材料,例如氮化硅(si

x

ny)或其他氮化物材料)上的其他材料。在一些实施例中,层732包含氮化硼(b

x

ny),且层732通过在凹口730中的间隙壁708上沉积氯化硼(bcl3)形成。氯化硼键结至间隙壁708的表面。接着,以氮(n2)等离子体处理间隙壁708的表面,以形成层732(有时也被称为氮化硼层)。

179.在一些实施例中,层732包含碳化钨(wc

x

),碳化钨通过沉积氟化钨前驱物(例如六氟化钨(wf6)或其他氟化钨)形成。氟化钨与氢氟烃(ch

xfy

,例如二氟甲烷(ch2f2))反应,以形成碳化钨。碳化钨形成作为在间隙壁708上的非挥发副产物沉积层。之后,在将切割材料沉积于凹口730中之前,移除形成于间隙壁708上的碳化钨(例如通过蚀刻或其他移除技术),这是由于碳化钨为较差的介电材料。在使用氟碳(c

xfy

)聚合物的实施例中,由于氟碳(c

xfy

)聚合物为较好的介电材料,因此氟碳(c

xfy

)聚合物可保留在凹口730中。

180.如图7c的剖面示意图714所示,层732的沉积操作导致蚀刻包含层间介电层704的凹口730的侧壁部分,以移除包含层间介电层704的凹口730的侧壁部分的材料。在一些实施例中,氯化硼接触并与层间介电层704的氧化物材料反应。氧化物材料的氧与氯化硼之间的反应导致形成挥发性副产物氧氯化硼(bclo),这反应导致层间介电层704在切割金属漏极区710下方的部分的宽度缩小。在一些实施例中,wf

x

接触并与层间介电层704的氧化物材料反应。氧化物材料的氧与wf

x

之间的反应导致形成挥发性副产物四氟氧化钨(wof4),这反应导致层间介电层704在切割金属漏极区710下方的部分的宽度缩小。这减少了半导体装置相邻源极或漏极接点之间的y方向间距,这减少了源极或漏极接点的接触电阻。

181.在一些实施例中,层间介电层704在切割金属漏极区710下方的部分的初始宽度w1在约15nm至约300nm之间的范围中,且在层732的沉积操作之后,取决于制程能力,层间介电层704在切割金属漏极区710下方的部分的宽度w2在约10nm至约295nm之间的范围中,以实现源极或漏极区的特定接触电阻,及/或减少漏极到漏极漏电的可能性。然而,初始宽度w1和在沉积操作之后的宽度w2的其他数值也在本发明实施例的范围中。

182.如图7c的剖面示意图716所示,层732形成于凹口730中的间隙壁708上,导致凹口730在间隙壁708的部分之间的宽度缩小。此宽度缩小使得形成于半导体装置中的存储器单元的单元尺寸缩小,这能够增加半导体装置的存储器单元密度以及增加半导体装置的装置效能。

183.在一些实施例中,凹口730在凹口730的侧壁上的间隙壁708的表面之间的初始宽度w3在约10nm至约200nm之间的范围中,在层732的沉积之后,取决于制程能力,凹口730的宽度w4在约9nm至约190nm之间的范围中,以实现半导体装置的存储器单元(或其他电路结构)的特定尺寸及/或减少相邻切割多晶硅区之间桥接的风险。然而,初始宽度w3和在沉积层732之后的宽度w4的其他数值也在本发明实施例的范围中。在一些实施例中,层732的厚度在约1nm至约10nm之间的范围中,以足以减少初始宽度w3。

184.如图7d所示,从牺牲层结构706的顶表面以及间隙壁708的顶表面移除层732的多

余或剩余的材料。在一些实施例中,蚀刻工具108进行蚀刻或清洁操作,以移除层732的多余或剩余的材料。再者,如第7d图所示,形成到达外延区724的开口734,以准备形成连接至外延区724的源极或漏极接点。开口734形成于凹口730中,通过层732、间隙壁708以及位于凹口730底部的底部对比加强层726。

185.在一些实施例中,使用光阻层中的图案来形成开口734。在这些实施例中,沉积工具102在牺牲层结构706、间隙壁708及/或半导体装置的其他部分上形成光阻层。曝光工具104将光阻层暴露于辐射源,以将光阻层图案化。显影工具106将光阻层显影并移除光阻层的一部分,以暴露图案。蚀刻工具108蚀刻通过层732、间隙壁708以及位于凹口730底部的底部对比加强层726,以形成开口734。在一些实施例中,蚀刻操作包含等离子体蚀刻技术、湿化学蚀刻技术及/或其他类型的蚀刻技术。在一些实施例中,光阻移除工具移除光阻层的剩下部分(例如使用化学剥离剂、等离子体灰化及/或其他技术)。在一些实施例中,使用硬遮罩层用作基于图案形成开口734的替代技术。

186.如图7e所示,硅化物层736形成于外延区724上的开口734中。硅化物层736包含金属硅化物,例如硅化钴或硅化镍等。硅化物层736被包含在外延区724上,以减少外延区724与将形成于外延区724上方的源极或漏极接点之间的接触电阻。沉积工具102及/或镀覆工具112通过化学气相沉积技术、物理气相沉积技术、原子层沉积技术、电镀技术、以上连结图1描述的沉积技术及/或其他沉积技术来沉积硅化物层736。

187.如图7f所示,源极或漏极接点738形成于硅化物层736上方及/或硅化物层736上的凹口730中。沉积工具102及/或镀覆工具112通过化学气相沉积技术、等离子体辅助化学气相沉积技术、原子层沉积技术、电镀技术、以上连结图1描述的沉积技术及/或其他沉积技术来沉积源极或漏极接点738。

188.如上所述,提供图7a-图7f作为范例。其他范例可不同于参考图7a-图7f的描述。

189.图8a-图8d为本文描述的范例实施例800的图式。范例实施例800包含氮化硼(b

x

ny)层的形成制程,可使用氮化硼层的形成制程来形成本文描述的各种氮化硼层。如图8a所示,范例实施例800包含氧化层802和氮化层804。在一些实施例中,氧化层802包含本文描述的浅沟槽隔离层506、本文描述的介电层606及/或本文描述的介电层704等。在一些实施例中,氮化层804包含本文描述的主动区层504、本文描述的多晶硅层604及/或本文描述的间隙壁708等。

190.如图8a所示,氮化硼层的形成制程包含沉积操作或蚀刻机中的原位沉积步骤(例如通过沉积工具102或蚀刻工具108来进行),其中在氧化层802的表面上以及氮化层804的表面上沉积氯化硼(bcl3)806。氯化硼806通过化学气相沉积或蚀刻工具108的原位沉积步骤及/或其他沉积技术来沉积。氯化硼806与氧化层802的氧808反应以及氮化层804的氮810反应。

191.如图8b所示,氧化层802中的氧808与氯化硼806之间的反应,导致形成氧化层802中的凹口812。氧化层802的材料通过氯化硼806移除,以形成凹口812。氧808与氯化硼806的结合形成挥发性副产物氧氯化硼(bclo)814。

192.再者,如图8b所示,氮化层804中的氮810与氯化硼806之间的反应,导致氮化层804的表面上的氮810与氯化硼806中的硼之间形成氮-硼键816。氮-硼键816的形成导致副产物氯化氢的形成。

193.如图8c所示,以氮(n2)等离子体820处理氮化层804的表面。氮等离子体820促进氮化层804的表面上的氮-硼键816的成长。在替代的实施例中,氮化层804不包含氮化物,而包含硅层。在这些替代的实施例中,氯化硼806的氯与氢键结,以形成氯化氢副产物,且使用氮等离子体820在硅层的表面上形成氮-硼键816,这导致在硅层上形成氮化硼层。

194.如图8d所示,使用氮等离子体820的表面处理导致在氮化层804上形成氮化硼层822。氮化硼层822包含六角形结构。氮化硼层822具有相对大的崩溃电压、平面外(out-of-plane)介电常数约3.29(对于单层六方氮化硼(hexagonal boron nitride,h-bn))至约3.76(对于块状六方氮化硼)以及平面内(in-plane)介电常数约6.82(对于单层六方氮化硼)至约6.93(对于块状六方氮化硼)。

195.在一些实施例中,氯化硼沉积操作以及氮等离子体处理操作的时间在约10秒至约600秒的范围中,以在氮化层804上形成氮化硼层822至特定厚度及/或在氧化层802中形成凹口812至特定深度。在一些实施例中,氯化硼806与氮等离子体820之间的比例在约0.1至约10的范围中,以实现氮化硼层822的特定硼浓度及/或特定氮浓度。

196.如上所述,提供图8a-图8d作为范例。其他范例可不同于参考图8a-图8d的描述。

197.图9为装置900的范例组件的图式。在一些实施例中,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)及/或晶圆/晶粒转移工具114包含一个或多个装置900及/或装置900的一个或多个组件。如图9所示,装置900可包含汇流排910、处理器920、存储器930、存储组件940、输入组件950、输出组件960及/或通信组件970。

198.汇流排910包含能够实现在装置900的组件之间的有线及/或无线通信的组件。处理器920包含中央处理单元、图形处理单元、微处理器、控制器、微控制器、数字信号处理器、现场可编程栅极阵列、专用集成电路及/或其他类型的处理器组件。处理器920以硬件、固件或硬件和软件的组合来实现。在一些实施例中,处理器920包含能够编程以进行功能的一个或多个处理器。存储器930包含随机存取存储器、唯读存储器及/或其他类型的存储器(例如快闪存储器、磁存储器及/或光存储器)。

199.存储组件940存储有关于装置900的操作的信息及/或软件。举例来说,存储组件940可包含硬盘机、磁盘机、光盘机、固态硬盘、光盘片、数字多功能影音光盘及/或其他类型的非暂存性电脑可读取记录媒体。输入组件950使装置900能够接收输入,例如使用者输入及/或感应输入。举例来说,输入组件950可包含触控屏幕、键盘、小键盘、鼠标、按钮、麦克风、开关、感测器、全球定位系统组件、加速计、陀螺仪及/或致动器。输出组件960使装置900能够提供输出,例如通过显示器、喇叭及/或一个或多个发光二极管。通信组件970使装置900能够与其他装置通信,例如通过有线连接及/或无线连接。举例来说,通信组件970可包含接收器、传送器、收发器、数据机、网络接口卡及/或天线。

200.装置900可进行本文描述的一个或多个制程。举例来说,非暂存性电脑可读取记录媒体(例如存储器930及/或存储组件940)可存储一组指令(例如一个或多个指令、代码、软件码及/或程序码)以供处理器920执行。处理器920可执行此组指令,以进行本文描述的一个或多个制程。在一些实施例中,通过一个或多个处理器920执行此组指令,导致一个或多个处理器920及/或装置900进行本文描述的一个或多个制程。在一些实施例中,固线式电路(hardwired circuitry)可以代替指令或与指令组合使用,以进行本文描述的一个或多个

制程。

201.图9所示的组件的数量和排列仅供范例。相较于图9的所示的装置,装置900可包含额外的组件、较少的组件、不同的组件或不同排列的组件。

202.额外地或替代地,装置900的一组组件(例如一个或多个组件)可进行一个或多个被描述为由装置900的另一组组件进行的功能。

203.图10为关于形成本文描述的半导体装置的范例制程1000的流程图。在一些实施例中,图10的一个或多个制程方框可通过一个或多个半导体加工工具(例如半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个))进行。额外地或替代地,图10的一个或多个制程方框可通过装置900的一个或多个组件来进行,例如处理器920、存储器930、存储组件940、输入组件950、输出组件960及/或通信组件970。

204.如图10所示,制程1000可包含在外延区上方形成通过介电层到达间隙壁的开口(方框1010)。举例来说,如上所述,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在外延区724上方形成通过介电层704到达间隙壁708的开口(例如凹口730)。

205.再者,如图10所示,制程1000可包含在开口的底部的间隙壁上以及沿开口的侧壁的间隙壁上形成层(方框1020)。举例来说,如上所述,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在开口的底部的间隙壁708上以及开口的侧壁的间隙壁708上形成层732。在一些实施例中,层通过在间隙壁上沉积前驱物,并以等离子体处理前驱物来形成。在一些实施例中,层减少开口沿大致垂直于介电层的第一方向的第一宽度。在一些实施例中,前驱物从开口的侧壁移除材料,以增加开口沿大致平行于介电层的第二方向的第二宽度。

206.再者,如图10所示,制程1000可包含蚀刻通过在开口的底部的层,以及通过间隙壁到达外延区(方框1030)。举例来说,如上所述,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可蚀刻通过在开口的底部的层732,以及通过间隙壁708到达外延区724。

207.制程1000可包含额外的实施例,例如任何单一实施例或以下描述的实施例的组合及/或结合本文别处描述的一个或多个其他制程。

208.在第一实施例中,制程1000包含在蚀刻通过在开口的底部的层732,以及通过间隙壁708到达外延区724之后,在外延区724上方的开口中形成源极或漏极接点738。在第二实施例中,单独或结合第一实施例,外延区724包含鳍式场效晶体管的源极区或漏极区(例如被包含在半导体装置200或存储器单元300中)。在第三实施例中,单独或结合第一实施例和第二实施例的一个或多个,层732的材料包含碳化钨(w

xcy

)、氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)、氟碳(c

xfy

)聚合物的至少一种。

209.在第四实施例中,单独或结合第一实施例到第三实施例的一个或多个,在形成层732期间,减少了相邻开口之间通过介电层704的切割金属漏极区710的宽度w1。在第五实施例中,单独或结合第一实施例到第四实施例的一个或多个,层732减少开口的宽度w3。

210.在第六实施例中,单独或结合第一实施例到第五实施例的一个或多个,形成层732包含在间隙壁708上沉积氯化硼(bcl3)806作为前驱物,其中氯化硼806在间隙壁708的表面

上与氮810键结,且以氮(n2)等离子体820处理间隙壁708的表面,以形成层732,其中间隙壁708的表面上的氮810和氮等离子体820与氯化硼806反应,以形成氮化硼(b

x

ny)822。在第七实施例中,单独或结合第一实施例到第六实施例的一个或多个,氯化硼806与介电层704中的氧808反应,以移除介电层704的一个或多个部分。

211.在第八实施例中,单独或结合第一实施例到第七实施例的一个或多个,第二宽度增加,导致用于金属源极或漏极接点的宽度增加,这减少了金属源极或漏极接点的接触电阻。在第九实施例中,单独或结合第一实施例到第八实施例的一个或多个,形成层包含在间隙壁的表面上沉积六氟化钨(wf6)作为前驱物,以二氟甲烷(ch2f2)处理间隙壁的表面,其中六氟化钨的钨与间隙壁的表面上的二氟甲烷反应,以形成碳化钨(wc

x

)作为层,其中六氟化钨与介电层中的氧反应,以移除介电层的一个或多个部分,且六氟化钨和氧形成挥发性副产物四氟氧化钨(tungsten(vi)oxytetrafluoride(wof4))。

212.虽然图10显示制程1000的范例方框,但是在一些实施例中,相较于图10,制程1000可包含额外的方框、较少的方框、不同的方框或不同排列的方框。额外地或替代地,可并行制程1000的两个或更多个方框。

213.图11为关于形成本文描述的半导体装置的范例制程1100的流程图。在一些实施例中,图11的一个或多个制程方框可通过一个或多个半导体加工工具(例如半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个))进行。额外地或替代地,图11的一个或多个制程方框可通过装置900的一个或多个组件来进行,例如处理器920、存储器930、存储组件940、输入组件950、输出组件960及/或通信组件970。

214.如图11所示,制程1100可包含形成凹口通过半导体装置的第一层的一部分,通过相邻于第一层的半导体装置的第二层的一部分,并进入第一层和第二层下方的半导体装置的基底的一部分中(方框1110)。举例来说,如上所述,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可形成凹口(例如凹口514和614)通过半导体装置200的第一层(例如主动区层504、多晶硅层604)的一部分,通过相邻于第一层的半导体装置200的第二层(例如浅沟槽隔离层506、介电层606)的一部分,并进入第一层和第二层下方的半导体装置200的基底(例如基底202、502、602)的一部分中。在一些实施例中,凹口包含对应至第一层的第一组侧壁以及对应第二层的第二组侧壁。

215.再者,如图11所示,制程1100可包含在凹口中的第一层的第一组侧壁上形成第三层(方框1120)。举例来说,如上所述,半导体加工工具(例如沉积工具102、曝光工具104、显影工具106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在凹口中的第一层的第一组侧壁上形成第三层(例如层516、层616)。在一些实施例中,使用前驱物来形成第三层,其中前驱物与第一层的第一材料和氮等离子体的组合反应,以在凹口中的第一层的第一组侧壁上形成第三层。在一些实施例中,第三层减少了凹口在第一组侧壁之间的第一宽度。在一些实施例中,前驱物与第二层的第二材料反应,以蚀刻凹口中的第二层的第二组侧壁,这增加了凹口在第二组侧壁之间的第二宽度。

216.再者,如图11所示,制程1100可包含在第三层上方以介电材料填充凹口(方框1130)。举例来说,如上所述,半导体加工工具(例如沉积工具102、曝光工具104、显影工具

106、蚀刻工具108、平坦化工具110、镀覆工具112的一个或多个)可在第三层上方以介电材料(例如切割主动区518(或鳍切割隔离区)、切割多晶硅区618(或栅极切割隔离区或栅极隔离区))填充凹口。

217.制程1100可包含额外的实施例,例如任何单一实施例或以下描述的实施例的组合及/或结合本文别处描述的一个或多个其他制程。

218.在第一实施例中,第三层的材料包含碳化钨(w

xcy

)、氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)或氟碳(c

xfy

)聚合物的至少一种。在第二实施例中,单独或结合第一实施例,第一层包含主动区层504,第二层包含浅沟槽隔离层506,且介电材料包含切割主动区518(或鳍切割隔离区)。

219.在第三实施例中,单独或结合第一实施例和第二实施例的一个或多个,第一层包含多晶硅层604,第二层包含介电层,且介电材料包含切割多晶硅区618(或栅极切割隔离区或栅极隔离区)。在第四实施例中,单独或结合第一实施例到第三实施例的一个或多个,凹口的第一宽度(例如凹口514的宽度w1、凹口614的宽度w1)沿第一层延伸,并包含对应至介电材料的切割区的x方向宽度;凹口的第二宽度(例如凹口514的宽度w2、凹口614的宽度w2)横跨第一层,并包含切割区的y方向宽度,第三层减少切割区的临界尺寸。在第五实施例中,单独或结合第一实施例到第四实施例的一个或多个,形成第三层包含形成第三层至厚度在约1nm至约10nm的范围中。

220.虽然图11显示制程1010的范例方框,但是在一些实施例中,相较于图11,制程1100可包含额外的方框、较少的方框、不同的方框或不同排列的方框。额外地或替代地,可并行制程1100的两个或更多个方框。

221.图12为本文描述的范例实施例1200的图式。范例实施例1200包含用以形成本文描述的各种碳化钨层的例示性碳化钨(wc

x

)层形成制程。如图12所示,范例实施例1200包含氮化层1202(其可替代地包含硅层)和氧化层1204。在一些实施例中,氧化层包含本文描述的浅沟槽隔离层506、本文描述的介电层606及/或本文描述的介电层704等。在一些实施例中,氮化层1202(或硅层)包含本文描述的主动区层504、本文描述的多晶硅层604及/或本文描述的间隙壁708等。

222.如图12所示,碳化钨层形成制程包含沉积操作或蚀刻机中的原位沉积步骤(例如通过沉积工具102或蚀刻工具108来进行),其中在氧化层1204的表面上以及氮化层1202的表面上沉积六氟化钨(wf6)。六氟化钨1206通过化学气相沉积或蚀刻工具108的原位沉积步骤及/或其他沉积技术来沉积。六氟化钨1206与氧化层1204的氧反应,以形成挥发性副产物四氟氧化钨1208,这导致蚀刻氧化层1204。

223.再者,如图12所示,六氟化钨1206中的氟与氮化层1202的表面上的氢键结,以形成氢氟酸(hf)1210。再者,氢氟烃1212(提供ch

xfy

,例如二氟甲烷(ch2f2),ch

xfy

也与氮化层1202的表面上的氢键结,以形成氢氟酸(hf))。氢氟烃1212中的碳与六氟化钨1206中的钨键结,以在氮化层1202的表面上形成六氟化钨(wf6)。

224.如上所述,提供图12作为范例。其他范例可不同于参考图12的描述。

225.以此方式,本文描述的各种半导体技术能够缩小鳍式场效晶体管(及/或其他类型的半导体晶体管)的一个或多个尺寸及/或增加鳍式场效晶体管的一个或多个尺寸。在本文描述的各种实施例中,可使用氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)(例如氧化硼

(b2o3))、氟碳(c

xfy

)聚合物及/或其他材料,以通过选择性沉积来缩小鳍式场效晶体管的一个或多个x方向尺寸,而通过蚀刻来增加或扩大鳍式场效晶体管的一个或多个y方向尺寸。举例来说,鳍式场效晶体管的金属漏极的x方向尺寸、鳍式场效晶体管的主动区的x方向尺寸及/或鳍式场效晶体管的多晶区的x方向尺寸可通过选择性沉积氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)(例如氧化硼(b2o3))、氟碳(c

xfy

)聚合物及/或其他材料来增加。此选择性沉积通过蚀刻可允许鳍式场效晶体管的一个或多个y方向尺寸增加。以此方式,使用本文描述的技术缩小鳍式场效晶体管的一个或多个x方向尺寸可允许缩小互补式金属氧化物半导体逻辑装置尺寸(例如,静态随机存取存储器装置及/或其他类型的存储器装置的单元尺寸)。再者,使用本文描述的技术增加鳍式场效晶体管的一个或多个y方向尺寸可允许扩大各种半导体制程裕度,其可增加半导体制造品质以及半导体制造产率。

226.如上所述,本文描述的一些实施例提供方法,此方法包含在外延区上方形成通过介电层到达间隙壁的开口。此方法包含在开口的底部的间隙壁上及沿开口的侧壁的间隙壁上形成层。通过在间隙壁上沉积前驱物,并以等离子体处理前驱物来形成层,层减少开口沿第一方向的第一宽度,第一方向大致垂直于介电层。前驱物从开口的侧壁移除材料,以增加开口沿第二方向的第二宽度,第二方向大致平行于介电层。此方法包含蚀刻通过在开口的底部的层以及间隙壁,以到达外延区。

227.在一些其他实施例中,上述方法更包含:在蚀刻通过在开口的底部的层和间隙壁到达外延区之后,在外延区上方的开口中形成金属源极或漏极接点。

228.在一些其他实施例中,其中第二宽度增加导致金属源极或漏极接点的宽度增加,这减少了金属源极或漏极接点的接触电阻。

229.在一些其他实施例中,其中层的材料包含以下至少一者:碳化钨(w

xcy

)、氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)或氟碳(c

xfy

)聚合物。

230.在一些其他实施例中,其中在形成层期间,通过介电层在相邻开口之间的切割金属漏极区的宽度缩小。

231.在一些其他实施例中,其中形成层的步骤包含:在间隙壁上沉积氯化硼作为前驱物,其中氯化硼与间隙壁的表面上的氮键结;以及以氮等离子体处理间隙壁的表面,以形成层,其中间隙壁的表面上的氮和氮等离子体与氯化硼反应,以形成氮化硼。

232.在一些其他实施例中,其中氯化硼与介电层中的氧反应,以移除介电层的一个或多个部分。

233.在一些其他实施例中,其中形成层的步骤包含:在间隙壁的表面上沉积六氟化钨作为前驱物;以二氟甲烷处理间隙壁的表面,其中六氟化钨的钨与间隙壁的表面上的二氟甲烷反应,以形成碳化钨作为层,其中六氟化钨与介电层中的氧反应,以移除介电层的一个或多个部分,且其中六氟化钨与氧形成挥发性副产物四氟氧化钨。

234.如上所述,本文描述的一些实施例提供方法,此方法包含形成凹口,凹口通过半导体装置的第一层的一部分、相邻于第一层的半导体装置的第二层的一部分,并进入第一层和第二层下方的半导体装置的基底的一部分中。凹口包含对应第一层的第一组侧壁和对应第二层的第二组侧壁。此方法包含在凹口中的第一层的第一组侧壁上形成第三层。使用前驱物来形成第三层,其中前驱物与第一层的第一材料和氮等离子体的组合反应,以在凹口中的第一层的第一组侧壁上形成第三层。第三层减少凹口在第一组侧壁之间的第一宽度。

前驱物与第二层的第二材料反应,以蚀刻凹口中的第二层的第二组侧壁,这增加了凹口在第二组侧壁之间的第二宽度。此方法包含在第三层上方以介电材料填充凹口。

235.在一些其他实施例中,其中第三层的材料包含以下至少一者:碳化钨(w

xcy

)、氮化硼(b

x

ny)、碳化硼(b

x

c)、氧化硼(b

x

oy)或氟碳(c

xfy

)聚合物。

236.在一些其他实施例中,其中第一层包含主动区层,其中第二层包含浅沟槽隔离层,且其中介电材料包含切割主动区。

237.在一些其他实施例中,其中第一层包含多晶硅层,其中第二层包含介电层,其中介电材料包含切割多晶硅区。

238.在一些其他实施例中,其中凹口的第一宽度沿第一层延伸,并包含对应介电材料的切割区的x方向宽度,其中凹口的第二宽度横跨第一层,并包含切割区的y方向宽度,且其中第三层减少切割区的临界尺寸。

239.在一些其他实施例中,其中形成第三层的步骤包含:形成第三层至厚度在约1nm至约10nm的范围中。

240.如上所述,本文描述的一些实施例提供半导体装置,半导体装置包含第一主动区和第二主动区,位于半导体装置的基底上沿第一方向延伸。半导体装置包含鳍切割隔离区,位于第一主动区与第二主动区之间。半导体装置包含源极或漏极区,位于第一主动区和第二主动区中。半导体装置包含接点,电性连接至源极或漏极区。半导体装置包含浅沟槽隔离层,相邻于第一主动区和第二主动区。半导体装置包含第一栅极区和第二栅极区,沿垂直于第一方向的第二方向延伸。半导体装置包含栅极切割隔离区,位于第一栅极区与第二栅极区之间。半导体装置包含以下至少一者:第一氮化硼层,位于接点及与接点有关联的间隙壁之间;第二氮化硼层,位于第一鳍切割隔离区与第一主动区之间以及鳍切割隔离区与第二主动区之间;或第三氮化硼层,位于栅极切割隔离区与第一栅极区之间以及栅极切割隔离区与第二栅极区之间。

241.在一些其他实施例中,上述半导体装置更包含:第一氮化层,且其中相邻于第一氮化层的接点的宽度在约9nm至约190nm的范围中。

242.在一些其他实施例中,上述半导体装置更包含:第二氮化硼层,且其中相邻于第二氮化硼层的鳍切割隔离区的第一宽度在约5nm至约200nm的范围中,且其中鳍切割隔离区的第二宽度在约8nm至约225nm的范围中。

243.在一些其他实施例中,其中第二氮化硼层在鳍切割隔离区与基底之间,且其中第三氮化硼层在栅极切割隔离区与基底之间。

244.在一些其他实施例中,上述半导体装置更包含:第三氮化硼层,且其中相邻于第三氮化硼层的栅极切割隔离区的宽度在约10nm至约200nm的范围中。

245.在一些其他实施例中,其中栅极切割隔离区的另一宽度在约15nm至约225nm的范围中。

246.前述内文概述了许多实施例的特征,使本技术领域中具有通常知识者可以从各个方面更加了解本发明实施例。本技术领域中具有通常知识者应可理解,且可轻易地以本发明实施例为基础来设计或修饰其他制程及结构,并以此达到相同的目的及/或达到与在此介绍的实施例等相同的优点。本技术领域中具有通常知识者也应了解这些相等的结构并未背离本发明的发明精神与范围。在不背离本发明的发明精神与范围的前提下,可对本发明

实施例进行各种改变、置换或修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1