半导体封装装置的制作方法

本公开涉及半导体封装,具体涉及半导体封装装置。

背景技术:

1、随着smt(surface mounted technology,表面贴装技术)的组件component密度逐渐升高,组件之间的空间也变得更密集,组件与组件之间的基板线路的空间也因此被压缩,目前组件之间的连接焊盘terminal pad可通过共用焊盘pad的形式实现。

2、然而,共用pad的设计会让在其上面的焊料solder在高温回焊时的锡分布与流动不均,造成组件倾斜tilt与单边移动shift的问题,进而导致组件在面临dsm(double sidemolding,双面塑封)的研磨grinding制程时会有损坏的风险。

技术实现思路

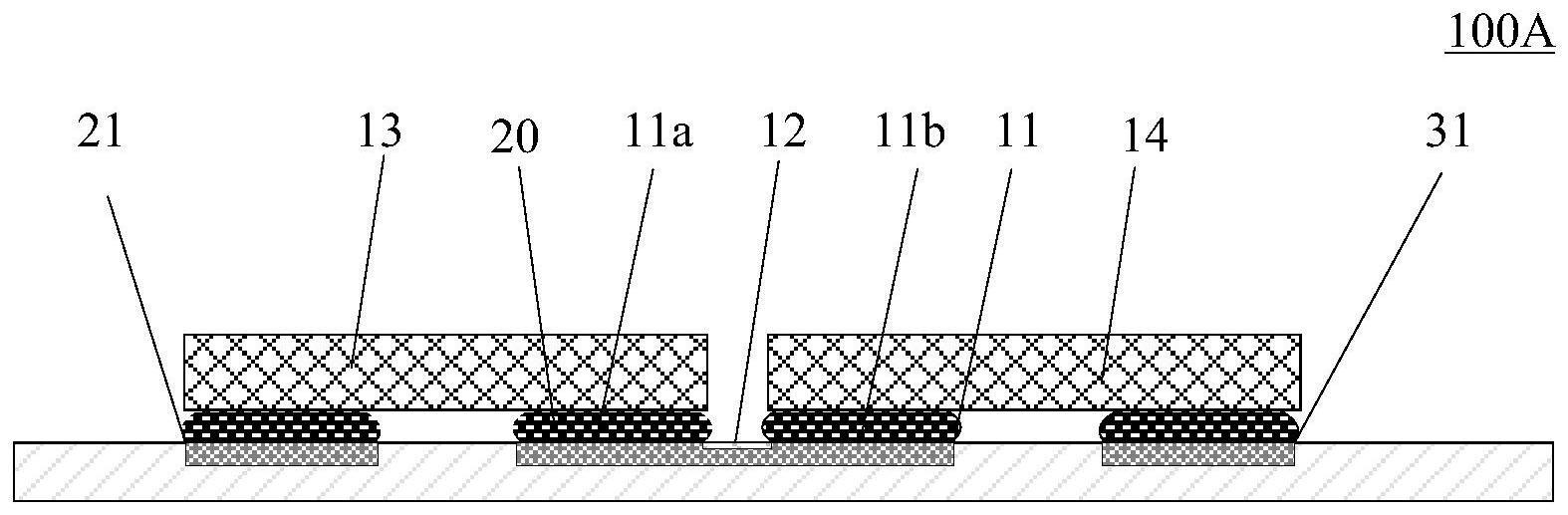

1、本公开提供了一种半导体封装装置,包括:

2、共用焊盘,表面设置有第一区域、第二区域及阻挡结构,所述阻挡结构区隔所述第一区域和所述第二区域;

3、所述第一区域和所述第二区域上分别设置有焊接材料,所述阻挡结构能够阻挡设置于所述第一区域和所述第二区域的焊接材料。

4、在一些可选的实施方式中,所述阻挡结构的表面粗糙度大于所述第一区域的表面粗糙度及所述第二区域的表面粗糙度。

5、在一些可选的实施方式中,所述阻挡结构包括至少两个凹槽。

6、在一些可选的实施方式中,所述凹槽从所述共用焊盘的一侧延伸至另一侧。

7、在一些可选的实施方式中,所述凹槽垂直于所述凹槽延伸方向截面的宽度与深度比值大于等于1。

8、在一些可选的实施方式中,所述至少两个凹槽中,一个凹槽与所述第一区域相邻设置,另一个凹槽与所述第二区域相邻设置。

9、在一些可选的实施方式中,所述阻挡结构包括凸出部,所述凸出部突出于所述共用焊盘表面。

10、在一些可选的实施方式中,所述凸出部从所述共用焊盘的一侧延伸至另一侧。

11、在一些可选的实施方式中,所述凸出部包括阻焊材料。

12、在一些可选的实施方式中,所述装置还包括:

13、第一焊盘,与所述第一区域相邻设置,所述第一焊盘表面面积与所述第一区域表面面积相同;

14、第二焊盘,与所述第二区域相邻设置,所述第二焊盘表面面积与所述第二区域表面面积相同。

15、在一些可选的实施方式中,所述装置还包括:

16、第一电子元件,通过焊接材料设置于所述第一焊盘和所述第一区域上;

17、第二电子元件,通过焊接材料设置于所述第二焊盘和所述第二区域上。

18、在一些可选的实施方式中,所述装置还包括:

19、线路层,包括设置有所述共用焊盘、所述第一焊盘和所述第二焊盘的导电迹线及所述第一电子元件和所述第二电子元件。

20、在一些可选的实施方式中,所述第一区域表面面积与所述第二区域表面面积相同。

21、在一些可选的实施方式中,所述第一区域和所述第二区域之间的最小距离大于等于90微米。

22、本公开实施例提供的半导体封装装置,通过设计半导体封装装置包括:共用焊盘,表面设置有第一区域、第二区域及阻挡结构,阻挡结构区隔第一区域和第二区域;第一区域和第二区域上分别设置有焊接材料,阻挡结构能够阻挡设置于第一区域和第二区域的焊接材料。通过阻挡结构对第一区域和第二区域的焊接材料的阻挡,能够避免焊接过程中焊接材料在第一区域与第二区域之间移动,以防止焊接材料分布与流动不均。

技术特征:

1.一种半导体封装装置,包括:

2.根据权利要求1所述的装置,其中,所述阻挡结构的表面粗糙度大于所述第一区域的表面粗糙度及所述第二区域的表面粗糙度。

3.根据权利要求1所述的装置,其中,所述阻挡结构包括至少两个凹槽。

4.根据权利要求3所述的装置,其中,所述凹槽从所述共用焊盘的一侧延伸至另一侧。

5.根据权利要求3所述的装置,其中,所述凹槽垂直于所述凹槽延伸方向截面的宽度与深度比值大于等于1。

6.根据权利要求1所述的装置,其中,所述阻挡结构包括凸出部,所述凸出部突出于所述共用焊盘表面。

7.根据权利要求1所述的装置,其中,所述装置还包括:

8.根据权利要求7所述的装置,其中,所述装置还包括:

9.根据权利要求8所述的装置,其中,所述装置还包括:

10.根据权利要求7所示的装置,其中,所述第一区域表面面积与所述第二区域表面面积相同。

技术总结

本公开实施例提供了半导体封装装置,通过设计半导体封装装置包括:共用焊盘,表面设置有第一区域、第二区域及阻挡结构,所述阻挡结构区隔所述第一区域和所述第二区域;所述第一区域和所述第二区域上分别设置有焊接材料,所述阻挡结构能够阻挡设置于所述第一区域和所述第二区域的焊接材料。

技术研发人员:陈毅

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!