存储器装置的制作方法

1.本揭露实施例涉及存储器装置。

背景技术:

2.磁性随机存取存储器(magnetic random access memory;mram)是下一代存储器技术的主要候选者之一,其旨在超越各种现有存储器的性能。mram提供与易失性静态随机存取存储器(volatile static random access memory;sram)相当的性能和与易失性动态随机存取存储器(volatile dynamic random access memory;dram)相当的密度和更低的功耗。与非易失性快闪存储器(non-volatile flash memory)相比,mram提供更快的访问速度,并且随着时间的推移遭受最小的劣化。自旋轨道扭矩mram(spin orbit torque mram;sot-mram)是一种类型的mram。与另一种类型的mram的自旋转移扭矩mram(spin transfer torque mram;stt-mram)相比,sot-mram在速度和耐久性方面提供更好的性能。然而,进一步降低sot-mram的开关能量是有限的。

技术实现要素:

3.本发明实施例的一种存储器装置,包括:基底;自旋轨道扭矩层;磁性穿隧接面,与所述自旋轨道扭矩层堆叠于所述基底之上。所述磁性穿隧接面包括:合成自由层,包括合成反铁磁结构、第一间隔件层和自由层,其中所述合成反铁磁结构设置在所述自旋轨道扭矩层和所述自由层之间,且所述合成反铁磁结构经配置为改变所述自由层的磁化方向;阻障层,设置于所述合成自由层旁以及参考层,设置在所述阻障层旁。

4.本发明实施例的一种存储器装置,包括:写入晶体管和读取晶体管,形成在基底的表面区域上;自旋轨道扭矩层,位于所述写入晶体管和所述读取晶体管之上,且与所述写入晶体管的一端子和所述读取晶体管的一端子电连接;磁性穿隧接面,立于所述自旋轨道扭矩层上,且通过所述磁性穿隧接面的第一端子与所述自旋轨道扭矩层电耦合;以及位线,与所述磁性穿隧接面的第二端子电耦合。所述磁性穿隧接面包括:合成自由层,包括合成反铁磁结构、自由层和在所述合成反铁磁结构和所述自由层之间的第一交换耦合金属层,其中所述合成反铁磁结构比所述自由层更接近所述自旋轨道扭矩层;阻障层,设置于所述合成自由层之上;以及参考层,设置于所述阻障层之上。

5.本发明实施例的一种存储器装置,包括:读取晶体管,形成在基底的表面区域上,并且包括在所述基底上延伸的读取字线;位线,位于所述读取字线之上,且与所述读取晶体管的第一端子耦合;自旋轨道扭矩层,设置在所述读取晶体管之上;磁性穿隧接面,设置在所述自旋轨道扭矩层下,其中所述磁性穿隧接面通过所述磁性穿隧接面的第一端子与所述读取晶体管的第二端子电耦合,并通过所述磁性穿隧接面的第二端子与所述自旋轨道扭矩层电耦合;选择器,设置在所述自旋轨道扭矩层之上,并通过所述选择器的第一端子与所述自旋轨道扭矩层电耦合;以及写入字线,位于所述选择器之上并与所述选择器的第二端子电耦合。所述磁性穿隧接面包括:合成自由层,包括合成反铁磁结构、自由层以及在所述合

成反铁磁结构和所述自由层之间的第一交换耦合金属层,其中所述合成反铁磁结构设置在所述自旋轨道扭矩层和所述第一交换耦合金属层之间;阻障层,设置于所述合成自由层下;以及参考层,设置在所述阻障层下。

附图说明

6.结合附图阅读以下详细描述会最好地理解本公开的各方面。应注意,根据业界中的标准惯例,各种特征未按比例绘制。实际上,为了论述清楚起见,可任意地增大或减小各种特征的尺寸。

7.图1a是示意性地绘示根据本公开的一些实施例的存储阵列的电路图。

8.图1b绘示如图1a所示的存储阵列中经选定的单位单元中的写入路径。

9.图1c绘示如图1a所示的存储阵列中经选定的单位单元中的读取路径。

10.图2是图1a所示的多个单位单元中的一者的示意性三维视图。

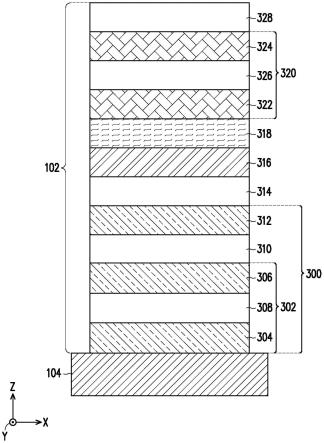

11.图3a至图3e是分别示出根据本公开的一些实施例的立于自旋轨道扭矩层上的磁性穿隧接面(magnetic tunneling junction;mtj)的示意性截面图。

12.图4a至图4c是各自示出根据本公开的一些实施例的立于自旋轨道扭矩层上的mtj的示意性平面图。

13.图5是示出根据本公开的一些实施例的用于制造均参照图2描述的多个单位单元中的相邻单位单元的方法的流程图。

14.图6a至图6l是图5所示制造过程中的中间体结构的截面示意图。

15.图7a至图7e是图6f至图6j所示的中间体结构的示意性平面图。

16.图8是绘示根据本公开的一些其他实施例的存储阵列的电路图。

17.图9是根据本公开的一些实施例示出如图8所示的存储阵列中的多个单位单元中的相邻单位单元的示意性三维视图。

18.图10是示出根据本公开的一些实施例的用于制造参照图9描述的多个单位单元中的相邻单位单元的方法的流程图。

19.图11a至图11l是图10所示制造过程中的中间体结构的示意性剖视图。

20.[符号的说明]

[0021]

10、90:存储阵列

[0022]

100、900:单位单元

[0023]

102、102a、102b、102c、902:磁性穿隧接面

[0024]

104、904:自旋轨道扭矩层

[0025]

200:基底

[0026]

202:接触插栓

[0027]

204、1002、1006:着陆垫

[0028]

206、1008:底部通孔

[0029]

208、1010:顶部通孔

[0030]

300、300a、300b、300c、904:合成自由层

[0031]

302、320:合成反铁磁结构

[0032]

304、306、322、324:铁磁层

[0033]

308、310、318、326、332、338、342:间隔件层

[0034]

312:自由层

[0035]

314:阻障层

[0036]

316:参考层

[0037]

328:顶盖层

[0038]

330、340:超顺磁性层

[0039]

334、336:铁磁子层

[0040]

344:扩散阻障件

[0041]

700:源极/漏极结构

[0042]

702:栅极介电层

[0043]

704、706、708、716、718、1200、1202、1210、1212、1214、1216、1218、1220、1222:介电层

[0044]

710:自旋霍尔材料层

[0045]

712、712’、1204:多层结构

[0046]

714:钝化层

[0047]

1000、1004:通孔

[0048]

1012:切换层

[0049]

1206:电极层

[0050]

1208:电极

[0051]

bd:位线驱动电路

[0052]

be:后端结构

[0053]

bl:位线

[0054]

cs:电流源电路

[0055]

dt:隔离晶体管

[0056]

dwl:虚设字线

[0057]

fe:前端结构

[0058]

l

102

、w

102

:尺寸

[0059]

m、m’、m”:磁化方向

[0060]

pr1、pr2:掩模图案

[0061]

s:选择器

[0062]

s600、s602、s6004、s606、s608、s610、s612、s614、s616、s618、s620、s622、s624、s1100、s1102、s1104、s1106、s1108、s1110、s1112、s1114、s1116、s1118、s1120、s1122:步骤

[0063]

sl:源极线

[0064]

rp:读取电流

[0065]

rt:读取晶体管

[0066]

rwl:读取字线

[0067]

wd:字线驱动电路

[0068]

wp:写入电流

[0069]

wt:写入晶体管

[0070]

wwl:写入字线

[0071]

x、y、z:方向

具体实施方式

[0072]

以下揭露内容提供用于实施所提供目标物的不同特征的许多不同的实施例或实例。以下阐述组件及布置的具体实例,以简化本揭露。当然,该些仅为实例且不旨在进行限制。举例而言,在以下说明中将第一特征形成于第二特征之上或第二特征上可包括其中第一特征与第二特征被形成为直接接触的实施例,且亦可包括其中第一特征与第二特征之间可形成有附加特征、进而使得第一特征与第二特征可不直接接触的实施例。另外,本揭露可能在各种实例中重复使用参考编号及/或字母。此种重复使用是出于简洁及清晰的目的,且自身并不指示所论述的各种实施例及/或配置之间的关系。

[0073]

此外,为易于说明,本文中可能使用例如“在

…

之下”、“下方”、“下部的”、“在

…

上方”、“上部的”等空间相对性用语来阐述图中所示一个组件或特征与另一(其他)组件或特征的关系。所述空间相对性用语旨在除图中所绘示的定向以外亦囊括装置在使用或操作中的不同定向。装置可具有其他定向(旋转90度或处于其他定向),且本文中所使用的空间相对性描述语可同样相应地进行解释。

[0074]

图1a是示意性地绘示根据本公开的一些实施例的存储阵列10的电路图。图1b绘示如图1a所示的存储阵列10中经选定的单位单元(unit cell)100中的写入路径。图1c绘示如图1a所示的存储阵列10中经选定的单位单元100中的读取路径。

[0075]

参考图1a,存储阵列10是磁性随机存取存储器(magnetic random access memory;mram)阵列。存储阵列10包括沿行和列侧向排列的多个单位单元100。具体来说,如图1a所示,每行的多个单位单元100沿方向x排列,而每列的多个单位单元100沿方向y排列,其中方向x垂直于方向y。在一些实施例中,多个单位单元100的每一列与一对写入字线wwl和读取字线rwl耦合,并且多个单位单元100的每一行与位线bl以及一对源极线sl耦合。在这些实施例中,每个单位单元100可以定义在多条写入字线wwl中的一者和多条读取字线rwl中的一者之间,以及在多条位线bl中的一者和多条源极线sl中的两者之间。此外,写入字线wwl和读取字线rwl可以沿着方向y延伸,并且位线bl以及源极线sl可以沿着方向x延伸。

[0076]

每个单位单元100包括磁性穿隧接面(magnetic tunneling junction;mtj)102作为存储器组件。mtj102中的多个铁磁层的多个磁化取向(magnetization orientation)可以确定mtj102的电阻。当多个磁化取向处于平行状态时,mtj102可以具有低电阻状态,并且当多个磁化取向处于反平行状态时,mtj102可以具有高电阻状态。通过改变mtj102中的多个磁化取向,mtj102可以被写入以储存互补逻辑状态(例如,指示高电阻状态的逻辑高状态和指示低电阻状态的逻辑低状态)。此外,根据本公开的实施例,mtj102经配置为通过利用自旋霍尔效应(spin hall effect)而被写入,并且存储阵列10可以被称为自旋轨道扭矩mram(spin orbit torque mram;sot-mram)阵列。自旋轨道扭矩(sot)层104,或也称为自旋霍尔电极(spin hall electrode;she),垂直地位于每个mtj102下方。在写入操作期间,通过sot层104的面内电荷电流(in-plane charge current)可藉由自旋霍尔效应而被转换为垂直自旋电流。详细地,面内电荷电流被驱动为垂直于sot层104和mtj102的堆叠方向(即,

垂直于图2中的方向z)。垂直自旋电流然后流入mtj102中的铁磁层并藉由自旋轨道扭矩将其磁化转换。以此方式,mtj102的多个磁化取向(即,mtj102的电阻)可以被改变,并且位数据可以被写入到mtj102中。在读取操作期间,可以感测mtj102的电阻状态,并且可以读出储存在mtj102中的位数据。

[0077]

写入操作的能量效率(energy efficiency)高度依赖于sot层104的自旋霍尔电导率(spin hall conductivity)。sot层104的自旋霍尔电导率越高,写入操作所需的功耗(power consumption)就越少。sot层104的自旋霍尔电导率定义为sot层104的自旋霍尔角与sot层104的电阻率(electrical resistivity)的比率。sot层104的自旋霍尔角表示从穿过sot层104的面内电荷电流由于自旋霍尔效应感应而转换到垂直自旋电流的转换效率,并定义为经感应的垂直自旋电流与相应的面内电荷电流的比率。换言之,自旋霍尔角越大,从面内电荷电流转换到垂直自旋电流的转换效率越高,且自旋霍尔电导率越高。另一方面,面内电荷电流的分流率(shunting ratio)受sot层104的电阻率影响。分流率被定义为sot层104的薄层电阻(sheet resistance)与最靠近sot层104的mtj102中的铁磁层的薄层电阻的比率。当sot层104的电阻率相对较高时,面内电荷电流的较大部分可选择低电阻路径而通过立于sot层104上的mtj102,而该部分面内电荷电流可能不会有助于产生垂直自旋电流。因此,从面内电荷电流转换到垂直自旋电流的转换效率较低。另一方面,当sot层104的电阻率相对较低时,面内电荷电流的分流率变低,且从面内电荷电流转换到垂直自旋电流的转换效率更高。因此,为了提高sot层104的自旋霍尔电导率,sot层104的自旋霍尔角必须高,和/或sot层104的电阻率必须低。

[0078]

在一些实施例中,sot层104包括一种或多种重金属(heavy metal)或掺杂有重金属的材料。在某些实施例中,pt、α-w、β-w、β-ta、aupt、w3ta、bi

x

sey、bisete、其多层结构、其合金等或其组合用于作为sot层104的材料。在一些实施例中,sot层104的厚度介于从约3nm到约20nm的范围内。sot层104的自旋霍尔角可以随着sot层104的厚度而增加,并且直到sot层104的厚度等于或大于约3nm时才饱和。因此,如果sot层104的厚度低于约3nm,则sot层104的自旋霍尔角可能受到限制。另一方面,如果sot层104的厚度大于约20nm,则写入操作对电荷电流的需求显著增加,从而损害了写入操作的能量效率。

[0079]

如图1a所示,在一些实施例中,每个单位单元100还包括写入晶体管wt和读取晶体管rt。每个单位单元100中的写入晶体管wt和读取晶体管rt与sot层104耦合。特别地,写入晶体管wt和读取晶体管rt可以在mtj102的相对侧与sot层104的多个部分耦合,使得mtj102可以立于写入晶体管wt和读取晶体管rt之间的写入电流路径上(即,前述的面内电荷电流上)。因此,mtj102可以藉由写入电流而被写入。写入晶体管wt和读取晶体管rt可以分别是三端装置。每个写入晶体管wt的栅极端子可以与多条写入字线wwl中的一者耦合,并且每个读取晶体管rt的栅极端子可以与多条读取字线rwl中的一者耦合。另外,每个单位单元100中的写入晶体管wt和读取晶体管rt分别通过源极/漏极端子与sot层104耦合,并通过另一个源极/漏极端子分别与多条源极线sl中的一者耦合。在一些实施例中,每个单位单元100中的写入晶体管wt和读取晶体管rt与多条源极线sl中的两者耦合。此外,每个mtj102的一个端子与下伏的sot层104耦合,并且每个mtj102的另一个端子与多条位线bl中的一者耦合。

[0080]

字线驱动电路wd可以与多条写入字线wwl和多条读取字线rwl耦合,并且经配置为

通过多条写入字线wwl和多条读取字线rwl控制多个写入晶体管wt和多个读取晶体管rt的切换。此外,电流源电路(current source circuit)cs可以与多条源极线sl耦合。电流源电路cs经配置为提供用于写入mtj102的写入电流(即,上述的面内电荷电流)以及用于感测mtj102的电阻状态的读取电流,并且可以与字线驱动电路wd结合。进一步地,位线驱动电路bd可以与多条位线bl耦合,且经配置为感测通过mtj102的读取电流,以识别mtj102的电阻状态。

[0081]

参考图1a和图1b,在写入操作期间,所选定的单位单元100的写入晶体管wt和读取晶体管rt都导通,并且写入电流wp(即,如上所述的面内电荷电流)可以流过写入晶体管wt、读取晶体管rt和它们之间的sot层104。作为自旋轨道相互作用的结果,流经sot层104的写入电流wp可能在mtj102上引起sot,因此mtj102可以经受写入。写入晶体管wt和读取晶体管rt通过设置对应的写入字线wwl和读取字线rwl而导通,并且通过在多条源极线sl中对应的两条之间设置电压差来提供写入电流wp。另一方面,位线bl可为浮置(floated)。

[0082]

参考图1a和图1c,在读取操作期间,所选定的单位单元100的读取晶体管rt导通,而同一单位单元100中的写入晶体管wt可以保持关断。在与读取晶体管rt耦合的位线bl和源极线sl之间可以设置电压差,从而读取电流rp可以流过连接在读取晶体管rt和位线bl之间的mtj102。由于自旋轨道耦合效应,mtj102的不同磁化取向(即,平行状态和反平行状态)可能导致穿过mtj102的传导电子的散射量的变化。这种变化导致mtj102的电阻不同,并且可能影响读取电流rp的值或mtj102两端的电压降的值。因此,可以读出储存在mtj102中的位数据(即,电阻状态)。另一方面,与写入晶体管wt耦合的源极线sl可为浮置。

[0083]

图2是图1a所示多个单位单元100中的一者的示意性三维视图。

[0084]

参考图2,所选定的单位单元100中的写入晶体管wt和读取晶体管rt形成在装置晶片的前端(front end of line;feol)结构fe中。写入晶体管wt的栅极端子可以由位于基底200上的写入字线wwl提供。类似地,读取晶体管rt的栅极端子可以由位于基底200上的读取字线rwl提供。在一些实施例中,基底200是半导体基底。写入字线wwl和读取字线rwl可以沿方向x彼此侧向间隔开,并且都可以沿方向y侧向延伸。写入晶体管wt的源极与漏极端子(未绘示)位于写入字线wwl的相对侧,且读取晶体管rt的源极与漏极端子(未绘示)位于读取字线rwl的相对侧。在写入晶体管wt和读取晶体管rt是平面型晶体管的那些实施例中,写入字线wwl以及读取字线rwl分别位于基底200的平面表面上,并且写入晶体管wt和读取晶体管rt的源极和漏极端子可以是形成在基底200的浅区域中的经掺杂区或外延结构(未示出)。在写入晶体管wt和读取晶体管rt是鳍型晶体管的那些实施例中,写入字线wwl和读取字线rwl分别于基底200的顶部区域处覆盖鳍结构并与鳍结构相交,并且写入晶体管wt和读取晶体管rt的源极和漏极端子可以是与鳍结构接触(例如,侧向接触)的外延结构(未示出)。在写入晶体管wt和读取晶体管rt是栅极全环绕(gate-all-around;gaa)晶体管的那些实施例中,基底200之上的多个半导体片堆叠分别被写入字线wwl或读取字线rwl包围,并且写入晶体管wt和读取晶体管rt的源极与漏极端子可以是与半导体片堆叠接触(例如,侧向接触)的外延结构(未示出)。此外,多个接触插栓(contact plug)202可以沿着方向z立在写入晶体管wt和读取晶体管rt的多个源极/漏极端子上。多个接触插栓202与这些源极/漏极端子电连接,以便将这些源极/漏极端子连接到上覆的多个导电组件。

[0085]

在一些实施例中,虚设字线(dummy word line)dwl位于写入字线wwl和读取字线

rwl之间。详细地,如图2所示,虚设字线dwl沿方向x与写入字线wwl和读取字线rwl侧向间隔开。虚设字线dwl、写入字线wwl和读取字线rwl可以沿着相同的方向延伸,例如方向y。通过设置虚设字线dwl,可以在写入晶体管wt和读取晶体管rt之间形成寄生晶体管(parasitic transistor)。寄生晶体管可以在结构上与写入晶体管wt和读取晶体管rt相同。寄生晶体管的栅极端子可以由虚设字线dwl提供。写入晶体管wt和读取晶体管rt中的每一者与寄生晶体管共享其多个源极/漏极端子中的一者。在一些实施例中,虚设字线dwl经配置为接收可以保证寄生晶体管关断状态的栅极电压,从而可以有效地避免写入晶体管wt和读取晶体管rt之间的干扰。因此,包括虚设字线dwl的寄生晶体管也可以被称为隔离晶体管dt。

[0086]

源极线sl、sot层104、mtj102和位线bl可以集成在形成在feol结构fe上方的后端(back-end-of-lin;beol)结构be中。在一些实施例中,与写入晶体管wt和读取晶体管rt耦合的多条源极线sl是beol结构be中底部金属化层的多个部分,并且可以沿着方向x延伸。多条源极线sl通过在其间垂直延伸的多个接触插栓202与写入晶体管wt和读取晶体管rt的一些源极/漏极端子连接。在一些实施例中,写入晶体管wt和读取晶体管rt的其他源极/漏极端子通过在其间垂直延伸的多个接触插栓202与多个着陆垫(landing pad)204连接,其中着陆垫204也形成在beol结构be的底部金属化层中。此外,sot层104和mtj102可以形成在底部金属化层之上。sot层104可以通过在其间垂直延伸的多个底部通孔(bottom via)206与底部金属化层中的多个着陆垫204电连接。换句话说,sot层104可以通过下伏的多个底部通孔206、多个着陆垫204和多个接触插栓202与写入晶体管wt和读取晶体管rt的多个源极端子或多个漏极端子耦合。mtj102沿着方向z竖立或堆叠在sot层104上,并且可以位于多个底部通孔206之间,从而立于在多个底部通孔206之间流动的写入电流的路径上。在一些实施例中,如图2所示,sot层104延伸超出对应的多个底部通孔206的边缘。然而,本公开不限于此。在一些替代实施例中,sot层104的边缘与对应的多个底部通孔206的边缘对齐。此外,位线bl可以形成在mtj102之上的另一个金属化层中,并且可以沿着方向x延伸。在一些实施例中,位线bl通过在其间垂直延伸的顶部通孔(top via)208与mtj102电连接。

[0087]

图3a至图3e是分别示出根据本公开的一些实施例的立于自旋轨道扭矩层上的mtj的示意性截面图。

[0088]

参考图3a,沿方向z立于sot层104上的mtj102可以是多层结构,并且至少包括合成自由层300、参考层316和夹置在合成自由层300和参考层316之间的阻障层314。

[0089]

在一些实施例中,mtj102包括夹置在具有固定或「钉扎层(pinned)」磁化取向的磁性固定层(例如参考层316)和具有可变或「自由」磁化取向的磁性自由层(例如合成自由层300)之间的介电层(例如阻障层314)。由于穿隧式磁阻效应(tunnel magnetoresistance effect),参考层316和合成自由层300之间的电阻值随着合成自由层300中的磁化取向切换而变化。在一些实施例中,如果参考层316的磁化方向和合成自由层300的磁化方向处于平行的相对取向,则电荷载流子(例如,电子)更有可能穿隧过阻障层314,使得mtj102处于低电阻状态。相反地,在一些实施例中,如果参考层316的磁化方向和合成自由层300的磁化方向处于反平行取向,则电荷载流子(例如,电子)将穿隧过阻障层314的可能性较小,使得mtj102处于高电阻状态。电阻值的两个状态被认为是储存在单位单元100中的两个逻辑状态“1”或“0”。也就是说,在mtj102内,合成自由层300充当状态保持层,且其磁性状态决定了相应单位单元100的状态。

plane magnetic anisotropy;pma)的自由层312可以具有约0.5nm和约1nm之间的厚度。在另外的实施例中,自由层312具有(100)取向的bcc结构。

[0095]

在一些实施例中,合成反铁磁(synthetic antiferromagnetic;saf)结构302包括一个或多个间隔件层,每个间隔件层夹置在两个铁磁层之间。例如,如图3a所示,saf结构302包括铁磁层304、铁磁层306和在铁磁层304和铁磁层306之间的间隔件层308,即两个铁磁层和一个间隔件层。具体地,在这种情况下,铁磁层304、间隔件层308、铁磁层306、间隔件层310和自由层312一起形成五层的合成自由层300。然而,本公开不限于此。在一些替代实施例中,saf结构302可以包括沿方向z交替堆叠的铁磁层和间隔件层。在一些实施例中,如图3a所示,铁磁层304、间隔件层308和铁磁层306依次且垂直地堆叠在sot层104上。

[0096]

在一些实施例中,间隔件层308在铁磁层304和铁磁层306之间引起rkky耦合,使得铁磁层304和铁磁层306彼此反铁磁耦合。因此,当铁磁层304具有第一磁化方向时,铁磁层306具有与第一磁化方向反平行的第二磁化方向。在一些实例中,这种间隔件层308也可以被称为交换耦合层(exchange coupling layer)或反铁磁耦合层(antiferromagnetically coupling layer)。在一些实施例中,间隔件层308是非磁性金属层。在一些实施例中,间隔件层308包括ru、w、钒(v)、钛(ti)、前述的组合等。在一些实施例中,间隔件层308的厚度在约0.2nm至约1.5nm的范围内以提供反铁磁耦合。

[0097]

在一些实施例中,铁磁层304和铁磁层306中的每一个具有可切换的磁化方向。在一些实施例中,铁磁层304和铁磁层306中的每一个的磁化方向在水平轴上是可切换的,例如沿着方向x或方向y。在一些替代实施例中,铁磁层304和铁磁层306中的每一个的磁化方向在垂直轴上是可切换的,例如沿着方向z。如上所述,铁磁层304中磁化方向的切换受到自旋霍尔效应驱动,且铁磁层306中磁化方向的切换受到间隔件层308藉由rkky耦合驱动。

[0098]

在一些实施例中,铁磁层304和铁磁层306中的每一个被形成为具有低饱和磁化强度(ms)。在一些实施例中,铁磁层304和铁磁层306中的每一个的饱和磁化强度在从约550eum/cm3到约1150eum/cm3的范围内。在一些实施例中,铁磁层304的饱和磁化强度实质上等于铁磁层306的饱和磁化强度。在一些实施例中,如图3a所示,铁磁层304和铁磁层306中的每一个是单一层。在这样的实施例中,铁磁层304和铁磁层306中的每一个包括钴-铬合金或钴-铁-镍合金。在铁磁层304和铁磁层306中的每一个包括钴-铬合金的实施例中,钴-铬合金可以是co

1-x

cr

x

,其中0.05<x<0.2。如果co

1-x

cr

x

中的「x」大于或等于约0.2,则钴-铬合金变成顺磁性材料(paramagnetic material),从而失去其磁耦合强度;和/或如果co

1-x

cr

x

中的「x」小于或等于约0.05,则钴-铬合金层表现出高饱和磁化强度,从而导致高开关电流(switching current)。在铁磁层304和铁磁层306中的每一个包括钴-铁-镍合金的实施例中,钴-铁-镍合金可以是co

x-fe

y-niz,其中x《0.5,y《0.3,z》0.5。如果在co

x-fe

y-niz中,「x」大于或等于约0.5,「y」大于或等于约0.3,和/或「z」小于或等于约0.5,钴-铁-镍合金层表现出高饱和磁化强度,从而导致高开关电流。在一些实施例中,铁磁层304的材料与铁磁层306的材料相同。然而,本公开不限于此。在一些替代实施例中,只要铁磁层304的饱和磁化强度实质上等于铁磁层306的饱和磁化强度,铁磁层304的材料可以与铁磁层306的材料不同。在一些实施例中,铁磁层304和铁磁层306中的每一个的厚度介于从约0.5nm到约2.5nm的范围内。铁磁层304和铁磁层306中的每一个的厚度可以取决于对于稳定磁态是需要垂直的方向(例如,方向z)还是平面内优选的方向(例如,方向x或方向y)。此外,包含在saf结构302中的

铁磁层304、间隔件层308和铁磁层306各自可形成有与上覆的自由层312的预期结晶结构(例如,bcc结构)相似或相同的结晶结构,以向上覆的自由层312提供优选的成长模板(growth template)。因此,可以形成具有改善的结晶度的上覆的自由层312。

[0099]

间隔件层310在saf结构302的自由层312和铁磁层306之间引起rkky耦合,使得铁磁层306和自由层312彼此反铁磁耦合。因此,由于间隔件层310提供的反平行交换耦合,自由层312的磁化方向与铁磁层306的磁化方向相反。也就是说,saf结构302经配置为通过间隔件层310引起的交换耦合来改变自由层312的磁化方向。此外,在一些实例中,这种间隔件层310可以被称为交换耦合层或反铁磁耦合层。在一些实施例中,间隔件层310是非磁性金属层。在一些实施例中,间隔件层310包括ru、w、v、ti、前述的组合等。在一些实施例中,间隔件层310的材料与间隔件层308的材料相同。在一些替代实施例中,间隔件层310的材料不同于间隔件层308的材料。在一些实施例中,间隔件层310的厚度在约0.2nm至约1.5nm的范围内,以提供反铁磁耦合。

[0100]

通过在mtj102中使用合成自由层300,存储阵列10可以提供优于mtj中只有单一自由层的传统存储阵列的改进。首先,通过在合成自由层300中设置saf结构302、间隔件层310和自由层312,增强合成自由层300的矫顽磁场(magnetic coercive field)(hc)和有效各向异性场(hk),从而可提高存储阵列10的数据稳定性、数据处理和数据保持能力,从而增加存储阵列10的可靠性。在某些实施例中,合成自由层300的矫顽磁场(hc)介于从约100mt至约130mt的范围内。其次,由于铁磁层304和铁磁层306中的每一个的饱和磁化强度低,可以减少通过sot层104的写入电流(即面内电荷电流)。在某些实施例中,在存储阵列10中,当写入电流介于从大约30ua到大约45ua的范围内时,切换时间可以是10ns;且当写入电流介于从大约50ua到大约80ua的范围内时,切换时间可以达到2ns。第三,由于saf结构302的多个铁磁层(例如,铁磁层304和铁磁层306)之间的偶极耦合和自旋扭矩有助于saf结构302更快地切换,通过将saf结构302、间隔件层310和自由层312设置在合成自由层300中,合成自由层300的切换可以更快。

[0101]

在一些实施例中,mtj102还包括介于参考层316和saf结构320之间的间隔件层318(参见下文关于saf结构320的详细描述)。详细地说,如图3a所示,间隔件层318上覆于参考层316,并将参考层316与saf结构320隔离开。在一些实施例中,间隔件层318是用以触发反铁磁耦合的层。在此类实施例中,间隔件层318由诸如ru、w、钼(mo)、铱(ir)等或其组合的材料形成。在一些实施例中,间隔件层318的厚度介于从约2埃到约10埃的范围内。在一些实施例中,可以使用较厚的间隔件层318来减少上覆层对saf结构320的晶格失配(crystalline lattice mismatch)的影响。在一些实施例中,间隔件层318是可选的并且不是mtj102的一部分。

[0102]

saf结构320经配置以增强在参考层316中磁化方向的钉扎。通过相对于参考层316改变合成自由层300的磁化方向,对参考层316的磁化方向进行钉扎使得单位单元100在低电阻状态和高电阻状态之间转换。因为saf结构320和参考层316形成在合成自由层300之上,所以这样的mtj102可以被认为是「顶部钉扎」的mtj。然而,本公开不限于此。在一些替代实施例中,mtj102的层的顺序可以颠倒并且sot层104可以形成在mtj102之上。在这样的实施例中,因为合成自由层300形成在参考层316和saf结构320之上,所以这样的mtj可以被认为是「底部钉扎」的mtj。

[0103]

在一些实施例中,saf结构320包括一个或多个间隔件层,每个间隔件层夹置在两个铁磁层之间。例如,如图3a所示,saf结构320包括铁磁层322、铁磁层324和在铁磁层322和铁磁层324之间的间隔件层326,即两个铁磁层和一个间隔件层。然而,本公开不限于此。在一些替代实施例中,saf结构320可以包括沿方向z交替堆叠的铁磁层和间隔件层。在一些实施例中,如图3a所示,铁磁层322、间隔件层326和铁磁层324依次且垂直地堆叠在sot层104上。

[0104]

间隔件层326在铁磁层322和铁磁层324之间引起rkky耦合,使得铁磁层322和铁磁层324彼此反铁磁耦合。因此,由于间隔件层326提供的反平行交换耦合,铁磁层322的磁化方向与铁磁层324的磁化方向相反。此外,在一些实例中,这种间隔件层326可以被称为交换耦合层或反铁磁耦合层。在一些实施例中,间隔件层326是非磁性金属层。在一些实施例中,间隔件层326包括ru、w、v、ti、前述的组合等。在一些实施例中,间隔件层326的材料与间隔件层308的材料相同。在一些替代实施例中,间隔件层326的材料不同于间隔件层308的材料。在一些实施例中,间隔件层326的厚度在约0.2nm至约1.5nm的范围内以提供反铁磁耦合。

[0105]

在一些实施例中,铁磁层322和铁磁层324中的每一个具有固定的磁化取向。在一些实施例中,铁磁层322和铁磁层324中的每一个包括fe、co、ni、feco合金、nife合金、coni合金、cofeb合金、cofebw合金、feb合金、fept合金、fepd合金和合适的铁磁材料中的一者或多者。在一些实施例中,铁磁层322和铁磁层324中的每一个的厚度介于从约1nm到约3nm的范围内。铁磁层322和铁磁层324中的每一个的厚度可以取决于对于稳定磁态是需要垂直的方向(例如,方向z)还是平面内优选的方向(例如,方向x或方向y)。在一些实施例中,saf结构320的总厚度在约3nm至约10nm的范围内,例如约5nm。在一些实施例中,较厚的saf结构320可以具有更强的反铁磁特性,或者可以更稳健地抵抗外部磁场或热波动。在一些实施例中,saf结构320可具有(111)取向的面心立方(face-center-cubic,fcc)结构。在一些实施例中,saf结构320是可选的并且不是mtj102的一部分。在一些实施例中,钉扎层(未示出)还设置在参考层316之上。在这些实施例中,钉扎层由反铁磁材料形成,例如ptmn、irmn、mnni、femn、pdmn、crfe、crco。

[0106]

此外,在一些实施例中,mtj102还包括作为mtj102中的最外部层(例如,最顶部层)的顶盖层328。在saf结构320上覆于参考层316的那些实施例中,如图3a所示,顶盖层328设置在saf结构320上。顶盖层328可以保护下伏的层免受刻蚀损坏和/或氧化。根据一些实施例,顶盖层328由诸如钽、氮化钽、钛、氮化钛等或其组合的导电材料形成。

[0107]

参考图3a和图3b,图3b中所示的mtj102a与图3a中所示的mtj102相似,因此相同的标号用于指代相同或相似的部分,在此不再赘述。下面将描述mtj102a和mtj102之间的差异。

[0108]

参考图3b,在mtj102a中,合成自由层300a还包括超顺磁性层(superparamagnetic layer)330和间隔件层332。也就是说,在mtj102a中,超顺磁性层330、间隔件层332、铁磁层304、间隔件层308、铁磁层306、间隔件层310和自由层312共同形成了七层的合成自由层300a。详细地,如图3b所示,超顺磁性层330形成在sot层104和saf结构302之间,且间隔件层332形成在超顺磁性层330和saf结构302之间。也就是说,间隔件层332上覆于超顺磁性层330,并将超顺磁性层330与saf结构320隔离开。

[0109]

在一些实施例中,在超顺磁性层330中,磁化方向不稳定并且可以由于随机热波动而随机改变方向。也就是说,超顺磁性层330具有随机磁矩(magnetic moment)。在一些实施例中,超顺磁性层330的磁化方向的沿方向x的x分量、沿方向y的y分量和沿方向z的z分量随机变化。在这样的实施例中,超顺磁性层330包括钴-铬合金。在某些实施例中,钴-铬合金可以是co

1-x

cr

x

,其中0.05<x<0.2。由于钴-铬合金中的co含量很低,以至于co中的自旋不能形成短程交换(这决定了自旋的反平行或平行排列),因此超顺磁性层330具有随机磁矩,其中x分量、y分量和z分量都随机变化。在一些实施例中,超顺磁性层330的厚度在约0.5nm至约1.5nm的范围内。在一些实施例中,超顺磁性层330的饱和磁化强度在约20eum/cm3至约100eum/cm3的范围内。

[0110]

在一些实施例中,间隔件层332是非磁性金属层。在一些实施例中,间隔件层332包括ru、w、v、ti、前述的组合等。在一些实施例中,间隔件层332的厚度介于从约0.2nm到约1.5nm的范围内。在一些实施例中,间隔件层332可以在saf结构302的超顺磁性层330和铁磁层304之间引起rkky耦合。在这样的实施例中,通过间隔件层332的厚度控制,铁磁层304和铁磁层306可以是铁磁耦合或反铁磁耦合。

[0111]

通过在mtj102a中使用合成自由层300a,本公开的存储阵列可以提供优于mtj中具有单一自由层的传统存储阵列的改进。首先,通过在合成自由层300a中设置saf结构302、间隔件层310和自由层312,增强合成自由层300a的矫顽磁场(hc)和有效各向异性场(hk),从而可提高存储阵列10的数据稳定性、数据处理和数据保持能力,从而提高这种存储阵列的可靠性。在某些实施例中,合成自由层300a的矫顽磁场(hc)介于从约80mt至约120mt的范围内。其次,除了铁磁层304和铁磁层306各自的低饱和磁化强度之外,与铁磁层304、铁磁层306和自由层312耦合的超顺磁性层330的随机磁矩可以提供热随机角(thermally randomized angle)(其加快了铁磁层304、铁磁层306和自由层312的初始磁进动(initial magnetic precession)),使得通过sot层104的写入电流(即面内电荷电流)可以进一步降低。在mtj102a中包含合成自由层300a的某些实施例中,当写入电流介于从约20ua至约35u a的范围内时,切换时间可为10ns;且当写入电流介于从约40ua到约65ua的范围内时,切换时间可以达到2ns。第三,由于saf结构302的多个铁磁层(例如,铁磁层304和铁磁层306)之间的偶极耦合和自旋扭矩有助于saf结构302更快地切换,通过将saf结构302、间隔件层310和自由层312设置在合成自由层300a中,合成自由层300a的切换可以更快。

[0112]

在上述实施例中,saf结构302中的铁磁层304和铁磁层306中的每一个是单一层。然而,本公开不限于此。在一些替代实施例中,saf结构302中的铁磁层304和铁磁层306中的每一个可以是多层结构。下面将参考图3c和图3d来描述细节。

[0113]

参考图3a和图3c,图3c中所示的mtj102b与图3a中所示的mtj102相似,因此相同的标号用于指代相同或相似的部分,在此不再赘述。下面将描述mtj102b和mtj102之间的差异。

[0114]

参考图3c,在mtj102b的合成自由层300b中,铁磁层304和铁磁层306中的每一个包括铁磁子层(ferromagnetic sub-layer)334、铁磁子层336和夹置在铁磁子层334和铁磁子层336之间的间隔件层338。也就是说,在合成自由层300b中,铁磁层304和铁磁层306中的每一个都是三层结构,其包括两个铁磁子层和一个间隔件层。换句话说,在合成自由层300b中,两个铁磁子层334、336被一个间隔件层338隔开。

[0115]

在一些实施例中,铁磁子层334和铁磁子层336中的每一个被形成为具有高饱和磁化强度(ms)。在一些实施例中,铁磁子层334和铁磁子层336中的每一个的饱和磁化强度介于从约1100eum/cm3到约1600eum/cm3的范围内。在一些实施例中,铁磁子层334和铁磁子层336中的每一个包括钴-铁合金。在某些实施例中,钴-铁合金可以是co

x

fey,其中0.1《x《0.4,0.5《y《0.8,x+y=1。如果co

x

fey中的「x」小于或等于约0.1和/或大于或等于约0.4,co

x

fey中的「y」小于或等于约0.5和/或大于或等于约0.8,和/或「x+y」不等于1,则钴-铁合金表现出低饱和磁化强度,从而导致低矫顽磁场(hc)和低保持力。在一些实施例中,铁磁子层334的材料与铁磁子层336的材料相同。在一些替代实施例中,铁磁子层334的材料不同于铁磁子层336的材料。在一些实施例中,铁磁子层334和铁磁子层336中的每一个的厚度介于从约0.1nm到约2nm的范围内。铁磁子层334和铁磁子层336中的每一个的厚度可以取决于对于稳定磁态是需要垂直的方向(例如,方向z)还是平面内优选的方向(例如,方向x或方向y)。

[0116]

在一些实施例中,间隔件层338形成为具有非磁性或低饱和磁化强度(ms)。如此,即使铁磁子层334和铁磁子层336中的每一个形成为具有高饱和磁化强度(ms),通过设置夹置在铁磁子层334和铁磁子层336之间的间隔件层338,铁磁层304和铁磁层306中的每一者仍然具有低的高饱和磁化强度(ms),其范围从例如约500eum/cm3到约1150eum/cm 3

。在间隔件层338被形成为具有非磁性的实施例中,间隔件层338是非磁性金属层。在一些实施例中,间隔件层338包括ru、w、v、ti、cr、cu、al、ni、前述的组合等。在一些实施例中,间隔件层338的厚度介于从约0.1nm到约2nm的范围内。在间隔件层338形成为具有低饱和磁化强度(ms)的实施例中,间隔件层338的厚度可以取决于对于稳定磁态是需要垂直的方向(例如,方向z)还是平面内优选的方向(例如,方向x或方向y)。

[0117]

在一些实施例中,铁磁层304中铁磁子层334的材料与铁磁层306中铁磁子层334的材料相同;铁磁层304中铁磁子层336的材料与铁磁层306中铁磁子层336的材料相同;以及铁磁层304中间隔件层338的材料与铁磁层306中间隔件层338的材料相同。然而,本公开不限于此。在一些替代实施例中,只要铁磁层304的饱和磁化强度实质上等于铁磁层306的饱和磁化强度,铁磁层304中的铁磁子层334的材料可以与铁磁层306中的铁磁子层334的材料不同;铁磁层304中的铁磁子层336的材料可以与铁磁层306中的铁磁子层336的材料不同;和/或铁磁层304中的间隔件层338的材料可以与铁磁层306中的间隔件层338的材料不同。

[0118]

此外,包括在saf结构302中的多个铁磁子层334、多个铁磁子层336和多个间隔件层338各自可以形成有与上覆的自由层312的预期结晶结构(例如,bcc结构)相似或相同的结晶结构,因此以便为上覆的自由层312提供优选的成长模板。因此,可以形成具有改善的结晶度的上覆的自由层312。

[0119]

通过在mtj102b中使用合成自由层300b,本公开的存储阵列可以提供优于mtj中具有单一自由层的传统存储阵列的改进。首先,通过在合成自由层300b中布置saf结构302、间隔件层310和自由层312,增强合成自由层300b的矫顽磁场(hc)和有效各向异性场(hk),从而可提高包括合成自由层300b的存储阵列的数据稳定性、数据处理和数据保持能力,从而提高这种存储阵列的可靠性。在某些实施例中,合成自由层300b的矫顽磁场(hc)介于从约150mt至约200mt的范围内。其次,由于铁磁层304和铁磁层306中的每一个的饱和磁化强度低,可以减少通过sot层104的写入电(即面内电荷电流)。在mtj102b中包含合成自由层300b的某些实施例中,当写入电流介于从约60ua至约100ua的范围内时,切换时间可为10ns;当

写入电流介于从约100ua到约170ua的范围内时,切换时间可以达到2ns。第三,由于saf结构302的多个铁磁层(例如,铁磁层304和铁磁层306)之间的偶极耦合和自旋扭矩有助于saf结构302更快地切换,通过将saf结构302、间隔件层310和自由层312设置在合成自由层300b中,合成自由层300b的切换可以更快。

[0120]

参考图3c和图3d,图3d中所示的mtj102c与图3c中所示的mtj102b相似,因此相同的标号用于指代相同或相似的部分,在此不再赘述。下面将描述mtj102c和mtj102b之间的差异。

[0121]

参考图3d,在mtj102c中,合成自由层300c还包括超顺磁性层340和间隔件层342。具体来说,如图3d所示,超顺磁性层340形成在sot层104和saf结构302之间,且间隔件层342形成在超顺磁性层340和saf结构302之间。也就是说,间隔件层342上覆于超顺磁性层340,并将超顺磁性层340与saf结构320分隔开。

[0122]

在一些实施例中,超顺磁性层340的材料与针对图3b所示的mtj102a提到的超顺磁性层330的材料实质上相同或相似,因此为简单起见,在此不再重复其详细描述。另外,对于超顺磁性层340的细节或描述(如材料、性质、厚度等),在此不再赘述,请参考前述实施例。在一些实施例中,间隔件层342的材料与针对图3b中所示的mtj102a提到的间隔件层332的材料实质上相同或相似,因此为简单起见,在此不再重复其详细描述。另外,对于间隔件层342的细节或描述(例如材料、性质、厚度等),在此不再赘述,请参考前述实施例。

[0123]

通过在mtj102c中使用合成自由层300c,本公开的存储阵列可以提供优于mtj中具有单一自由层的传统存储阵列的改进。首先,通过在合成自由层300c中设置saf结构302、间隔件层310和自由层312,增强合成自由层300c的矫顽磁场(hc)和有效各向异性场(hk),从而可提高包括合成自由层300c的存储阵列的数据稳定性、数据处理和数据保持能力,从而提高这种存储阵列的可靠性。在某些实施例中,合成自由层300c的矫顽磁场(hc)介于从约130mt至约180mt的范围内。其次,除了铁磁层304和铁磁层306各自的低饱和磁化强度之外,与铁磁层304、铁磁层306和自由层312耦合的超顺磁性层340的随机磁矩可以提供热随机角(其加快了铁磁层304、铁磁层306和自由层312的初始磁进动),使得通过sot层104的写入电流(即面内电荷电流)可以进一步降低。在mtj102c中包含合成自由层300c的某些实施例中,当写入电流介于从约50ua至约80ua的范围内时,切换时间可为10ns;当写入电流介于从约100ua到约130ua的范围内时,切换时间可以达到2ns。第三,由于saf结构302的多个铁磁层(例如,铁磁层304和铁磁层306)之间的偶极耦合和自旋扭矩有助于saf结构302更快地切换,通过将saf结构302、间隔件层310和自由层312设置在合成自由层300c中,合成自由层300c的切换可以更快。

[0124]

参考图3e,在一些实施例中,扩散阻障件(diffusion barrier)344设置在sot层104和mtj之间,mtj可以是参考图3a描述的mtj102、参考图3b描述的mtj102a、参考图3c描述的mtj102b,或参考图3d描述的mtj102c。扩散阻障件344经配置为防止sot层104和最靠近sot层104的mtj的层(例如,mtj102的铁磁层304、mtj102a的超顺磁性层330、mtj102b的铁磁子层334、mtj102c的超顺磁性层340)之间的相互扩散,并且可以由非磁性导电材料形成,例如钼。

[0125]

图4a至图4c是各自示出根据本公开的一些实施例的立于自旋轨道扭矩层上的mtj的示意性平面图。

[0126]

参考图4a,在一些实施例中,mtj102的主轴与sot层104的主轴实质上对齐或实质上平行,其中写入路径沿sot层104的主轴定向。在这些实施例中,mtj102中的合成自由层300的磁化方向m(如参考图3a所述)也可以与sot层104的主轴实质上对齐或实质上平行。作为图4a中所示的实例,sot层104的主轴和多个底部通孔206之间的经定向写入路径沿着方向x(即面内方向),且mtj102的主轴以及mtj102中合成自由层300的磁化方向m也沿着方向x。mtj102沿方向x的尺寸l

102

与mtj102沿方向y的尺寸w

102

(即,另一个面内方向)的比率可以例如在从大约1.5到大约5的范围内。

[0127]

参考图4b,在一些实施例中,mtj102的主轴相交于(例如,垂直于)sot层104的主轴,其中写入路径沿着sot层104的主轴定向。在这些实施例中,mtj102中的合成自由层300的磁化方向m’(其实质上与mtj102的主轴对齐)也可以相交于(例如,垂直于)sot层104的主轴。作为图4b中所示的实例,sot层104的主轴和多个底部通孔206之间的经定向写入路径沿方向x,而mtj102的主轴以及mtj102中合成自由层300的磁化方向m’沿着方向y。mtj102沿方向x的尺寸l

102

与mtj102沿方向y的尺寸w

102

之比率可例如在约1.5至约5的范围内。

[0128]

参考图4c,在一些实施例中,mtj102形成为实质上对称的形状。在这些实施例中,mtj102中的合成自由层300的磁化方向m”可以沿着与mtj102接触的sot层104的表面实质上垂直的方向z(即,平面外方向(out-of-plane direction))。此外,mtj102沿方向x的尺寸l

102

与mtj102沿方向y的尺寸w

102

之比率可接近或等于1。

[0129]

需要说明的是,mtj102是举例说明sot层104和立于sot层104上的mtj的各种配置。参考图3b描述的sot层104和mtj102b也可以具有图4a到图4c中所示的变化。类似地,参考图3c描述的sot层104和mtj102b或参考图3d描述的sot层104和mtj102c也可以具有图4a到图4c所示的变化。

[0130]

图5是示出根据本公开的一些实施例的用于制造均参照图2描述的多个单位单元100中的相邻单位单元100的方法的流程图。图6a至图6l是图5所示制造过程中的中间体结构的截面示意图。特别地,图6f至图6j是示出用于形成和钝化单位单元100中的sot层104和mtj102的中间体结构的放大示意图。图7a至图7e是图6f至图6j所示的中间体结构的示意性平面图。

[0131]

参考图5和图6a,执行步骤s600,并且在基底200的表面区域上形成多个写入晶体管wt以及多个读取晶体管rt。如参考图1a和图2所描述,多个单位单元100中的每一个可以包括多个写入晶体管wt中的一者和多个读取晶体管rt中的一者。在这些晶体管是平面型晶体管的那些实施例中,写入晶体管wt包括形成在基底200的平面表面之上的写入字线wwl,以及形成在基底200的浅区域中的多个源极/漏极结构700。类似地,读取晶体管rt包括形成在基底200的平面表面之上的读取字线rwl和形成在基底200的浅区域中的多个源极/漏极结构700。写入字线wwl和读取字线rwl分别通过栅极介电层702而与基底200隔开。在一些实施例中,多个隔离晶体管dt与写入晶体管wt和读取晶体管rt一起形成。在这些实施例中,多条虚设字线dwl分别形成在写入晶体管wt和相邻的读取晶体管rt之间,并且分别通过栅极介电层702与基底200隔开。

[0132]

需要说明的是,写入晶体管wt、读取晶体管rt和隔离晶体管dt在此描述为平面型晶体管。然而,如参考图2所描述的,写入晶体管wt、读取晶体管rt和隔离晶体管dt可以替代地形成为鳍型晶体管或gaa晶体管,并且写入晶体管wt、读取晶体管rt和隔离晶体管dt中的

组件的结构可以相应地修改。

[0133]

参考图5和图6b,执行步骤s602,并且在基底200之上形成介电层704以及多个接触插栓202。介电层704可以覆盖多个写入晶体管wt、多个读取晶体管rt和多个隔离晶体管dt。多个接触插栓202沿方向z穿通介电层704,以建立与多个源极/漏极结构700之间的电连接。在一些实施例中,介电层704和多个接触插栓202通过镶嵌工艺(例如,单镶嵌工艺)形成。

[0134]

参考图5和图6c,进行步骤s604,并且在介电层704上形成介电层706以及多条源极线sl和多个着陆垫204。介电层706可以侧向包围多条源极线sl和多个着陆垫204,且多条源极线sl和多个着陆垫204垂直地与多个接触插栓202重叠并与多个接触插栓202电连接。一对源极线sl和着陆垫204通过在其间的多个接触插栓202与每个写入晶体管wt的多个源极/漏极结构700相连。类似地,一对源极线sl和着陆垫2074通过在其间的多个接触插栓202与每个读取晶体管rt的多个源极/漏极结构700相连。在一些实施例中,形成介电层706、源极线sl和着陆垫204的方法包括镶嵌工艺。

[0135]

参考图5和图6d,执行步骤s606,并且在介电层706上形成介电层708以及多个底部通孔206。多个底部通孔206可以沿方向z穿过介电层708,以与多个着陆垫204建立电连接。如此一来,每个写入晶体管wt的多个源极/漏极结构700中的一个与相应的源极线sl相连,而每个写入晶体管wt的多个源极/漏极结构700中的另一个通过在其间的相应的着陆垫204和接触插栓202与相应的底部通孔206相连。类似地,每个读取晶体管rt的多个源极/漏极结构700中的一个与相应的源极线sl相连,而每个读取晶体管rt的多个源极/漏极结构700中的另一个通过在其间的相应的着陆垫204和接触插栓202与相应的底部通孔206相连。在一些实施例中,形成介电层708和底部通孔206的方法包括镶嵌工艺(例如,单镶嵌工艺)。

[0136]

参考图5和图6e,进行步骤s608,并且在介电层708上全面地形成自旋霍尔材料层710。自旋霍尔材料层710将被图案化以在随后的步骤中形成如参考图1a和图2所述的多个sot层104。在一些实施例中,自旋霍尔材料层710包括一种或多种重金属或掺杂有重金属的材料。在某些实施例中,pt、α-w、β-w、β-ta、aupt、w3ta、bi

x

sey、bisete、其多层结构、其合金等或其组合用于作为自旋霍尔材料层710的材料。在一些实施例中,形成自旋霍尔材料层710的方法可以包括溅射工艺或共溅射工艺,并且可以包括后续的热处理。在一些实施例中,热处理是退火工艺。在一些实施例中,热处理的工艺温度介于从约350℃至约450℃的范围内,且热处理的工艺时间介于从约10分钟至约60分钟的范围内。

[0137]

此后,执行步骤s610,并在自旋霍尔材料层710上形成多层结构712。多层结构712将被图案化以在随后的步骤中形成如参考图1a和图2所描述的mtj102。在一些实施例中,形成多层结构712的方法包括多个沉积工艺,且每个沉积工艺包括溅射工艺、共溅射工艺或其组合。

[0138]

此外,阻障材料层(未示出)可以在形成多层结构712之前可选地形成在自旋霍尔材料层710上,并且可以被图案化以形成如参考图3e所描述的扩散阻障件344,所述图案化连同多层结构712的图案化一起。在一些实施例中,形成阻障材料层的方法包括溅射工艺或共溅射工艺。

[0139]

需要说明的是,根据一些实施例,下文描述的mtj102和多层结构712仅用于详述形成单位单元100的制造工艺。在单位单元100使用参考图3b描述的mtj102a、参考图3c描述的mtj102b或参考图3d描述的mtj102c的替代实施例中,可以形成对应的多层结构而不是多层

结构712在当前步骤中的自旋霍尔材料层710上。

[0140]

参考图5、图6f和图7a,进行步骤s612,并在多层结构712上形成掩模图案pr1。掩模图案pr1可以具有多个分离的部分。掩模图案pr1的每个部分经配置为限定随后形成的sot层104的边界,并且在每个单位单元100中垂直地重叠一对底部通孔206。在一些实施例中,掩模图案pr1是光刻胶图案。在一些实施例中,掩模图案pr1通过光刻工艺形成。

[0141]

参考图5、图6g和图7b,进行步骤s614,使用掩模图案pr1对自旋霍尔材料层710和多层结构712进行图案化。自旋霍尔材料层710被图案化以形成sot层104。形成经图案化多层结构712’,并将在随后的步骤中进一步图案化以形成mtj102。目前,经图案化多层结构712’的边界与sot层104的边界实质上对齐,如图6g和图7b所示。一种或多种刻蚀工艺(例如,各向异性刻蚀工艺)可用于sot层104和经图案化多层结构712’的当前图案化工艺。在刻蚀工艺期间,掩模图案pr1可以用作阴影掩模(shadow mask)。此外,掩模图案pr1可以在sot层104和经图案化多层结构712’通过例如剥离工艺或灰化工艺形成之后去除。

[0142]

参考图5、图6h和图7c,进行步骤s616,在经图案化多层结构712’上形成掩模图案pr2。掩模图案pr2可以具有多个分离的部分。掩模图案pr2的每个部分经配置为限定随后形成的mtj102的边界,并且位于每个单位单元100中的一对底部通孔206之间。在一些实施例中,掩模图案pr2是光刻胶图案。在一些实施例中,掩模图案pr2通过光刻工艺形成。

[0143]

参考图5、图6i和图7d,执行步骤s618,并且进一步将经图案化多层结构712’图案化以形成mtj102。随着mtj102的缩小,mtj102的边界可能不会与掩模图案pr2的边界完全重叠。例如,掩模图案pr2可以具有矩形边界,而mtj102可以具有从掩模图案pr2的矩形边界侧向凹陷的椭圆形边界。一种或多种刻蚀工艺(例如,各向异性刻蚀工艺)可以用于mtj102的当前图案化工艺。在刻蚀工艺期间,掩模图案pr2可以用作阴影掩模。此外,可以在通过例如剥离工艺或灰化工艺形成mtj102之后去除掩模图案pr2。

[0144]

参考图5、图6j和图7e,执行步骤s620,并且在介电层708之上形成钝化层714。在一些实施例中,钝化层714全面地沉积,并且介电层708、多个sot层104和多个mtj102被钝化层714所覆盖。此外,在一些实施例中,钝化层714共形地分布在介电层708、多个sot层104和多个mtj102上。钝化层714可以由绝缘材料形成,例如al2o3、sinx、siox、mgo。此外,在一些实施例中,形成钝化层714的方法包括沉积工艺,例如化学气相沉积(cvd)工艺。

[0145]

参考图5和图6k,执行步骤s622,并且在介电层708之上形成介电层716以及多个顶部通孔208。介电层716可以形成为超过钝化层714的最顶表面的高度,使得钝化层714可以被介电层716完全覆盖。多个顶部通孔208从介电层716的顶表面通过介电层716和钝化层714沿方向z延伸到多个mtj102的顶表面。在一些实施例中,形成介电层716和顶部通孔208的方法包括镶嵌工艺(例如,单镶嵌工艺)。

[0146]

参考图5和图6l,执行步骤s624,并且在介电层716上形成介电层718以及多条位线bl。介电层718侧向包围多个位线bl。多个位线bl与多个顶部通孔208垂直地重叠并与多个顶部通孔208电连接。在一些实施例中,形成介电层718和位线bl的方法包括镶嵌工艺(例如,单镶嵌工艺)。在替代实施例中,介电层716、介电层718、顶部通孔208和位线bl通过双镶嵌工艺形成。

[0147]

至此,形成了参考图1a和图2描述的存储阵列10中的单位单元100。应当注意的是,图2中省略了参考图6a至图6l和图7a至图7e描述的一些组件(例如,介电层704、706、708、

716、718和钝化层714)。尽管多个sot层104和多个mtj102被描述为形成在自beol结构be底部起的第一和第二金属化层之间,但是多个sot层104和多个mtj102可以替代地形成在beol结构be中的其他垂直地相邻的金属化层之间,且可以在beol结构be中形成更多导电特征,以用于对所述sot层104和所述mtj102进行布线。此外,可以执行进一步的beol工艺以形成装置晶片。此外,装置晶片可进行封装工艺以形成多个半导体封装。

[0148]

图8是绘示根据本公开的一些实施例的存储阵列90的电路图。

[0149]

参照图8,与参照图1a描述的存储阵列10类似,存储阵列90包括沿行和列排列的多个单位单元900。具体来说,如图8所示,多个单位单元900的每一行都沿着方向x排列,而多个单位单元900的每一列都沿着方向y排列。此外,多个单位单元900的每一列都与一对写入字线wwl和读取字线rwl耦合,而多个单位单元900的每一行与一对位线bl和源极线sl耦合。虽然未示出,但是写入字线wwl和读取字线rwl可以与字线驱动电路耦合,位线bl可以与位线驱动电路耦合,并且源极线sl可以与电流源电路耦合,如参考图1a所描述的。

[0150]

每个单位单元900包括mtj902和与mtj902中的合成自由层接触的sot层904。如将参考图9所描述,mtj902和sot层904的堆叠顺序可以不同于参考图2描述的mtj102和sot层104的堆叠顺序。此外,在一些实施例中,sot层904通过选择器s与对应的写入字线wwl耦合,同时与对应的读取字线rwl耦合,其间没有选择器或晶体管。此外,在一些实施例中,mtj902通过读取晶体管rt与位线bl耦合。

[0151]

选择器s是由一对电极和夹置在所述电极之间的切换层(switching layer)形成的两端开关装置。当在所述电极上设置足够的偏压时,选择器s将导通,并且电流可以流过选择器s。另一方面,如果选择器s没有设置偏压或偏置电压不足,选择器s处于关断状态,且可能会阻止电流流过选择器s。如此一来,sot层904和写入字线wwl之间的耦合可以由选择器s控制。在一些实施例中,选择器s是指数型选择器(exponential type selector)或阈值型选择器(threshold type selector)。在指数类型选择器上可以观察到指数iv曲线;而在阈值类型选择器上可以观察到「回弹(snapback)」iv曲线。例如,指数型选择器可以是金属-绝缘体-金属(metal-insulator-metal;mim)型的选择器,且阈值型选择器可以是阈值切换选择器(例如,双向阈值切换(ovonic threshold switching;ots)选择器、金属-绝缘体-过渡(metal-insulator-transition;mit)选择器、场辅助超线性阈值(field assist superlinear threshold;fast)选择器、混合离子电子传导(mixed ionic-electron conduction;miec)选择器等)。

[0152]

在写入操作期间,所选定的单位单元900的选择器s导通。通过在与所选定的单位单元900耦合的写入字线wwl和源极线sl之间设置电压差,写入电流wp可以从所选定的写入字线wwl通过在其间的选择器s和sot层904流向所选定的源极线sl,反之亦然。作为自旋轨道相互作用的结果,流经sot层904的写入电流wp可能在mtj902上引起sot,因此mtj902可进行写入。另一方面,所选定的单位单元900的读取晶体管rt可以与在未选定的多个单位单元900中的多个选择器s和多个读取晶体管rt一起保持在关断状态。

[0153]

在读取操作期间,所选定的单位单元900的读取晶体管rt导通。通过在与所选定的单位单元900耦合的位线bl和源极线sl之间设置电压差,读取电流rp可以通过在其间的sot层904、mtj102和读取晶体管rt从所选定的源极线sl流到所选定的位线bl,反之亦然。由于自旋轨道耦合效应,mtj902的不同磁化取向(即平行状态和反平行状态)可能导致mtj902的

不同电阻,并可能影响读取电流rp的值或mtj902两端的电压降值。因此,可以读出储存在mtj902中的位数据。另一方面,所选定的单位单元900的选择器s与在未所选定的多个单位单元900中的多个读取晶体管rt和多个选择器s一起保持在关断状态。

[0154]

图9是根据本公开的一些实施例示出如图8所示的存储阵列90中的多个单位单元900中的相邻单位单元的示意性三维视图。图9中所示的单位单元900的结构类似于参考图2所述的单位单元100的结构。将仅描述单位单元100和单位单元900之间的差异,而单位单元100和单位单元900中相同或类似的部分不再重复。

[0155]

参考图9,feol结构fe可以不再包括参考图2描述的写入晶体管wt。此外,与读取晶体管rt耦合的位线bl可以与多个着陆垫204一起是beol结构be中底部金属化层的一部分。位线bl和多个着陆垫204可以通过多个接触插栓202与多个读取晶体管rt的多个源极和漏极端子连接。多个通孔1000可分别沿方向z立于多个着陆垫204上。在一些实施例中,另一金属化层中的多个着陆垫1002设置在多个通孔1000上。多个着陆垫1002与多个通孔1000垂直地重叠并与多个通孔1000电连接。

[0156]

根据一些实施例,多个mtj902从多个sot层904下方与所述sot层904接触,而不是立于所述sot层904上。详细地,如图9所示,多个mtj902立于多个着陆垫1002上,且多个sot层904位于并堆叠在多个mtj902上。mtj902可包括如参考图3a所述的mtj102中的多个层、如参考图3b所述的mtj102a中的多个层、如参考图3c所述的mtj102b中的多个层或如参考图3d所述的mtj102c中的多个层,但具有相反的堆叠顺序。换言之,合成自由层300、300a、300b或300c可以是mtj902中的顶部层,而顶盖层328可以是mtj902中的底部层。此外,除了sot层904位于mtj902上之外,sot层904可以与参考图1a、图2描述的sot层104相同。在一些实施例中,参考图3e所描述的扩散阻障件344可以进一步设置在mtj902和sot层904之间。进一步地,多个通孔1004可以立在多个sot层904,且多个着陆垫1006以及多条源极线sl覆盖多个通孔1004并与多个通孔1004电连接。每个sot层904可以通过在其间的多个通孔1004与多条源极线sl中的一者和多个着陆垫1006中的一者连接。

[0157]

多个选择器s可以设置在多个着陆垫1006上。在一些实施例中,多个选择器s包括多个底部通孔1008、与所述底部通孔1008重叠的多个顶部通孔1010、以及位于所述底部通孔1008和所述顶部通孔1010之间的切换层1012。在这些实施例中,如图9所示,多个选择器s共享公共的切换层1012。可以选择切换层1012的材料,使得当设置偏压时,电子可以以最短距离流动通过切换层1012,而不是进入相邻的单位单元900。换句话说,所述设置偏压具有局部效应,因此即使切换层1012侧向延伸到相邻的单位单元900,所述设置偏压也可能仅局部地有效以允许电子沿方向z(即垂直方向)流过切换层1012(例如,从顶部通孔1010到底部通孔1008,反之亦然)。例如,切换层1012可以由包括氧化铪的材料形成,并且可以掺杂有cu、al、n、p、s、si、zr、gd、ti、la、ti等或其组合。此外,多条写入字线wwl可分别位于多个顶部通孔1010上。

[0158]

通过使用集成在beol结构be中的多个选择器s来代替多个写入晶体管wt,可以显著减少每个单位单元900的占用面积。因此,可以有效地增加存储阵列90的储存密度。此外,通过在多个mtj902之上设置多个sot层904,可以在不影响用于写入操作的自旋轨道相互作用的情况下,更灵活地选择作为mtj902的成长模板的晶种层(未示出)的材料。因此,多个mtj902中的多个层可以具有改进的结晶特性,并且可以增强多个mtj902的穿隧式磁阻

(tunneling magnetoresistance,tmr)。

[0159]

图10是示出根据本公开的一些实施例的用于制造参照图9描述的多个单位单元900的相邻单位单元900的方法的流程图。图11a至图11l是图10所示制造过程中的中间体结构的示意性剖视图。

[0160]

需要说明的是,图10和图11a至图11l所示的制造工艺与参照图5和图6a至图6l描述的制造工艺相似,因此仅描述这些制造工艺之间的差异。这些制造过程中相同或相似的部分不再赘述,且相同或相似的组件可以相同的标号指代。作为实例,相似/相同的部分可以包括:使用单镶嵌工艺、双镶嵌工艺或其组合来形成介电层和介电层中的导电特征(例如,接触插栓、着陆垫和通孔)。

[0161]

参考图10和图11a,执行步骤s1100,并且在基底200的表面区域上形成多个读取晶体管rt。在一些实施例中,多个隔离晶体管dt与多个读取晶体管rt一起形成。在这些实施例中,多条虚设字线dwl分别形成在多条读取字线rwl中的相邻的读取字线rwl之间。详细地,如图11a所示,虚设字线dwl沿方向x与对应的读取字线rwl侧向间隔开。

[0162]

参考图10和图11b,执行步骤s1102,并且在基底200之上形成介电层704以及多个接触插栓202。多个接触插栓202沿方向z穿过介电层704,以与多个读取晶体管rt的多个源极/漏极结构700建立电连接。

[0163]

参考图10和图11c,执行步骤s1104,并且在介电层704之上形成介电层706以及多条位线bl和多个着陆垫204。多条位线bl和多个着陆垫204被介电层704侧向包围。每个读取晶体管rt的多个源极/漏极结构700通过在其间的多个接触插栓202与多个着陆垫204中的一者和多条位线bl中的一者连接。尽管下文另有说明,但同一行中的相邻的读取晶体管rt可以与相同的位线bl耦合,如参考图8所述。

[0164]

参考图10和图11d,执行步骤s1106,并且在介电层706之上形成介电层1200、介电层1202以及多个通孔1000和多个着陆垫1002。介电层1202沿方向z堆叠在介电层1200上。多个通孔1000垂直地延伸穿过介电层1200,以到达嵌入在介电层706中的下伏的多个着陆垫204,从而与所述着陆垫204建立电连接。多个着陆垫1002被介电层1202侧向包围,并分别与多个通孔1000垂直地重叠和电连接。

[0165]

参考图10和图11e,进行步骤s1108,在介电层1202上形成多层结构1204。多层结构1204将被图案化以在随后的步骤中形成如参考图8和图9所述的mtj902。在一些实施例中,形成多层结构1204的方法包括多个沉积工艺,且每个沉积工艺包括溅射工艺、共溅射工艺或其组合。

[0166]

在一些实施例中,在形成多层结构1204之前,在介电层1202上预形成电极层1206。在这些实施例中,电极层1206可以与随后的步骤中的多层结构1204一起被图案化。形成电极层1206的方法可以包括溅射工艺或共溅射工艺。

[0167]

参考图10和图11f,执行步骤s1110,并且图案化多层结构1204以形成多个mtj902。这种图案化可以包括光刻工艺和一个或多个刻蚀工艺。在其中在形成多层结构1204之前在介电层1202上预形成电极层1206的那些实施例中,可以将电极层1206与多层结构1204一起图案化,以形成多个电极1208。

[0168]

参考图10和图11g,执行步骤s1112,并且形成介电层1210以侧向包围多个mtj902。形成介电层1210的方法可以包括沉积工艺(例如,cvd工艺)和平坦化工艺(例如,研磨工艺、

刻蚀工艺或其组合)。

[0169]

参考图10和图11h,执行步骤s1114,并且在介电层1210之上形成介电层1212以及多个sot层904。多个sot层904被介电层1212侧向包围。根据一些实施例,用于形成介电层1212的方法可以包括在介电层1210和多个mtj902上形成介电材料层。随后,可以通过光刻工艺和刻蚀工艺对介电材料层进行图案化以形成具有多个开口的介电层1212。此后,自旋霍尔材料层可以形成在介电层1212上,并且可以填充介电层1212的多个开口。在一些实施例中,形成自旋霍尔材料层的方法可以包括溅射工艺或共溅射工艺,并且可以包括后续的热处理。此外,可以执行平坦化工艺以去除介电层1212上方的自旋霍尔材料层的多个部分。在多个开口中的自旋霍尔材料层的剩余部分可以形成多个sot层904。

[0170]

参考图10和图11i,执行步骤s1116,并且在介电层1212之上形成介电层1214、介电层1216以及多个通孔1004、多条源极线sl和多个着陆垫1006。介电层1216沿方向z堆叠在介电层1214上。多个通孔1004垂直地穿过介电层1214,以到达嵌入在介电层1212中的多个sot层904,从而与所述sot层904建立电连接。多个着陆垫1006和多条源极线sl被介电层1216侧向包围,且与多个通孔1004垂直地重叠并电连接。每个sot层904可以通过在其间的多个通孔1004与多条源极线sl中的一者和多个着陆垫1006中的一者电连接。需要注意的是,尽管在下文中另有说明,但同一行中相邻的读取晶体管rt可以与相同的源极线sl耦合,如参考图8所述。

[0171]

参考图10和图11j,执行步骤s1118,并且在介电层1216之上形成介电层1218和多个选择器s的多个底部通孔1008。多个底部通孔1008垂直地穿过介电层1218,以到达多个着陆垫1216,从而与所述着陆垫1216建立电连接。

[0172]

参考图10和图11k,进行步骤s1120,并且在介电层1218上形成多个选择器s的切换层1012。根据一些实施例,切换层1012全面地形成在介电层1218上。在一些实施例中,形成切换层1012的方法包括沉积工艺,例如cvd工艺或物理气相沉积(physical vapor deposition;pvd)工艺。

[0173]

参考图10和图11l,执行步骤s1122,并且在切换层1012之上形成介电层1220、介电层1222以及多个选择器s的多个顶部通孔1010和多条写入字线wwl。介电层1222沿方向z堆叠在介电层1220上。多个顶部通孔1010垂直地穿过介电层1222,以到达切换层1012,且沿方向z可与多个底部通孔1008重叠。多条写入字线wwl被介电层1222侧向包围,并与多个顶部通孔1010垂直地重叠并电连接。

[0174]

至此,形成了参考图8和图9描述的存储阵列90中的多个单位单元900。需要说明的是,图11a至图11l所描述的一些组件(例如介电层704、706、1200、1202、1210、1212、1214、1216、1218和电极1208)在图9中省略绘示。尽管多个sot层904和多个mtj902被描述为形成在自beol结构be底部起的第二和第三金属化层之间,但是多个sot层904和多个mtj902可以替代地形成在beol结构be中的其他垂直地相邻的金属化层之间,且可以在beol结构be中形成更多或更少的导电特征,以用于对所述sot层904和所述mtj902进行布线。此外,可以执行进一步的beol工艺以形成装置晶片。此外,装置晶片可进行封装工艺以形成多个半导体封装。

[0175]

应当注意的是,虽然包括立在sot层104上的mtj102的第一型储存组件被描述为由feol结构fe中的写入晶体管wt和读取晶体管rt驱动(如图2所示),并且包括自下方与sot层

904接触的mtj902的第二型储存组件被描述为由feol结构fe中的读取晶体管wt和beol结构be中的选择器s驱动(如图9所示),第一型储存组件可以替代地由晶体管和选择器的组合驱动,而第二型储存组件可以替代地由两个晶体管驱动。其他驱动方案也可用于第一型储存组件和第二型储存组件,并且驱动器和储存组件之间的布线可以相应地修改。本公开不限制储存组件的驱动方案。

[0176]

根据实施例,存储器装置包括基底、自旋轨道扭矩层和磁性穿隧接面。磁性穿隧接面与自旋轨道扭矩层堆叠于基底之上,且包括合成自由层、阻障层和参考层。合成自由层包括合成反铁磁结构、第一间隔件层和自由层,其中合成反铁磁结构设置在自旋轨道扭矩层和自由层之间,并且合成反铁磁结构经配置为改变自由层的磁化方向。

[0177]

根据实施例,存储器装置包括基底、自旋轨道扭矩层和磁性穿隧接面。磁性穿隧接面与自旋轨道扭矩层堆叠于基底之上,且包括合成自由层、阻障层和参考层。合成自由层包括合成反铁磁结构、第一间隔件层和自由层,其中合成反铁磁结构设置在自旋轨道扭矩层和自由层之间,并且合成反铁磁结构经配置为改变自由层的磁化方向。阻障层设置于所述合成自由层旁。参考层设置在所述阻障层旁。

[0178]

在一些实施例中,所述合成反铁磁结构包括:第一铁磁层,具有第一磁化方向;第二铁磁层,具有不同于所述第一磁化取向的第二磁化方向;以及第二间隔件层,位于所述第一铁磁层和所述第二铁磁层之间。

[0179]

在一些实施例中,所述合成自由层还包括:第超顺磁性层,位在所述自旋轨道扭矩层和所述合成反铁磁结构之间;以及第三间隔件层,位在所述超顺磁性层和所述合成反铁磁结构之间。

[0180]

在一些实施例中,所述第一铁磁层和所述第二铁磁层中的每一个包括钴-铬合金、钴-铁-镍合金或钴-铁合金。

[0181]

在一些实施例中,所述第一间隔件层、所述第二间隔件层和所述第三间隔件层中的每一个包括ru、w、v或ti,并且所述第一间隔件层、所述第二间隔件层和所述第三间隔件层中的每一个的厚度介于从0.2nm到1.5nm的范围内。

[0182]

在一些实施例中,所述超顺磁性层包括钨-钴合金。

[0183]

在一些实施例中,所述存储器装置还包括位于所述磁性穿隧接面和所述自旋轨道扭矩层之间的扩散阻障件,其中所述扩散阻障件由非磁性导电材料形成。

[0184]

根据实施例,存储器装置包括写入晶体管、读取晶体管、自旋轨道扭矩层、磁性穿隧接面和位线。写入晶体管和读取晶体管形成在基底的表面区域上。自旋轨道转矩层位于写入晶体管和读取晶体管之上,并与写入晶体管的第一端子和读取晶体管的第二端子电连接。磁性穿隧接面立于自旋轨道扭矩层上,且通过磁性穿隧接面的第一端子与自旋轨道扭矩层电耦合,其中磁性穿隧接面包括合成自由层、阻障层和参考层。合成自由层包括合成反铁磁结构、自由层以及在合成反铁磁结构和自由层之间的第一交换耦合金属层,其中合成反铁磁结构比自由层更接近自旋轨道扭矩层。阻障层位于合成自由层之上。参考层设置在阻障层之上。位线与磁性穿隧接面的第二端子电耦合。

[0185]

根据实施例,存储器装置包括写入晶体管、读取晶体管、自旋轨道扭矩层、磁性穿隧接面和位线。写入晶体管和读取晶体管形成在基底的表面区域上。自旋轨道转矩层位于写入晶体管和读取晶体管之上,并与写入晶体管的一端子和读取晶体管的一端子电连接。

磁性穿隧接面立于自旋轨道扭矩层上,且通过磁性穿隧接面的第一端子与自旋轨道扭矩层电耦合,其中磁性穿隧接面包括合成自由层、阻障层和参考层。合成自由层包括合成反铁磁结构、自由层以及在合成反铁磁结构和自由层之间的第一交换耦合金属层,其中合成反铁磁结构比自由层更接近自旋轨道扭矩层。阻障层位于合成自由层之上。参考层设置在阻障层之上。位线与磁性穿隧接面的第二端子电耦合。

[0186]

在一些实施例中,所述写入晶体管的所述端子是所述写入晶体管的多个源极和漏极端子中的一者,所述读取晶体管的所述端子是所述读取晶体管的多个源极和漏极端子中的一者;以及所述合成反铁磁结构包括:第一铁磁层,具有第一磁化方向;第二铁磁层,具有不同于所述第一磁化方向的第二磁化方向;以及第二交换耦合金属层,位于所述第一铁磁层和所述第二铁磁层之间。

[0187]

在一些实施例中,所述第一铁磁层和所述第二铁磁层中的每一个包括钴-铬合金或钴-铁-镍合金,所述钴-铬合金表示为co

1-x

cr

x

,其中0.05《x《0.2,且所述钴-铁-镍合金表示为co

x-fe

y-niz,其中x《0.5,y《0.3,z》0.5。

[0188]

在一些实施例中,所述第一铁磁层和所述第二铁磁层中的每一个包括两个铁磁子层和夹置在所述两个铁磁子层之间的间隔件层,所述两个铁磁子层中的每一个包括钴-铁合金,所述钴-铁合金表示为co

x

fey,其中0.1《x《0.4,0.5《y《0.8,x+y=1,所述间隔件层包括ru、w、v、ti、cr、cu、al或ni。

[0189]

在一些实施例中,所述合成自由层还包括:超顺磁性层,位在所述自旋轨道扭矩层和所述合成反铁磁结构之间;以及非磁性间隔件层,位在所述超顺磁性层和所述合成反铁磁结构之间,其中所述超顺磁性层包含钨-钴合金,所述钨-钴合金表示为w

1-x

co

x

,其中0.01《x《0.5。

[0190]

在一些实施例中,所述存储器装置还包括钝化层,共形地覆盖所述磁性穿隧接面的侧壁和顶表面以及所述自旋轨道扭矩层的顶表面。

[0191]

在一些实施例中,所述存储器装置还包括:第一源极线,位于所述写入晶体管和所述读取晶体管之上,且与所述写入晶体管的另一个源极/漏极端子电耦合;以及第二源极线,位于所述写入晶体管和所述读取晶体管之上,并与所述读取晶体管的另一个源极/漏极端子电耦合。

[0192]

在一些实施例中,所述存储器装置还包括虚设字线,位于所述基底上并位于所述写入晶体管和所述读取晶体管之间。

[0193]

根据实施例,存储器装置包括读取晶体管、位线、自旋轨道扭矩层、磁性穿隧接面、选择器和写入字线。读取晶体管形成在基底的表面区域上,并且包括在基底上延伸的读取字线。位线位于读取字线之上并与读取晶体管的第一端子耦合。自旋轨道转矩层设置在读取晶体管之上。磁性穿隧接面设置在自旋轨道扭矩层下,其中磁性穿隧接面通过磁性穿隧接面的第一端子与读取晶体管的第二端子电耦合,并通过磁性穿隧接面的第二端子与自旋轨道扭矩层电耦合,以及磁性穿隧接面包括合成自由层、阻障层和参考层。合成自由层包括合成反铁磁结构、自由层以及在合成反铁磁结构与自由层之间的第一交换耦合金属层,其中合成反铁磁结构设置在自旋轨道扭矩层和第一交换耦合金属层之间。阻障层位于合成自由层下。参考层设置在阻障层下。选择器设置在自旋轨道扭矩层之上,并通过选择器的第一端子与自旋轨道扭矩层电耦合。写入字线位于选择器之上,并与选择器的第二端子电耦合。

[0194]

在一些实施例中,所述读取晶体管的所述第一端子是所述读取晶体管的多个源极/漏极端子中的一者,所述读取晶体管的所述第二端子是所述读取晶体管的所述多个源极/漏极端子中的另一者;以及所述合成反铁磁结构包括:第一铁磁层,具有第一磁化方向;第二铁磁层,具有不同于所述第一磁化方向的第二磁化方向;以及第二交换耦合金属层,位于所述第一铁磁层和所述第二铁磁层之间。

[0195]

在一些实施例中,所述第一铁磁层和所述第二铁磁层中的每一个包括单一层,所述单一层包括钴-铬合金或钴-铁-镍合金,所述钴-铬合金表示为co

1-x

cr

x

,其中0.05《x《0.2,所述钴-铁-镍合金表示为co

x-fe

y-niz,其中x《0.5,y《0.3,z》0.5。

[0196]

在一些实施例中,所述第一铁磁层和所述第二铁磁层中的每一个包括多层结构,所述多层结构包括钴-铁合金,所述钴-铁合金表示为co

x

fey,其中0.1《x《0.4,0.5《y《0.8,x+y=1,间隔件层包括ru、w、v、ti、cr、cu、al或ni。

[0197]

在一些实施例中,所述合成自由层还包括:超顺磁性层,位在所述自旋轨道扭矩层和所述合成反铁磁结构之间;以及非磁性间隔件层,位于所述超顺磁性层和所述合成反铁磁结构之间,其中所述超顺磁性层包含钨-钴合金,所述钨-钴合金表示为w

1-x

co

x

,其中0.01《x《0.5。

[0198]

以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,其可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,此种等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下对其作出各种改变、代替及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1