半导体装置的形成方法与流程

1.本发明实施例是关于半导体装置,特别是关于纳米结构。

背景技术:

2.全绕式栅极(gate-all-around;gaa)场效晶体管(field effect transistor;fet)为一种栅极结构(例如,全绕式栅极结构)围绕电流通道的多个侧壁以影响来自各个方向的电流并减少短通道效应(short channel effects;sce)的晶体管。在全绕式栅极场效晶体管中,并不是提供鳍片作为电流通道,电流通道是采取使用一或多个硅纳米线将源极区以及漏极区耦合的形式来提供。

技术实现要素:

3.本发明实施例提供一种半导体装置的形成方法,包含形成纳米结构,所述纳米结构具有第一材料的第一组膜层以及与所述第一组膜层交替的具有第二材料的第二组膜层;沉积硬遮罩于所述第一组膜层的顶层上,所述硬遮罩包含位于所述第一组膜层的顶层上的第一硬遮罩层以及位于所述第一硬遮罩层上的第二硬遮罩层;沉积披覆结构的多个元件于所述纳米结构以及所述硬遮罩的多个侧壁上;移除所述披覆结构的顶部;以及在移除所述披覆结构的顶部之后,移除所述第二硬遮罩层。

4.本发明实施例提供一种半导体装置的形成方法,包含形成纳米结构,所述纳米结构在第一高度具有顶表面;以及形成披覆结构,所述披覆结构在第二高度具有顶表面,所述纳米结构设置于所述披覆结构的多个元件之间,其中形成在所述第二高度具有顶表面的披覆结构包含形成硬遮罩于所述纳米结构上;形成披覆结构于所述纳米结构的多个侧壁上以及于所述硬遮罩的多个侧壁上;移除所述披覆结构的第一顶部;在移除所述披覆结构的第一顶部之后,移除所述硬遮罩;以及在移除所述硬遮罩之后,移除所述披覆结构的第二顶部,且其中所述纳米结构的顶表面包括硅基的结构,所述硅基的结构具有实质上平坦的顶表面,所述实质上平坦的顶表面自所述披覆结构的多个元件的第一元件延伸至所述披覆结构的多个元件的第二元件。

5.本发明实施例提供一种半导体装置的形成方法,包含沉积第一硬遮罩层于纳米结构上;沉积第二硬遮罩层于所述第一硬遮罩层上;沉积披覆结构的多个元件于所述纳米结构、所述第一硬遮罩层、以及所述第二硬遮罩层的多个侧壁上;沉积材料于所述第二硬遮罩层的顶表面上以及于所述披覆结构的顶表面上;对半导体装置的顶表面执行平坦化操作以自所述披覆结构的顶表面以及自所述第二硬遮罩层的顶表面移除所述材料;在执行所述平坦化操作之后,移除所述披覆结构的第一顶部;在移除所述披覆结构的所述第一顶部之后,移除所述第二硬遮罩层;以及在移除所述第二硬遮罩层之后,移除所述披覆结构的第二顶部以及移除所述第一硬遮罩层。

附图说明

6.由以下的详细叙述配合所附图式,可最好地理解本发明实施例。应注意的是,依据在业界的标准做法,各种特征并未按照比例绘制且仅用于说明。事实上,可任意地放大或缩小各种元件的尺寸,以清楚地表现出本发明实施例之特征。

7.图1为可实施本公开所描述的系统及/或方法的例示性环境的示意图。

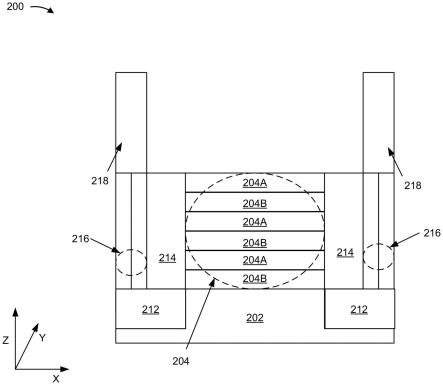

8.图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h、图2i、图2j以及图2k为本公开所描述的形成半导体装置的例示性实施例的示意图。

9.图3为图1的一或多个装置的例示性组件的示意图。

10.图4、图5以及图6为关于制造硅刻面的方法的例示性制程的方法流程图。

11.其中,附图标记说明如下:

12.100:环境

13.102:沉积机台

14.104:蚀刻机台

15.106:平坦化机台

16.108:晶圆/晶粒转移机台

17.200:半导体装置

18.202:基板

19.204:纳米结构

20.204a:硅基的膜层

21.204b:硅基的膜层

22.208:第一硬遮罩层

23.210:第二硬遮罩层

24.212:隔离结构

25.214:披覆结构

26.216:介电结构

27.218:介电结构

28.220:平坦化操作

29.222:内凹部分

30.224:距离

31.300:装置

32.310:总线

33.320:处理器

34.330:存储器

35.340:存储元件

36.350:输入元件

37.360:输出元件

38.370:通信元件

39.400:制程

40.410:制程区块

41.420:制程区块

42.430:制程区块

43.440:制程区块

44.450:制程区块

45.500:制程

46.510:制程区块

47.520:制程区块

48.600:制程

49.610:制程区块

50.620:制程区块

51.630:制程区块

52.640:制程区块

53.650:制程区块

54.660:制程区块

55.670:制程区块

56.680:制程区块

57.x:坐标轴

58.y:坐标轴

59.z:坐标轴

具体实施方式

60.以下公开提供了许多的实施例或范例,用于实施所提供的标的物的不同元件。各元件和其配置的具体范例描述如下,以简化本发明实施例的说明。当然,这些仅仅是范例,并非用以限定本发明实施例。举例而言,叙述中若提及第一元件形成在第二元件之上,可能包含第一和第二元件直接接触的实施例,也可能包含额外的元件形成在第一和第二元件之间,使得它们不直接接触的实施例。此外,本发明实施例可能在各种范例中重复参考数值以及/或字母。如此重复是为了简明和清楚的目的,而非用以表示所讨论的不同实施例及/或配置之间的关系。

61.再者,其中可能用到与空间相对用词,例如「在

……

之下」、「下方」、「较低的」、「底部」、「上方」、「较高的」、及/或「顶部」等类似用词,是为了便于描述图式中一个(些)部件或特征与另一个(些)部件或特征之间的关系。空间相对用词用以包括使用中或操作中的装置的不同方位,以及图式中所描述的方位。当装置被转向不同方位时(旋转90度或其他方位),其中所使用的空间相对形容词也将依转向后的方位来解释。

62.在一些情况中,半导体装置的纳米结构(例如,用来形成全绕式栅极(gaa)晶体管的结构)的顶部可包含硅基的结构(例如,顶硅层(top silicon layer))。所述硅基的结构可沉积作为纳米结构延伸至披覆(cladding)结构的多个元件之间的膜层。在制造制程期间,硅基的结构可借由第一硬遮罩层以及第二硬遮罩层(例如,同样设置于披覆结构的多个元件之间的第一硬遮罩层以及第二硬遮罩层)来覆盖。第二硬遮罩层在对半导体装置的顶表面(例如,包含硬遮罩、披覆结构、及/或披覆结构外侧的介电结构的顶表面)进行平坦化

chemical vapor deposition;sacvd)机台、原子层沉积(atomic layer deposition;ald)机台、等离子体增强原子层沉积(plasma-enhanced atomic layer deposition;peald)机台、或其他类型的化学气相沉积机台。在一些实施例中,沉积机台102包含物理气相沉积(physical vapor deposition;pvd)机台,诸如溅镀(sputtering)机台或其他类型的物理气相沉积(pvd)机台。在一些实施例中,例示性环境100包含多个沉积机台102的类型。

67.蚀刻机台104为半导体制程机台,其能够蚀刻各种类型的基板、晶圆、或半导体装置的材料。举例来说,蚀刻机台104可包含湿式蚀刻机台、干式蚀刻机台、及/或其他类型的蚀刻机台。湿式蚀刻机台可包含化学蚀刻机台或其他类型的湿式蚀刻机台,其包含填充了蚀刻剂的腔室(chamber)。基板可在腔室中放置特定的时间区段以移除基板的一或多个部分的特定数量。干式蚀刻机台可包含等离子体蚀刻机台、激光蚀刻机台、反应离子蚀刻(reactive ion etching;rie)机台、或气相蚀刻机台等其他示例。干式蚀刻机台可使用溅镀技术、等离子体辅助蚀刻技术(例如,等离子体溅镀技术或其他类型的涉及使用离子化气体以等向性地(isotropically)或定向地(directionally)蚀刻一或多个部分的技术)、或其他类型的干式蚀刻技术来移除基板的一或多个部分。

68.平坦化机台106为半导体制程机台,其能够对晶圆或半导体装置的各种膜层进行抛光或者平坦化。举例来说,平坦化机台106可包含化学机械平坦化(chemical mechanical planarization;cmp)机台及/或其他类型的平坦化机台,其能对沉积或电镀的材料的膜层或表面进行抛光或平坦化。平坦化机台106可以使用化学与机械力的组合(例如,化学蚀刻以及自由磨料(abrasive)抛光)对半导体装置的表面进行抛光或平坦化。平坦化机台106可使用磨料以及腐蚀性化学研磨浆(slurry)并结合抛光垫以及固定环(retaining ring)(例如,通常大于半导体装置的直径)。抛光垫以及半导体装置可借由动态抛光头压在一起并借由固定环维持在一定的位置。动态抛光头可以以不同的旋转轴来旋转,以移除材料并平整半导体装置的任何不规则形貌(topography),使半导体装置平坦或成为平面。

69.晶圆/晶粒转移机台108包含移动机械、机械臂、电车(tram)或有轨车(rail car)、高架吊车转移(overhead hoist transfer;oht)机台、自动材料处理系统(automated material handling system;amhs)、及/或其他类型的机台,其用于在半导体制程机台102、104、与106之间转移晶圆及/或晶粒及/或往返于其他地点,诸如晶圆架、存储室、或其他地点。在一些实施例中,晶圆/晶粒转移机台108可为程序化机台,以行走特定的路径及/或可半自动地或自动地操作。

70.提供图1所绘示的机台数量以及配置来作为一或多个示例。在实际操作中,其可能有额外的机台、更少的机台、不同的机台、或不同于图1所绘示的机台配置。此外,可以在单一机台之中实施图1所绘示的两个或以上的机台,或者可以作为多个分布式机台实施图1所绘示的单一机台。额外地或者替代地,环境100的机台组合(例如,一或多个机台)可执行由环境100的另一个机台组合所执行的一或多个本公开描述的功能。

71.图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h、图2i、图2j以及图2k为本公开所描述的形成半导体装置200的例示性实施例的示意图。例示性实施例可为形成包含纳米结构晶体管的半导体装置的一部份的例示性制程,诸如纳米线(nanowire)晶体管、纳米片(nanosheet)晶体管、全绕式栅极(gaa)晶体管、及/或多桥接通道(multi bridge channel)晶体管等其他示例。半导体装置200可包含一或多个未绘示于图2a、图2b、图2c、图2d、图2e、

图2f、图2g、图2h、图2i、图2j以及图2k中的额外的装置、结构、及/或膜层。举例来说,半导体装置200可包含形成于图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h、图2i、图2j以及图2k中所绘示的半导体装置200的部分上方及/或下方的多个膜层上的额外膜层。额外地或者替代地,可形成一或多个具有横向位移的额外的半导体结构于相同的膜层中,如图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h、图2i、图2j以及图2k中所绘示的半导体装置200的部分。

72.如图2a所绘示,半导体装置200可包含基板202。基板202可包含半导体装置晶粒基板、半导体晶圆、或可在其中及/或其上形成半导体装置及/或半导体结构的其他类型的基板。在一些实施例中,基板202是由硅(si)、包含硅的材料、iii-v族化合物半导体材料诸如砷化镓(gaas)、绝缘体上覆硅(silicon on insulator;soi)、或其他类型的半导体材料所形成。基板可进一步包含一或多个以鳍片为主的结构。

73.交替地设置硅基的膜层204a(例如,纯硅及/或锗浓度小于1%的硅)以及硅基的膜层204b(例如,硅锗)于彼此的顶部上(例如,沿着半导体装置200的z方向)以形成堆叠。举例来说,硅基的膜层204a的其中一层设置于硅基的膜层204b的其中一层上方,接着硅基的膜层204b的另一层设置于硅基的膜层204a上方,依此类推。硅基的膜层204a以及硅基的膜层204b具有不同的材料成分(例如,其中一者为硅锗而另一者为硅)。

74.堆叠可包含以任意数目交替设置的硅基的膜层204a与硅基的膜层204b,其形成了纳米结构204。硅基的膜层204a与硅基的膜层204b可具有不同的厚度。每层硅基的膜层204a彼此可具有不同的厚度。每层硅基的膜层204b彼此可具有不同的厚度。每个硅基的膜层204a以及每个硅基的膜层204b的厚度之范围可为数纳米至数十纳米。无论硅基的膜层204a或者硅基的膜层204b都可形成为最底层的膜层(或者最接近基板202的膜层)。

75.硅基的膜层204a与硅基的膜层204b可自基板202成长。举例而言,每个硅基的膜层204a以及每个硅基的膜层204b可借由分子束外延(molecular beam epitaxy;mbe)制程、诸如金属有机化学气相沉积(metal organic chemical vapor deposition;mocvd)制程的化学气相沉积制程、及/或其他合适的成长制程来成长。在外延成长期间,基板202的晶体结构向上延伸,造成硅基的膜层204a与硅基的膜层204b具有与基板202相同的晶体排列。硅基的膜层204a与硅基的膜层204b沿着x方向连续地延伸。

76.纳米结构204可包含硅基的膜层204a的顶层。硅基的膜层204a的顶层可为纳米结构204的顶层且可形成纳米结构204的顶表面。硅基的膜层204a的顶层可被配置来提供通道于源极/漏极之间并穿过之后的沉积操作所沉积的栅极结构。在一些实施例中,在本公开的全文中,可使用另一种的材料(例如,其他不同于硅基的结构的材料)来代替硅基的膜层204a的顶层。举例来说,可使用另一种类型的通道材料或牺牲材料来代替硅基的膜层204a的顶层。

77.半导体装置200可包含第一硬遮罩层208于硅基的膜层204a的顶层的顶表面上(例如,纳米结构204的顶表面上)。半导体装置200可同样包含第二硬遮罩层210于第一硬遮罩层208的顶表面上。在一些实施例中,沉积机台(例如,沉积机台102)使用例如化学气相沉积(cvd)、及/或物理气相沉积(pvd)等其他示例沉积第一硬遮罩层208(例如,硅锗基的材料)于硅基的膜层204a的顶层的顶表面上,及/或沉积第二硬遮罩层210于第一硬遮罩层208的顶表面上。第二硬遮罩层210可包含硅基的材料,第二硬遮罩层210的材料与用来形成硅基的膜层204a的顶层的材料相同。

78.在一些实施例中,第一硬遮罩层208可沉积为大约2纳米至大约8纳米的厚度。如此一来,第一硬遮罩层208具有足够的厚度以允许在第二硬遮罩层210的移除期间(例如,导孔蚀刻)进行的一些蚀刻,但又不会过厚以免需要长时间的移除制程(例如,导孔蚀刻),这将影响制造效率。此外,具有不必要地大厚度的第一硬遮罩层208可能会增加制造半导体装置200的成本。

79.如图2b所绘示,可蚀刻硅基的膜层204a以及硅基的膜层204b的堆叠以形成一或多个鳍片结构。图2b仅绘示出单个鳍片结构,然而,堆叠可包含未绘示于图2b中的额外的鳍片结构。每个沿着半导体装置的y方向伸长的鳍片结构可包含彼此交替堆叠的硅基的膜层204a以及硅基的膜层204b的堆叠。半导体装置200可包含任意数目的鳍片结构,而仍维持在本公开的范围之内。

80.借由使用例如光学微影以及蚀刻技术图案化硅基的膜层204a、硅基的膜层204b、以及基板202来形成鳍片结构。举例来说,第二硬遮罩层210形成于最上方的硅基的膜层204a以及硅基的膜层204b上方。在一些实施例中,第二硬遮罩层210可包含一或多层膜层,每层都是由与硅基的膜层204a以及硅基的膜层204b的材料相似的半导体材料所形成。在一些实施例中,第二硬遮罩层210以及第一硬遮罩层208(例如,由硅锗形成的膜层)可共同形成硬遮罩。在一些实施例中,硬遮罩的第一硬遮罩层208是由sige所形成,而第二硬遮罩210是由硅所形成。

81.第二硬遮罩层210可使用光学微影技术来图案化。一般来说,光学微影技术利用光阻材料(未绘示),经过沉积、辐照(曝光)、以及显影以移除光阻材料的一部份。剩余的光阻材料保护了其下方的材料,诸如此示例中的第二硬遮罩层210,能不受后续诸如蚀刻的制程步骤所影响。举例来说,光阻材料用来图案化第二硬遮罩层210以形成图案化遮罩,其被图案化以覆盖一或多个鳍片结构的最顶表面。

82.第二硬遮罩层210随后用来图案化硅基的膜层204a、硅基的膜层204b、以及基板202的外露部分以形成多个沟槽(或多个开口),从而在相邻的沟槽之间定义出一或多个鳍片结构,如图2b所绘示。沟槽沿着y方向连续地延伸。当形成了多个鳍片结构时,此沟槽可设置于鳍片结构的任意相邻鳍片之间。在一些实施例中,鳍片结构是借由使用例如反应离子蚀刻(rie)、中性束蚀刻(neutral beam etch;nbe)、类似的蚀刻、任意其他合适的制程、或上述的组合的制程蚀刻硅基的膜层204a、硅基的膜层204b、以及基板202中的沟槽来形成。蚀刻可为非等向性蚀刻(anisotropic)。在一些实施例中,沟槽可为彼此平行的条状(当从顶部向下看时),且彼此之间紧密间隔。在一些实施例中,沟槽可为连续的并围绕鳍片结构。

83.如图2c所绘示,半导体装置200可包含在制造阶段的期间设置的多个隔离结构212(有时被称作隔离区)。如图2c所绘示,每个隔离结构212可相邻设置于一个或多个鳍片的鳍片旁(例如,于鳍片结构的相邻鳍片之间),且至少部分地内嵌至鳍片结构的各自的较低部分之中(例如,相邻于基板202的多个部分)。

84.隔离结构212是由绝缘材料所形成,且可将邻近的主动结构(例如,鳍片结构)彼此电性地隔离。隔离结构212连续地延伸于y方向中。绝缘材料可为诸如氧化硅的氧化物、氮化物、类似的绝缘材料、任意其他合适的材料、或上述的组合,且可借由高密度等离子体化学气相沉积(hdp-cvd)、可流动化学气相沉积(flowable chemical vapor deposition;fcvd)(例如,沉积以化学气相沉积为主的材料于远程(remote)等离子体系统中,并进行后固化使

phosphosilicate glass;bpsg)、未掺杂硅酸盐玻璃(undoped silicate glass;usg)、任意其他合适的材料、或类似的介电材料,且可借由任意合适的方法来沉积,诸如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、或可流动化学气相沉积(fcvd)。

91.如图2e所绘示,半导体装置200可包含一个以上的介电结构216。一或多个介电结构216可为在各种制造阶段的一阶段的期间设置于披覆结构214的侧壁上的氮化物基的介电层(nitride-based dielectric layer)。如图2e所绘示,一或多个介电结构216可包含沿着披覆结构214的侧壁延伸以及沿着隔离结构212的顶部延伸的氮化物基的介电层,而第二氧化物基(second oxide-based layer)的膜层沿着氮化物基的介电层的侧壁设置。

92.在形成披覆结构214之后,可顺应地沉积氮化物基的介电层于披覆结构214的侧壁以及于隔离结构212的顶部。氮化物基的介电层可包含sicn或任意其他合适的材料,且可借由任意合适的沉积制程来形成,诸如化学气相沉积(诸如等离子体增强化学气相沉积(hdp-cvd)、高深宽比制程(high aspect ratio process;harp)、或上述的组合)制程、原子层沉积制程、其他可接受的制程、或上述的组合。在一些实施例中,在形成一个以上的介电结构216的氮化物基的介电层之前,可顺应地形成第二氧化物基的膜层于披覆层214上方。第二氧化物基的膜层可作为披覆结构214在蚀刻氮化物基的介电层时的保护层。第二氧化物基的膜层可包含介电材料,诸如氧化硅、磷硅酸盐玻璃(psg)、硼硅酸盐玻璃(bsg)、掺杂硼的磷硅酸盐玻璃(bpsg)、未掺杂硅酸盐玻璃(usg)、任意其他合适的材料、或类似的介电材料,且可借由任意合适的方法来沉积,诸如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、或可流动化学气相沉积(fcvd)。

93.在一些面向中,一或多个介电结构216可包含在各种制造阶段的一阶段的期间设置的第三氧化物基(third oxide-based layer)的膜层。第三氧化物基的膜层可沿着氮化物基的介电层的底部与侧壁延伸,且在半导体装置200的y方向中连续地延伸。

94.在形成氮化物基的介电层之后,形成第三氧化物基的膜层于鳍片(例如,堆叠)之间的沟槽中。第三氧化物基的膜层可包含介电材料,诸如氧化硅、磷硅酸盐玻璃(psg)、硼硅酸盐玻璃(bsg)、掺杂硼的磷硅酸盐玻璃(bpsg)、未掺杂硅酸盐玻璃(usg)、任意其他合适的材料、或类似的介电材料,且可借由任意合适的方法来沉积,诸如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、或可流动化学气相沉积(fcvd)。首先形成氧化物基的膜层以与披覆结构214的顶表面共平面。第三氧化物基的膜层的各自的顶表面可具有平坦表面、凸面、凹面(诸如碟状)、任意其他合适的表面、或上述的组合。可借由适当的蚀刻或平坦化处理(诸如化学机械抛光处理(cmp))将第三氧化物基的膜层的顶表面形成平面、凸面、及/或凹面。可接着使用合适的蚀刻制程来凹蚀第三氧化物基的膜层,诸如对第三氧化物基的膜层的材料具有选择性的蚀刻制程。

95.如图2f所绘示,可回蚀刻一或多个介电结构216使得一或多个介电结构216的膜层的顶表面自披覆结构214的顶表面内凹。此外,可移除披覆结构214的上部(例如,通过平坦化处理)以形成披覆结构214的多个元件于鳍片的侧壁上。

96.如图2g所绘示,形成介电结构218(例如,高介电常数介电质(high-kdielectric))于一或多个介电结构216的膜层的上表面上、于披覆结构214的元件的上表面上、及/或于第二硬遮罩层210的上表面上。介电结构218可包含高介电常数介电材料,诸如氧化铪等其他示例。介电结构218可包含盖层。可提供盖层来避免介电结构218的成分(例如,高介电常数

介电质)在随后的退火制程期间扩散出去并污染半导体机台。可在退火制程之后移除盖层。在一些实施例中,一或多个半导体制程机台(例如,沉积机台102)使用化学气相沉积(cvd)、物理气相沉积(pvd)、及/或回流(reflow)等其他示例形成介电结构218,以沉积介电结构218的材料于一或多个介电结构216的顶表面上。

97.在一些实施例中,第一硬遮罩层208包含与披覆结构214相同的材料。举例来说,第一硬遮罩层208以及披覆结构214两者可都包含硅锗基的材料(例如,sige)。在一些实施例中,第一硬遮罩层208可包含等于或大于披覆结构214的锗浓度。举例来说,第一硬遮罩层208以及披覆结构214可具有范围为大约16%至大约30%的锗浓度。在一些实施例中,第一硬遮罩层208可具有大约25%的锗浓度,披覆结构214可具有大约21%的锗浓度。如此一来,当使用配置来蚀刻较低锗浓度的蚀刻剂时(例如,配置来蚀刻披覆结构214),可以以快于蚀刻第一硬遮罩层208的速率来蚀刻披覆结构214。

98.如图2h所绘示,一或多个半导体制程机台可平坦化半导体装置200的顶表面。在一些实施例中,平坦化机台(例如,平坦化机台106)可执行平坦化操作220来平坦化半导体装置200的顶表面以自披覆结构214及/或第二硬遮罩层210等半导体装置200的其他半导体结构的顶表面移除介电结构218的材料。在一些实施例中,第二硬遮罩层210被配置为平坦化操作的停止层以表示平坦化操作220已经完成(例如,将停止平坦化操作)。如此一来,在平坦化操作220期间,第二硬遮罩层210可保护第一硬遮罩层208以及披覆结构214(例如,不受损害)。在平坦化操作220之后,披覆结构214及/或第二硬遮罩层210的顶表面可在进行平坦化操作220之后露出。

99.如图2i所绘示,在沉积第二硬遮罩层210之后及/或在执行平坦化操作220之后,一或多个半导体制程机台可移除披覆结构214的顶部以形成披覆结构214的内凹部分222。在一些实施例中,蚀刻机台(例如,蚀刻机台104)基于执行湿式蚀刻制程蚀刻披覆结构214的顶部以移除披覆结构214的顶部(例如,披覆结构214的第一顶部)。在一些实施例中,执行湿式蚀刻制程包含使用具有高选择性的液体来移除披覆结构214的材料。举例来说,液体可包含被配置为与披覆结构214的硅锗基的材料反应的化学品(chemical)。在一些实施例中,湿式蚀刻制程可移除第二硬遮罩层210的一或多个部分。举例来说,湿式蚀刻制程可自第二硬遮罩层210的上表面移除转角及/或边缘。在一些实施例中,湿式蚀刻制程可基于第二硬遮罩层210包含被包括在披覆结构214中的一或多种材料来移除第二硬遮罩层210的一或多个部分。举例来说,湿式蚀刻制程可使用被配置来移除披覆结构214的硅锗基的材料的蚀刻剂,且此蚀刻剂可同样基于第二硬遮罩层210包含的硅基的材料移除第二硬遮罩层110的一或多个部分。在此示例中,此蚀刻剂可以以快于移除第二硬遮罩层210的材料的速率来移除披覆结构214的材料。

100.基于移除披覆结构214的顶部,披覆结构214的顶表面可能低于第二硬遮罩层210的最顶表面。举例来说,在移除披覆结构214的顶部之后,披覆结构214的顶表面与第二硬遮罩层210的最顶表面之间的距离224之范围为大约12纳米至大约18纳米。在一些实施例中,距离224的范围为第二硬遮罩层210在蚀刻披覆结构214的顶部之前的厚度的大约二分之一至大约三分之二。如此一来,披覆结构214的顶表面足够低,以露出够多的第二硬遮罩层210的侧表面(例如,二分之一至三分之二),并允许第二硬遮罩层210的有效蚀刻,同时减少、或避免留下多余的硬遮罩材料于披覆结构214与第一硬遮罩层208之间的转角中。

101.如图2j所绘示,在移除披覆结构214的顶部之后,一或多个半导体制程机台可移除第二硬遮罩层210。在一些实施例中,蚀刻机台(例如,蚀刻机台104)基于执行来移除第二硬遮罩层210的湿式蚀刻制程蚀刻第二硬遮罩层210。在一些实施例中,执行湿式蚀刻制程包含使用具有高选择性的液体来移除第二硬遮罩层210的材料。举例来说,液体可包含被配置为与第二硬遮罩层210的硅基的材料进行反应的化学品。在蚀刻第二硬遮罩层210之后,可留下第二硬遮罩层210的一或多个部分(例如,于硅基的膜层204a的顶层以及披覆结构214的元件两者所交会的转角中)。

102.在一些实施例中,湿式蚀刻制程可移除披覆结构214及/或第一硬遮罩层208的一或多个部分。举例来说,湿式蚀刻制程可自披覆结构214的上表面及/或第一硬遮罩层208的中央部移除转角及/或边缘。在一些实施例中,湿式蚀刻制程可基于披覆结构214及/或第一硬遮罩层208的一或多个部分包含被包括在第二硬遮罩层210中的一或多种材料来移除披覆结构214及/或第一硬遮罩层208的一或多个部分。举例来说,湿式蚀刻制程可使用被配置来移除第二硬遮罩层210的硅基的材料的蚀刻剂,且此蚀刻剂可同样基于披覆结构214及/或第一硬遮罩层208包含的硅锗基的材料移除披覆结构214及/或第一硬遮罩层208的一或多个部分。在此示例中,此蚀刻剂可以以快于移除披覆结构214及/或第一硬遮罩层208的材料的速率来移除第二硬遮罩层210的材料。在一些实施例中,在移除第二硬遮罩层210之后,第一硬遮罩层208的顶表面可实质上不含第二硬遮罩层210的材料(例如,基于先移除披覆结构214的顶部)。

103.如图2k所绘示,在移除第二硬遮罩层210之后,一或多个制程机台可移除披覆结构214以及第一硬遮罩层208的额外顶部(例如,第二顶部)。在一些实施例中,蚀刻机台(例如蚀刻机台104)基于执行被配置来移除披覆结构214以及第一硬遮罩层208的材料的一或多道湿式蚀刻制程蚀刻披覆结构214(例如,披覆结构214延伸至硅基的膜层204a的顶层的顶表面上方的部分)以及第一硬遮罩层208的额外顶部。在一些实施例中,执行湿式蚀刻制程包含使用具有高选择性的液体来移除披覆结构214以及第一硬遮罩层208的材料(例如当披覆结构214包含与第一硬遮罩层208实质上相同的材料,诸如具有相同或不同锗浓度的硅锗基的材料)。举例来说,移除披覆结构214的额外部分以及移除第一硬遮罩层208包含配置来选择性蚀刻包含于披覆结构214以及第一硬遮罩层208中的相同材料的单蚀刻操作。在一些实施例中,单蚀刻操作可同样移除第二硬遮罩层210在蚀刻第二硬遮罩层210之后所剩余的一或多个部分。

104.在一些实施例中,在移除披覆结构214的额外部分以及移除第一硬遮罩层208之后,一或多个半导体制程机台(例如,蚀刻机台104)对披覆结构214以及硅基的膜层204a的顶层执行清洗操作。清洗操作可移除第一硬遮罩层208及/或披覆结构214位于硅基的膜层204a的顶层的顶表面上方的残留(residual)材料。

105.在一些实施例中,基于移除披覆结构的额外顶部(例如,在借由移除硬遮罩的操作与结合图2e描述的移除顶部的分开操作中)、移除第一硬遮罩层208、及/或执行清洗操作,披覆结构214的顶表面可位于大约等于或低于硅基的膜层204a的顶层的顶表面的高度。额外地或者替代地,硅基的膜层204a的顶层可形成为纳米结构204的顶表面(例如,可形成与硅基的膜层204a相同的材料)且可延伸至披覆结构214的多个元件之间(例如,连续地延伸至披覆结构214的多个元件之间)。硅基的膜层204a的顶层及/或披覆结构214可进一步提供

纳米结构204的实质上平坦的顶表面,以改善半导体装置200的后续膜层的沉积。额外地或者替代地,纳米结构204的顶表面可实质上不含第一硬遮罩层208的材料以及实质上不含第二硬遮罩层210的材料。如此一来,半导体装置200可具有改善的效率以及可具有降低的故障可能性,其可节省原本可能用来制造替代半导体装置的资源。

106.在移除披覆结构214以及第一硬遮罩层208的额外顶部之后以及在移除第二硬遮罩层210之后,一或多个半导体制程机台可执行一或多个额外的操作以形成全绕式栅极装置(gaa)于半导体装置200之内。举例来说,一或多个半导体制程机台可执行金属栅极沉积制程。金属栅极沉积制程可包含形成多晶栅极于纳米结构204上、形成间隔物及/或内间隔物于纳米结构的多个膜层之间、形成源极/漏极、以及蚀刻多晶栅极与硅基的膜层204a或硅基的膜层204b的一者(例如,堆叠的牺牲层)以提供围绕硅基的膜层204a或硅基的膜层204b的剩余一者的体积。沉积机台(例如,沉积机台102)可沉积一或多层介电层(例如,界面层及/或高介电常数介电层)于硅基的膜层204a或硅基的膜层204b的剩余一者上,以提供电性绝缘于硅基的膜层204a或硅基的膜层204b的剩余一者周围。沉积机台可沉积一或多层栅极材料层,诸如功函数金属,位于硅基的膜层204a或硅基的膜层204b的剩余一者周围的一或多层介电层上;以及填充金属,以填充围绕硅基的膜层204a或硅基的膜层204b的剩余一者的体积。如此一来,硅基的膜层204a或硅基的膜层204b的剩余一者可作为穿过栅极材料的通道,其可接着使用作晶体管(例如,纳米结构装置及/或纳米结构晶体管)来存储信息。

107.在形成全绕式栅极装置(gaa)之后,沉积机台可沉积一或多种的材料于介电结构218的多个元件之间。举例来说,一或多个的半导体制程机台可移除披覆结构214并形成源极/漏极区。可形成一或多个的源极/漏极区的接触件以及栅极区的接触件。可形成一或多个的接触件以在后段制程(back-end-of-line;beol)区中使用金属导线连接半导体装置200。

108.如前所述,提供图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h、图2i、图2j以及图2k作为示例。其他示例可能与图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h、图2i、图2j以及图2k所描述的示例不同。

109.图3为装置300的例示性元件的示意图,其可对应至沉积机台102、蚀刻机台104、平坦化机台106、及/或晶圆/晶粒转移机台108。在一些实施例中,沉积机台102、蚀刻机台104、平坦化机台106、及/或晶圆/晶粒转移机台108可包含一或多个装置300及/或装置300的一或多个元件。如图3所绘示,装置300可包含总线310(bus)、处理器320(processor)、存储器330、存储元件340、输入元件350、输出元件360、以及通信元件370。

110.总线310包含能使装置300之间的元件进行有线(wired)及/或无线(wireless)通信的元件。处理器320包含中央处理器(central processing unit;cpu)、图形处理器(graphics processing unit;gpu)、微处理器(microprocessor)、控制器(controller)、微控制器(microcontroller)、数字信号处理器(digital signal processor;dsp)、场可程序化栅极阵列(field-programmable gate array;fpga)、特定应用集成电路(application-specific integrated circuit;asic)、及/或其他类型的处理元件。处理器320是以硬件(hardware)、固件(firmware)、或硬件与固件的组合来实施。在一些实施例中,处理器320包含能够被程序化以执行功能的一或多个的处理器。存储器330包含随机存取存储器(random access memory;ram)、唯读存储器(read only memory;rom)、及/或其他类型的存储器(例

如,快闪存储器(flash memory)、磁存储器(magnetic memory)、及/或光存储器(optical memory))。

111.存储元件340存储与装置300的操作相关的信息或软件。举例来说,存储元件340可包含硬盘驱动器(hard disk drive;hdd)、磁盘驱动器(magnetic disk drive)、光盘驱动器(optical disk drive)、固态硬盘驱动器(solid state disk drive;ssd)、光盘(compact disc;cd)、数字多功能光盘(digital versatile disc;dvd)、及/或其他类型的非暂态电脑可读取媒体(non-transitory computer readable medium)。输入元件350使装置300能够接收输入,诸如使用者输入及/或感测输入。举例来说,输入元件350可包含触控屏幕、键盘、触控板(keypad)、鼠标、按钮、麦克风、切换器(switch)、感测器、全球定位系统(global positioning system;gps)元件、加速计(accelerometer)、陀螺仪(gyroscope)、及/或执行器(actuator)。输出元件360使装置300能够提供输出,诸如通过显示器、扬声器、及/或一或多个发光二极管(light-emitting diodes;led)。通信元件370使装置300能够与其他装置进行通信,诸如通过有线连接及/或无线连接。举例来说,通信元件370可包含接收器、发射器(transmitter)、收发器(transceiver)、调制解调器(modem)、网络接口卡(network interface card)、及/或天线(antenna)。

112.本公开描述的装置300可执行一或多个处理功能。举例来说,非暂态电脑可读取媒体(例如,存储器330及/或存储元件340)可存储一组借由处理器320所执行的指令(instructions)(例如,一或多个指令、代码(code)、软件代码、及/或程序代码)。处理器320可执行此组指令以执行一或多个本公开描述的处理功能。在一些实施例中,由一或多个处理器320所执行的此组指令,造成了一或多个处理器320及/或装置300能执行一或多个本公开描述的处理功能。在一些实施例中,硬接线电路可用来代替指令或者与指令结合以执行一或多个本公开描述的处理功能。因此,本公开描述的实施例并不限于硬件电路以及软件的任何特定组合。图3中所绘示的元件的数字以及配置是提供作为示例。装置300可包含额外的元件、更少的元件、不同的元件、或与图3所绘示的元件配置不同的元件配置。额外地或者替代地,装置300的一组元件(例如,一或多个元件)可执行由装置300的另一组元件所执行的一或多个本公开描述的功能。

113.图4为与纳米结构以及其制造方法相关的例示性制程400的示意图。在一些实施例中,可借由一或多个半导体制程机台(例如,沉积机台102、蚀刻机台104、平坦化机台106、及/或晶圆/晶粒转移机台108)执行图4的一或多个制程区块。额外地或者替代地,可借由装置300的一或多个元件执行图4的一或多个制程区块,上述一或多个元件为诸如处理器320、存储器330、存储元件340、输入元件350、输出元件360、及/或通信元件370。

114.如图4所绘示,制程400可包含形成纳米结构,其具有第一材料的第一组膜层以及具有与所述第一组膜层交替的第二材料的第二组膜层(制程区块410)。举例来说,一或多个半导体制程机台可形成具有第一材料的第一组膜层204a以及具有与所述第一组膜层204a交替的第二材料的第二组膜层204b的纳米结构204,如上方所描述。

115.如图4所进一步绘示,制程400可包含沉积硬遮罩于所述第一组膜层的顶层上,硬遮罩包括位于所述第一组膜层的顶层上的第一硬遮罩层以及位于第一硬遮罩层上的第二硬遮罩层(制程区块420)。举例来说,一或多个半导体制程机台可沉积硬遮罩于所述第一组膜层204a的顶层上,硬遮罩包括位于所述第一组膜层204a的顶层上的第一硬遮罩层208以

及位于第一硬遮罩层208上的第二硬遮罩层210,如上方所描述。

116.如图4所进一步绘示,制程400可包含沉积披覆结构的多个元件于纳米结构以及硬遮罩的多个侧壁上(制程区块430)。举例来说,一或多个半导体制程机台可沉积披覆结构214的多个元件于纳米结构204以及硬遮罩的多个侧壁上,如上方所描述。

117.如图4所进一步绘示,制程400可包含移除披覆结构的顶部(制程区块440)。举例来说,一或多个半导体制程机台可移除披覆结构214的顶部,如上方所描述。

118.如图4所进一步绘示,在移除披覆结构的顶部之后,制程400可包含移除第二硬遮罩层(制程区块450)。举例来说,在移除披覆结构214的顶部之后,一或多个半导体制程机台可移除第二硬遮罩层210,如上方所描述。

119.制程400可包含额外的实施例,诸如任何单一实施例或与下方描述的实施例的任意组合及/或与本公开的其他地方描述的一或多个其他制程相关联。

120.在第一实施例中,在沉积硬遮罩之后以及在移除披覆结构的顶部之前,制程400包含沉积介电结构于披覆结构的多个元件的顶表面上以及于硬遮罩的顶表面上,以及执行平坦化操作以自披覆结构的多个元件的顶表面以及自硬遮罩的顶表面移除介电结构。

121.在第二实施例中,单独地或者与第一实施例结合,平坦化操作被配置为到达第一硬遮罩层而中止。

122.根据该半导体装置的形成方法,其中在移除披覆结构的顶部之后,披覆结构的顶表面与第二硬遮罩层的最顶表面之间的距离为大约12纳米至大约16纳米。

123.根据该半导体装置的形成方法,其中在移除披覆结构的顶部之后,披覆结构的顶表面与第二硬遮罩层的最顶表面之间的距离为第二硬遮罩层在蚀刻披覆结构的顶部之前的厚度的大约二分之一至大约三分之二。

124.在第三实施例中,单独地或者与一或多个第一实施例及第二实施例结合,第一硬遮罩层的厚度为大约2纳米至大约8纳米。

125.在第四实施例中,单独地或者与一或多个第一实施例、第二实施例、及第三实施例结合,披覆结构包括硅锗基的材料。

126.在第五实施例中,单独地或者与一或多个第一实施例、第二实施例、第三实施例、及第四实施例结合,第一组膜层包括纳米结构的多个通道。

127.在第六实施例中,单独地或者与一或多个第一实施例、第二实施例、第三实施例、第四实施例、及第五实施例结合,在移除第二硬遮罩层之后,制程400包含移除披覆结构延伸至所述第一组膜层的顶层的顶表面上方的额外部分,以及移除第一硬遮罩层。

128.在第七实施例中,单独地或者与一或多个第一实施例、第二实施例、第三实施例、第四实施例、第五实施例、及第六实施例结合,披覆结构与第一硬遮罩层是由相同的材料所形成,以及其中移除披覆结构的额外部分以及移除第一硬遮罩层包括单蚀刻操作,单蚀刻操作用以选择性蚀刻所述相同的材料。

129.在第八实施例中,单独地或者与一或多个第一实施例、第二实施例、第三实施例、第四实施例、第五实施例、第六实施例、及第七实施例结合,在移除披覆结构的额外部分以及移除蚀刻停止层之后,制程400包含对披覆结构以及所述硅基的结构执行清洗操作。

130.在第九实施例中,单独地或者与一或多个第一实施例、第二实施例、第三实施例、第四实施例、第五实施例、第六实施例、第七实施例、及第八实施例结合,第一硬遮罩层被配

置作为与移除第二硬遮罩层的蚀刻操作相关的蚀刻停止层。

131.尽管图4绘示出制程400的例示性制程区块,在一些实施例中,制程400可包含额外的制程区块、更少的制程区块、不同的制程区块、或与图4所绘示的制程区块具有不同配置的制程区块。额外地或者替代地,可平行执行制程400的两个或以上的制程区块。

132.图5为与纳米结构以及其制造方法相关的例示性制程500的示意图。在一些实施例中,可借由一或多个半导体制程机台(例如,沉积机台102、蚀刻机台104、平坦化机台106、及/或晶圆/晶粒转移机台108)执行图5的一或多个制程区块。额外地或者替代地,可借由装置300的一或多个元件执行图5的一或多个制程区块,上述一或多个元件为诸如处理器320、存储器330、存储元件340、输入元件350、输出元件360、及/或通信元件370。

133.如图5所绘示,制程500包含形成纳米结构,其在第一高度具有顶表面(制程区块510)。举例来说,一或多个半导体制程机台可形成纳米结构204,其在第一高度具有顶表面,如上方所描述。

134.如图5所进一步绘示,制程500可包含形成披覆结构,其在第二高度具有顶表面,纳米结构设置于披覆结构的多个元件之间(制程区块520)。举例来说,一或多个半导体制程机台可形成披覆结构214,其在第二高度具有顶表面,纳米结构204设置于披覆结构214的多个元件之间,如上方所描述。在一些实施例中,形成在第二高度具有顶表面的披覆结构214包括形成硬遮罩208及/或210于纳米结构上,形成披覆结构214于纳米结构204的多个侧壁上以及于硬遮罩208及/或210的多个侧壁上,移除披覆结构214的第一顶部,在移除披覆结构214的第一顶部之后,移除硬遮罩208及/或210,以及在移除硬遮罩208及/或210之后,移除披覆结构214的第二顶部。在一些实施例中,纳米结构204的顶表面包括硅基的结构204a,所述硅基的结构204a具有实质上平坦的顶表面,所述实质上平坦的顶表面自所述披覆结构214的多个元件的第一元件延伸至所述披覆结构214的多个元件的第二元件。

135.制程500可包含额外的实施例,诸如任何单一实施例或与下方描述的实施例的任意组合及/或与本公开的其他地方描述的一或多个其他制程相关联。

136.在第一实施例中,纳米结构的顶表面不含第一硬遮罩层的材料以及不含第二硬遮罩层的材料。

137.在第二实施例中,单独地或者与第一实施例结合,披覆结构包括硅锗基的材料。

138.在第三实施例中,单独地或者与一或多个第一实施例及第二实施例结合,硅锗基的材料具有大约18%至大约30%的锗浓度。

139.在第四实施例中,单独地或者与一或多个第一实施例、第二实施例、及第三实施例结合,半导体装置包含介电结构,介电结构设置于披覆结构的顶表面上以及设置于于纳米结构的顶表面上。

140.在第五实施例中,单独地或者与一或多个第一实施例、第二实施例、第三实施例、及第四实施例结合,第二高度大约等于或者小于该第一高度。

141.尽管图5绘示出制程500的例示性制程区块,在一些实施例中,制程500可包含额外的制程区块、更少的制程区块、不同的制程区块、或与图5所绘示的制程区块具有不同配置的制程区块。额外地或者替代地,可平行执行制程500的两个或以上的制程区块。

142.图6为与纳米结构以及其制造方法相关的例示性制程600的示意图。在一些实施例中,可借由一或多个半导体制程机台(例如,沉积机台102、蚀刻机台104、平坦化机台106、

及/或晶圆/晶粒转移机台108)执行图6的一或多个制程区块。额外地或者替代地,可借由装置300的一或多个元件执行图5的一或多个制程区块,上述一或多个元件为诸如处理器320、存储器330、存储元件340、输入元件350、输出元件360、及/或通信元件370。

143.如图6所绘示,制程600包含沉积第一硬遮罩层于纳米结构上(制程区块610)。举例来说,一或多个的半导体制程机台可沉积第一硬遮罩层208于纳米结构204上,如上方所描述。

144.如图6所进一步绘示,制程600可包含沉积第二硬遮罩层于第一硬遮罩层上(制程区块620)。举例来说,一或多个半导体制程机台可沉积第二硬遮罩层210于第一硬遮罩层208上,如上方所描述。

145.如图6所进一步绘示,制程600可包含沉积披覆结构的多个元件于纳米结构、于第一硬遮罩层、以及于第二硬遮罩层的多个侧壁上(制程区块630)。举例来说,一或多个的半导体制程机台可沉积披覆结构214的多个元件于纳米结构204、于第一硬遮罩层208、以及于第二硬遮罩层210的多个侧壁上,如上方所描述。

146.如图6所进一步绘示,制程600可包含沉积材料于第二硬遮罩层的顶表面上以及于披覆结构的顶表面上(制程区块640)。举例来说,一或多个半导体制程机台可沉积材料于第二硬遮罩层210的顶表面上以及于披覆结构214的顶表面上,如上方所描述。

147.如图6所进一步绘示,制程600可包含对半导体装置的顶表面执行平坦化操作以自披覆结构的顶表面以及自第二硬遮罩层的顶表面移除材料(制程区块650)。举例来说,一或多个半导体制程机台可对半导体装置200的顶表面执行平坦化操作220以自披覆结构214的顶表面以及自第二硬遮罩层210的顶表面移除材料,如上方所描述。

148.如图6所进一步绘示,在执行平坦化操作之后,制程600可包含移除披覆结构的第一顶部(制程区块660)。举例来说,在执行平坦化操作之后,一或多个半导体制程机台可移除披覆结构214的第一顶部,如上方所描述。

149.如图6所进一步绘示,在移除披覆结构的第一顶部之后,制程600可包含移除第二硬遮罩层(制程区块670)。举例来说,在移除披覆结构214的第一顶部之后,一或多个半导体制程机台可移除第二硬遮罩层210,如上方所描述。

150.如图6所进一步绘示,在移除第二硬遮罩层之后,制程600可包含移除披覆结构的第二顶部以及移除第一硬遮罩层(制程区块680)。举例来说,在移除第二硬遮罩层210之后,一或多个半导体制程机台可移除披覆结构214的第二顶部以及移除第一硬遮罩层208,如上方所描述。

151.制程600可包含额外的实施例,诸如任何单一实施例或与下方描述的实施例的任意组合及/或与本公开的其他地方描述的一或多个其他制程相关联。

152.在第一实施例中,移除披覆结构的第一顶部包括执行湿式蚀刻制程以移除披覆结构的第一顶部。

153.在第二实施例中,单独地或者与第一实施例结合,执行湿式蚀刻制程包括使用具有高选择性的液体来移除披覆结构的材料。

154.尽管图6绘示出制程600的例示性制程区块,在一些实施例中,制程600可包含额外的制程区块、更少的制程区块、不同的制程区块、或与图6所绘示的制程区块具有不同配置的制程区块。额外地或者替代地,可平行执行制程600的两个或以上的制程区块。

155.基于在蚀刻第二硬遮罩层210之前蚀刻披覆结构214的第一顶部,可减少来自第二硬遮罩层210的残留物残存量、可减少移除第二硬遮罩层210的过蚀刻、及/或在移除第二硬遮罩层210之后可维持第一硬遮罩层208的完整。基于在移除第二硬遮罩层210之后维持了第一硬遮罩层208的完整,蚀刻机台可移除披覆结构214的第二顶部以及移除第一硬遮罩层208,但不对形成纳米结构204的顶表面的硅基的膜层204a造成损害。如此一来,硅基的膜层204a的顶表面可实质上地平坦及/或可自披覆结构214的第一元件延伸至披覆结构214的第二元件,及/或可提供阻障于纳米结构204的较低膜层与设置于硅基的膜层204a的顶层上的材料之间等等。

156.如同在上方更详细的描述,本公开描述的一些实施例提供了一种半导体装置的形成方法。此半导体装置的形成方法包含形成纳米结构,所述纳米结构具有第一材料的第一组膜层以及与所述第一组膜层交替的具有第二材料的第二组膜层。此半导体装置的形成方法同样包含沉积硬遮罩于所述第一组膜层的顶层上,所述硬遮罩包括位于所述第一组膜层的顶层上的第一硬遮罩层以及位于所述第一硬遮罩层上的第二硬遮罩层。此半导体装置的形成方法更包含沉积披覆结构的多个元件于所述纳米结构以及所述硬遮罩的多个侧壁上。此半导体装置的形成方法额外地包含移除所述披覆结构的顶部。在移除所述披覆结构的顶部之后,此半导体装置的形成方法更包含移除所述第二硬遮罩层。

157.在沉积所述硬遮罩之后以及在移除所述披覆结构的顶部之前,此半导体装置的形成方法更包含沉积介电结构于所述披覆结构的多个元件的顶表面上以及于所述硬遮罩的顶表面上,以及执行平坦化操作以自所述披覆结构的多个元件的顶表面以及自所述硬遮罩的顶表面移除所述介电结构。在此半导体装置的形成方法中,所述平坦化操作于到达所述第一硬遮罩层而中止。在此半导体装置的形成方法中,在移除所述披覆结构的顶部之后,所述披覆结构的顶表面与所述第二硬遮罩层的最顶表面之间的距离为大约12纳米至大约16纳米。在此半导体装置的形成方法中,在移除所述披覆结构的顶部之后,所述披覆结构的顶表面与所述第二硬遮罩层的最顶表面之间的距离为所述第二硬遮罩层在蚀刻所述披覆结构的顶部之前的厚度的大约二分之一至大约三分之二。在此半导体装置的形成方法中,所述第一硬遮罩层的厚度为大约2纳米至大约8纳米。在此半导体装置的形成方法中,所述披覆结构包括硅锗基的材料。在此半导体装置的形成方法中,所述第一组膜层包括所述纳米结构的多个通道。在移除所述第二硬遮罩层之后,此半导体装置的形成方法更包含移除所述披覆结构延伸至所述第一组膜层的顶层的顶表面上方的额外部分,以及移除所述第一硬遮罩层。在此半导体装置的形成方法中,所述披覆结构与所述第一硬遮罩层是由相同的材料所形成。在此半导体装置的形成方法中,移除所述披覆结构的额外部分以及移除所述第一硬遮罩层包括单蚀刻操作,所述单蚀刻操作用以选择性蚀刻所述相同的材料。在移除所述披覆结构的额外部分以及移除所述蚀刻停止层之后,此半导体装置的形成方法更包含对所述披覆结构以及所述硅基的结构执行清洗操作。在此半导体装置的形成方法中,所述第一硬遮罩层被配置作为与移除所述第二硬遮罩层的蚀刻操作相关的蚀刻停止层。

158.如同在上方更详细的描述,本公开描述的一些实施例提供了一种半导体装置的形成方法。此半导体装置的形成方法包含形成纳米结构,所述纳米结构在第一高度具有顶表面。此半导体装置的形成方法同样包含形成披覆结构,所述披覆结构在第二高度具有顶表面,所述纳米结构设置于所述披覆结构的多个元件之间。在此半导体装置的形成方法中,形

成在第二高度具有顶表面的所述披覆结构包括形成硬遮罩于所述纳米结构上,形成所述披覆结构于所述纳米结构的多个侧壁上以及于所述硬遮罩的多个侧壁上,移除所述披覆结构的第一顶部,在移除所述披覆结构的第一顶部之后,移除所述硬遮罩,以及在移除所述硬遮罩之后,移除所述披覆结构的第二顶部。在此半导体装置的形成方法中,所述纳米结构的顶表面包括硅基的结构,所述硅基的结构具有实质上平坦的顶表面,所述实质上平坦的顶表面自所述披覆结构的多个元件的第一元件延伸至所述披覆结构的多个元件的第二元件。

159.在此半导体装置的形成方法中,所述纳米结构的顶表面不含第一硬遮罩层的材料以及不含第二硬遮罩层的材料。在此半导体装置的形成方法中,所述披覆结构包括硅锗基的材料。在此半导体装置的形成方法中,所述硅锗基的材料具有大约18%至大约30%的锗浓度。在此半导体装置的形成方法中,所述第二高度大约等于或者小于所述第一高度。

160.如同在上方更详细的描述,本公开描述的一些实施例提供了一种半导体装置的形成方法。此半导体装置的形成方法包含沉积第一硬遮罩层于纳米结构上。此半导体装置的形成方法同样包含沉积第二硬遮罩层于所述第一硬遮罩层上。此半导体装置的形成方法更包含沉积披覆结构的多个元件于所述纳米结构、于所述第一硬遮罩层、以及于所述第二硬遮罩层的多个侧壁上。此半导体装置的形成方法额外地包含沉积材料于所述第二硬遮罩层的顶表面上以及于所述披覆结构的顶表面上。此半导体装置的形成方法更包含对所述半导体装置的顶表面执行平坦化操作以自所述披覆结构的顶表面以及自所述第二硬遮罩层的顶表面移除材料。在执行所述平坦化操作之后,此半导体装置的形成方法同样包含移除所述披覆结构的第一顶部。在移除所述披覆结构的第一顶部之后,此半导体装置的形成方法额外地包含移除所述第二硬遮罩层。在移除所述第二硬遮罩层之后,此半导体装置的形成方法更包含移除所述披覆结构的第二顶部以及移除所述第一硬遮罩层。

161.在此半导体装置的形成方法中,移除所述披覆结构的第一顶部包含了执行湿式蚀刻制程以移除所述披覆结构的第一顶部。在此半导体装置的形成方法中,执行所述湿式蚀刻制程更包含了使用具有高选择性的液体来移除所述披覆结构的材料。

162.以上概述数个实施例的特征,以使本发明所属技术领域中具有通常知识者可以更加理解本发明实施例的观点。本发明所属技术领域中具有通常知识者应理解,可轻易地以本发明实施例为基础,设计或修改其他制程和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本发明所属技术领域中具有通常知识者也应理解,此类等效的结构并无悖离本发明的精神与范围,且可在不违背本发明的精神和范围下,做各式各样的改变、取代和替换。因此,本发明的保护范围当视后附的权利要求书所界定为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1