高电子迁移率晶体管的结构和制备方法与流程

本申请实施例涉及半导体器件,尤其涉及一种高电子迁移率晶体管的结构和制备方法。

背景技术:

1、随着电子设备向着低功耗、高运行速率的方向发展,对电子设备的基石—晶体管的要求越来越高。其中,高电子迁移率晶体管(hemt,high electron mobilitytransistor) 成为晶体管的研究方向。在hemt中,栅极击穿电压为重要参数。传统hemt中,栅极击穿电压较低,例如为10v。在栅极电压信号过冲(overshoot)时,过冲的栅极电压超过10v,导致栅极击穿,限制了器件的应用场景。

2、为了提高栅极击穿电压,业界提出采用增大hemt的耗尽层(也可以称为pn结或者空间电荷区)的方案。例如,增大hemt中,p型半导体层和n型半导体层的宽度;再例如,在hemt中,纵向依次堆叠p型半导体层和n型半导体层;再例如,在hemt 中,横向依次设置p型半导体层、n型半导体层和p型半导体层。在这些方案中,均存在hemt的耗尽区域不能充分耗尽的问题,也即是说,p型半导体层中还存在一些自由空穴无法扩散至n型半导体层中,同样,n型半导体层中还存在一些自由电子无法扩散至p型半导体层中,从而制约了栅极击穿电压的提升;另外,如果p型半导体层中还存在一些自由空穴,则p型半导体中给空穴的俘获和发射提供空间,导致hemt在各种电压状态下的阈值电压不稳定等,从而降低了器件的可靠性。由此,如何提高hemt栅极击穿电压以及hemt的可靠性,成为需要解决的问题。

技术实现思路

1、通过采用本申请所示的高电子迁移率晶体管的结构和制备方法,可以提高hemt栅极击穿电压以及hemt的可靠性。

2、为达到上述目的,本申请采用如下技术方案:

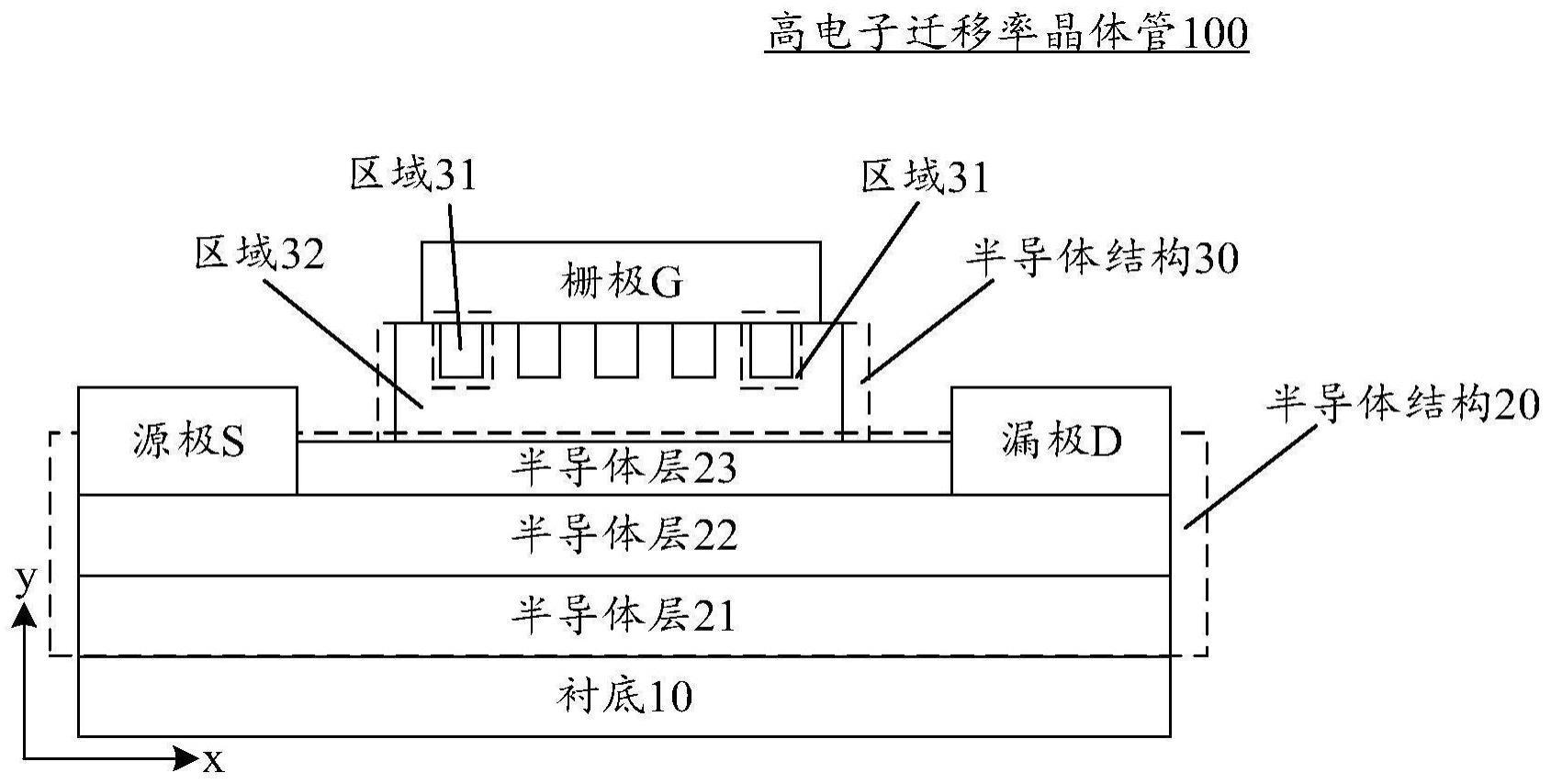

3、第一方面,本申请实施例提供一种高电子迁移率晶体管的结构,该高电子迁移率晶体管包括:衬底;沉积于所述衬底之上的第一半导体结构;沉积于所述第一半导体结构之上的第二半导体结构;设置于所述第二半导体结构之上的栅极;其中,所述第二半导体结构中、靠近所述栅极的一侧,间隔设置有多个第一区域,所述多个第一区域中掺杂有第一元素,所述多个第一区域中的每一个区域,由所述第二半导体结构的表面延伸至所述第二半导体结构的内部,所述第二半导体结构中、除所述多个第一区域之外的第二区域,掺杂有第二元素。

4、第一半导体结构例如为图2所示的半导体结构20,第二半导体结构例如为图2所示的半导体结构30。

5、本申请实施例提供的hemt,通过在第二半导体结构中设置多个第一区域,可以增大第二半导体结构中、第一区域与第二区域之间的接触面积,从而使得第一区域中更多的自由空穴扩散至第二区域中,同样,第二区域中更多自由电子扩散至第一区域,提高 hemt在各种电压状态下阈值电压的稳定性,从而提高hemt的可靠性;另外,由于第一区域中更多的空穴扩散至第二区域中、第二区域中更多的自由电子扩散至第一区域中,也即提高了耗尽层的宽度,从而可以提高hemt的栅极击穿电压。

6、基于第一方面,在一种可能的实现方式中,所述第二半导体结构和所述栅极之间还设置有第一半导体层,所述第一半导体层的材料与所述多个第一区域的材料相同。

7、基于第一方面,在一种可能的实现方式中,所述第一半导体结构包括多层半导体层,所述多层半导体层中、与所述第二半导体结构相接触的第二半导体层的两侧,还分别设置有源极和漏极。

8、基于第一方面,在一种可能的实现方式中,其特征在于,所述第一区域由氮化镓晶体中掺杂硅元素形成;所述第二区域由氮化镓晶体中掺杂镁元素形成。

9、基于第一方面,在一种可能的实现方式中,所述第二半导体层的材料为铝镓氮;所述衬底的材料为硅、蓝宝石、碳化硅、氮化镓或者金刚石。

10、第二方面,本申请实施例提供一种电子器件,该电子器件包括如第一方面所述的高电子迁移率晶体管。

11、具体的,电子器件可以为未经封装的裸芯片。另外,电子器件还可以是高电子迁移率晶体管裸芯片被封装于封装壳后的器件。该封装壳可以包括但不限于塑封管壳、金属管壳(例如金壳、镍壳)等,在封装壳的外表面引出高电子迁移率晶体管的源极、漏极和栅极。

12、第三方面,本申请实施例提供一种用于制备高电子迁移率晶体管的方法,该方法包括:提供一衬底;在所述衬底上形成第一半导体结构;在所述第一半导体结构之上形成第二半导体结构;在所述第二半导体结构之上形成栅极;其中,所述第二半导体结构中、靠近所述栅极的一侧,间隔设置有多个第一区域,所述多个第一区域中掺杂有第一元素,所述多个第一区域中的每一个区域,由所述第二半导体结构的表面延伸至所述第二半导体结构的内部,所述第二半导体结构中、除所述多个第一区域之外的第二区域,掺杂有第二元素。

13、在一种可能的实现方式中,所述在所述第二半导体结构之上形成栅极之前,所述方法还包括:在所述第二半导体结构之上形成第一半导体层,所述第一半导体层的材料与所述第一区域的材料相同。

14、在一种可能的实现方式中,所述第一半导体结构包括多层半导体层;所述制备方法还包括:刻蚀所述多层半导体层中、与所述第二半导体结构相接触的第二半导体层的两侧,以暴露出所述多层半导体层中的第三半导体层;在所述第二半导体层两侧、所暴露出的所述第三半导体层之上,分别形成源极和漏极。

15、在一种可能的实现方式中,所述在所述第一半导体结构之上形成第二半导体结构,包括:在所述第一半导体结构之上沉积第一半导体材料,所述第一半导体材料是由氮化镓中掺杂镁元素形成的;在所述第一半导体材料之上形成图案化的掩膜层;对所述第一半导体材料中、未被所述掩膜层覆盖的部分,进行离子注入,以在所述第一半导体材料中形成所述多个第一区域;去除所述掩膜层;对所述第一半导体材料中未形成所述第一区域、且靠近侧边的部分进行刻蚀,以形成所述第二半导体结构。

16、在一种可能的实现方式中,所述在所述第一半导体结构之上形成第二半导体结构,包括:在所述第一半导体结构之上依次沉积第一半导体材料和第二半导体材料;在所述第二半导体材料之上形成图案化的掩膜层;刻蚀所述第二半导体材料中未被所述掩膜层覆盖的部分,以在所述第一半导体材料之上形成所述多个第一区域;在所述第一半导体材料之上、所述多个半导体柱周围继续生长所述第一半导体材料,以形成所述第二半导体结构。

17、在一种可能的实现方式中,所述在所述第一半导体结构之上形成第二半导体结构,包括:在所述第一半导体结构之上沉积第一半导体材料;在所述第一半导体材料之上形成图案化的掩膜层;刻蚀所述第一半导体材料中未被所述掩膜层覆盖的部分,以形成多个凹槽;在所述多个凹槽中的每一个凹槽中生长第二半导体材料,以形成所述多个第一区域;刻蚀所述第一半导体材料中、未嵌入所述第二半导体层的部分,以形成所述第二半导体结构。

技术特征:

1.一种高电子迁移率晶体管的结构,其特征在于,包括:

2.根据权利要求1所述的高电子迁移率晶体管的结构,其特征在于,所述第二半导体结构和所述栅极之间还设置有第一半导体层,所述第一半导体层的材料与所述多个第一区域的材料相同。

3.根据权利要求1或2所述的高电子迁移率晶体管的结构,其特征在于,所述第一半导体结构包括多层半导体层,所述多层半导体层中、与所述第二半导体结构相接触的第二半导体层的两侧,还分别设置有源极和漏极。

4.根据权利要求1-3任一项所述的高电子迁移率晶体管的结构,其特征在于,

5.根据权利要求3所述的高电子迁移率晶体管的结构,其特征在于,

6.一种高电子迁移率晶体管的制备方法,其特征在于,包括:

7.根据权利要求6所述的制备方法,其特征在于,所述在所述第二半导体结构之上形成栅极之前,所述方法还包括:

8.根据权利要求6所述的制备方法,其特征在于,所述第一半导体结构包括多层半导体层;所述制备方法还包括:

9.根据权利要求6-8任一项所述的制备方法,其特征在于,所述在所述第一半导体结构之上形成第二半导体结构,包括:

10.根据权利要求6-8任一项所述的制备方法,其特征在于,所述在所述第一半导体结构之上形成第二半导体结构,包括:

11.根据权利要求6-8任一项所述的制备方法,其特征在于,所述在所述第一半导体结构之上形成第二半导体结构,包括:

技术总结

本申请实施例提供了一种高电子迁移率晶体管的结构和制备方法,高电子迁移率晶体管的结构包括:衬底;沉积于衬底之上的第一半导体结构;沉积于第一半导体结构之上的第二半导体结构;设置于第二半导体结构之上的栅极;其中,第二半导体结构中、靠近栅极的一侧,间隔设置有多个第一区域,多个第一区域中掺杂有第一元素,多个第一区域中的每一个区域,由第二半导体结构的表面延伸至第二半导体结构的内部,第二半导体结构中、除多个第一区域之外的区域,掺杂有第二元素,本申请提供的高电子迁移率晶体管,可以提高高电子迁移率晶体管的性能。

技术研发人员:程亮,林威,全汝岱,杨松

受保护的技术使用者:华为数字能源技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!