VCSEL芯片及其制备方法与流程

本技术涉及半导体激光器领域,更为具体地涉及vcsel芯片及其制备方法。

背景技术:

1、vcsel(vertical-cavity surface-emitting laser,垂直腔面发射激光器)是指在衬底的垂直方向上形成谐振腔,沿垂直方向出射激光的一种半导体激光器。vcsel芯片具有温漂小、低阈值、光纤耦合效率高、易于集成和封装等特性,被广泛应用于智慧交通、健康医疗、生物检测和军事安防等领域。

2、在实际产业中,当vcsel芯片被应用于车载激光雷达时,vcsel芯片可作为投射光源对被测目标进行深度测量以采集路况信息来辅助车辆实现路线规划、路障规避等功能。vcsel芯片的出光性能将影响激光雷达的深度测量功能,是激光雷达的重要性能指标。

3、目前,vcsel芯片在车载激光雷达的应用中,出现出光强度不均的问题。具体地,vcsel芯片包括多个发光点,理想情况下,多个发光点的出光强度一致。而在实际应用中,vcsel芯片的多个发光点的出光强度的一致性较差,将影响激光雷达的深度测量的准确性。

4、因此,需要一种新型的vcsel芯片的设计方案,以提高vcsel芯片的出光强度均匀度。

技术实现思路

1、本技术的一个优势在于提供了一种vcsel芯片及其制备方法,其中,所述vcsel芯片能够通过减弱其发光区域结构中周缘部分的散热性能来平衡所述发光区域结构的中区部分和周缘部分的出光强度,以提高vcsel芯片的出光强度均匀度。

2、在本技术的另一个优势在于提供了一种vcsel芯片及其制备方法,其中,所述vcsel芯片能够在保证其整体出光强度的同时提高其出光强度均匀度,以平衡所述vcsel芯片的整体出光强度与其出光强度均匀度的关系。

3、本技术的又一个优势在于提供了一种vcsel芯片及其制备方法,其中,所述vcsel芯片通过减弱其发光区域结构中周缘部分的散热性能来提高vcsel芯片的出光强度均匀度,这样,可降低vcsel芯片的设计难度。

4、本技术的又一个优势在于提供了一种vcsel芯片及其制备方法,其中,所述vcsel芯片能够在不改变各个vcsel发光单元的相对位置关系的前提下提高vcsel芯片的出光均匀度。

5、在本技术的一个优势在于提供了一种vcsel芯片及其制备方法,其中,在本技术的vcsel芯片的制备过程中沿用传统的vcsel芯片的制备工艺,这样,可保留原有的vcsel芯片生产线和生产设备以将其用于制备本技术的vcsel芯片,有效降低vcsel芯片的生产线改造成本,进而降低制备成本。

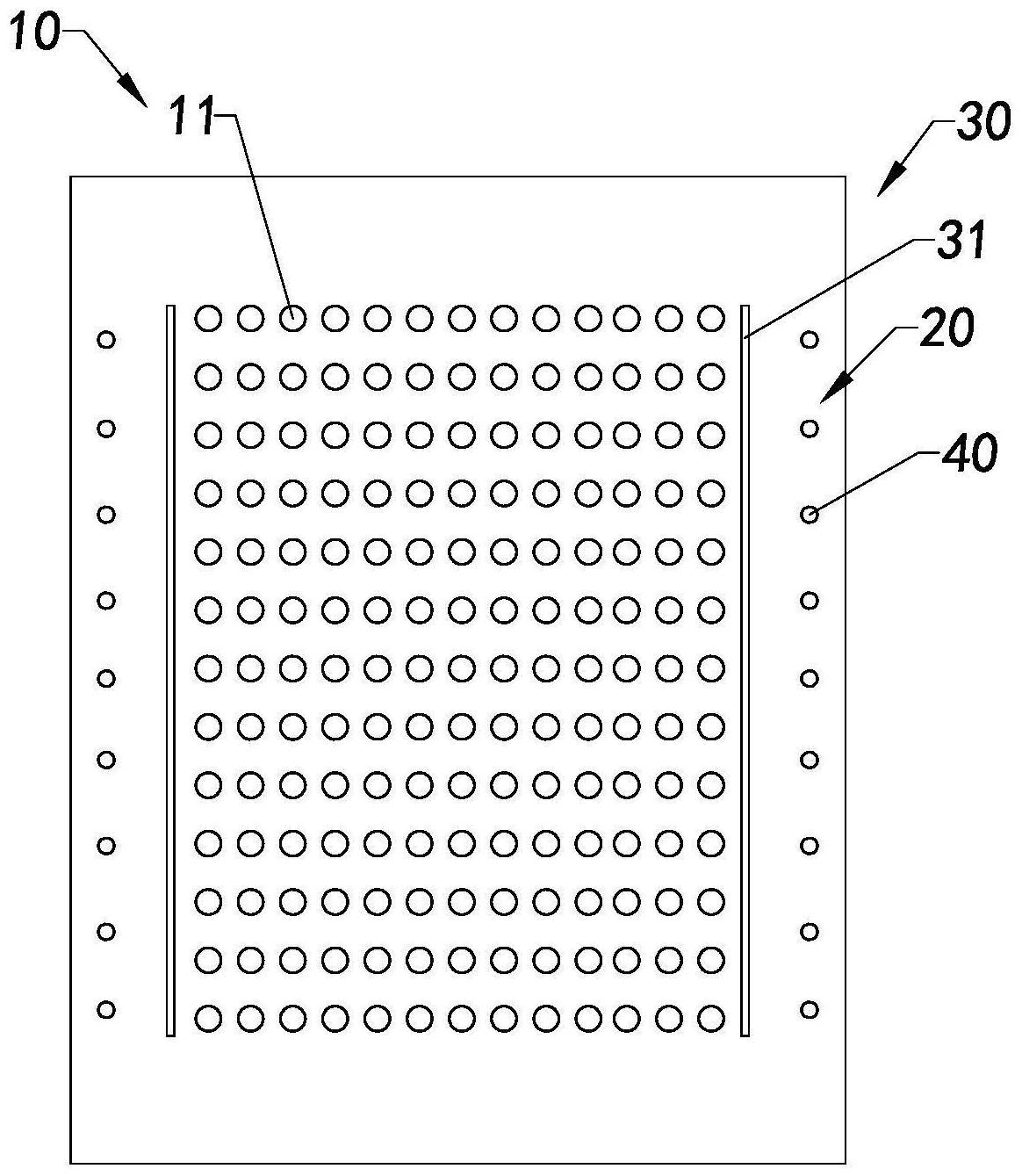

6、为了实现上述至少一优势或其他优势和目的,根据本技术的一个方面,提供了一种vcsel芯片,其包括:

7、发光区域结构,包括多个vcsel发光单元;

8、环绕所述发光区域结构的外围区域结构;以及

9、形成于所述外围区域结构的阻热结构。

10、在本技术的vcsel芯片中,所述阻热结构形成于所述外围区域结构的位置邻近于所述发光区域结构。

11、在本技术的vcsel芯片中,所述阻热结构包括凹陷地形成于所述外围区域结构的至少一凹槽。

12、在本技术的vcsel芯片中,所述外围区域结构自下而上包括第二衬底层结构部分、第二n型电接触层结构部分、第二n-dbr层结构部分、第二主动层结构部分、第二p-dbr层结构部分和第二p型电接触层结构部分,其中,所述第二p型电接触层结构部分的上表面形成所述外围区域结构的上表面。

13、在本技术的vcsel芯片中,所述第二p型电接触层结构部分的至少一部分向下凹陷以形成所述至少一凹槽。

14、在本技术的vcsel芯片中,所述第二p型电接触层结构部分的至少一部分延伸至所述第二主动层结构部分。

15、在本技术的vcsel芯片中,所述第二p型电接触层结构部分的至少一部分延伸至所述第二n-dbr层结构部分。

16、在本技术的vcsel芯片中,所述第二p型电接触层结构部分的至少一部分延伸至所述第二衬底层结构部分。

17、在本技术的vcsel芯片中,所述至少一凹槽贯穿所述外围区域结构的上表面并延伸至所述外围区域结构的内部。

18、在本技术的vcsel芯片中,所述至少一凹槽延伸至所述第二主动层结构部分。

19、在本技术的vcsel芯片中,所述至少一凹槽延伸至所述第二n-dbr层结构部分。

20、在本技术的vcsel芯片中,所述至少一凹槽延伸至第二衬底层结构部分。

21、在本技术的vcsel芯片中,所述至少一凹槽包括相对于所述发光区域结构对称分布的第一凹槽和第二凹槽。

22、在本技术的vcsel芯片中,所述多个vcsel发光单元以等间距的方式分布于所述发光区域结构。

23、在本技术的vcsel芯片中,每一个所述vcsel发光单元自下而上包括负电极、衬底层、n型电接触层、n-dbr层、有源区、限制层、p-dbr层、p型电接触层和正电极,其中,所述限制层具有与所述有源区对应的限制孔。

24、在本技术的vcsel芯片中,所述的vcsel芯片进一步包括形成于所述外围区域结构的至少一电连接端,其中,所述阻热结构形成于所述外围区域结构的位置位于所述至少一电连接端和所述发光区域结构之间。

25、在本技术的vcsel芯片中,所述阻热结构进一步包括填充于所述至少一凹槽内的填充体,所述填充体由阻热材料制成。

26、在本技术的vcsel芯片中,所述vcsel芯片的整光强均匀度的提升幅度为3%-25%。

27、根据本技术的另一个方面,提供了一种vcsel芯片的制备方法,其包括:

28、形成外延层结构,其中,所述外延层结构包括第一区域结构和环绕于所述第一区域的第二区域结构,所述第一区域结构自下而上包括:第一衬底层结构部分、第一n型电接触层结构部分、第一n-dbr层结构部分、第一主动层结构部分和第一p-dbr层结构部分,所述第二区域结构自下而上包括:第二衬底层结构部分、第二n型电接触层结构部分、第二n-dbr层结构部分、第二主动层结构部分和第二p-dbr层结构部分;

29、去除所述第二区域结构的至少一部分,以在所述第二区域结构形成至少一凹槽;

30、去除所述第一区域结构的至少一部分以形成隔离区域;

31、在形成所述至少一凹槽后的外延层结构的上表面形成p型电接触层结构,以在所述第一p-dbr层结构部分的上表面形成第一p型电接触层结构部分,在所述第二p-dbr层结构部分的上表面和所述至少一凹槽的上表面形成第二p型电接触层结构部分,以形成相互间隔的多个子结构单元,每个所述子结构单元自下而上包括:n型电接触层、n-dbr层、有源区、p-dbr层和p型电接触层;

32、形成电连接于所述第一p型电接触层结构部分的多个正电极;

33、对所述多个子结构单元进行处理,以在所述有源区的上方形成具有限制孔的限制层;以及

34、形成电连接于形成所述限制层后的多个子结构单元的负电连接结构,以形成包括多个vcsel发光单元的发光区域结构。

35、在本技术的vcsel芯片的制备方法中,去除所述第二区域的至少一部分,包括:在所述第二区域施加可蚀刻层;通过掩膜将所述可蚀刻层塑性为具有预设形状和尺寸的模板,其中,所述第二区域包括用于形成所述阻热结构的预设部分和环绕于所述预设部分的剩余部分,所述模板的预设形状和尺寸与所述剩余部分的形状和尺寸一致;以及,通过蚀刻工艺去除所述模板和所述第二区域的预设部分,以在所述第二区域形成至少一凹槽。

36、在本技术的vcsel芯片的制备方法中,对所述多个子结构单元进行处理,以在所述有源区的上方形成具有限制孔的限制层,包括:对所述多个子结构单元进行氧化,以在所述有源区的上方形成具有限制孔的氧化限制层。

37、在本技术的vcsel芯片的制备方法中,去除所述第二区域结构的至少一部分,以在所述第二区域结构形成至少一凹槽,以及,去除所述第一区域结构的至少一部分以形成隔离区域,被同时执行。

38、根据本技术的另一个方面,提供了一种vcsel芯片的制备方法,其包括:

39、形成外延层结构,其中,所述外延层结构包括第一区域结构和环绕于所述第一区域的第二区域结构,所述第一区域结构自下而上包括:第一衬底层结构部分、第一n型电接触层结构部分、第一n-dbr层结构部分、第一主动层结构部分和第一p-dbr层结构部分,所述第二区域结构自下而上包括:第二衬底层结构部分、第二n型电接触层结构部分、第二n-dbr层结构部分、第二主动层结构部分和第二p-dbr层结构部分;

40、在所述外延结构的上表面形成p型电接触层结构,以在所述第一p-dbr层结构部分的上表面形成第一p型电接触层结构部分,在所述第二p-dbr层结构部分的上表面形成第二p型电接触层结构部分;

41、去除形成所述第二p型电接触层结构部分后的第二区域的至少一部分,以在所述第二区域形成至少一凹槽;

42、去除所述第一区域结构和所述第一p型电接触层结构部分的至少一部分以形成相互间隔的多个子结构单元,每个所述子结构单元自下而上包括:n型电接触层、n-dbr层、有源区、p-dbr层和p型电接触层;

43、形成电连接于所述第一p型电接触层结构部分的多个正电极;

44、对所述多个子结构单元进行处理,以在所述有源区的上方形成具有限制孔的限制层;以及

45、形成电连接于形成所述限制层后的多个子结构单元的负电连接结构,以形成包括多个vcsel发光单元的发光区域结构。

46、通过对随后的描述和附图的理解,本技术进一步的目的和优势将得以充分体现。

47、本技术的这些和其它目的、特点和优势,通过下述的详细说明,附图和权利要求得以充分体现。

- 还没有人留言评论。精彩留言会获得点赞!