显示基板的制作方法

1.本发明涉及显示技术领域,具体地,涉及一种显示基板。

背景技术:

2.低温多晶氧化物(low-temperature polycrystalline oxide,缩写为ltpo)半导体产品结合了低温多晶硅(low temperature poly-silicon,缩写为ltps)迁移率高、充电快,以及金属氧化物(metal oxide)低漏电流和低功耗的优势,使显示产品的用户体验得到大步提升。

3.现有的一种低温多晶氧化物有机发光二极管(organic light-emitting diode,缩写为oled)阵列基板包括玻璃衬底(glass)、第一缓冲层(buffer)、第一栅极绝缘层(gate insulator,缩写为gi)、第二栅极绝缘层、层间介质层(inter-level dielectric,缩写为ild)和第二缓冲层,其中,第一缓冲层设置在玻璃衬底上,第一缓冲层上设置有低温多晶硅薄膜晶体管(thin film transistor,缩写为tft)的多晶硅(p-si),第一栅极绝缘层设置在第一缓冲层上,并覆盖多晶硅,第二栅极绝缘层设置在第一栅极绝缘层上,层间介质层设置在第二栅极绝缘层上,第二缓冲层设置在层间介质层上,第二缓冲层上设置有金属氧化物薄膜晶体管的金属氧化物。

4.但是,现有的一种低温多晶氧化物有机发光二极管阵列基板,由于膜层数量多,导致玻璃衬底可能会因各膜层应力而翘曲变形,对低温多晶氧化物产品的生产效率产生影响,并且还会导致制备工艺复杂且成本较高。

技术实现要素:

5.本发明旨在至少解决现有技术中存在的技术问题之一,提出了一种显示基板,其能够减小衬底翘曲变形的程度,提高产品的生产效率,并能够降低制备工艺的复杂度及成本。

6.为实现上述目的,本发明提供一种显示基板,包括第一缓冲层、第一栅极绝缘层、第二栅极绝缘层和第二缓冲层,所述第一缓冲层上用于设置多晶硅薄膜晶体管中的多晶硅,所述第一栅极绝缘层设置在所述第一缓冲层上,并覆盖设置在所述第一缓冲层上的所述多晶硅,所述第二栅极绝缘层设置在所述第一栅极绝缘层上,所述第二缓冲层设置在所述第二栅极绝缘层上,所述第二缓冲层上用于设置氧化物薄膜晶体管中的氧化物。

7.可选的,所述第二栅极绝缘层包括第一子绝缘层和第二子绝缘层,所述第一子绝缘层设置在所述第一栅极绝缘层上,所述第二子绝缘层设置在所述第一子绝缘层上,所述第二缓冲层设置在所述第二子绝缘层上,所述第二子绝缘层中的氢的含量小于所述第一子绝缘层中的氢的含量。

8.可选的,所述第二子绝缘层中的硅氢键的含量小于所述第一子绝缘层中的硅氢键的含量。

9.可选的,所述第一子绝缘层中的硅氢键的含量的范围为3%-10%,和/或,所述第

二子绝缘层中的硅氢键的含量的范围为0.5%-3%。

10.可选的,所述第二子绝缘层中的硅氢键的含量的范围为0.5%-1.5%。

11.可选的,所述第二子绝缘层的致密度大于所述第一子绝缘层中的致密度。

12.可选的,所述第二子绝缘层中的硅元素与氮元素的比值大于所述第一子绝缘层中的硅元素与氮元素的比值。

13.可选的,所述第一子绝缘层中的硅元素与氮元素的比值的范围为0.7-0.8,和/或,所述第二子绝缘层中的硅元素与氮元素的比值的范围为0.8-1.5。

14.可选的,所述第二子绝缘层中的硅元素与氮元素的比值的范围为1-1.5。

15.可选的,所述第一子绝缘层的厚度的范围为50nm-150nm,和/或,所述第二子绝缘层的范围为10nm-100nm。

16.本发明具有以下有益效果:

17.本发明提供的显示基板,与现有的一种低温多晶氧化物有机发光二极管阵列基板相比,不是在第二栅极绝缘层上先设置层间介质层,之后再在层间介质层上设置第二缓冲层,而是在第二栅极绝缘层上直接设置第二缓冲层,也就是说,本发明提供的显示基板,与现有的一种低温多晶氧化物有机发光二极管阵列基板相比,去掉了设置在第二栅极绝缘层和第二缓冲层之间的层间介质层,从而能够减少设置在显示基板的衬底上的膜层的数量,减小衬底受到的各膜层的应力,进而能够减小衬底翘曲变形的程度,提高产品的生产效率,并能够降低制备工艺的复杂度及成本。

附图说明

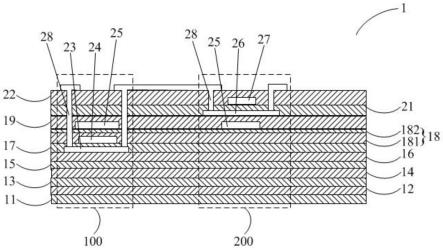

18.图1为本发明提供的显示基板的一种结构示意图;

19.图2为本发明提供的显示基板的另一种结构示意图;

20.附图标记说明:

21.1-显示基板;11-衬底;12-第一柔性膜层;13-第一阻挡层;14-第二柔性膜层;15-第二阻挡层;16-第一缓冲层;17-第一栅极绝缘层;18-第二栅极绝缘层;181-第一子绝缘层;182-第二子绝缘层;19-第二缓冲层;21-第三栅极绝缘层;22-层间介质层;23-多晶硅;24-第一栅极;25-第二栅极;26-氧化物;27-第三栅极;28-漏极金属连接线;100-多晶硅薄膜晶体管;200-氧化物薄膜晶体管。

具体实施方式

22.为使本领域的技术人员更好地理解本发明的技术方式,下面结合附图来对本发明提供的显示基板进行详细描述。

23.如图1和图2所示,本发明实施例提供一种显示基板1,包括第一缓冲层16、第一栅极绝缘层17、第二栅极绝缘层18和第二缓冲层19,第一缓冲层16上用于设置多晶硅薄膜晶体管100中的多晶硅23,第一栅极绝缘层17设置在第一缓冲层16上,并覆盖设置在第一缓冲层16上的多晶硅23,第二栅极绝缘层18设置在第一栅极绝缘层17上,第二缓冲层19设置在第二栅极绝缘层18上,第二缓冲层19上用于设置氧化物薄膜晶体管200中的氧化物26。

24.本发明实施例提供的显示基板1,与现有的一种低温多晶氧化物26有机发光二极管阵列基板相比,不是在第二栅极绝缘层18上先设置层间介质层22,之后再在层间介质层

22上设置第二缓冲层19,而是在第二栅极绝缘层18上直接设置第二缓冲层19,也就是说,本发明实施例提供的显示基板1,与现有的一种低温多晶氧化物26有机发光二极管阵列基板相比,去掉了设置在第二栅极绝缘层18和第二缓冲层19之间的层间介质层22,从而能够减少设置在显示基板1的衬底11上的膜层的数量,减小衬底11受到的各膜层的应力,进而能够减小衬底11翘曲变形的程度,提高产品的生产效率,并能够降低制备工艺的复杂度及成本。

25.可选的,多晶硅薄膜晶体管100可以包括低温多晶硅薄膜晶体管。

26.可选的,低温多晶硅薄膜晶体管中的多晶硅23可以包括低温多晶硅。

27.可选的,氧化物薄膜晶体管200可以包括金属氧化物薄膜晶体管。

28.可选的,金属氧化物薄膜晶体管中的氧化物26可以包括铟镓锌氧化物26(indium gallium zinc oxide,缩写为igzo)。

29.如图2所示,在本发明一优选实施例中,第二栅极绝缘层18可以包括第一子绝缘层181和第二子绝缘层182,第一子绝缘层181设置在第一栅极绝缘层17上,第二子绝缘层182设置在第一子绝缘层181上,第二缓冲层19设置在第二子绝缘层182上,第二子绝缘层182中的氢的含量小于第一子绝缘层181中的氢的含量。

30.这样的设计是由于多晶硅薄膜晶体管100具有“喜氢(h)”的特性,氢可以去除多晶硅薄膜晶体管100中的多晶硅23与第一栅极绝缘层17的界面处的悬挂键,改善多晶硅薄膜晶体管100的特性,而氧化物薄膜晶体管200具有“厌氢”的特性,氢会使氧化物薄膜晶体管200的特性变得不稳定。因此,一方面通过将第一子绝缘层181设置在第一栅极绝缘层17上,使第一子绝缘层181相对于第二子绝缘层182靠近多晶硅23,由于第一子绝缘层181中的氢的含量大于第二子绝缘层182中的氢的含量,因此,可以使第一子绝缘层181中的氢更容易的游离扩散至多晶硅23与第一栅极绝缘层17的界面处,从而可以利用第一子绝缘层181中的氢去除多晶硅23与第一栅极绝缘层17的界面处的悬挂键,进而可以改善多晶硅薄膜晶体管100的特性。并且,另一方面通过将第二子绝缘层182设置在第一子绝缘层181上,第二缓冲层19设置在第二子绝缘层182上,使第二子绝缘层182相对于第一子绝缘层181靠近设置在第二缓冲层19上的氧化物26,由于第二子绝缘层182中的氢的含量小于第一子绝缘层181中的氢的含量,因此,可以减少游离扩散至氧化物26的沟道的氢,从而可以减小氢对氧化物薄膜晶体管200的特性的影响,使氧化物薄膜晶体管200的特性能够保持稳定,进而在减少设置在显示基板1的衬底11上的膜层的数量,减小衬底11受到的各膜层的应力,减小衬底11翘曲变形的程度,提高产品的生产效率,并降低制备工艺的复杂度及成本的基础上,还能够减小对氧化物薄膜晶体管200的特性的影响,使氧化物薄膜晶体管200的特性能够保持稳定。

31.可选的,第一子绝缘层181可以包括氮化硅(sin)薄膜。

32.可选的,第二子绝缘层182可以包括氮化硅薄膜。

33.在本发明一优选实施例中,第二子绝缘层182中的硅氢键的含量可以小于第一子绝缘层181中的硅氢键的含量。

34.这是由于在例如氮化硅薄膜的第一子绝缘层181和第二子绝缘层182中,会存在硅氮键(si-n),并且会可能会残留有硅氢键(si-h),其中,硅氢键的键能较低,在显示基板1进行例如高温退火工艺时,硅氢键较容易断开分离成硅(si)和氢(h),而氢在高温退火的作用下,会游离扩散至多晶硅23与第一栅极绝缘层17的界面处,去除多晶硅23与第一栅极绝缘

层17的界面处的悬挂键,因此,第一子绝缘层181和第二子绝缘层182中的硅氢键的含量,就可以代表第一子绝缘层181和第二子绝缘层182中的氢的含量,因此,通过使第二子绝缘层182中的硅氢键的含量可以小于第一子绝缘层181中的硅氢键的含量,可以实现第二子绝缘层182中的氢的含量小于第一子绝缘层181中的氢的含量,而硅氮键的键能较高,在显示基板1进行例如高温退火工艺时,硅氮键较高,在显示基板1进行例如高温退火工艺时,硅氮键较为稳定不易断开。

35.在本发明一优选实施例中,第一子绝缘层181中的硅氢键的含量的范围可以为3%-10%,和/或,第二子绝缘层182中的硅氢键的含量的范围可以为0.5%-3%。

36.在本发明一优选实施例中,第二子绝缘层182中的硅氢键的含量的范围可以为0.5%-1.5%。

37.在本发明一优选实施例中,第二子绝缘层182的致密度可以大于第一子绝缘层181中的致密度。

38.通过使第二子绝缘层182的致密度大于第一子绝缘层181中的致密度,可以借助第二子绝缘层182阻挡第一子绝缘层181和第二子绝缘层182中的氢向上游离扩散至氧化物26的沟道,从而可以进一步减小氢对氧化物薄膜晶体管200的特性的影响,使氧化物薄膜晶体管200的特性能够进一步保持稳定,进而在减少设置在显示基板1上的膜层的数量,减小显示基板1的衬底11受到的各膜层的应力,减小衬底11翘曲变形的程度,提高产品的生产效率,并降低制备工艺的复杂度及成本的基础上,能够进一步减小对氧化物薄膜晶体管200的特性的影响,使氧化物薄膜晶体管200的特性能够进一步保持稳定

39.在本发明一优选实施例中,第二子绝缘层182中的硅元素与氮元素的比值可以大于第一子绝缘层181中的硅元素与氮元素的比值。

40.通过使第二子绝缘层182中的硅元素与氮元素的比值大于第一子绝缘层181中的硅元素与氮元素的比值,可以实现第二子绝缘层182的致密度大于第一子绝缘层181中的致密度。

41.在本发明一优选实施例中,第一子绝缘层181中的硅元素与氮元素的比值的范围可以为0.7-0.8,和/或,第二子绝缘层182中的硅元素与氮元素的比值的范围可以为0.8-1.5。

42.在本发明一优选实施例中,第二子绝缘层182中的硅元素与氮元素的比值的范围可以为1-1.5。

43.在本发明一优选实施例中,第一子绝缘层181的厚度的范围可以为50nm-150nm,和/或,第二子绝缘层182的范围可以为10nm-100nm。

44.可选的,显示基板1可以还包括衬底11(可选为玻璃衬底11(glass))、第一柔性膜层12(材料可选为聚酰亚胺(polyimide,缩写为pi))、第一阻挡层13(barrier)、第二柔性膜层14(材料可选为聚酰亚胺)、第二阻挡层15、第三栅极绝缘层21、层间介质层22、第一栅极24(gate)、第二栅极25、第三栅极27和源漏极金属连接线28(sd)。

45.其中,第一柔性膜层12、第一阻挡层13、第二柔性膜层14和第二阻挡层15由下至上依次层叠设置在衬底11上,第二阻挡层15上层叠设置有第一缓冲层16,第一栅极24设置在第一栅极绝缘层17上,第二栅极绝缘层18设置在第一栅极绝缘层17上,并覆盖第一栅极24,第二栅极25设置在第二栅极绝缘层18上,并被设置在第二栅极绝缘层18上的第二缓冲层19

覆盖(如图1所示),当第二栅极绝缘层18包括第一子绝缘层181和第二子绝缘层182时,第一子绝缘层181设置在第一栅极绝缘层17上,并覆盖第一栅极24,第二子绝缘层182设置在第一子绝缘层181上,第二栅极25设置在第二子绝缘层182上,并被设置在第二子绝缘层182上的第二缓冲层19覆盖(如图2所示),第三栅极绝缘层21设置在第二缓冲层19上,并覆盖设置在第二缓冲层19上的氧化物26,第三栅极27设置在第三栅极绝缘层21上,层间介质层22设置在第三栅极绝缘层21上,并覆盖第三栅极27,多晶硅薄膜晶体管100可以包括多晶硅23、位于多晶硅23上方的第一栅极24和第二栅极25,氧化物薄膜晶体管200可以包括氧化物26、位于氧化物26下方的第二栅极25和位于氧化物26上方的第三栅极27,源漏极金属连接线28穿过部分膜层与多晶硅23的用于形成源极和漏极的两端连接,并穿过部分膜层与氧化物26的用于形成源极和漏极的两端连接。

46.并且,显示基板1可以还包括图中未示出的保护层(pvx),保护层可以设置在层间介质层22上,并覆盖位于层间介质层22上的部分源漏极金属连接线28。

47.综上所述,本发明实施例提供的显示基板1能够减小衬底11翘曲变形的程度,提高产品的生产效率,并能够降低制备工艺的复杂度及成本。

48.可以理解的是,以上实施方式仅仅是为了说明本发明的原理而采用的示例性实施方式,然而本发明并不局限于此。对于本领域内的普通技术人员而言,在不脱离本发明的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1