一种冷源晶体管、其制作方法及集成电路与流程

本技术涉及半导体,特别涉及一种冷源晶体管、其制作方法及集成电路。

背景技术:

1、传统金氧半场效晶体管(metal-oxide-semiconductor field-effecttransistor,mosfet)受限于载流子玻尔兹曼分布(maxwell–boltzmann distribution),会因为热激发形成漏电流,使得电流的栅控效率在常温下无法突破60mv/dec的亚阈值摆幅,亚阈值摆幅是衡量晶体管开启与关断状态之间相互转换速率的性能指标,它代表源漏电流变化十倍所需要栅电压的变化量,又称为s因子,s因子越小意味着开启关断速率越快。因此,为了降低亚阈值摆幅,mosfet的阈值电压通常设置在100到300mv之间。

2、现有研究中,能使亚阈值摆幅小于60mv/dec的晶体管主要有隧穿场效应晶体管(tunnel fet,t-fet)和负电容场效应晶体管(negative vapacitance fet,nc-fet)两类。t-fet的开态电流太低,没有实用价值,nc-fet由于负电容的不稳定性对晶体管的实际应用造成严重阻碍,因此被业界放弃。

3、目前一种新型的超陡阈值摆幅场效应晶体管:冷源晶体管(cold source fet,csfet)被提出。csfet的技术核心是通过源端载流子态密度调控,从而减少热载流子分布降低亚阈值摆幅,使得集成电路的工作电压进一步降低。

4、但上述csfet的亚阈值摆幅的计算通常基于理想化的弹道运输条件,但在实际应用中,由于电子-声子相互作用(electron-phonon interaction)所带来的耦合散射输运,会引起电子热化问题。因此,冷电子在从源端进入到沟道之前会出现部分热化的问题,热化后的高能电子又会重新形成漏电流,使得电流的栅控效率升高。有鉴于此,需要提出一种新型冷源晶体管,在保证开态电流足够大的前提下,使其性能也能更加稳定。

技术实现思路

1、本技术提供了一种冷源晶体管、其制作方法及集成电路,由于栅极设置于沟道区上,使得冷载流子不再受到被外部重新热化,因此可以降低由热化的冷载流子造成的漏电,从而降低亚阈值摆幅,使其性能也能更加稳定。

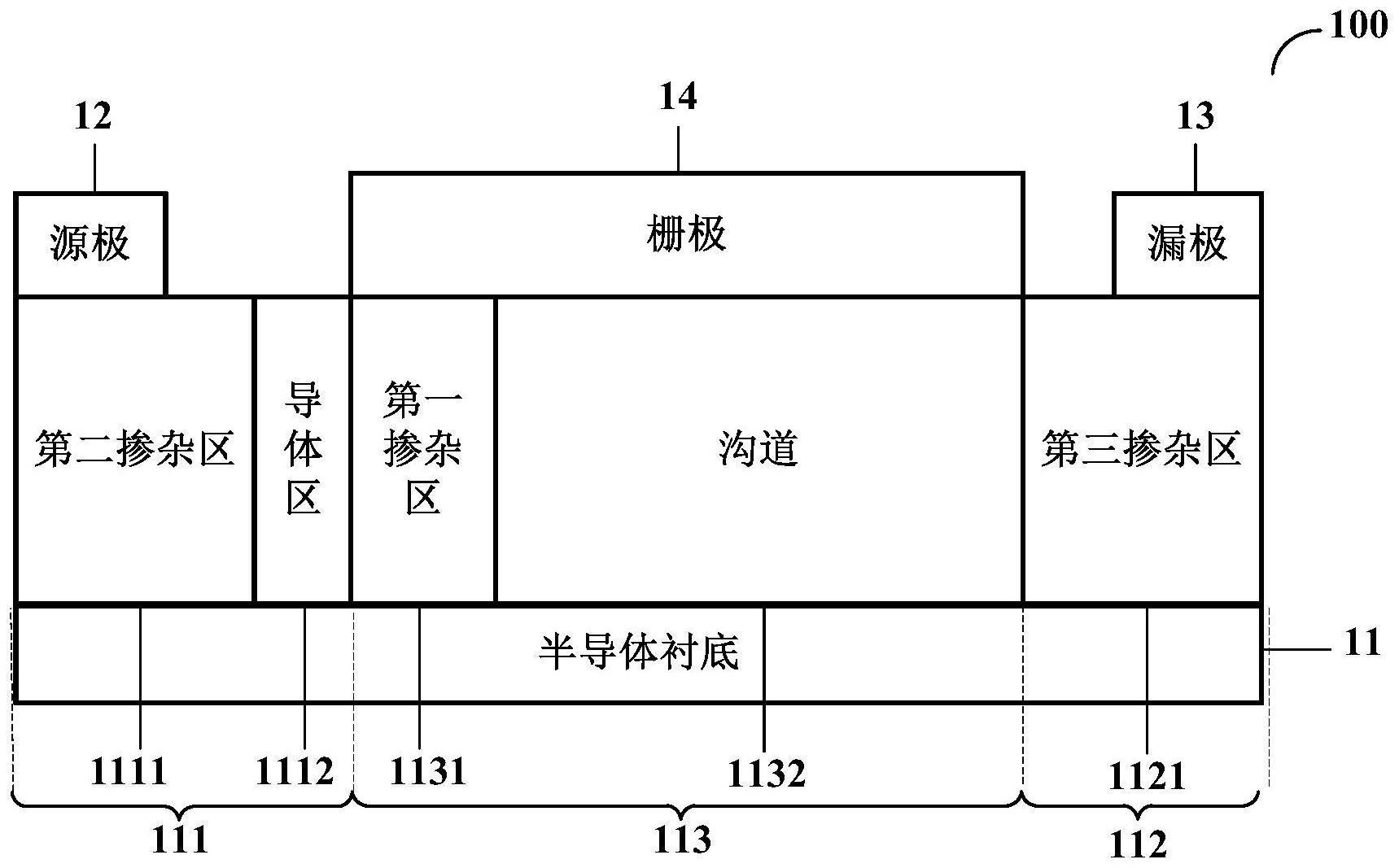

2、第一方面,本技术提供一种冷源晶体管,包括:半导体衬底、源极、漏极以及栅极;半导体衬底具有源区、漏区以及位于源区与漏区之间的沟道区,源极耦合于源区,漏极耦合于漏区,栅极设置于沟道区上;沟道区包括第一掺杂区及沟道,第一掺杂区在源区一侧,沟道在漏区一侧;源区包括第二掺杂区及导体区,导体区设置在第一掺杂区和第二掺杂区之间;漏区包括第三掺杂区;第一掺杂区与第三掺杂区属于同一掺杂类型,第二掺杂区与第三掺杂区属于不同的掺杂类型。

3、在制作过程中,可采用掺杂工艺在半导体衬底的表面形成源区、漏区以及位于源区与漏区之间的沟道区。由于第一掺杂区与第三掺杂区属于同一掺杂类型,可以采用同一掺杂工艺制作第一掺杂区与第三掺杂区,从而节省工艺步骤,节约制作成本。

4、在本方面中,半导体衬底可以为硅(体硅)衬底结构。还可以是石墨烯(狄拉克锥结构)、锗(ge)、锗硅(sige)、氮化镓(gan)、铟镓砷(ingaas)等半导体材料中的一种或多种。冷源晶体管相当于开关器件,在实际应用中,在冷源晶体管关闭状态下,源极和漏极之间处于绝缘状态,源区内的电子无法通过沟道区到达漏区。通过向栅极来施加栅极电压,使冷源晶体管处于开启状态,源极与漏极之间处于导通状态。当栅极电压高于阈值电压时,源极与漏极之间导通。当栅极电压低于阈值电压时,冷源晶体管会处于亚阈值状态,源极与漏极之间具有微量漏电流。

5、理想情况下,由于第二掺杂区的能带相对于第一掺杂区的能带上移,而第一掺杂区的能带相对于第二掺杂区的能带下移,第二掺杂区的能带与第一掺杂区的能带相等时,能带才停止相对移动,第二掺杂区与第一掺杂区之间形成的pn结达到平衡状态。达到平衡状态的pn结中,第二掺杂区的价带和第一掺杂区的导带存在重叠区域,在该重叠区域中,电子可以从第二掺杂区遂穿到第一掺杂区,而禁带所在的区域,电子无法遂穿。且由于可以产生电子遂穿的重叠区域仅占比较小的一部分区域,而电子无法遂穿的禁带占了大部分区域,所以pn结可以有效抑制受热能激发的高能载流子,降低由热激发造成的漏电,从而降低亚阈值摆幅。并且,为了提高隧串效率,通过在第二掺杂区与第一掺杂区之间设置导体区,使第二掺杂区以及导体区形成了金属和半导体接触,二者之间的接触面会形成肖特基势垒。当冷载流子可以越过肖特基势垒时,进入沟道区的载流子数量较大且可以迅速通过形成较大的电流,且表现出超低的亚阈值摆幅。如此可以大大提高遂穿几率,提升冷源晶体管的开态电流。

6、但实际情况下,相关技术中的冷源晶体管在进行亚阈值摆幅推算时,仅基于弹道输运考虑,电子的热化问题并未考虑。但实际上,由于电子实际上会受到各类散射影响,电子在从源区到沟道区之前,会出现部分热化问题。为了解决该问题,本技术提供的冷源晶体管,栅极设置于沟道区上,从而当冷载流子越过pn结以及肖特基势垒,从第一掺杂区进入沟道时,使得冷载流子不再受到被外部重新热化,因此可以降低由热化的冷载流子造成的漏电,从而降低亚阈值摆幅。

7、在本技术的一种实施方式中,冷源晶体管可以为p型冷源晶体管,第一掺杂区的掺杂剂为p型掺杂剂,第二掺杂区的掺杂剂为第一浓度的n型掺杂剂,沟道中的掺杂剂为第二浓度的n型或p型掺杂剂,第一浓度高于第二浓度。

8、在本技术的另一种实施方式中,该冷源晶体管可以为n型冷源晶体管,第一掺杂区的掺杂剂为n型掺杂剂,第二掺杂区的掺杂剂为第三浓度的p型掺杂剂,沟道中的掺杂剂为第四浓度的n型或p型掺杂剂,第三浓度高于第四浓度。

9、通过在源区到沟道区中设置掺杂类型不同的掺杂区,从而形成能量间隙,通过调整源区中的载流子态密度,能够有效过滤高能电子,从而使载流子的能带降低,换言之,本技术实施例中的冷源晶体管的工作参数表现与工作在低温环境下相类似。导体区的厚度较小,可以为3~5nm,以保证足够高的透射和低的热化率。

10、本技术实施例提供的上述冷源晶体管中,导体区中包括用于提供冷载流子的材料,提供冷载流子的材料可以包括以下至少一种:金属材料、半金属材料、金属硅化物材料、拓扑绝缘体、二维过渡金属硫化物以及二维过渡金属碳化物。

11、金属材料包括:铝、金、银、铂、镍、钯、钴、钨或钌中的至少一种。上述半金属材料是指导带和价带之间相隔很窄的材料。根据能带理论,导带和价带之间的间隔从窄到宽,固体可以依次分为金属、半金属、半导体和绝缘体。也就是说,半金属材料的导带与价带之间的间隔,小于半导体材料的导带与价带之间的间隔,且大于金属材料的导带与价带之间的间隔。对于半导体和绝缘体,导带和价带之间的间隔相对较大,使得费米能级附近电子的态密度等于零,成为带隙,其中绝缘体的带隙比半导体的大。金属的费米能级则在导带当中,附近有足够大的电子态密度,使得电流可以良好地传导。而对于半金属材料,由于半金属材料的导带和价带之间的间隔十分小,使得费米能级附近电子的态密度接近于零但不为零,因此半金属材料没有带隙。半金属材料在元素周期表中处于金属向非金属过渡的位置,物理性质和化学性质介于金属和非金属之间。例如,半金属材料包括:砷、锑、铋、锡或石墨中的至少一种。

12、金属硅化物材料可以为硅化镍、硅化铂、硅化钯、硅化铱中的一种或多种。拓扑绝缘体是一种内部绝缘,界面允许电荷移动的材料。在拓扑绝缘体的内部,电子能带结构和常规的绝缘体相似,其费米能级位于导带和价带之间。在拓扑绝缘体的表面存在一些特殊的量子态,这些量子态位于块体能带结构的带隙之中,从而允许导电。

13、在本技术的一种实施方式中,栅极与沟道区之间还可以包括栅极介质层。在本技术提供的冷源晶体管为电荷俘获型冷源晶体管时,栅极介质层包括:位于栅极靠近沟道区一侧的隧穿层,位于隧穿层与栅极之间的电荷俘获层,以及位于电荷俘获层与栅极之间的电荷阻挡层。

14、在本技术提供的冷源晶体管为铁电冷源晶体管时,栅极介质层包括:位于栅极靠近沟道区一侧的界面氧化层,以及位于界面氧化层与栅极之间的铁电层。

15、在本技术的一种实施方式中,本技术提供的冷源晶体管中,栅极位于半导体衬底的一侧,上述冷源晶体管还可以包括:覆盖栅极的顶面和侧面的绝缘层,绝缘层可以绝缘栅极与源极,且绝缘层可以绝缘栅极与漏极。例如,该绝缘层可以包括第一绝缘层,以及覆盖第一绝缘层的第二绝缘层,第一绝缘层可以采用二氧化硅材料制作,第二绝缘层可以采用氧化硅材料制作,当然,第一绝缘层和第二绝缘层也可以采用其他材料,此处不做限定。本技术实施例中,通过设置覆盖栅极的顶面和侧面的绝缘层,可以绝缘栅极与源极和漏极,防止栅极与源极或漏极发生短接。

16、第二方面,本技术提供了一种集成电路,该集成电路可以包括:第一方面中提供的冷源晶体管,以及与冷源晶体管电连接的信号线。因本技术实施例提供的冷源晶体管的亚阈值摆幅较低,因此,本技术实施例中的集成电路的工作电压也较低,进而可以降低该集成电路的功耗。

17、第三方面,本技术还提供一种冷源晶体管的制作方法,该方法包括:

18、提供半导体衬底;在半导体衬底上形成源区、漏区以及位于源区与漏区之间的沟道区,沟道区包括第一掺杂区及沟道,第一掺杂区在源区一侧,沟道在漏区一侧;源区包括第二掺杂区及导体区,导体区设置在第一掺杂区和第二掺杂区之间;漏区包括第三掺杂区,第一掺杂区与第三掺杂区属于同一掺杂类型,第二掺杂区与第三掺杂区属于不同的掺杂类型;在半导体衬底上设置栅极,栅极设置于沟道区上;在源区设置源极,在漏区设置漏极。

19、在本技术的一种实施方式中,采用掺杂工艺分别形成第一掺杂区和第三掺杂区,包括:采用同一掺杂工艺,形成第一掺杂区和第三掺杂区。

20、在本技术的一种实施方式中,在半导体衬底上设置栅极包括:在半导体衬底上设置界面氧化层;在界面氧化层上设置铁电层;在铁电层上设置栅极。

21、在本技术的一种实施方式中,在半导体衬底上设置栅极包括:在沟道区上设置隧穿层;在隧穿层上电荷俘获层;在电荷俘获层上设置电荷阻挡层;在电荷阻挡层上设置栅极。

22、在本技术的一种实施方式中,源区与漏区相对于沟道可以对称设置,由于第一掺杂区与第三掺杂区属于同一掺杂类型,第二掺杂区与第三掺杂区属于不同的掺杂类型,第一导体区与第二导体区的材质相同。在具体使用时,可以无需区分源极、漏极,在第一电极为源极时,第二电极则为漏极,因此使用的场景更广,并且便于维护。

- 还没有人留言评论。精彩留言会获得点赞!