一种全隔离N型LDMOS器件及其制备方法

一种全隔离n型ldmos器件及其制备方法

技术领域

1.本发明属于半导体技术,涉及半导体集成电路制造领域,尤其涉及一种全隔离n型ldmos器件(fully isolated lateral double-diffusion metal oxide semiconductor field effect transistor,全隔离横向双扩散金属-氧化物-半导体场效应晶体管)及其制备方法。

背景技术:

2.随着功率集成电路的发展,bcd工艺已经成为了主流的功率器件制备技术,ldmos也由于其耐压能力强、驱动电流大、开关性能好、成本客观等优点成为了bcd工艺的核心器件。

3.ldmos器件通常用于高压上应用,随着对高电压水平的需求增加,在特定的使用需求下,ldmos需要满足电路系统之间的高电压隔离,来防止内部源端电压高于漏端造成的横向漏电。传统技术中,通常使用横向三极管形成结隔离,这种结隔离的方法往往会存在结击穿的危险,为了避免横向结击穿问题,只能通过增大面积的方式来解决。

技术实现要素:

4.本发明的目的是针对现有的结隔离的全隔离n型ldmos隔离方法面积较大,侧向隔离漏电的问题,提出了一种设有双层深沟槽(dti)结构全隔离n型ldmos器件及其制备方法,通过改变横向的隔离方式,增大横向bv的同时减少面积和漏电电流。

5.为实现上述目的,本发明采用以下技术方案:一种全隔离n型ldmos器件,特点是所述器件的结构是以几何中心横向对称分布,具体包括:p型衬底;沿p型衬底向上外延的p型外延层p-epi;设于p型衬底与p型外延层p-epi交界处的重掺杂n型埋层nbl;设于p型外延层p-epi顶部表面中心位置的p型区域hvpw,p型区域hvpw顶端表面中部设有p型外延层substrate电极端及对称分布于所述电极端两侧的n型源端;对称分布于p型区域hvpw两侧的n型漂移区n-drift;设于p型区域hvpw及n型漂移区n-drift底部的p型区域p-type;设于n型漂移区n-drift表面的n型漏端;设于p型外延层p-epi顶部的栅极,栅极与p型外延层p-epi之间设有栅极氧化物,栅极两侧设有侧墙;设于n型漂移区n-drift外侧、与重掺杂n型埋层nbl相连的n型区域dnw;设于n型区域dnw表面的深浓度n型区域n-well,以及设于所述n型区域n-well表面的n型nbl电极端;设于n型区域dnw和n型漂移区n-drift之间、与重掺杂n型埋层nbl相连的内侧深沟

槽结构;设于n型区域dnw与重掺杂n型埋层nbl外侧的深度深沟槽结构及注入在深度深沟槽结构底部的p-区域;设于深度深沟槽结构外侧的p型区域p-well,在p型区域p-well表面顶部设有p型衬底substrate电极端;在p型外延层p-epi顶端表面,设有对称于p型区域hvpw的浅沟槽隔离结构。

6.所述p型衬底为本征、轻掺杂的硅或外延硅;所述p型区域hvpw为p型掺杂的硅;所述p型区域p-well为p型掺杂的硅;所述p型区域p-type为浓于p型外延层p-epi掺杂浓度的硅;所述p型外延层substrate电极端和所述p型衬底substrate电极端为重掺杂的硅;所述p-区域为轻掺杂p型硅;所述栅极为重掺杂多晶硅或者金属;所述栅极氧化物为二氧化硅或二氧化铪;所述侧墙为二氧化硅或sio

2-nitride-sio2结构;所述浅沟槽隔离结构为二氧化硅;所述外侧的深度深沟槽结构与内侧深沟槽结构为二氧化硅或二氧化硅外包其他材料构成的绝缘结构,其中外侧深度深沟槽结构深度高于内侧深沟槽结构深度;所述n型漂移区n-drift为用作漂移区的n型掺杂区域;所述n型源端与n型漏端为n型重掺杂区域;所述重掺杂n型埋层nbl为重掺杂n型区域;所述n型区域dnw为n型掺杂区域;所述n型区域n-well为n型掺杂区域;所述n型nbl电极端为重掺杂n型区域,其中n型区域dnw、n型区域n-well与n型nbl电极端一起构成了重掺杂n型埋层nbl的引出,其掺杂浓度为n型nbl电极端大于n型区域n-well大于n型区域dnw;所述p型外延层substrate电极端、p型区域hvpw与p型区域p-type一起构成深度深沟槽结构内侧的p型外延层p-epi的引出;所述p型衬底substrate电极端与p型区域p-well一起构成深度深沟槽结构外侧的p型衬底的引出。

7.所述外侧深度深沟槽结构用于隔离重掺杂n型埋层nbl,内侧深沟槽结构用于隔离所示结构的n型漂移区n-drift和n型区域dnw ,其中外侧深度深沟槽结构深度要保证大于n型埋层nbl最终深度,内侧深沟槽结构要保证伸入n型埋层nbl最终区域1/5~3/5,既n型漂移区n-drift和n型区域dnw在横向的隔离,同时保证n型区域dnw和重掺杂n型埋层nbl的连通不被内侧深沟槽结构隔断。

8.本发明由所述内侧深沟槽结构形成横向隔离,由高浓度的p-type区域形成纵向隔离,从而形成全隔离型n型ldmos器件。

9.一种上述的全隔离n型ldmos器件的制备方法,该方法包括以下具体步骤:第一步:准备半导体材料,所述半导体材料为p型衬底,p型衬底为p型半导体;第二步:采用光刻工艺,以nbl层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层;采用离子注入工艺,在p型衬底表面注入n型半导体杂质,去胶;第三步:采用外延工艺,在p型衬底表面形成p型外延层p-epi,同时通过外延工艺伴随着的热过程,第二步所注入n型杂质向上扩散入外延层、向下扩散入衬底,形成n型埋层nbl;第四步:采用光刻工艺,以dnw层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层;采用离子注入工艺,p型外延层p-epi表面注入n型半导体杂质,通过推阱工艺使n型杂质扩散形成n型区域dnw;去胶;

第五步:采用刻蚀工艺,在p型外延层p-epi刻蚀浅沟槽,填充氧化物绝缘层sio2,形成浅沟槽隔离(sti)结构;第六步:采用光刻工艺,以内侧深沟槽层的掩模版进行曝光显影,打开所述内侧深沟槽结构的形成区域,采用刻蚀工艺刻蚀内侧深沟槽;在刻蚀所形成的内侧深沟槽区域填充二氧化硅或二氧化硅包其他材料构成的绝缘结构,形成内侧深沟槽结构;第七步:采用光刻工艺,以内侧深沟槽层的掩模版进行曝光显影,打开所述外侧深度深沟槽结构的形成区域,采用刻蚀工艺刻蚀外侧深度深沟槽;在刻蚀所形成的外侧深度深沟槽区域采用热氧化工艺在沟槽表面形成一层氧化层,采用离子注入工艺注入p型杂质在外侧沟槽下方形成p-区域;在刻蚀所形成的外侧深度深沟槽区域填充二氧化硅或二氧化硅包其他材料构成的绝缘结构,形成深度深沟槽结构;第八步:采用光刻工艺,以p-type层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层,采用离子注入工艺,在p型外延层p-epi表面注入p型半导体杂质形成p型区域p-type,去胶;第九步:采用光刻工艺,以n-well层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层,采用离子注入工艺,在p型外延层p-epi表面注入n型半导体杂质形成n型区域n-well,去胶;第十步:采用光刻工艺,以n-drift层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层,采用离子注入工艺,在p型外延层p-epi表面注入n型半导体杂质形成n型漂移区n-drift,去胶;第十一步:采用光刻工艺,以p-well层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层,采用离子注入工艺,在p型外延层p-epi表面注入p型半导体杂质形成p型区域p-well,去胶;第十二步:采用光刻工艺,以hvpw层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层,采用离子注入工艺,在p型外延层p-epi表面注入p型半导体杂质形成p型区域hvpw,去胶;第十三步:采用热氧化炉管工艺,在p型外延层p-epi表面生长栅极氧化层,栅极氧化层材料为sio2或hfo2;采用cvd工艺,在栅极氧化层上方淀积多晶硅作为栅极;第十四步:采用cvd工艺,在p型外延层p-epi表面淀积绝缘层,绝缘层材料为sio2或sio

2-nitride-sio2,通过刻蚀工艺在栅极两侧形成侧墙;第十五步:采用光刻工艺,以n+层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层,采用离子注入工艺,在p型外延层p-epi表面高浓度浅层注入n型杂质,形成n型源端、n型漏端、n型nbl电极端,去胶;采用光刻工艺,以p+层的掩模版进行曝光显影,在表面留下图形化的光刻胶pr作为阻挡层,采用离子注入工艺,在p型外延层p-epi表面高浓度浅层注入p型杂质,形成p型外延层substrate电极端和p型衬底substrate电极端,去胶;得到双层dti结构的新型的全隔离n型ldmos器件。

10.本发明的一种新型的有双层dti结构的全隔离n型ldmos器件,内侧深沟槽结构取代用于形成横向的三极管的p-drift区域,外侧深度深沟槽结构用于隔离埋层nbl区域。

11.这种全隔离n型ldmos横向的击穿电压一定程度上与内侧深沟槽的宽度有关,相比于传统结隔离结构的ldmos结构拥有更小的面积和更高的击穿电压。高压情况下,具有双层

dti结构的全隔离ldmos器件可以在保证横向击穿电压的条件下大大减少器件的面积,提高集成度,且避免结隔离存在的寄生晶体管开启造成漏电问题。

附图说明

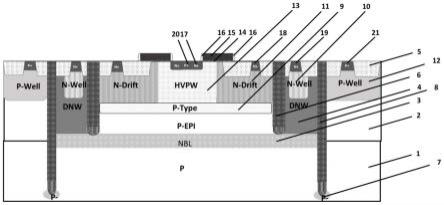

12.图1为本发明的结构示意图;图2为传统设有结隔离结构的全隔离n型ldmos器件的结构示意图;图3为传统全隔离n型ldmos器件中,结隔离结构的击穿电压随p-drift区域宽度的变化折线图;图4为本发明中内侧深沟槽结构6宽度为1um时,dti隔离结构的击穿曲线图;图5为本发明制备流程图。

具体实施方式

13.以下结合附图及实施例对本发明的具体实施方式进行详细描述,以下实施例及附图用于说明本发明,但不用来限制本发明的范围。

14.参阅图1,本发明所述的全隔离n型ldmos器件,其结构是以器件的几何中心横向对称分布,包括p型衬底1;沿p型衬底1向上的外延的p型外延层p-epi 2;设于p型衬底1与p型外延层p-epi 2交界处的重掺杂n型埋层nbl 3;设于外延层p-epi 2顶部表面位置的p型区域hvpw 13,p型区域hvpw 13顶端中部表面设有p型外延层substrate电极端20及对称分布于所述电极端20两侧的n型源端17;对称分布于p型区域hvpw 13两侧的n型漂移区n-drift 11及设于p型区域hvpw 13及n型漂移区n-drift 11底部的p型区域p-type 9;设于n型漂移区n-drift 11表面的n型漏端18;设于p型外延层p-epi 2顶部的栅极15,栅极15与p型外延层p-epi 2之间设有栅极氧化物14,栅极15两侧设有侧墙16;设于n型漂移区n-drift 11外侧、与重掺杂n型埋层nbl 3相连的n型区域dnw4;设于n型区域dnw4表面深浓度的n型区域n-well 10,以及设于n型区域n-well 10表面的n型nbl电极端19;设于n型区域dnw 4和n型漂移区n-drift 11之间、与重掺杂n型埋层nbl 3相连的内侧深沟槽结构6,设于n型区域dnw 4与重掺杂n型埋层nbl 3外侧的深度深沟槽结构8及注入在深度深沟槽结构8底部的p-区域7;设于深度深沟槽结构8外侧的p型区域p-well 12,设于p型区域p-well 12表面顶部的p型衬底substrate电极端21;在p型外延层p-epi 2表面,设有对称于p型区域hvpw 13的浅沟槽隔离结构5。

15.本发明是一种双层dti结构的全隔离n型ldmos器件,整个器件为关于器件几何中心横向对称的两个n型ldmos拼接结构。p型衬底1中形成一个重掺杂n型埋层nbl 3,在p型衬底中形成一个深n阱dnw4和浅n阱n-well 10,用作重掺杂n型埋层nbl 3的引出。n型漂移区n-drift 11作为漂移区主要承担耐压,在n型漂移区n-drift 11中形成重掺杂n型区域形成漏端18。器件中心形成一个p阱hvpw 13,hvpw 13提供n型ldmos的沟道区域,p型区域hvpw 13上形成重掺杂n型区域形成源端17,重掺杂p型区域形成外延层引出的substrate电极端20。

16.在漂移区n-drift 11与p阱hvpw 13下端注入一层比外延层p-epi 2浓度高的p-type区域9,构成全隔离n型ldmos的纵向隔离,防止纵向由于外延层p-epi 2浓度低造成漂移区n-drift 11与埋层nbl 3穿通。

17.器件表面有源区区域通过浅沟槽隔离(sti)结构5进行隔离,sti结构5由绝缘材料sio2形成。表面栅极15跨在sti结构5、n型漂移区n-drift 11和p型区域hvpw 13上,栅极15由金属材料或重掺杂多晶硅构成,栅极氧化物4材料为sio2或hfo2。其中,栅极15跨在sti结构5上的部分充当场板,用来辅助耗尽。

18.本发明设置了双层深沟槽隔离(dti)结构。内侧深沟槽结构6位于n型漂移区n-drift 11与n型区域dnw 4之间,内侧深沟槽结构6用于n型ldmos的横向隔离,其中横向击穿电压(bv)与内侧深沟槽结构6的宽度有关。外侧深度深沟槽结构8用于重掺杂n型埋层nbl 3与外侧硅衬底的隔离,深沟槽结构6与深度深沟槽结构8均由绝缘材料构成,为sio2或sio2包其他材料,外侧深度深沟槽结构8深于埋层nbl 3,内侧深沟槽结构6要保证伸入埋层nbl 3最终区域的1/5~3/5。外侧深度深沟槽结构8下方存在轻掺杂p-区域7,p-区域7可以防止dti底部寄生晶体管的开启。

实施例

19.参阅图1,本实施例的设有双层深沟槽(dti)结构的新型全隔离n型ldmos器件的特点是内侧深沟槽结构6与外侧深度深沟槽结构8是由sio2构成的绝缘结构。本实施例中重掺杂n型埋层nbl 3纵向中间位置距离外延层表面距离约为15um,外侧深度深沟槽结构8深度要深于重掺杂n型埋层nbl 3,深度约为25um,宽度为2um,用于同一片硅片上不同nbl的隔离;内侧深沟槽结构6用来提供全隔离器件的横向隔离,隔离漂移区n-drift 11与n型区域dnw 4,需要保证伸入重掺杂n型埋层nbl 3最终区域1/5~3/5,既保证漂移区n-drift 11和n型区域dnw 4在横向的隔离,也要保证n型区域dnw 4和重掺杂n型埋层nbl 3的连通不被内侧深槽隔断,本实施例中内侧深沟槽结构6宽度为1um,深度约为15um。

20.参阅图2,传统的全隔离n型ldmos器件通过在传统ldmos结构中加入p-drift区域22,使得n-drift区域11、p-drift区域22与dnw4共同构成横向的npn结构,从而对ldmos器件进行横向隔离。与图2传统设有结隔离结构的全隔离n型ldmos器件相比,本发明设有双层dti结构的新型全隔离n型ldmos器件的特点在于,应用内侧深沟槽结构6进行器件的横向隔离,在保证隔离结构的耐压性能的同时可以节省面积。

21.参阅图3,在传统设有结隔离的全隔离ldmos器件中,对用于横向隔离的npn结构耐压性能进行仿真测试。测试方法为:将漏端18扫描0~200v电压,p-drift电极端23与nbl电极端19接0电位。结果显示该npn结构横向耐压与p-drift区域22宽度有关。当p-drift区域22宽度下降至5um时,n-drift区域11、p-drift区域22与dnw4共同构成横向的npn结构的击穿电压降至84v。由于当p-drift区域宽度减小,用于横向隔离的npn结构在发生p-drift区域22与n-drift区域11的结击穿前会先出现n-drift区域11与dnw区域4的穿通现象,从而限制了用于横向隔离的npn结构的耐压特性。

22.图4显示出本发明,即设有双重dti结构的新型全隔离n型ldmos器件,在内侧深沟槽结构6宽度1um时,用于横向隔离的内侧深沟槽结构6的耐压iv曲线。测试方法为:将nbl电极端19接0电位,将漏端18扫描0~200v电压。当内侧深沟槽结构6宽度为1um时,即可满足耐压结构击穿电压达到93v,相比于传统的设有结隔离的n型全隔离ldmos器件,在满足击穿电压的条件下可以节省设计面积。

23.参阅图5,为实现上述器件,本发明采用的制备方法,包括以下步骤:

步骤a:准备轻掺杂的p型半导体材料,所述半导体材料为衬底层1;步骤b:采用光刻工艺,以nbl层的掩模版进行曝光显影,在表面留下图形化的pr(光刻胶)作为阻挡层;采用离子注入工艺,在衬底层1表面注入n型半导体杂质,去胶。

24.步骤c:采用外延工艺,在p型衬底层1表面形成p型外延层2(p-epi),同时通过外延工艺伴随着的热过程,n型杂质扩散形成埋层3(nbl),本实施例中nbl层3纵向中间位置距离外延层表面距离约为15um;步骤d:采用光刻工艺,以dnw层的掩模版进行曝光显影,在表面留下图形化的pr(光刻胶)作为阻挡层;采用离子注入工艺,外延层2表面注入n型半导体杂质,通过推阱工艺使n型杂质扩散形成深n阱4(dnw),去胶;步骤e:采用刻蚀工艺,在外延层2刻蚀浅沟槽,填充氧化物绝缘层sio2,形成浅沟槽隔离(sti)结构5;步骤f:采用刻蚀工艺,在外延层2刻蚀内侧深沟槽,深度约为15um,宽度为1um,填充氧化绝缘层sio2材料形成深沟槽隔离结构6。采用刻蚀工艺,在外延层2与衬底层1刻蚀外侧深沟槽,深度约为25um,宽度为2um,采用离子注入工艺向外侧深沟槽底部注入p型杂质,杂质浓度在3

×

10

15

cm-3

~7

×

10

15

cm-3

之间,形成p-区域7,填充氧化绝缘层sio2形成深沟槽隔离结构8;步骤g:采用光刻工艺,以p-type层的掩模版进行曝光显影,在表面留下图形化的pr(光刻胶)作为阻挡层,采用离子注入工艺,在外延层2表面注入p型半导体杂质形成p-type区域9,去胶;通过重复的光刻与离子注入工艺最终形成p-type区域9、n-well区域10、n-drift区域11、p-well区域12、hvpw区域13;步骤h:采用热氧化炉管工艺,在外延层2表面生长栅极氧化层14,栅极氧化层材料为sio2。采用cvd工艺,在栅极氧化层14上方淀积多晶硅作为栅极15;步骤i:采用cvd工艺,在外延层2表面淀积绝缘层,绝缘层材料为sio

2-nitride-sio2,通过刻蚀工艺在栅极两侧形成侧墙结构16;步骤j:采用光刻工艺,以n+层的掩模版进行曝光显影,在表面留下图形化的pr(光刻胶)作为阻挡层,采用离子注入工艺,在外延层2表面高浓度浅层注入n型杂质,形成源区17、漏区18、nbl引出端19,并对栅极多晶硅进行重掺杂,去胶;采用光刻工艺,以p+层的掩模版进行曝光显影,在表面留下图形化的pr(光刻胶)作为阻挡层,采用离子注入工艺,在外延层2表面注入高浓度浅层注入p型杂质,形成外延层2体电极substrate20和衬底层1体电极substrate21,去胶,得到双层dti结构的新型全隔离n型ldmos器件。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1