一种IGBT芯片及其驱动方法、存储介质

一种igbt芯片及其驱动方法、存储介质

技术领域

1.本发明涉及半导体器件技术领域,尤其涉及一种igbt芯片及其驱动方法、存储介质,igbt芯片是采用了平面与沟槽双独立沟道的双极性器件。

背景技术:

2.近三十年来我国igbt技术飞速发展,从结构简单的平面栅到沟槽栅igbt,再到现有的沟槽平面、精细沟槽、以及复合栅等技术,都在不断优化芯片结构以求达到最好效果。目前尝试突破传统igbt的v

cesat-e

off

之间的权衡关系成为研究的重点,即在降低器件的导通压降的同时,优化关断损耗和通耗的折中关系。

3.平面栅结构的igbt制作工艺简单,耐压性能好,但是由于其沟道区在表面,限制沟道密度导致电导调制效应较弱,导通压降较高。如图1所示,平面栅结构的igbt主要包括:p+集电极层101、n型缓冲层102、n-漂移区103、n阱区104、p阱区105、n+掺杂区106、平面栅极107、栅氧化层108以及金属层109。沟槽栅结构可以消除jfet效应,减小导通压降,但是芯片饱和电流过大,短路能力差,如图2所示,沟槽栅结构的igbt包括p+集电极层201、n型缓冲层202、n-漂移区203、沟槽栅极204、栅氧化层205、n阱区206、p阱区207、n+掺杂区208、隔离层209以及金属层210;有人还提出具有沟槽的平面栅结构的igbt芯片,如图3所示结构,能够结合平面栅和沟槽栅的优点,在平面栅的基础上引入沟槽,沟槽侧面形成载流子积累层,增强了电导调制效应,在不降低击穿电压的前提下,降低器件的通态损耗,主要包括:p+集电极层301、n型缓冲层302、n-漂移区303、n阱区304、p阱区305、n+掺杂区306、沟槽栅极307、栅氧化层308以及金属层309。但是,沟槽的引入增大了栅极和发射极(金属层所在位置为发射极)之间的电容,增加了开关时间,增大开关损耗。

4.为了实现低损耗,近年来一些新型复合栅结构被提出。单沟道结构如专利cn104659088a、cn207097831u和cn104051509b中所提出的,改变多种门极形式,沟槽侧用于载流子积累来降低导通压降,但只有一个沟道。

5.双沟道单门极结构如专利cn108598160b提出的一种融合了平面栅和沟槽栅结构的复合栅芯片,综合了沟槽栅和平面栅的优点。但是与图3所示结构一样具有较大的栅射电容,开关时间几倍于图1、图2所示结构。专利cn108428740b在cn108598160b的结构基础上提出一种具有含虚栅的复合栅结构的igbt芯片,引入虚栅极,优化复合栅的输入和输出电容,优化芯片开通电流的变化率,以及降低开关损耗;但是只有一个门极优化效果有限,并且引入了多个沟槽,大大增加了工艺的复杂度和成本。

技术实现要素:

6.本发明要解决的问题是针对现有igbt芯片开关速度较慢、开关损耗较大的问题,提供一种igbt芯片。

7.为解决上述技术问题,本发明采用的技术方案是:一种igbt芯片,包括元胞,所述元胞由对称设置的两个第一结构拼接而成;

所述第一结构包括n型衬底、间隔设置的第一栅极和第二栅极;所述第一栅极和第二栅极通过氧化层隔开;所述n型衬底上表面开设有沿着n型衬底高度方向向下伸入n型衬底的凹槽,所述第一栅极为设置在n型衬底上的第一栅极,所述第二栅极的至少部分伸入所述凹槽,所述第一栅极和第二栅极之间的氧化层厚度d的取值范围不小于100埃米;所述第一栅极下方设置有第一有源区,所述凹槽的远离第一栅极一侧设置有第二有源区;所述第一有源区、第二有源区均设置于n型衬底上;各个元胞的第一有源区中的第一金属层、第二有源区中的第二金属层相互接触从而形成igbt芯片的发射极;各个元胞的n型衬底相互接触从而形成一体结构。

8.本发明中,通过引出间隔设置的第一栅极和第二栅极,从而在每个第一结构上设置两个独立的可驱动栅极,形成纵横两个方向的双独立沟道,使芯片能够同时施加多个电压驱动,大大增强芯片的电压驱动能力,减小引入沟槽而增大的开关延迟,提高芯片的开关速度,大幅度降低开关损耗。两个门极驱动信号同时作用,可以降低器件开关损耗。

9.上述技术方案中,所述第一有源区包括相邻设置的第一n+掺杂区、第一金属层;所述第一金属层位于第一n+掺杂区的远离第二栅极一侧;所述第一有源区还包括形成在n型衬底中的第一n阱区、位于第一n阱区上的第一p阱区、位于第一p阱区上的第一n+掺杂区和第一金属层,第一p阱区绕设在第一n+掺杂区和第一金属层外侧,第一n阱区绕设在第一p阱区外侧;所述第一n+掺杂区的上端面、第一p阱区的上端面、第一n阱区的上端面均朝向第一栅极设置;所述第二有源区包括在n型衬底高度方向由上到下依次设置的第二n+掺杂区、第二p阱区、第二n阱区,还包括与第二n+掺杂区相邻设置且位于第二p阱区上的第二金属层;所述第二金属层位于第二n+掺杂区的远离第一栅极一侧;所述第二n+掺杂区的壁面、第二p阱区的壁面、第二n阱区的壁面至少形成所述凹槽的远离第一栅极的壁面的部分或全部;在一个元胞中,其中一个第一结构的第二有源区的第二金属层、第二p阱区、第二n阱区与另一个第一结构的第二有源区的第二金属层、第二p阱区、第二n阱区分别对应接触。

10.通过上述设置,从而在第一栅极下方设置第一栅极对应的有源区,在凹槽的远离第一栅极一侧设置对应于第二栅极的有源区。

11.在一种优选实施方式中,所述第二n阱区底面所在的高度位置高于凹槽槽底所在的高度位置。

12.本发明中,通过上述设置,使得n阱区的深度不超过沟槽的深度,避免过早击穿的问题。

13.在一种优选实施方式中,定义第一方向为两个第一结构相互拼接形成元胞的方向,所述第一p阱区上端面在第一方向上的投影尺寸c1与形成所述凹槽的远离第一栅极的壁面的第二p阱区的壁面高度c2相等。

14.本发明中,通过上述设置,使得作为平面栅极的第一栅极的长度c1(开通后形成反型层的长度)与作为沟道栅极的第二栅极的长度c2(开通后形成反型层的长度)相等,从而

可以达到较好的导通状态,有利于降低导通压降。

15.在一种优选实施方式中,所述凹槽深度为6um-8um。

16.申请人在研究时发现,沟槽深度越大,则igbt芯片的导通压降越小,且击穿电压先增大后减小。通过设置凹槽深度的取值范围,不仅可以令igbt芯片的导通压降较小、令击穿电压较大,且可以尽量避免令凹槽深度过深而带来的加工难度问题。

17.在一种优选实施方式中,所述凹槽在第一方向上的尺寸w1取值范围为4um

ꢀ‑

6um,所述第二n阱区在第一方向上的尺寸wd的取值范围为2um

ꢀ‑

4um,第一结构在第一方向上的尺寸为20 um

ꢀ‑

22um。

18.现有技术中,平面栅结构的芯片的半元胞在第一方向上的尺寸为20um-30um居多,凹槽宽度基本在1-3um范围内,相较于平面栅结构,本技术引入凹槽结构,可以实现较小的元胞尺寸,且凹槽宽度加大也便于其深度的加工。

19.申请人在研究时发现,wd越大,则导通压降越大,且击穿电压越小,而第一方向上第一n阱区与凹槽之间的间距wm(即在第一方向上的尺寸)越大,则导通压降越大,且击穿电压越小,通过设置较大的w1值(凹槽宽度)、令元胞在第一方向上的尺寸较小,从而可以设置较小的wd值,且使得wm值可以尽量较小,从而可以到达较小的导通压降、较大的击穿电压。而且,通过设置较大的w1值,即增加沟槽的宽度,能使载流子积累层范围变大,也可以在一定程度上降低导通压降。

20.上述技术方案中,所述第一结构还包括p+集电极层、n型缓冲层,所述p+集电极层、n型缓冲层、n型衬底在n型衬底高度方向由下到上依次设置。

21.上述技术方案中,所述第二栅极与凹槽槽底之间的氧化层厚度大于所述第二栅极与凹槽侧壁之间的氧化层厚度。

22.本发明中,通过上述设置,从而可以降低过早击穿的风险。

23.上述技术方案中,所述第二栅极与凹槽槽底之间的氧化层厚度大于第一栅极与n型衬底之间的氧化层厚度。

24.本发明中,由于因为沟槽底部深入芯片内部,较容易击穿,因此对厚度关系进行上述设置,从而降低击穿风险。

25.本发明还提供一种如上述所述的igbt芯片的驱动方法,所述第一栅极、第二栅极上均施加有驱动电压,且在所述第一栅极上施加的驱动电压与在第二栅极上施加的驱动电压相互独立。

26.通过上述设置,在igbt芯片导通时,在两个栅极上可以均可以施加驱动信号,从而增大了芯片的驱动能力。

27.上述技术方案中:当igbt芯片从关断状态向导通状态转换时,在所述第一栅极、第二栅极上同时施加导通电压;当igbt芯片从导通状态向关断状态转换时,在所述第一栅极、第二栅极上同时施加关断电压。

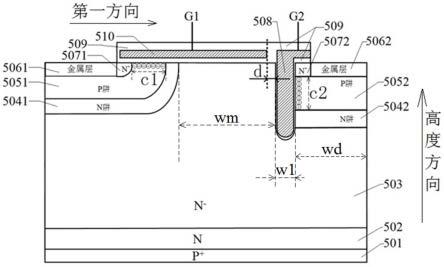

28.本发明中,第一栅极、第二栅极上均施加有驱动电压,两个门极驱动信号同时作用,从而增大了芯片的驱动能力。

29.上述技术方案中:

当igbt芯片从关断状态向导通状态转换时,在所述第一栅极上施加导通电压的时刻比在第二栅极上施加导通电压的时刻早第一预设时间t1。

30.当igbt芯片从导通状态向关断状态转换时,在所述第二栅极上施加关断电压的时刻比在第一栅极上施加关断电压的时刻早第二预设时间t2。

31.本发明中,通过采用上述技术方案,关断时,由于作为沟槽栅极的第二栅极处的栅射电容较大,先使第二栅极关断,关断了一个导电沟道,载流子注入减少,芯片内部载流子减少,从而加快器件的关断进程。

32.优选地,0<t1≤5us,0<t2≤10us。

33.上述技术方案中:当igbt芯片从关断状态向导通状态转换时,在所述第一栅极、第二栅极上同时施加导通电压;当igbt芯片从导通状态向关断状态转换时,在所述第二栅极上施加关断电压的时刻比在第一栅极上施加关断电压的时刻早第三预设时间t3。优选地,0<t3≤10us。

34.本发明中,通过采用上述技术方案,igbt芯片导通时,两个导电沟道同时注入载流子,从而加快开通速度;igbt芯片关断时,门极驱动信号不同,先使第二栅极关断,减小载流子的注入,从而提高关断速度,降低损耗。

35.本发明还提供一种存储介质,所述存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上述所述igbt芯片的驱动方法的步骤。

36.与现有技术相比,本发明可以具有如下优点:1)在本发明中,导通压降低,通态损耗低;解决了折叠型复合栅结构的igbt芯片设计中的一大难题,即由于门极电容增加而引起的开关延时。

37.2)将第一栅极和第二栅极分别独立驱动,形成两个独立的沟道,大大增强芯片的电压驱动能力,从而极大的减小引入沟槽而增大的开关延迟,实现快速开关,两个门极驱动信号同时作用,极大地降低器件开关损耗,由于双极性器件内部的载流子效应远远大于单极性,所以这种设计对于高压大功率的双极性器件尤其重要。

38.3)在本发明中,门极(栅极)施加不同的驱动信号不会对芯片本身产生影响,可以应用多种驱动方法,一是同时驱动,二是分时驱动,三是复合驱动;三种驱动方法都能大幅度降低损耗。对于关断损耗,分时驱动和复合驱动的效果更明显;而复合驱动方式的总损耗最小。

附图说明

39.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

40.图1为现有技术中的具有平面栅结构的igbt芯片的半元胞的剖面示意图;图2为现有技术中的具有沟槽栅结构的igbt芯片的半元胞的剖面示意图;图3为现有技术中具有沟槽的平面栅结构的igbt芯片的半元胞的剖面示意图;图4为本发明实施例1的第一栅极、第二栅极的立体结构示意图;

图5为本发明实施例1的未设置第一栅极、第二栅极的第一结构的立体结构示意图;图6为本发明实施例1的第一结构的纵剖面结构示意图;图7为本发明实施例1的两个第一结构拼接的示意图;图8为本发明实施例1的第一结构的第一金属层、第二金属层相互连接的局部示意图;图9为本发明实施例1中的高压大功率平面与沟槽双独立沟道的igbt芯片与附图中其他结构的关断波形对比;图10为本发明实施例2-4中的驱动电路示意图;图11为本发明实施例2-4中的驱动信号示意图;图12为本发明实施例2-4中的不同方式驱动的关断过程对比波形图;图13为本发明实施例4中的关断延时时间和关断总时长的关系图;图14为本发明实施例3-4中的不同方式驱动的开通过程对比波形图;图15为本发明实施例中的凹槽深度与导通压降、击穿电压的关系曲线示意图;图16为本发明实施例中的wd值与导通压降、击穿电压的关系曲线示意图;图17为本发明实施例中的w1值与导通压降、击穿电压的关系曲线示意图。

具体实施方式

41.下面将结合本技术的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

42.实施例1本发明提供一种igbt芯片,包括元胞,所述元胞由镜像对称设置的两个第一结构(也可称为半元胞)拼接而成。

43.所述第一结构包括n型衬底503、间隔设置的第一栅极510和第二栅极508;所述n型衬底503上表面开设有沿着n型衬底503高度方向向下伸入n型衬底503的凹槽1,所述第一栅极510为设置在n型衬底503上的第一栅极510,所述第二栅极508的至少部分伸入所述凹槽1,所述第一栅极510和第二栅极508通过氧化层509隔开。所述第一栅极510和第二栅极508之间的氧化层厚度d不小于100埃米。d优选为100埃米-200埃米(即第一栅极510与第二栅极508之间用于隔离的氧化层509的厚度为100埃-200埃米);所述第一栅极510下方设置有第一有源区,所述凹槽1的远离第一栅极510一侧设置有第二有源区;所述第一有源区、第二有源区均设置于n型衬底503上;各个元胞的第一有源区中的第一金属层5061、第二有源区中的第二金属层5062相互接触从而形成igbt芯片的发射极;各个元胞的n型衬底503相互接触从而形成一体结构。

44.所述第一有源区包括相邻设置的第一n+掺杂区5071、第一金属层5061;所述第一金属层5061位于第一n+掺杂区5071的远离第二栅极508一侧;所述第一有源区还包括形成在n型衬底503中的第一n阱区5041、位于第一n阱区

5041上的第一p阱区5051、位于第一p阱区5051上的第一n+掺杂区5071和第一金属层5061,第一p阱区5051绕设在第一n+掺杂区5071和第一金属层5061外侧,第一n阱区5041绕设在第一p阱区5051外侧;所述第一n+掺杂区5071的上端面、第一p阱区5051的上端面、第一n阱区5041的上端面均朝向第一栅极510设置。

45.所述第二有源区包括在n型衬底503高度方向由上到下依次设置的第二n+掺杂区5072、第二p阱区5052、第二n阱区5042,还包括与第二n+掺杂区5072相邻设置且位于第二p阱区5052上的第二金属层5062;所述第二金属层5062位于第二n+掺杂区5072的远离第一栅极510一侧;所述第二n+掺杂区5072的壁面、第二p阱区5052的壁面、第二n阱区5042的壁面至少形成所述凹槽1的远离第一栅极510的壁面的部分或全部;在一个元胞中,其中一个第一结构的第二有源区的第二金属层5062、第二p阱区5052、第二n阱区5042与另一个第一结构的第二有源区的第二金属层5062、第二p阱区5052、第二n阱区5042分别对应接触;所述第二n阱区5042底面所在的高度位置高于凹槽1槽底所在的高度位置;定义第一方向为两个第一结构相互拼接形成元胞的方向,所述第一p阱区5051上端面在第一方向上的投影尺寸c1与形成所述凹槽1的远离第一栅极510的壁面的第二p阱区5052的壁面高度c2相等。

46.在第一结构中,第一栅极510的第一金属层5061、第二栅极508的第二金属层5062通过跨接在第一栅极510上方、第二栅极508上方的跨接金属结构5063相互连接。

47.在第一结构中,第一栅极510的第一p阱区5051、第二栅极508的第二p阱区5052互不接触;第一栅极510的第一n阱区5041、第二栅极508的第二n阱区5042互不接触。

48.所述第一结构还包括p+集电极层501、n型缓冲层502,所述p+集电极层501、n型缓冲层502、n型衬底503在n型衬底503高度方向由下到上依次设置。

49.伸入所述凹槽1的第二栅极508的部分与凹槽1槽底之间的氧化层509厚度大于所述第二栅极508的部分与凹槽1侧壁之间的氧化层509厚度。

50.所述第二栅极508与凹槽1槽底之间的氧化层509厚度大于第一栅极510与n型衬底503之间的氧化层509厚度。

51.具体的,本发明提供一种高压大功率平面与沟槽双独立沟道的igbt芯片及其驱动方法。

52.本发明提供的高压大功率igbt芯片,包括n型衬底503和形成于所述衬底表面的若干个并联的元胞,仅以单个元胞为例,所述元胞包括栅极区和位于栅极区两侧的有源区。

53.所述有源区由上到下依次为n+掺杂区、p阱区、n阱区;所述有源区存在于第一栅极510区的下方和第二栅极508区的两侧区域。所述栅极区包括所述衬底表面上的第一栅极510;以及在指定位置向下刻蚀而成的沟槽,所述沟槽内设有第二栅极508;栅极区和n型衬底之间以氧化层隔开,其中第二栅极508底部的氧化层厚度要大于第一栅极510下方的氧化层厚度;所述第一栅极510和第二栅极508的材料均为多晶硅,所述第一栅极510和第二栅极508之间隔开;通过该实施方式,平面和第二栅极508之间电位不会互相影响,能够分别独立驱动。

54.在一种实施方式中,相较于折叠型复合栅结构的igbt,至少可以降低30%的关断损耗。

55.本发明还提供该芯片可应用的驱动方法,两个门极(栅极)可以同时驱动也可以分时驱动甚至是复合驱动,都能够实现降低损耗的效果,尤其采用复合驱动可以最大程度的降低总损耗。

56.在一个实施例中,第二栅极508底部的氧化层厚度要大于第一栅极510下方的氧化层厚度。因为沟槽底部深入芯片内部,较容易击穿,所以设置的要厚一些。

57.第一栅极510有源区的n+掺杂区、p阱区、n阱区的浓度均与第二栅极508有源区域相同。即沟槽栅n阱区=平面栅n阱区浓度;沟槽栅p阱区=平面栅p阱区浓度;沟槽栅n+掺杂区=平面栅n+掺杂区浓度)。这样设置可以减小工艺掺杂复杂度,并且可以使开启电压相接近。并且工艺简单一些。

58.所述p阱区的深度大于n+掺杂区的深度。p阱区包裹n+区域才能形成沟道。

59.优选的,所述n阱区的深度不超过沟槽的深度。如果n阱区超过沟槽的话,会造成过早击穿。

60.第一栅极510和第二栅极508的沟道都处于开通状态,两个通道同时注入载流子,芯片内载流子就比只有一个通道注入的多。将平面和沟槽隔离开就可以达到提到的技术效果,但第一栅极510的长度影响芯片的导通压降这一关键参数,因此在两个栅极510和508互不影响的情况下,尽量使第一栅极510长度长一些。

61.在一个实施例中,所述第二栅极508和第一栅极510各自施加一个栅极驱动。

62.如图6所示,本发明提出的igbt芯片的特征为:硅晶片掺杂p型杂质得到p+集电极衬底501,在p+衬底501的基础上外延n型缓冲层502和n-漂移区503,具体地,在n型衬底上进行注入和刻蚀形成栅极区和有源区。其中,栅极区包括第二栅极508、第一栅极510、栅氧化层509,优选地,第二栅极508底部的栅氧化层509要稍厚于侧壁,从而防止过早击穿。有源区包括沟槽栅有源区和平面栅有源区,有源区均通过相同的工艺步骤实现。其中,第一栅极510的有源区包括从上到下分布的第一n+掺杂区5071、第一p阱区5051、第一n阱区5041,还包括第一金属层5061。第二栅极508的有源区包括从上到下分布的第二n+掺杂区5072、第二p阱区5052、第二n阱区5042,还包括第二金属层5062。具体地,第一栅极510的多晶硅与第二栅极508的多晶硅不相连,在g1和g2端各自施加一个栅极驱动,如图10所示,两个栅极各自配备一个独立的驱动v

gg

和v

gg’。

63.n+掺杂区507、p阱区505、n阱区504位于栅极区两侧且互相接触,具体地,n+掺杂区507在第一栅极510正下方且与金属层506形成欧姆接触,p阱区505与第一栅极510下的栅氧化层509接触且包裹n+掺杂区507,n阱区504与第一栅极510下的栅氧化层509接触且包裹p阱区505;不同的,第二栅极508的掺杂区依次向下分布n+掺杂区507、p阱区505、n阱区504,且都止于沟槽侧壁;其中n阱区504的深度不超过沟槽的深度,如果n阱区超过沟槽的话,会造成过早击穿。n+掺杂区507与金属层506也形成欧姆接触。

64.沟槽掺杂区和平面掺杂区的p阱区505、n阱区504以及n+掺杂区507均注入相同的杂质剂量,从而保证阈值电压近乎相同,并且工艺简单一些。合理设置沟槽掺杂区的p阱区505、n阱区504以及n+掺杂区507的结深,尽量保证平面沟道520和沟槽沟道530长度相同。

65.平面沟道520和沟槽沟道530长度,指的是开通后形成反型层的长度,即图5中第一

栅极510 / 第二栅极508与p阱接触的地方,这样可以达到较好的导通状态,有利于降低导通压降。

66.在一个实施例中,每两个所述单元以镜像对称的方式组成一个元胞。

67.在一个实施例中,所述元胞为六角形元胞结构,并且多个所述元胞以蜂窝状分布在所述n型衬底上;或者,所述元胞为方形元胞结构,并且多个所述元胞矩阵式地分布在所述n型衬底上;或者,所述元胞为条形元胞结构,并且多个所述元胞并排地分布在所述n型衬底上。

68.所述元胞为六角形元胞结构,多个所述元胞呈蜂窝状分布;或所述元胞为方形结构,多个所述元胞呈矩阵式分布;或所述元胞为条形结构,多个所述元胞并排分布。

69.在一个实施例中,所述igbt芯片还包括形成在所述n型衬底背面的背部结构,所述背部结构为穿通型、非穿通型或软穿通型。非穿通型背部结构是集电极p+区,穿通型的背部结构还增加了n—buffer区;而软穿通型就是spt,其区别在于n—buffer区是高斯掺杂(即浓度依次减小)图9是本发明实施例中的高压大功率平面与沟槽双独立沟道的igbt芯片与附图中其他结构的关断波形,其中610为本发明提出结构的关断电压波形,611为关断电流波形;620为图1所示平面栅结构的关断电压波形,621为其关断电流波形;630为专利cn108598160b中的折叠型复合栅结构的关断电压波形,631为其关断电流波形;640为图3所示具有沟槽的平面栅结构的关断电压波形,641为其关断电流波形。如图9中所示波形图,使第一栅极510和第二栅极508分别独立驱动,大大加快了器件的开关进程,减小了折叠型复合栅结构由于引入沟槽而增大的开关延时,开关损耗大幅度降低。

70.实施例2如图11所示,本发明还提供一种如上述所述的igbt芯片的驱动方法,所述第一栅极510、第二栅极508上均施加有驱动电压,在所述第一栅极510上施加的驱动电压与在第二栅极508上施加的驱动电压相互独立。

71.即,电路中,每个igbt的两个栅极分别接两个信号,分别驱动第二栅极508、第一栅极510。

72.本发明提供的压大功率平面与沟槽双独立沟道igbt芯片的驱动方法,其特征在于,在一个实施方式中,采用同时驱动,即控制两个栅极开通和关断的驱动信号完全相同;在第一栅极510和第二栅极508同时接入上升沿或下降沿,第一栅极510、第二栅极508时间一致、关断一致,增大了芯片的驱动能力。

73.本实施例中,当igbt芯片从关断状态向导通状态转换时,在所述第一栅极510、第二栅极508上同时施加导通电压;当igbt芯片从导通状态向关断状态转换时,在所述第一栅极510、第二栅极508上同时施加关断电压。

74.本发明还提供一种存储介质,所述存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上述所述igbt芯片的驱动方法的步骤。

75.在该实施例中,同时驱动方式如图11中100所示,第一栅极510和第二栅极508施加的门极驱动信号正负电压的跳变的时刻801和802相同,两个栅极同时被施加阈值以上的电

压,能够同时开启或同时关断。

76.实施例3本实施例3与实施例2的区别在于,igbt芯片从关断状态向导通状态转换时以及从导通状态向关断状态转换时,在第一栅极510上施加电压、在第二栅极上施加电压的先后顺序有差别。

77.本实施例中,当igbt芯片从关断状态向导通状态转换时,在所述第一栅极510上施加导通电压的时刻比在第二栅极508上施加导通电压的时刻早第一预设时间t1;本实施例中,当igbt芯片从导通状态向关断状态转换时,在所述第二栅极508上施加关断电压的时刻比在第一栅极510上施加关断电压的时刻早第二预设时间t2。

78.优选地,t1≤5us,t2≤10us。

79.在该实施方式中,采用分时驱动,即控制两个栅极开通和关断的驱动信号存在差异性;开通和关断过程中,正负电压的跳变的时刻都不同,关断时,由于第二栅极508处的栅射电容较大,先使第二栅极508关断,关断了一个导电沟道,载流子注入减少,芯片内部载流子减少,从而加快器件的关断进程。

80.在一个实施方式中,图11中200所示为分时驱动信号示意图,两个栅极被施加不同的驱动电压,具体地,开通时,第一栅极510先被施加开通信号803,第二栅极508的开通信号延时t1,延时开通可以降低电流过充和集电极电流上升率,增强芯片开通过程中的稳定性,但开通损耗略有增加;关断时,第二栅极508先被施加关断信号804,而第一栅极510的关断信号有一个时长为t2的延时,一个栅极提前关断可以使芯片内部载流子浓度减小,使关断过程中抽取载流子的时间缩短,从而大幅度减小关断损耗,总开关损耗减小。

81.实施例4本实施例4与实施例2的区别在于,igbt芯片从导通状态向关断状态转换时,在第一栅极510上施加电压、在第二栅极上施加电压的先后顺序有差别。

82.本实施例中,当igbt芯片从关断状态向导通状态转换时,在所述第一栅极510、第二栅极508上同时施加导通电压;当igbt芯片从导通状态向关断状态转换时,在所述第二栅极508上施加关断电压的时刻比在第一栅极(510)上施加关断电压的时刻早第三预设时间t3。

83.优选地,t3≤10us。

84.在该实施例中,采用同时驱动和分时驱动结合的复合驱动方式,其特征主要是开通时,两个门极(栅极)驱动信号完全一致,同时开通,两个导电沟道同时注入载流子,加快开通速度,关断时,门极驱动信号不同,先使第二栅极508关断,减小载流子的注入,提高关断速度,降低损耗。

85.在一个实施例中,图11中300所示为复合驱动信号示意图,复合驱动的开通过程与同时驱动方式相同,关断过程与分时驱动方式相同。即在开通过程,两个栅极被施加相同的驱动信号,第一栅极510和第二栅极508在开通信号805处,同时被施加正跳变,由于开通前芯片内部载流子浓度较低,因此双沟道同时注入载流子会加快开通速度,这样的控制方式,与分时驱动相比,开通损耗更小;在关断时,同样地,第二栅极508先被施加关断信号806,而第一栅极510的关断信号有一个时长为t3的延时;沟槽侧沟道的关断使注入到芯片内部的载流子减小,大大降低芯片内的载流子浓度,提高了关断速度。

86.上述实施例中描述的驱动方式对影响关断过程的效果如图12所示,其中920为本发明提出的结构采用同时驱动方法的集电极电压波形,921为其对应的集电极电流波形;910为本发明提出的结构采用分时驱动方法的集电极电压波形,911为其对应的集电极电流波形;作为对比,930为专利cn108598160b中的结构的集电极电压波形,931为其对应的集电极电流波形;可以看出,相比于折叠型复合栅igbt芯片,本技术的方案大大减小了关断延时,并且采用分时驱动方法200的实施例关断速度比采用同时驱动方法100更快,关断损耗也最小。

87.图13为在关断时第二栅极相对于第一栅极的关断延时时间t2和关断总时长的关系图,其中t

off

表示关断所需时间,体现t2的长短对关断时间的影响,具体的,采用分时驱动的器件的关断时间1002(即栅极比栅极提前10s关断)比同时驱动的1001(即第一栅极、第二栅极同时关断)短一些,随着延时时间的增加,关断总时长不断减小,直到10μs以后,趋于不变,最大缩短时间大概1μs,但是这对于高压大功率芯片来说,损耗大大降低。

88.图14为采用分时驱动方式200和复合驱动方式300的芯片开通波形对比图,1101为采用复合驱动方式的集电极电压波形,1103为其对应的集电极电流波形;1102为采用分时驱动方式的集电极电压波形,1104为其对应的集电极电流波形。如图14中所示,采用复合驱动方式300,即两个门极同时开通的开通速度比采用分时驱动200要快,由于开通前芯片内部载流子浓度较低,因此双沟道同时注入载流子会加快开通速度,损耗也更小。

89.与原有技术相比,本发明提出了独立的可驱动的第一栅极510和第二栅极508,形成纵横两个方向的双独立沟道,并增加了门极驱动,以实现所述功能,在不增加工艺复杂度的同时保留最优效果;并且对于此芯片,提出了三种可应用的驱动方法,其中复合驱动方法能够大大降低器件的损耗。

90.实施例5本实施例中,进一步地,令所述凹槽深度为6um-8um。

91.如图15所示,申请人在研究时发现,沟槽深度约大,则igbt芯片的导通压降越小,且击穿电压越先增大后减小。通过设置凹槽深度的取值范围,不仅可以令igbt芯片的导通压降较小(从而降低功耗)、令击穿电压较大,且可以尽量避免令凹槽深度过深而带来的加工难度问题。

92.实施例6本实施例中,进一步地,令:所述凹槽在第一方向上的尺寸w1取值范围为4um

ꢀ‑

6um,所述第二n阱区在第一方向上的尺寸wd的取值范围为2um

ꢀ‑

4um,所述第一结构(半元胞)在第一方向上的尺寸为20 um

ꢀ‑

22um。

93.如图16、图17所示,申请人在研究时发现,wd越大,则导通压降越大,且击穿电压越小,而第一方向上第一n阱区与凹槽之间的间距wm(即在第一方向上的尺寸)越大,则导通压降越大,且击穿电压越小,通过设置较大的w1值(凹槽宽度)、设置较小的半元胞宽度(即在第一方向上的尺寸),使得wd可以取较小的值,且使得wm值可以尽量较小,从而可以到达较小的导通压降、较大的击穿电压。而且,增加沟槽的宽度能使载流子积累层范围变大,可以一定程度上降低导通压降。wd可取2-4um,同时沟槽宽度w1取4-6um,这样既可以实现较高耐压的同时,保持较小的导通压降。

94.本实施例中设置各个尺寸范围对igbt芯片的开关延时、开关损耗影响较小。

95.需要说明的是,本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

96.以上对本发明的实施例进行了详细说明,但所述内容仅为本发明的较佳实施例,不能被认为用于限定本发明的实施范围。凡依本发明范围所作的均等变化与改进等,均应仍归属于本专利涵盖范围之内。在阅读了本发明之后,本领域技术人员对本发明的各种等价形式的修改均落入本技术所附权利要求所限定的范围。在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1