显示基板和显示装置的制作方法

1.本公开的实施例涉及一种显示基板和显示装置。

背景技术:

2.随着显示技术的不断发展,微型有机发光二极管(micro organic light-emitting diode,简称micro-oled)显示装置是一种以硅基板为衬底的新型oled显示装置,又叫做硅基有机发光二极管(简称硅基oled)显示装置。硅基oled显示装置具有体积小、分辨率高等优点,其采用cmos集成电路工艺制备,可以实现像素的有源寻址,并且可以在硅基衬底上制备包括tcon(时序控制)电路、ocp(操作控制)电路等多种功能电路,可以实现轻量化。

3.微型oled(micro oled)显示器具有优秀的显示特性,例如分辨率高、亮度高、色彩丰富、驱动电压低、响应速度快、功耗低等,具有广阔的发展前景。

技术实现要素:

4.本公开实施例提供一种显示基板和显示装置。该显示基板包括驱动基板、阳极层、像素限定层、发光功能层、阴极层和封装层;驱动基板包括衬底和驱动电路;阳极层位于驱动基板上;像素限定层位于阳极层远离驱动基板的一侧;发光功能层位于阳极层远离驱动基板的一侧;阴极层位于发光功能层远离驱动基板的一侧;封装层位于阴极层远离驱动基板的一侧;驱动电路包括至少一个晶体管,晶体管包括半导体层,半导体层至少部分位于衬底内部;阳极层包括多个阳极,显示基板包括多个像素开口,多个像素开口位于像素限定层之中,且位于多个阳极远离驱动基板的一侧,多个像素开口被配置为与多个阳极至少存在交叠;各阳极包括主体部和凸起部,凸起部设置在主体部的周边,凸起部在垂直于驱动基板的方向上的尺寸大于主体部在垂直于驱动基板的方向上的尺寸,发光功能层包括多个发光部,多个发光部位于多个像素开口之内,且与多个阳极的所述主体部接触设置。由此,该显示基板可有效地避免相邻子像素之间的漏电和串扰。

5.本公开至少一个实施例提供一种显示基板,其包括:驱动基板,包括衬底和驱动电路;第一平坦层,位于所述驱动电路上;阳极层,位于所述第一平坦层远离所述驱动基板的一侧;像素限定层,位于所述阳极层远离所述驱动基板的一侧;发光功能层,位于所述阳极层远离所述驱动基板的一侧;阴极层,位于所述发光功能层远离所述驱动基板的一侧;以及封装层,位于所述阴极层远离所述驱动基板的一侧;所述驱动电路包括至少一个晶体管,所述晶体管包括半导体层,所述半导体层至少部分位于所述衬底内部,所述阳极层包括多个阳极,所述显示基板包括多个像素开口,且位于所述多个阳极远离所述驱动基板的一侧,所述多个像素开口被配置为与所述多个阳极至少存在交叠;各所述阳极包括主体部和凸起部,所述凸起部与所述主体部相连,所述凸起部第一方向上的尺寸大于所述主体部在所述第一方向上的尺寸,所述发光功能层包括多个发光部,所述多个发光部与所述多个阳极的所述主体部接触设置,所述主体部所在位置处的所述第一平坦层远离所述衬底的表面与所

述衬底的距离与所述凸起部所在位置处的所述第一平坦层远离所述衬底的表面与所述衬底的距离相等,所述主体部远离所述衬底的表面与所述第一平坦层远离所述衬底的表面的距离大于所述凸起部远离所述衬底的表面与所述第一平坦层远离所述衬底的表面的距离。

6.例如,在本公开一实施例提供的一种显示基板中,所述凸起部设置在所述主体部的周边。

7.例如,在本公开一实施例提供的一种显示基板中,所述像素限定层在所述驱动基板上的正投影与所述凸起部在所述驱动基板上的正投影交叠。

8.例如,在本公开一实施例提供的一种显示基板中,所述像素限定层包括像素限定部,所述像素限定部包括:像素限定平坦部,位于相邻的两个所述阳极之间;以及突起结构,分别位于相邻两个所述阳极的所述凸起部远离所述驱动基板的一侧,所述像素限定平坦部将所述突起结构相连。

9.例如,在本公开一实施例提供的一种显示基板中,所述像素限定部关于所述相邻两个所述阳极之间的间隔区的中心呈对称设置。

10.例如,在本公开一实施例提供的一种显示基板中,各所述突起结构包括:第一侧壁,位于所述突起结构靠近所述主体部的中心的一侧;以及第二侧壁,与所述第一侧壁相连,所述第二侧壁相对于所述第一侧壁,更远离所述驱动基板;所述第一侧壁的坡度角大于所述第二侧壁的坡度角。

11.例如,在本公开一实施例提供的一种显示基板中,所述第一侧壁的坡度角的取值范围为75-89度,所述第二侧壁的坡度角的取值范围为15-45度。

12.例如,在本公开一实施例提供的一种显示基板中,各所述突起结构还包括:第三侧壁,位于所述突起结构靠近所述像素限定平坦部的一侧,其中,所述第三侧壁的坡度角大于所述第二侧壁的坡度角,且小于所述第一侧壁的坡度角。

13.例如,在本公开一实施例提供的一种显示基板中,各所述突起结构还包括:第三侧壁,位于所述突起结构靠近所述像素限定平坦部的一侧,所述第一侧壁的坡度角为α,所述第二侧壁的坡度角为β,所述第三侧壁的坡度角为γ,并满足下列公式:β《γ《α。

14.例如,在本公开一实施例提供的一种显示基板中,所述第一侧壁的坡度角与所述第二侧壁的坡度角的差值等于所述第三侧壁的坡度角的i倍,i的取值范围为0.8

ꢀ‑ꢀ

1.2。

15.例如,在本公开一实施例提供的一种显示基板中,所述第一侧壁的坡度角α,所述第二侧壁的坡度角β,所述第三侧壁的坡度角γ满足下列公式:(α-β)=i*γ, i的取值范围为0.8

ꢀ‑ꢀ

1.2。

16.例如,在本公开一实施例提供的一种显示基板中,所述第一侧壁的坡度角与所述第二侧壁的坡度角的差值等于所述第二侧壁的坡度角与第三侧壁的坡度角的差值的j倍,j的取值范围为1.5-3。

17.例如,在本公开一实施例提供的一种显示基板中,所述第一侧壁的坡度角α,所述第二侧壁的坡度角β,所述第三侧壁的坡度角γ满足下列公式:(α-β)=j*(γ-β),j的取值范围为1.5-3。

18.例如,在本公开一实施例提供的一种显示基板中,所述第一侧壁的坡度角与所述第二侧壁的坡度角之和等于所述第三侧壁的坡度角的k倍,k的取值范围为2

ꢀ‑ꢀ

3。

19.例如,在本公开一实施例提供的一种显示基板中,所述第三侧壁的坡度角的取值

范围为45-60度。

20.例如,在本公开一实施例提供的一种显示基板中,所述第三侧壁在所述驱动基板上的正投影在第二方向上的尺寸大于所述第二侧壁在所述驱动基板上的正投影在所述第二方向上的尺寸,所述第二侧壁在所述驱动基板上的正投影在第二方向上的尺寸大于所述第一侧壁在所述驱动基板上的正投影在所述第二方向上的尺寸,所述第二方向为从所述凸起部到所述主体部的方向或从所述主体部到所述凸起部的方向,所述第二方向平行于所述驱动基板远离所述阳极层的表面。

21.例如,在本公开一实施例提供的一种显示基板中,所述第一侧壁在所述第一方向上的尺寸为h1,所述第二侧壁在所述第一方向上的尺寸为h2,所述第三侧壁在所述第一方向上的尺寸为h3,h1、h2和h3满足下列公式:h3*cosγ 》 h2*cosβ 》 h1*cosα。

22.例如,在本公开一实施例提供的一种显示基板中,各所述阳极的所述凸起部包括第四侧壁,位于所述凸起部靠近所述主体部的中心的一侧,所述第四侧壁的坡度角大于所述第二侧壁的坡度角,且小于所述第一侧壁的坡度角。

23.例如,在本公开一实施例提供的一种显示基板中,各所述阳极的所述凸起部包括第四侧壁,位于所述凸起部靠近所述主体部的中心的一侧,所述第四侧壁的坡度角为δ,且满足以下公式:β《δ《α。

24.例如,在本公开一实施例提供的一种显示基板中,各所述阳极的所述凸起部包括:第一子阳极层,位于所述驱动电路远离所述衬底的一侧;第二子阳极层,位于所述第一子阳极层远离所述驱动基板的一侧;以及第三子阳极层,位于所述第二子阳极层远离所述驱动基板的一侧。

25.例如,在本公开一实施例提供的一种显示基板中,所述第一子阳极层在第二方向上的尺寸大于所述第三子阳极层在所述第二方向上的尺寸,所述第三子阳极层在所述第二方向上的尺寸大于所述第二子阳极层在所述第二方向上的尺寸,所述第二方向为从所述凸起部到所述主体部的方向或从所述主体部到所述凸起部的方向,所述第二方向平行于所述驱动基板远离所述阳极层的表面。

26.例如,在本公开一实施例提供的一种显示基板中,所述第一子阳极层远离所述主体部的一端包括隆起部,所述隆起部在所述第一方向上的厚度大于所述第一子阳极层在所述第一方向上的平均厚度。

27.例如,在本公开一实施例提供的一种显示基板中,所述第三子阳极层远离所述主体部的一端向靠近所述第一子阳极层的方向弯曲。

28.例如,在本公开一实施例提供的一种显示基板中,各所述阳极的所述凸起部还包括:第四子阳极层,位于所述第二子阳极层和第三子阳极层之间,所述第四子阳极层在所述第二方向上的尺寸小于所述第二子阳极层在所述第二方向上的尺寸。

29.例如,在本公开一实施例提供的一种显示基板中,所述第三子阳极层在所述第二方向上超出所述第四子阳极层的尺寸小于所述像素限定层在所述驱动基板上的正投影与所述凸起部在所述驱动基板上的正投影的交叠区域在所述第二方向上的尺寸。

30.例如,在本公开一实施例提供的一种显示基板中,所述第二子阳极层包括第五侧壁,位于所述第二子阳极层远离所述主体部的一侧,所述第四子阳极层包括第六侧壁,位于

所述第四子阳极层远离所述主体部的一侧,所述第五侧壁的坡度角大于所述第四侧壁的坡度角,所述第六侧壁的坡度角大于所述第四侧壁的坡度角,所述第五侧壁的坡度角大于所述第六侧壁的坡度角。

31.例如,在本公开一实施例提供的一种显示基板中,所述第一子阳极层在所述第一方向上的厚度与所述第二子阳极层在所述第一方向上的厚度之比的范围在1/15-1/5。

32.例如,在本公开一实施例提供的一种显示基板中,所述第一子阳极层在所述第一方向上的厚度与所述第三子阳极层在所述第一方向上的厚度之比的范围在1/3-4/5。

33.例如,在本公开一实施例提供的一种显示基板中,所述第一子阳极层在所述第一方向上的厚度与所述第四子阳极层在所述第一方向上的厚度之比的范围在1/24-1/8。

34.例如,在本公开一实施例提供的一种显示基板中,相邻两个所述阳极之间的距离与所述阳极的凸起部在所述驱动基板上的正投影的长度之比的范围为2

ꢀ‑ꢀ

4。

35.例如,在本公开一实施例提供的一种显示基板中,相邻两个所述阳极之间的距离与所述阳极的凸起部在所述驱动基板上的正投影的长度之比的范围为2.5

ꢀ‑ꢀ

3.5。

36.例如,在本公开一实施例提供的一种显示基板中,所述凸起部围绕所述主体部设置。

37.例如,在本公开一实施例提供的一种显示基板中,所述阳极在所述驱动基板上的正投影的形状包括六边形。

38.例如,本公开一实施例提供的一种显示基板还包括:反射电极层,位于所述第一平坦层靠近所述阳极层的一侧;以及第二平坦层,位于所述反射电极层靠近所述阳极层的一侧。

39.例如,在本公开一实施例提供的一种显示基板中,所述反射电极层在所述像素开口中连续设置。

40.例如,在本公开一实施例提供的一种显示基板中,所述发光功能层与所述主体部之间存在第一孔隙,所述发光功能层与所述像素限定层之间存在至少一个第二孔隙,所述第一孔隙占据的空间大于所述第二孔隙占据的空间。

41.例如,在本公开一实施例提供的一种显示基板中,所述封装层包括:无机封装层,位于所述阴极层远离所述驱动基板的一侧,所述无机封装层包括多个子无机封装层。

42.例如,在本公开一实施例提供的一种显示基板中,所述多个子无机封装层之中至少存在两个相邻的采用不同的材料制作的子无机封装层,所述多个子无机封装层中至少存在两个相邻的采用相同的材料制作的子无机封装层。

43.例如,在本公开一实施例提供的一种显示基板中,在远离所述驱动基板的方向上,所述多个子无机封装层的折射率先增大后减小。

44.例如,在本公开一实施例提供的一种显示基板中,在远离所述驱动基板的方向上,所述多个子无机封装层在所述第一方向上的厚度逐渐减小。

45.例如,在本公开一实施例提供的一种显示基板中,各所述子无机封装层包括:交替设置的平坦区和双拱间隔区、位于所述平坦区远离所述双拱间隔区的一侧的第一拱形区、位于所述平坦区和所述双拱间隔区之间的第二拱形区、以及位于所述平坦区远离所述第二拱形区的第三拱形区,所述第一拱形区和所述第二拱形区关于所述平坦区的中心对称设置。

46.例如,在本公开一实施例提供的一种显示基板中,所述平坦区在第二方向上的尺寸为l,所述第二拱形区的中心和所述第三拱形区的中心在所述第二方向上的距离为第一距离d1,所述第一拱形区的中心和所述第二拱形区的中心在所述第二方向上的距离为第二距离d2,所述第一拱形区、所述第二拱形区和所述第三拱形区的曲率半径均为r,所述第一距离d1满足以下公式:d2 ≤ (l+d1) 《

ꢀꢀ

(l+r),所述第二方向为从所述凸起部到所述主体部的方向或从所述主体部到所述凸起部的方向,所述第二方向平行于所述驱动基板远离所述阳极层的表面。

47.例如,在本公开一实施例提供的一种显示基板中,所述平坦区在第二方向上的尺寸为l,所述第二拱形区的中心和所述第三拱形区的中心在所述第二方向上的距离为第一距离d1,所述第一拱形区的中心和所述第二拱形区的中心在所述第二方向上的距离为第二距离d2,所述第一拱形区、所述第二拱形区和所述第三拱形区的曲率半径均为r,所述第一距离d1满足以下公式:(l+d1) ≤ d2 《 (l+r),所述第二方向为从所述凸起部到所述主体部的方向或从所述主体部到所述凸起部的方向,所述第二方向平行于所述驱动基板远离所述阳极层的表面。

48.例如,在本公开一实施例提供的一种显示基板中,所述第一拱形区、所述第二拱形区或所述第三拱形区在所述驱动基板上的正投影与所述凸起部在所述驱动基板上的正投影交叠,所述平坦区在所述驱动基板上的正投影与所述主体部在所述驱动基板上的正投影交叠,所述第一拱形区、所述第二拱形区或所述第三拱形区远离所述驱动基板的表面与所述驱动基板之间的距离大于所述平坦区远离所述驱动基板的表面与所述驱动基板之间的距离。

49.例如,在本公开一实施例提供的一种显示基板中,所述双拱间隔区在所述驱动基板上的正投影与相邻两个所述阳极之间的间隔区在所述驱动基板上的正投影交叠。

50.例如,在本公开一实施例提供的一种显示基板中,所述多个子无机封装层包括:第一子无机封装层,位于所述阴极层远离所述驱动基板的一侧;第二子无机封装层,位于所述第一子无机封装层远离所述驱动基板的一侧;第三子无机封装层,位于所述第二子无机封装层远离所述驱动基板的一侧;以及第四子无机封装层,位于所述第三子无机封装层远离所述驱动基板的一侧。

51.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层的折射率小于所述第二子无机封装层的折射率,所述第四子无机封装层的折射率小于所述第三子无机封装层的折射率。

52.例如,在本公开一实施例提供的一种显示基板中,所述第二子无机封装层的折射率与所述第三子无机封装层的折射率相等。

53.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层的所述平坦区在所述第二方向上具有第一宽度,所述第二子无机封装层的所述平坦区在所述第二方向上具有第二宽度,所述第三子无机封装层的所述平坦区在所述第二方向上具有第三宽度,所述第四子无机封装层的所述平坦区在所述第二方向上具有第四宽度,所述第一宽度大于所述第二宽度,所述第二宽度大于所述第三宽度,所述第三宽度大于所述第四宽度。

54.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层的所述平坦区靠近所述第一拱形区的边缘、所述第二子无机封装层的所述平坦区靠近所述第一拱形区的边缘、所述第三子无机封装层的所述平坦区靠近所述第一拱形区的边缘和所述第四子无机封装层的所述平坦区靠近所述第一拱形区的边缘的第一连线与所述驱动基板远离所述阳极层的表面之间的夹角为第一夹角,所述第一子无机封装层的所述第一拱形区的顶点、所述第二子无机封装层的所述第一拱形区的顶点、所述第三子无机封装层的所述第一拱形区的顶点和所述第四子无机封装层的所述第一拱形区的顶点的第二连线与所述驱动基板远离所述阳极层的表面之间的夹角为第二夹角,所述第一夹角小于所述第二夹角。

55.例如,在本公开一实施例提供的一种显示基板中,所述第一夹角的范围为60-85度,所述第二夹角的范围为85-89度。

56.例如,在本公开一实施例提供的一种显示基板中,所述第一连线和所述第二连线的交点位于所述驱动基板之内。

57.例如,在本公开一实施例提供的一种显示基板中,所述驱动电路包括:半导体层,位于所述衬底之中;第一导电层,位于所述半导体层上;第二导电层,位于所述第一导电层远离所述衬底的一侧;第三导电层,位于所述第二导电层远离所述衬底的一侧;以及第四导电层,位于所述第三导电层远离所述衬底的一侧。

58.例如,在本公开一实施例提供的一种显示基板中,所述第一连线和所述第二连线的交点位于所述第三导电层远离所述衬底的上表面与所述阳极层之间。

59.例如,在本公开一实施例提供的一种显示基板中,所述第一连线与所述第二连线的交点与所述像素限定层的所述突起结构远离所述衬底的上表面的顶点之间距离大于所述第一子无机封装层在所述第一方向上的厚度。

60.例如,在本公开一实施例提供的一种显示基板中,所述第一连线与所述第二连线的交点与所述像素限定层的所述突起结构远离所述衬底的上表面的顶点之间距离小于所述第一子无机封装层在所述第一方向上的厚度和所述第二子无机封装层在所述第一方向上的厚度之和。

61.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层的所述第二拱形区靠近所述双拱间隔区的边缘、所述第二子无机封装层的所述第二拱形区靠近所述双拱间隔区的边缘、所述第三子无机封装层的所述第二拱形区靠近所述双拱间隔区的边缘和所述第四子无机封装层的所述第二拱形区靠近所述双拱间隔区的边缘的第三连线与所述驱动基板远离所述阳极层的表面之间的夹角为第三夹角,所述第三夹角小于所述第二夹角。

62.例如,在本公开一实施例提供的一种显示基板中,所述第一连线和所述三连线的交点位于所述第二导电层远离所述衬底的上表面与所述第三导电层靠近所述衬底的下表面之间。

63.例如,在本公开一实施例提供的一种显示基板中,所述第二连线和所述第三连线的交点位于所述第一导电层靠近所述衬底的下表面与所述衬底远离所述第一导电层的下表面之间。

64.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层的所述第三拱形区远离所述双拱间隔区的边缘、所述第二子无机封装层的所述第三拱形区远离所

述双拱间隔区的边缘、所述第三子无机封装层的所述第三拱形区远离所述双拱间隔区的边缘和所述第四子无机封装层的所述第三拱形区远离所述双拱间隔区的边缘的第四连线与所述驱动基板远离所述阳极层的表面之间的夹角为第四夹角,所述第四夹角小于所述第二夹角。

65.例如,在本公开一实施例提供的一种显示基板中,所述第一连线与所述第四连线的交点位于所述衬底远离所述第一导电层的一侧。

66.例如,在本公开一实施例提供的一种显示基板中,所述第三连线与所述第四连线的交点位于所述第二导电层远离所述衬底的上表面与所述第三导电层靠近所述衬底的下表面之间。

67.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层的所述第一拱形区远离所述衬底的上表面具有第一曲率半径,所述第二子无机封装层的所述第一拱形区远离所述衬底的上表面具有第二曲率半径,所述第三子无机封装层的所述第一拱形区远离所述衬底的上表面具有第三曲率半径,所述第四子无机封装层的所述第一拱形区远离所述衬底的上表面具有第四曲率半径,所述第一曲率半径小于所述第二曲率半径,所述第二曲率半径小于所述第三曲率半径,所述第三曲率半径小于所述第四曲率半径。

68.例如,在本公开一实施例提供的一种显示基板中,所述第四子无机封装层的所述第一拱形区的虚设圆心位于所述第一子无机封装层远离所述衬底的上表面和所述第四子无机封装层靠近所述衬底的下表面之间。

69.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层在所述第一方向上具有第一厚度,所述第二子无机封装层在所述第一方向上具有第二厚度,所述第三子无机封装层在所述第一方向上具有第三厚度,所述第四子无机封装层在所述第一方向上具有第四厚度,所述第一厚度大于所述第二厚度,所述第二厚度大于所述第三厚度,所述第三厚度大于所述第四厚度。

70.例如,在本公开一实施例提供的一种显示基板中,所述第一厚度与所述第二厚度的差值和所述第三厚度与所述第四厚度的差值的比例范围为1.5-2倍。

71.例如,在本公开一实施例提供的一种显示基板中,所述第二厚度和所述第三厚度之和与所述第一厚度的比例范围为0.8

ꢀ‑ꢀ

1.2。

72.例如,在本公开一实施例提供的一种显示基板中,所述第一厚度的范围为1000-1200纳米,所述第二厚度的范围为500-660纳米,所述第三厚度的范围480-560纳米,所述第四厚度的范围为180-260纳米。

73.例如,在本公开一实施例提供的一种显示基板中,所述第一子无机封装层的材料包括氧化硅和氮氧化硅,所述第二子无机封装层的材料包括氮化硅,所述第三子无机封装层的材料包括氮化硅,所述第四子无机封装层的材料包括氧化硅。

74.例如,在本公开一实施例提供的一种显示基板中,所述封装层还包括:有机封装层,位于所述无机封装层远离所述驱动基板的一侧,所述有机封装层包括第一区域、第二区域和第三区域,所述第一区域的平均厚度小于所述第二区域的平均厚度,所述第二区域的平均厚度小于所述第三区域的平均厚度。

75.例如,本公开一实施例提供的一种显示基板还包括:彩膜层,位于所述封装层远离所述驱动基板的一侧,所述彩膜层包括第一彩色滤光片、第二彩色滤光片和第三彩色滤光

片。

76.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片和所述第二彩色滤光片存在第一交叠区,所述第二彩色滤光片和所述第三彩色滤光片存在第二交叠区,所述第三彩色滤光片和所述第一彩色滤光片存在第三交叠区。

77.例如,在本公开一实施例提供的一种显示基板中,所述第一交叠区、所述第二交叠区和所述第三交叠区在所述驱动基板上的正投影与所述凸起部在所述驱动基板上的正投影交叠。

78.例如,在本公开一实施例提供的一种显示基板中,所述第一交叠区、所述第二交叠区和所述第三交叠区在所述驱动基板上的正投影与相邻两个所述阳极之间的间隔区在所述驱动基板上的正投影交叠。

79.例如,在本公开一实施例提供的一种显示基板中,所述第一交叠区在所述第二方向上的尺寸大于所述第二交叠区在所述第二方向上的尺寸,所述第二交叠区在所述第二方向上的尺寸大于所述第三交叠区在所述第二方向上的尺寸。

80.例如,在本公开一实施例提供的一种显示基板中,所述第一交叠区在所述第二方向上的尺寸范围为400-600纳米,所述第二交叠区在所述第二方向上的尺寸范围为250-350纳米,所述第三交叠区在所述第二方向上的尺寸范围为100-200纳米。

81.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片在所述第一方向上的平均尺寸大于所述第二彩色滤光片在所述第一方向上的平均尺寸,且小于所述第三彩色滤光片在所述第一方向上的平均尺寸。

82.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片在所述第一方向上的平均尺寸的范围为2.3-2.6微米,所述第二彩色滤光片在所述第一方向上的平均尺寸的范围为1.7-1.95微米,所述第三彩色滤光片在所述第一方向上的平均尺寸的范围为2.3-2.7微米。

83.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片在所述第一方向上的平均尺寸与所述第二彩色滤光片在所述第一方向上的平均尺寸的差值和所述第一彩色滤光片在所述第一方向上的平均尺寸与所述第三彩色滤光片在所述第一方向上的平均尺寸的差值之比的范围为2

ꢀ‑ꢀ

3。

84.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片包括第一边缘部、第二边缘部和位于所述第一边缘部和所述第二边缘部之间的中间部,所述中间部在所述第一方向上的平均尺寸小于所述第一边缘部在所述第一方向上的平均尺寸和所述第二边缘部在所述第一方向上的平均尺寸。

85.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片包括与所述第二彩色滤光片接触的第一接触面,所述第二彩色滤光片包括与所述第三彩色滤光片接触的第二接触面,所述第三彩色滤光片包括与所述第一彩色滤光片接触的第三接触面,所述第一接触面在垂直于所述驱动基板的第二方向上的尺寸与所述第二接触面在所述第二方向上的尺寸相等,且小于所述第三接触面在所述第二方向上的尺寸。

86.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片与所述驱动基板远离所述阳极层的表面的距离大于所述第三彩色滤光片与所述驱动基板远离所述阳极层的表面的距离,且小于所述第二彩色滤光片与所述驱动基板远离所述阳极层的表面

的距离。

87.例如,在本公开一实施例提供的一种显示基板中,所述第一彩色滤光片为红色滤光片,所述第二彩色滤光片为绿色滤光片,所述第三彩色滤光片为蓝色滤光片。

88.例如,在本公开一实施例提供的一种显示基板中,所述彩膜层的材料包括干燥剂。

89.例如,在本公开一实施例提供的一种显示基板中,所述彩膜层包括铝元素。

90.例如,本公开一实施例提供的一种显示基板还包括:保护层,位于所述彩膜层远离所述驱动基板的一侧。

91.例如,在本公开一实施例提供的一种显示基板中,所述彩膜层还包括:黑矩阵,位于第一彩色滤光片、第二彩色滤光片和第三彩色滤光片中任意相邻的两个之间。

92.例如,本公开一实施例提供的一种显示基板还包括:玻璃盖板,位于所述彩膜层远离所述驱动基板的一侧。

93.本公开至少一个实施例还提供一种显示装置,其包括上述任一项所述的显示基板。

94.本公开至少一个实施例还提供一种显示装置,其包括上述任一项所述的显示基板。

95.例如,本公开一实施例提供的一种显示装置还包括:对置基板,与所述显示基板相对设置,所述对置基板包括玻璃盖板和位于所述玻璃盖板上的彩膜层,所述彩膜层包括所述彩膜层包括第一彩色滤光片、第二彩色滤光片和第三彩色滤光片。

96.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片和所述第二彩色滤光片存在第一交叠区,所述第二彩色滤光片和所述第三彩色滤光片存在第二交叠区,所述第三彩色滤光片和所述第一彩色滤光片存在第三交叠区。

97.例如,在本公开一实施例提供的一种显示装置中,所述第一交叠区、所述第二交叠区和所述第三交叠区在所述驱动基板上的正投影与所述凸起部在所述驱动基板上的正投影交叠。

98.例如,在本公开一实施例提供的一种显示装置中,所述第一交叠区、所述第二交叠区和所述第三交叠区在所述驱动基板上的正投影与相邻两个所述阳极之间的间隔区在所述驱动基板上的正投影交叠。

99.例如,在本公开一实施例提供的一种显示装置中,所述第一交叠区在第二方向上的尺寸大于所述第二交叠区在所述第二方向上的尺寸,所述第二交叠区在所述第二方向上的尺寸大于所述第三交叠区在所述第二方向上的尺寸。

100.例如,在本公开一实施例提供的一种显示装置中,所述第一交叠区在所述第二方向上的尺寸范围为400-600纳米,所述第二交叠区在所述第二方向上的尺寸范围为250-350纳米,所述第三交叠区在所述第二方向上的尺寸范围为100-200纳米。

101.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片在所述第一方向上的平均尺寸大于所述第二彩色滤光片在所述第一方向上的平均尺寸,且小于所述第三彩色滤光片在所述第一方向上的平均尺寸。

102.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片在所述第一方向上的平均尺寸的范围为2.3-2.6微米,所述第二彩色滤光片在所述第一方向上的平均尺寸的范围为1.7-1.95微米,所述第三彩色滤光片在所述第一方向上的平均尺寸的范围

为2.3-2.7微米。

103.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片在所述第一方向上的平均尺寸与所述第二彩色滤光片在所述第一方向上的平均尺寸的差值和所述第一彩色滤光片在所述第一方向上的平均尺寸与所述第三彩色滤光片在所述第一方向上的平均尺寸的差值之比的范围为2

ꢀ‑ꢀ

3。

104.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片包括第一边缘部、第二边缘部和位于所述第一边缘部和所述第二边缘部之间的中间部,所述中间部在所述第一方向上的平均尺寸小于所述第一边缘部在所述第一方向上的平均尺寸和所述第二边缘部在所述第一方向上的平均尺寸。

105.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片包括与所述第二彩色滤光片接触的第一接触面,所述第二彩色滤光片包括与所述第三彩色滤光片接触的第二接触面,所述第三彩色滤光片包括与所述第一彩色滤光片接触的第三接触面,所述第一接触面在与所述驱动基板垂直的第二方向上的尺寸与所述第二接触面在所述第二方向上的尺寸相等,且小于所述第三接触面在所述第二方向上的尺寸。

106.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片与所述驱动基板远离所述阳极层的表面的距离大于所述第三彩色滤光片与所述驱动基板远离所述阳极层的表面的距离,且小于所述第二彩色滤光片与所述驱动基板远离所述阳极层的表面的距离。

107.例如,在本公开一实施例提供的一种显示装置中,所述第一彩色滤光片为红色滤光片,所述第二彩色滤光片为绿色滤光片,所述第三彩色滤光片为蓝色滤光片。

108.例如,在本公开一实施例提供的一种显示装置中,所述彩膜层的材料包括干燥剂。

109.例如,在本公开一实施例提供的一种显示装置中,所述彩膜层包括铝元素。

110.例如,在本公开一实施例提供的一种显示装置中,所述彩膜层还包括:黑矩阵,位于第一彩色滤光片、第二彩色滤光片和第三彩色滤光片中任意相邻的两个之间。

附图说明

111.为了更清楚地说明本公开实施例的技术方案,下面将对实施例的附图作简单地介绍,显而易见地,下面描述中的附图仅仅涉及本公开的一些实施例,而非对本公开的限制。

112.图1为本公开一实施例提供的一种显示基板的平面示意图。

113.图2为本公开一实施例提供的另一种显示基板的局部结构示意图。

114.图3为本公开一实施例提供的另一种显示基板的局部结构示意图。

115.图4a为本公开一实施例提供的另一种显示基板的局部结构示意图。

116.图4b为本公开一实施例提供的另一种显示基板的局部结构示意图。

117.图5为本公开一实施例提供的一种显示基板的平面示意图。

118.图6为本公开一实施例提供的另一种显示基板的局部结构示意图。

119.图7为本公开一实施例提供的另一种显示基板的局部结构示意图。

120.图8为本公开一实施例提供的另一种显示基板的局部结构示意图。

121.图9为本公开一实施例提供的一种显示基板中的第一彩色滤光片的示意图。

122.图10为本公开一实施例提供的另一种显示基板的局部结构示意图。

123.图11为本公开一实施例提供的一种驱动基板的结构示意图。

124.图12为本公开一实施例提供的另一种显示基板的局部结构示意图。

125.图13为本公开一实施例提供的一种显示装置的示意图。

126.图14为本公开一实施例提供的一种显示装置的平面图。

127.图15为本公开一实施例提供的另一种显示装置的示意图。

128.图16为本公开一实施例提供的一种显示基板的平面示意图。

129.图17为本公开一实施例提供的一种显示基板的局部剖面示意图。

130.图18为本公开一实施例提供的一种显示基板中驱动电路的等效示意图。

131.图19为本公开一实施例提供的一种显示基板中驱动电路的平面示意图。

132.图20a-20e分别示出了图19中所示的显示基板的各层布局的平面图。

133.图21为本公开一实施例提供的一种显示基板用于设置存储电容的区域的示意图。

134.图22为本公开一实施例提供的一种显示基板中存储电容的布局图。

135.图23a-图23d为图22中的各层布局的平面图。

136.图23e为本公开一实施例提供的一种显示基板中的存储电容的截面示意图。

137.图24a为本公开一实施例提供的一种显示基板的框图。

138.图24b为本公开一实施例提供的一种像素电路的示意图。

139.图24c示出了该像素电路形成闩锁效应的示意图。

140.图25a为本公开一实施例提供的另一种像素电路的示意图。

141.图25b为图24a所示像素电路的一种具体实现示例的电路图。

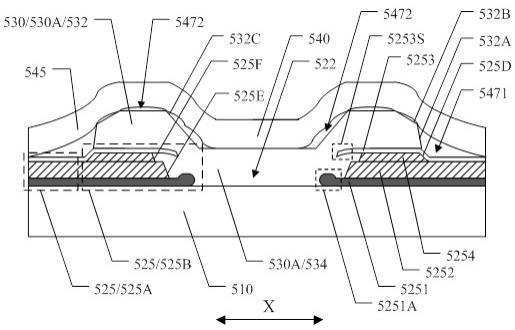

142.图25c示出了图25b所示像素电路的信号时序图。

143.图26a为本公开一实施例提供的另一种显示基板的示意图。

144.图26b为图26a沿剖面线i-i’的剖视图。

145.图27a为本公开一实施例提供的另一种显示基板的示意图。

146.图27b为本公开一实施例提供的另一种显示基板的示意图。

147.图28a-图28e为图27a所示的基板结构的形成过程。

148.图29a-29c为本公开一实施例提供的一种显示基板的形成过程的示意图。

149.图30a为本公开一实施例提供的一种显示基板中第二导电层的示意图。

150.图30b本公开一实施例提供的一种显示基板中第一导电层和第二导电层的示意图。

151.图31a为本公开一实施例提供的一种显示基板中的第三导电层的示意图。

152.图31b为本公开一实施例提供的一种显示基板中第二导电层和第三导电层的示意图。

具体实施方式

153.为使本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

154.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具

有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。

155.通常的大尺寸有机发光二极管(oled)显示装置通过将阳极隔离的方式来降低漏电和串扰。然而,在微型有机发光二极管(micro-oled)显示装置中,采用同样的方式虽然也可降低漏电和串扰,但是由于微型有机发光二极管显示装置中的像素限定层的厚度较低,并且像素密度较大,采用同样的方式不能彻底地隔离发光层,从而使得漏电和串扰现象仍然存在。

156.对此,本公开实施例提供一种显示基板和显示装置。该显示基板包括驱动基板、阳极层、像素限定层、发光功能层、阴极层和封装层;驱动基板包括衬底和驱动电路;阳极层位于驱动基板上;像素限定层位于阳极层远离驱动基板的一侧;发光功能层位于阳极层远离驱动基板的一侧;阴极层位于发光功能层远离驱动基板的一侧;封装层位于阴极层远离驱动基板的一侧;驱动电路包括至少一个晶体管,晶体管包括半导体层,半导体层至少部分位于衬底内部;阳极层包括多个阳极,显示基板包括多个像素开口,且位于多个阳极远离驱动基板的一侧,多个像素开口被配置为与多个阳极至少存在交叠;发光功能层包括多个发光部,多个发光部与多个阳极被暴露的部分接触设置。各阳极包括主体部和凸起部,凸起部与所述主体部相连,凸起部在垂直于驱动基板的第一方向上的尺寸大于主体部在垂直于驱动基板的第一方向上的尺寸。由此,该显示基板可提供一种微型的显示基板,可利用硅基电路板作为驱动基板来驱动发光功能层进行发光显示,并且还可减少和避免相邻子像素之间的串扰。

157.下面,结合附图对本公开实施例提供的显示基板和显示装置进行详细的说明。

158.本公开一实施例提供一种显示基板。图1为本公开一实施例提供的一种显示基板的平面示意图;图2为本公开一实施例提供的另一种显示基板的局部结构示意图。

159.如图1和图2所示,该显示基板500包括驱动基板510、阳极层520、像素限定层530、发光功能层540、阴极层550和封装层560;驱动基板510包括衬底512和驱动电路514;阳极层520位于驱动基板510上;像素限定层530位于阳极层520远离驱动基板510的一侧;发光功能层540位于阳极层520远离驱动基板510的一侧;阴极层550位于发光功能层540远离驱动基板510的一侧;封装层560位于阴极层550远离驱动基板510的一侧;驱动电路514包括至少一个晶体管t,晶体管t包括半导体层102,半导体层102至少部分位于衬底512内部。也就是说,衬底512部分可作为半导体层。需要说明的是,图1和图2中并未示出驱动电路的全部结构,驱动电路可以包括晶体管、存储电容、控流电阻、分压电阻等结构;驱动电路的具体电路结构可以根据实际需要进行设置,本公开的实施例对此不作限制。

160.例如,该驱动基板510可为硅基电路板,由于硅基电路板所采用的半导体制作工艺成熟,性能稳定,且具有较小的尺寸和精度,因此有利于制作微型显示装置。当然,本公开实施例包括但不限于此,驱动基板也可采用其他类型的驱动基板。

161.在一些示例中,如图1和图2所示,阳极层520包括多个阳极525,显示基板500包括多个像素开口535,多个像素开口535位于像素限定层530所在的膜层,且被像素限定层530

包围;多个像素开口535位于多个阳极525远离驱动基板510的一侧,多个像素开口535被配置为与多个阳极525至少存在交叠;发光功能层540包括多个发光部545,多个发光部545至少部分位于多个像素开口535之内,且与多个阳极525被暴露的部分接触设置。由此,多个阳极可驱动多个发光部进行发光显示。

162.在本公开实施例提供的显示基板中,驱动基板可采用半导体制作工艺进行制作,从而可将用于驱动各个像素进行发光和显示的像素驱动电路集成在驱动基板之中。由此,该显示基板可提供一种微型的显示基板,并具有分辨率高、亮度高、色彩丰富、驱动电压低、响应速度快、功耗低等优点。

163.在一些示例中,如图1和图2所示,多个阳极525与多个像素开口535一一对应设置,多个像素开口535与多个发光部545一一对应设置。需要说明的是,上述的“一一对应设置”是指一个阳极上设置一个像素开口,一个像素开口中设置一个发光部,并且阳极在驱动基板上的正投影与对应的像素开口在驱动基板上的正投影至少部分重叠,像素开口在驱动基板上的正投影与发光部在驱动基板上的正投影至少部分重叠。当然,本公开实施例包括但不限于此。

164.在一些示例中,如图2所示,该显示基板100还包括:第一平坦层591、第二平坦层592和反射电极层593;第一平坦层591位于驱动电路514和阳极层520之间;反射电极层593位于第一平坦层591靠近阳极层520的一侧;第二平坦层592位于反射电极层593靠近阳极层520的一侧。

165.在一些示例中,如图2所示,反射电极层593在像素开口535中连续设置。

166.在一些示例中,如图1和图2所示,该显示基板还包括彩膜层570,位于封装层560远离驱动基板510的一侧。当发光功能层被配置为发白光时,彩膜层可包括多个彩色滤光片,以实现彩色显示。当然,本公开实施例包括但不限于此,发光功能层也可被配置为直接发不同颜色的光。

167.在一些示例中,如图1和图2所示,该显示基板500还包括保护层580,位于彩膜层570远离驱动基板510的一侧。保护层580可以起到保护彩膜层570的效果,使得彩膜层570的滤光性能在长期使用过程中保持稳定,从而可提高显示基板的显示质量。

168.在一些示例中,如图1和图2所示,该显示基板500还包括玻璃盖板590,位于彩膜层570远离驱动基板510的一侧。

169.图3为本公开一实施例提供的另一种显示基板的局部结构示意图。图4a为本公开一实施例提供的另一种显示基板的局部结构示意图。如图3和图4a所示,图3所示的显示基板没有示出发光功能层,图4a所示的显示基板中示出了发光功能层。

170.如图3和图4a所示,各阳极525包括主体部525a和凸起部525b,凸起部525b与主体部525a相连,凸起部525b在第一方向上的尺寸大于主体部525a在第一方向上的尺寸;也就是说,凸起部525b的厚度大于主体部525a的厚度。主体部525a所在位置处的第一平坦层591远离衬底512的表面与衬底512的距离与凸起部525b所在位置处的第一平坦层591远离衬底512的表面与衬底512的距离相等,主体部525a远离衬底512的表面与第一平坦层591远离衬底512的表面的距离大于凸起部525b远离衬底512的表面与第一平坦层591远离衬底512的表面的距离。需要说明的是,第一方向可为垂直于驱动基板的方向。

171.在该示例提供的显示基板中,由于凸起部525b在垂直于驱动基板510的方向上的

尺寸大于主体部525a在垂直于驱动基板510的方向上的尺寸,因此位于两个阳极525之间,且与阳极525的边缘部分交叠的像素限定层530可形成与凸起部525对应的突起结构532。由此,在形成发光功能层540时,发光功能层540中的至少部分子功能层(例如电荷产生层)可更好地在突起结构532所在的位置断开,即相邻两个阳极525对应的发光部545中的至少部分子功能层不连接,从而可有效地避免相邻子像素之间的漏电和串扰。另一方面,此时的像素限定层530的突起结构532的高度也更高,从而可更好地起到像素限定的作用,从光学上减少和避免相邻子像素之间的串扰。

172.在一些示例中,如图3和图4a所示,各阳极525包括主体部525a和凸起部525b,凸起部525b设置在主体部525a的周边,从而可更好地使得发光功能层540中的至少部分功能层在主体部525a的边缘断开。

173.在一些示例中,如图3和图4a所示,像素限定层530在驱动基板510上的正投影与凸起部525b在驱动基板510上的正投影交叠。由此,像素限定层530可形成与凸起部525对应的,且位于凸起部525远离驱动基板510的一侧的突起结构532。

174.在一些示例中,如图3和图4a所示,像素限定层530包括像素限定部530a,像素限定部530a包括像素限定平坦部534和像素限定平坦部534两侧的两个突起结构532;像素限定平坦部534位于相邻的两个阳极525之间,两个突起结构532分别位于相邻两个阳极525的两个凸起部525b远离驱动基板510的一侧,像素限定平坦部534将两个突起结构532相连。也就是说,像素限定部530a既包括位于相邻两个阳极525之间的部分和与两个阳极525交叠的部分;由于相邻两个阳极525之间比较平坦,而阳极525的边缘部分设置有上述的凸出部525b,因此位于相邻两个阳极525之间的部分形成为上述像素限定平坦部534,而与两个阳极525交叠的部分形成为上述的突起结构532。

175.在该示例提供的显示基板中,在形成发光功能层540时,由于像素限定部530a的存在,发光功能层540中的至少部分子功能层(例如电荷产生层)可更好地在突起结构532所在的位置断开,即相邻两个阳极525对应的发光部545中的至少部分子功能层不连接,从而可有效地避免相邻子像素之间的漏电和串扰。另一方面,此时的突起结构532的高度也更高,从而可更好地起到像素限定的作用,从光学上减少和避免相邻子像素之间的串扰。

176.在一些示例中,如图3和图4a所示,像素限定部530a关于相邻两个阳极525之间的间隔区522的中心呈对称设置。需要说明的是,由于工艺误差的存在,实际的像素限定部在间隔区的中心的两侧的两个部分可能存在差异,因此上述的像素限定部关于相邻两个阳极之间的间隔区的中心呈对称设置的情形包括像素限定部在间隔区的中心的两侧的两个部分重合率达到80%的情况。

177.在一些示例中,如图3和图4a所示,各突起结构532包括第一侧壁532a和第二侧壁532b;第一侧壁532a位于突起结构532靠近阳极525的主体部525a的中心的一侧,第二侧壁532b与第一侧壁532a相连且位于第一侧壁532a远离驱动基板510的一侧,也就是说,第二侧壁532b相对于第一侧壁532a,更远离驱动基板510;第一侧壁532a的坡度角大于第二侧壁532b的坡度角。需要说明的是,由于实际工艺中第一侧壁或第二侧壁可能并非标准的平面,因此上述的坡度角可为第一侧壁或第二侧壁的两个端点的连线的坡度角。

178.在该示例提供的显示基板中,在形成发光功能层的过程中,由于第一侧壁的坡度角大于第二侧壁的坡度角,第一侧壁具有较大的坡度角,因此更加陡峭,从而可更好地使得

发光功能层中的至少部分子功能层(例如电荷产生层)在第一侧壁所在的位置断开。另一方面,由于第二侧壁的坡度角小于第一侧壁的坡度角,可形成一个平缓的平台,第二侧壁可对发光功能层的材料起到引导的作用,使得发光功能层在阳极被像素开口暴露的部分和突起结构相邻的位置形成接触不良的区域,从而可减少发光功能层在阳极被像素开口暴露的部分和突起结构相邻的位置的发光亮度。由此,该示例提供的显示基板可进一步降低相邻子像素之间的串扰。

179.在一些示例中,如图4a所示,发光功能层540与主体部525a之间存在第一孔隙5471,发光功能层540与像素限定层530之间存在至少一个第二孔隙5472,第一孔隙5471占据的空间大于第二孔隙5472占据的空间。由此,第一孔隙5471和第二孔隙5472形成了共同层横向传递载流子的弱传导区,有益于降低光的横向串扰。当然,本公开实施例包括但不限于此,发光功能层与像素限定层也可不形成上述的第二孔隙。

180.图4b为本公开一实施例提供的另一种显示基板的局部结构示意图。如图4b所示,发光功能层540与像素限定层530之间紧密贴合。

181.在一些示例中,如图3和图4a所示,突起结构532还包括第三侧壁532c,位于突起结构532远离主体部525a的一侧,第三侧壁532c的坡度角大于532b第二侧壁的坡度角,且小于第一侧壁532a的坡度角。由此,第三侧壁的坡度角较为平缓,从而可减少甚至避免后续在第三侧壁上形成的发光功能层中形成孔隙,进而避免形成水氧入侵的通道。另一方面,由于第三侧壁的坡度角较为平缓,因此也便于像素限定部形成完整的一体结构,避免在第三侧壁产生脱落(peeling)现象。

182.在一些示例中,如图3和图4a所示,各突起结构532还包括第三侧壁532c,第三侧壁532c位于突起结构532远离主体部525a的一侧。此时,第一侧壁532a的坡度角为α,第二侧壁532b的坡度角为β,第三侧壁532c的坡度角为γ,并满足下列公式:β《γ《α。在该示例提供的显示基板中,第三侧壁532c的坡度角γ相对于第一侧壁532a的坡度角α较为平缓,从而可减少甚至避免后续在第三侧壁532c上形成的发光功能层中形成孔隙,进而避免形成水氧入侵的通道。另一方面,由于第三侧壁532c的坡度角γ较为平缓,因此也便于像素限定部形成完整的一体结构,避免在第三侧壁产生脱落(peeling)现象。另一方面,由于第三侧壁532c的坡度角γ大于第二侧壁532b的坡度角β,因此可避免突起结构占用较大的面积,避免影响开口率。

183.在一些示例中,如图3和图4a所示,第一侧壁532a的坡度角与第二侧壁532b的坡度角的差值等于第三侧壁的坡度角的i倍,i的取值范围为0.8

ꢀ‑ꢀ

1.2。由此,该突起结构可较好地实现上述的防止相邻子像素之间的串扰、避免形成水氧入侵、避免像素限定部产生脱落现象的效果。

184.在一些示例中,如图3和图4a所示,第一侧壁的坡度角α,第二侧壁的坡度角β,第三侧壁的坡度角γ满足下列公式:(α-β)=i*γ,其中,i的取值范围为0.8

ꢀ‑ꢀ

1.2。

185.在该示例提供的显示基板中,由于第一侧壁的坡度角α,第二侧壁的坡度角β,第三侧壁的坡度角γ满足上述公式所限定的大小关系,该突起结构可较好地实现上述的防止相邻子像素之间的串扰、避免形成水氧入侵、避免像素限定部产生脱落现象的效果。

186.在一些示例中,如图3和图4a所示,第一侧壁532a的坡度角与第二侧壁532b的坡度角的差值等于第二侧壁532b的坡度角与第三侧壁532c的坡度角的差值的j倍,j的取值范围为1.5-3。由此,该突起结构可较好地实现上述的防止相邻子像素之间的串扰、避免形成水氧入侵、避免像素限定部产生脱落现象的效果。

187.在一些示例中,如图3和图4a所示,第一侧壁的坡度角α,第二侧壁的坡度角β,第三侧壁的坡度角γ满足下列公式:(α-β)=j*(γ-β),其中,j的取值范围为1.5-3。

188.在该示例提供的显示基板中,由于第一侧壁的坡度角α,第二侧壁的坡度角β,第三侧壁的坡度角γ满足上述公式所限定的大小关系,该突起结构可较好地实现上述的防止相邻子像素之间的串扰、避免形成水氧入侵、避免像素限定部产生脱落现象的效果。

189.在一些示例中,如图3和图4a所示,第一侧壁532a的坡度角与第二侧壁532b的坡度角之和等于第三侧壁532c的坡度角的k倍,k的取值范围为2

ꢀ‑ꢀ

3。由此,该突起结构可较好地实现上述的防止相邻子像素之间的串扰、避免形成水氧入侵、避免像素限定部产生脱落现象的效果。

190.在一些示例中,如图3和图4a所示,第一侧壁的坡度角α,第二侧壁的坡度角β,第三侧壁的坡度角γ满足下列公式:(α+β)=k*γ-β,其中,k的取值范围为2-3。

191.在该示例提供的显示基板中,由于第一侧壁的坡度角α,第二侧壁的坡度角β,第三侧壁的坡度角γ满足上述公式所限定的大小关系,该突起结构可较好地实现上述的防止相邻子像素之间的串扰、避免形成水氧入侵、避免像素限定部产生脱落现象的效果。

192.在一些示例中,如图3和图4a所示,第一侧壁532a的坡度角的取值范围可为75-89度;第二侧壁532b的坡度角的取值范围可为15-45度;第三侧壁532c的坡度角的取值范围可为45-60度。

193.在一些示例中,如图3和图4a所示,第一侧壁532a的坡度角的取值范围可为75-89度;第二侧壁532b的坡度角的取值范围可为25-35度;第三侧壁532c的坡度角的取值范围可为45-55度。

194.在一些示例中,如图3和图4a所示,第二侧壁532b在驱动基板510上的正投影在第二方向上的尺寸大于第一侧壁532a在驱动基板510上的正投影在第二方向上的尺寸。由此,该突起结构可更好地在第一侧壁所在的位置使得发光功能层中电荷产生层的断开。

195.在一些示例中,如图3和图4a所示,第三侧壁532c在驱动基板510上的正投影在第二方向上的尺寸大于第二侧壁532b在驱动基板510上的正投影在第二方向上的尺寸。由此,该突起结构可减少甚至避免后续在第三侧壁532c上形成的发光功能层中形成孔隙,进而避免形成水氧入侵的通道。另一方面,由于第三侧壁532c的坡度角γ较为平缓,因此也便于像素限定部形成完整的一体结构,避免在第三侧壁产生脱落(peeling)现象。

196.在一些示例中,如图3和图4a所示,第一侧壁532a在第一方向上的尺寸为h1,第二侧壁532b在第一方向上的尺寸为h2,第三侧壁532c在第一方向上的尺寸为h3,h1、h2和h3满足下列公式:

h3*cosγ 》 h2*cosβ 》 h1*cosα。

197.由此,该突起结构可更好地在第一侧壁所在的位置使得发光功能层中电荷产生层的断开;同时,该突起结构可减少甚至避免后续在第三侧壁上形成的发光功能层中形成孔隙,进而避免形成水氧入侵的通道。

198.在一些示例中,如图3和图4a所示,各阳极525的凸起部525b还包括第四侧壁525d,位于凸起部525b靠近主体部525a的中心的一侧,第四侧壁525d的坡度角大于第二侧壁532b的坡度角,且小于第一侧壁532a的坡度角。

199.在一些示例中,如图3和图4a所示,阳极525的凸起部525b包括第四侧壁525d,位于凸起部525b靠近主体部525a的中心的一侧,第四侧壁的坡度角为δ,且满足以下公式:β《δ《α。

200.在一些示例中,如图3和图4a所示,各阳极525的凸起部525b包括:第一子阳极层5251、第二子阳极层5252和第三子阳极层5253;第一子阳极层5251位于驱动电路514远离衬底512的一侧;第二子阳极层5252位于第一子阳极层5251远离驱动基板510的一侧;第三子阳极层5253位于第二子阳极层5252远离驱动基板510的一侧。

201.在一些示例中,如图3和图4a所示,第一子阳极层5251在第二方向上的尺寸大于第三子阳极层5253在第二方向上的尺寸,第三子阳极层5253在第二方向上的尺寸大于第二子阳极层5252在第二方向上的尺寸。由此,由于第三子阳极层在第二方向上的尺寸大于第二子阳极层在第二方向上的尺寸,第三子阳极层的边缘缺少支撑,因此可使得第三子阳极层5253形成向驱动基板510弯曲的弯曲结构5253s,在后续形成像素限定部时,可有效地避免像素限定部产生脱落(peeling)现象。需要说明的是,由于像素限定部通常采用无机材料制作,如果凸起部的边缘过于陡峭,则容易产生脱落现象。

202.另一方面,第三子阳极层可采用导电性能较差的材料制作,例如氧化铟锡;此时,由于第三子阳极层在第二方向上的尺寸大于第二子阳极层在第二方向上的尺寸,第三子阳极层的边缘缺少支撑,因此可使得第三子阳极层形成向驱动基板弯曲的弯曲结构,从而可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

203.例如,上述的第二方向为从凸起部525b到主体部525a的方向或者从主体部525a到凸起部525b的方向,第二方向平行于驱动基板510远离阳极层520的表面的方向。

204.例如,第三子阳极层的导电率小于第一子阳极层的导电率和第二子阳极层的导电率,从可更好地与发光功能层的功函数进行匹配。

205.在一些示例中,如图3和图4a所示,第三子阳极层5253在第二方向上超出第二子阳极层5252的尺寸小于像素限定层530在驱动基板510上的正投影与凸起部525b在驱动基板510上的正投影的交叠区域在第二方向上的尺寸。

206.在一些示例中,如图3和图4a所示,第三子阳极层5253在第二方向上超出第二子阳极层5252的尺寸小于像素限定层530在驱动基板510上的正投影与凸起部525b在驱动基板510上的正投影的交叠区域在第二方向上的尺寸的1/4。

207.在一些示例中,如图3和图4a所示,第三子阳极层5253远离主体部525a的一端向靠近第一子阳极层5251的方向弯曲,从而第三子阳极层可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也

可避免产生尖端放电等现象。

208.在一些示例中,如图3和图4a所示,各阳极525的凸起部525b还包括第四子阳极层5254,位于第二子阳极层5252和第三子阳极层5253之间。由此,可通过将位于阳极的凸起部的第四子阳极层保留,而将位于阳极的主体部的第四子阳极层刻蚀掉,从而可形成上述的具有高度差异的主体部和凸起部。

209.在一些示例中,如图3和图4a所示,第四子阳极层5254在第二方向上的尺寸小于第二子阳极层5252在第二方向上的尺寸。由此,形成在第四子阳极层5254上的第三子阳极层5253可更好地形成弯曲结构5253s,从而在后续形成像素限定部时,可有效地避免像素限定部产生脱落(peeling)现象。

210.在一些示例中,如图3和图4a所示,第三子阳极层5253在第二方向上超出第四子阳极层5254的尺寸小于像素限定层530在驱动基板510上的正投影与凸起部525b在驱动基板510上的正投影的交叠区域在所述第二方向上的尺寸。

211.在一些示例中,如图3和图4a所示,第二子阳极层5252包括第五侧壁525e,位于第二子阳极层525e远离主体部525a的一侧,第四子阳极层5254包括第六侧壁525f,位于第四子阳极层5254远离主体部525a的一侧;第五侧壁525e的坡度角大于第四侧壁525d的坡度角,第六侧壁525f的坡度角大于第四侧壁525d的坡度角,第五侧壁525e的坡度角大于第六侧壁525f的坡度角,从而避免第二子阳极层和第三子阳极层形成尖端结构。由此,可在一定程度上抑制尖端放电现象,从而可以提高产品的良率和使用寿命。

212.在一些示例中,如图3和图4a所示,第一子阳极层5251远离主体部525a的一端包括隆起部5251a,隆起部5251a在垂直于驱动基板510的方向上的厚度大于第一子阳极层5251在垂直于驱动基板510的方向上的平均厚度。由此,隆起部5251a也可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

213.在一些示例中,如图3和图4a所示,当第一子阳极层5251的隆起部5251a和第三子阳极层5253的弯曲结构5253s同时存在时,隆起部5251a和弯曲结构5253s可从上下两个方向起到将凸起部的边缘包裹的作用,进而可更好地在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。需要说明的是,本公开实施例包括但不限于此,当第一子阳极层5251的隆起部5251a或第三子阳极层5253的弯曲结构5253s单独存在时,也可在一定程度上起到将凸起部的边缘包裹作用。

214.在一些示例中,第一子阳极层5251在垂直于驱动基板510的方向上的厚度与第二子阳极层5252在垂直于驱动基板510的方向上的厚度之比的范围在1/15-1/5。

215.在一些示例中,第一子阳极层5251在垂直于驱动基板510的方向上的厚度与第三子阳极层5253在垂直于驱动基板510的方向上的厚度之比的范围在1/3-4/5。

216.在一些示例中,第一子阳极层5251在垂直于驱动基板510的方向上的厚度与第四子阳极层5254在垂直于驱动基板510的方向上的厚度之比的范围在1/24-1/8。

217.在一些示例中,第一子阳极层5251在垂直于驱动基板510的方向上的厚度范围为1-4纳米;第二子阳极层5252在垂直于驱动基板510的方向上的厚度范围为15-22纳米;第四子阳极层5254在垂直于驱动基板510的方向上的厚度范围为24-32纳米;第三子阳极层5253在垂直于驱动基板510的方向上的厚度范围为3-5纳米。

218.在一些示例中,第一子阳极层5251在垂直于驱动基板510的方向上的厚度范围为2-3纳米;第二子阳极层5252在垂直于驱动基板510的方向上的厚度范围为17-20纳米;第四子阳极层5254在垂直于驱动基板510的方向上的厚度范围为26-30纳米;第三子阳极层5253在垂直于驱动基板510的方向上的厚度范围为4纳米。

219.在一些示例中,相邻两个阳极525之间的距离与阳极525的凸起部525b在驱动基板510上的正投影的长度之比的范围为2

ꢀ‑ꢀ

4。也就是说,相邻两个阳极525之间的距离与阳极525在第二方向上的长度之比的范围为2

ꢀ‑ꢀ

4。由此,该显示基板可更好地避免相邻子像素之间的串扰。

220.在一些示例中,相邻两个阳极525之间的距离与阳极525的凸起部525b在驱动基板510上的正投影的长度之比的范围为2.5

ꢀ‑ꢀ

3.5。也就是说,相邻两个阳极525之间的距离与阳极525在第二方向上的长度之比的范围为2.5

ꢀ–ꢀ

3.5。由此,该显示基板可更好地避免相邻子像素之间的串扰。

221.在一些示例中,相邻两个阳极525之间的距离范围为0.6-1微米。也就是说,间隔区522的宽度范围可在0.6-1微米。当然,本公开实施例包括但不限于此,间隔区的宽度范围可根据实际情况进行设置。

222.在一些示例中,相邻两个阳极525的距离范围为0.7-0.9微米。当然,本公开实施例包括但不限于此,间隔区的宽度范围可根据实际情况进行设置。

223.图5为本公开一实施例提供的一种显示基板的平面示意图。如图5所示,凸起部525b围绕主体部525a设置。由此,该显示基板可有效地避免在任何方向上相邻的子像素之间的串扰,从而使得该显示基板可适应于不同的像素排列结构。

224.在一些示例中,如图5所示,阳极525在驱动基板510上的正投影的形状包括六边形。当然,本公开实施例包括但不限于此,阳极525在驱动基板510上的正投影的形状也可为其他合适的形状。需要说明的是,像素开口与阳极对应设置,因此像素开口在驱动基板上的正投影的形状与阳极在驱动基板上的正投影的形状相似。

225.在一些示例中,如图5所示,多个阳极525在驱动基板510上呈阵列排布,以形成阳极行610;在各阳极行610中,多个阳极525沿方向依次排布。

226.在一些示例中,如图5所示,上述的第二方向可为行方向。此时,各阳极525在驱动基板510上的正投影在第二方向上的尺寸与相邻两个阳极525之间的距离的比值范围在4

ꢀ‑ꢀ

6。由此,该显示基板可实现较大的开口率,并有效地避免相邻子像素之间的串扰。

227.在一些示例中,如图5所示,各阳极525在驱动基板510上的正投影在第二方向上的尺寸可为4-5微米。

228.图6为本公开一实施例提供的另一种显示基板的局部结构示意图。如图6所示,如图6所示,各阳极525的凸起部525b包括第一子阳极层5251、第二子阳极层5252和第三子阳极层5253;第一子阳极层5251位于驱动电路514远离衬底512的一侧;第二子阳极层5252位于第一子阳极层5251远离驱动基板510的一侧;第三子阳极层5253位于第二子阳极层5252远离驱动基板510的一侧。与图3和图4a所示的显示基板不同的是,图6所示的显示基板不包括第四子阳极层。

229.在一些示例中,如图6所示,阳极525的主体部525a与凸起部525b可具有相同的层结构,即包括同样数量的多个膜层和同样的层叠关系,但不限定各个膜层的厚度相同。此

时,可通过将位于阳极的主体部的第二子阳极层部分刻蚀,而保留阳极的凸起部的第二子阳极层,从而形成具有高度差异的主体部和凸起部。

230.在一些示例中,如图6所示,第一子阳极层5251在第二方向上的尺寸大于第三子阳极层5253在第二方向上的尺寸,第三子阳极层5253在第二方向上的尺寸大于第二子阳极层5252在第二方向上的尺寸;上述的第二方向为从凸起部525b到主体部525a的方向或者从主体部525a到凸起部525b的方向,第二方向平行于驱动基板510远离阳极层520的表面的方向。由此,由于第三子阳极层在第二方向上的尺寸大于第二子阳极层在第二方向上的尺寸,第三子阳极层的边缘缺少支撑,因此可使得第三子阳极层5253形成向驱动基板510弯曲的弯曲结构5253s,在后续形成像素限定部时,可有效地避免像素限定部产生脱落(peeling)现象。需要说明的是,由于像素限定部通常采用无机材料制作,如果凸起部的边缘过于陡峭,则容易产生脱落现象。

231.另一方面,第三子阳极层可采用导电性能较差的材料制作,例如氧化铟锡;此时,由于第三子阳极层在第二方向上的尺寸大于第二子阳极层在第二方向上的尺寸,第三子阳极层的边缘缺少支撑,因此可使得第三子阳极层形成向驱动基板弯曲的弯曲结构,从而可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

232.例如,第三子阳极层的导电率小于第一子阳极层的导电率和第二子阳极层的导电率。

233.在一些示例中,如图6所示,第三子阳极层5253远离主体部525a的一端向靠近第一子阳极层5251的方向弯曲,从而第三子阳极层可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

234.在一些示例中,如图6所示,第二子阳极层5252包括第五侧壁525e和第六侧壁525f,第六侧壁525f位于第五侧壁525e远离驱动基板510的一侧,即第六侧壁525f相比与第五侧壁525e更远离驱动基板510。第五侧壁525e的坡度角大于第四侧壁525d的坡度角,第六侧壁525f的坡度角大于第四侧壁525d的坡度角,第五侧壁525e的坡度角大于第六侧壁525f的坡度角,从而避免第二子阳极层形成尖端结构。由此,可在一定程度上抑制尖端放电现象,从而可以提高产品的良率和使用寿命。另外,通过在第二子阳极层5252的边缘形成包括第五侧壁和第六侧壁的阶梯形结构,可使得位于第二子阳极层上的第三子阳极层形成更加平滑的弯曲结构,从而可更好地防止像素限定部发生脱落现象。

235.在一些示例中,如图6所示,第一子阳极层5251远离主体部525a的一端包括隆起部5251a,隆起部5251a在垂直于驱动基板510的方向上的厚度大于第一子阳极层5251在垂直于驱动基板510的方向上的平均厚度。由此,隆起部5251a也可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

236.在一些示例中,如图6所示,当第一子阳极层5251的隆起部5251a和第三子阳极层5253的弯曲结构5253s同时存在时,隆起部5251a和弯曲结构5253s可从上下两个方向起到将凸起部的边缘包裹的作用,进而可更好地在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。需要说明的是,本公开实施例包括但不限

于此,当第一子阳极层5251的隆起部5251a或第三子阳极层5253的弯曲结构5253s单独存在时,也可在一定程度上起到将凸起部的边缘包裹作用。

237.图7为本公开一实施例提供的另一种显示基板的局部结构示意图。如图7所示,如图7所示,各阳极525的凸起部525b包括第一子阳极层5251、第二子阳极层5252、第三子阳极层5253和第四子阳极层5254;第一子阳极层5251位于驱动电路514远离衬底512的一侧;第二子阳极层5252位于第一子阳极层5251远离驱动基板510的一侧;第三子阳极层5253位于第二子阳极层5252远离驱动基板510的一侧;第四子阳极层5254位于第二子阳极层5252和第三子阳极层5253之间。

238.在一些示例中,如图7所示,阳极525的主体部525a与凸起部525b可具有相同的层结构,即包括同样数量的多个膜层和同样的层叠关系,但不限定各个膜层的厚度相同。此时,阳极525的主体部525a同样包括第一子阳极层5251、第二子阳极层5252、第三子阳极层5253和第四子阳极层5254;第一子阳极层5251位于驱动电路514远离衬底512的一侧;第二子阳极层5252位于第一子阳极层5251远离驱动基板510的一侧;第三子阳极层5253位于第二子阳极层5252远离驱动基板510的一侧;第四子阳极层5254位于第二子阳极层5252和第三子阳极层5253之间。此时,可通过将位于阳极的主体部的第二子阳极层部分刻蚀,而保留阳极的凸起部的第二子阳极层,从而形成具有高度差异的主体部和凸起部。

239.例如,如图7所示,位于阳极525的主体部525a的第一子阳极层5251在垂直于驱动基板510的方向上的厚度与位于阳极525的凸起部525b的第一子阳极层5251在垂直于驱动基板510的方向上的厚度相同。

240.例如,如图7所示,位于阳极525的主体部525a的第三子阳极层5253在垂直于驱动基板510的方向上的厚度与位于阳极525的凸起部525b的第三子阳极层5253在垂直于驱动基板510的方向上的厚度相同。

241.例如,如图7所示,位于阳极525的主体部525a的第四子阳极层5254在垂直于驱动基板510的方向上的厚度与位于阳极525的凸起部525b的第四子阳极层5254在垂直于驱动基板510的方向上的厚度相同。

242.在一些示例中,如图7所示,第一子阳极层5251在第二方向上的尺寸大于第三子阳极层5253在第二方向上的尺寸,第三子阳极层5253在第二方向上的尺寸大于第二子阳极层5252在第二方向上的尺寸;第四子阳极层5254在第二方向上的尺寸小于第二子阳极层5252在第二方向上的尺寸。上述的第二方向为从凸起部525b到主体部525a的方向或者从主体部525a到凸起部525b的方向,第二方向平行于驱动基板510远离阳极层520的表面的方向。由此,形成在第四子阳极层5254上的第三子阳极层5253可更好地形成弯曲结构5253s,从而在后续形成像素限定部时,可有效地避免像素限定部产生脱落(peeling)现象。

243.另一方面,第三子阳极层可采用导电性能较差的材料制作,例如氧化铟锡;此时,由于第三子阳极层在第二方向上的尺寸大于第二子阳极层在第二方向上的尺寸,第三子阳极层的边缘缺少支撑,因此可使得第三子阳极层形成向驱动基板弯曲的弯曲结构,从而可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

244.例如,第三子阳极层的导电率小于第一子阳极层的导电率和第二子阳极层的导电率。

245.在一些示例中,如图7所示,第三子阳极层5253远离主体部525a的一端向靠近第一子阳极层5251的方向弯曲,从而第三子阳极层可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

246.在一些示例中,如图7所示,第二子阳极层5252包括第五侧壁525e,位于第二子阳极层525e远离主体部525a的一侧,第四子阳极层5254包括第六侧壁525f,位于第四子阳极层5254远离主体部525a的一侧;第五侧壁525e的坡度角大于第四侧壁525d的坡度角,第六侧壁525f的坡度角大于第四侧壁525d的坡度角,第五侧壁525e的坡度角大于第六侧壁525f的坡度角,从而避免第二子阳极层和第三子阳极层形成尖端结构。由此,可在一定程度上抑制尖端放电现象,从而可以提高产品的良率和使用寿命。

247.在一些示例中,如图7所示,第一子阳极层5251远离主体部525a的一端包括隆起部5251a,隆起部5251a在垂直于驱动基板510的方向上的厚度大于第一子阳极层5251在垂直于驱动基板510的方向上的平均厚度。由此,隆起部5251a也可在一定程度上起到对于凸起部的边缘的包裹作用,进而可在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。

248.在一些示例中,如图7所示,当第一子阳极层5251的隆起部5251a和第三子阳极层5253的弯曲结构5253s同时存在时,隆起部5251a和弯曲结构5253s可从上下两个方向起到将凸起部的边缘包裹的作用,进而可更好地在像素限定部出现缺陷时防止凸起部的边缘与发光功能层接触,也可避免产生尖端放电等现象。需要说明的是,本公开实施例包括但不限于此,当第一子阳极层5251的隆起部5251a或第三子阳极层5253的弯曲结构5253s单独存在时,也可在一定程度上起到将凸起部的边缘包裹作用。

249.图8为本公开一实施例提供的另一种显示基板的局部结构示意图。如图8所示,封装层560包括无机封装层710;无机封装层710位于阴极层550远离驱动基板510的一侧。

250.在一些示例中,如图8所示,无机封装层710包括多个子无机封装层7100,多个子无机封装层7100之中至少存在两个相邻的采用不同的材料制作的子无机封装层7100,多个子无机封装层7100中至少存在两个相邻的采用相同的材料制作的子无机封装层7100。通过在多个子无机封装层7100之间设置至少两个相邻的采用不同的材料制作的子无机封装层7100和至少两个相邻的采用相同的材料制作的子无机封装层7100,该无机封装层可形成更加致密的膜层,从而可更好地防止水氧入侵,进而可提高该显示装置的使用寿命。

251.例如,各个子无机封装层7100的材料可选自氮化硅、氧化硅、氮氧化硅中的至少一种。

252.在一些示例中,如图8所示,在远离驱动基板510的方向上,多个子无机封装层7100的折射率先增大后减小。发光功能层540发出的出射光从折射率较小的子无机封装层进入折射率较大的子无机封装层时,出射光会在它们之间的界面发生折射,从而可降低出射光扩散角度,从而可在显示基板的内部减少或避免相邻子像素之间的串扰;然后,出射光再从折射率较大的子无机封装层进入折射率较小的子无机封装层,并在它们之间的界面发生折射,此时出射光的扩散角度增大,但是由于出射光已经接近显示基板的出光面,不会对相邻子像素造成串扰。

253.在一些示例中,如图8所示,各子无机封装层7100包括交替设置的平坦区ptq和双

拱间隔区jgq、位于平坦区ptq远离双拱间隔区jgq的一侧的第一拱形区gx1、位于平坦区ptq和双拱间隔区jgq之间的第二拱形区gx2、以及位于平坦区ptq远离第二拱形区gx2的第三拱形区gx3,第一拱形区gx1和第二拱形区gx2关于平坦区ptq的中心对称设置。

254.在一些示例中,如图8所示,第一拱形区gx1、第二拱形区gx2或第三拱形区gx3在驱动基板510上的正投影与凸起部525b在驱动基板510上的正投影交叠,平坦区ptq在驱动基板510上的正投影与主体部525a在驱动基板510上的正投影交叠。也就是说,各个子无机封装层7100的第一拱形区gx1、第二拱形区gx2或第三拱形区gx3在驱动基板510上的正投影与凸起部525b在驱动基板510上的正投影交叠,各个子无机封装层7100的平坦区ptq在驱动基板510上的正投影与主体部525a在驱动基板510上的正投影交叠;并且,各个子无机封装层7100的第一拱形区gx1、第二拱形区gx2和第三拱形区gx3与不同的阳极525的凸起部525b交叠。由此,各个子像素边缘的光可经过第一拱形区、第二拱形区或第三拱形区的折射而会聚到黑矩阵上,从而可避免相邻子像素之间的串扰。需要说明的是,上述的黑矩阵可为通常的黑矩阵或者至少两个彩色滤光片交叠而形成的光透过率较低,并起到黑矩阵的作用的结构。

255.在一些示例中,如图8所示,平坦区ptq在第二方向上的尺寸为l,第二拱形区gx2的中心和第三拱形区gx3的中心在第二方向上的距离为第一距离d1,第一拱形区gx1的中心和第二拱形区gx2的中心在第二方向上的距离为第二距离d2,第一拱形区gx1、第二拱形区gx2和第三拱形区gx3的曲率半径均为r,第一距离d1满足以下公式:d2 ≤ (l+d1) 《 (l+r)。

256.在本示例提供的显示基板中,通过使得第一距离d1满足上述的公式,可在提高像素密度或者开口率的同时,降低相邻子像素之间的串扰,从而可获得一个较好的显示效果。需要说明的是,上述的曲率半径为平均曲率半径,即对应弧线的平均曲率的倒数。例如,上述的第二方向为从凸起部到主体部的方向或从主体部到凸起部的方向,第二方向平行于驱动基板远离阳极层的表面。

257.在一些示例中,如图8所示,平坦区ptq在第二方向上的尺寸为l,第二拱形区gx2的中心和第三拱形区gx3的中心在第二方向上的距离为第一距离d1,第一拱形区gx1的中心和第二拱形区gx2的中心在第二方向上的距离为第二距离d2,第一拱形区gx1、第二拱形区gx2和第三拱形区gx3的曲率半径均为r,第一距离d1满足以下公式: (l+d1) ≤ d2 《 (l+r)。

258.在本示例提供的显示基板中,通过使得第一距离d1满足上述的公式,可在提高像素密度或者开口率的同时,降低相邻子像素之间的串扰,从而可获得一个较好的显示效果。

259.例如,上述的第二方向为从凸起部到主体部的方向或从主体部到凸起部的方向,第二方向平行于驱动基板远离阳极层的表面。

260.在一些示例中,如图8所示,在各子无机封装层7100中,第一拱形区gx1、第二拱形区gx2或第三拱形区gx3远离驱动基板510的表面与驱动基板510之间的距离大于平坦区ptq远离驱动基板510的表面与驱动基板510之间的距离。由此,第一拱形区gx1、第二拱形区gx2或第三拱形区gx3为向上拱起的结构。

261.在一些示例中,如图8所示,双拱间隔区jgq在驱动基板510上的正投影与相邻两个阳极525之间的间隔区522在驱动基板510上的正投影交叠。

262.在一些示例中,如图8所示,多个子无机封装层7100包括:第一子无机封装层711、第二子无机封装层712、第三子无机封装层713和第四子无机封装层714;第一子无机封装层711位于阴极层550远离驱动基板510的一侧;第二子无机封装层712位于第一子无机封装层711远离驱动基板510的一侧;第三子无机封装层713位于第二子无机封装层711远离驱动基板510的一侧;以及第四子无机封装层714位于第三子无机封装层713远离驱动基板510的一侧。

263.在一些示例中,如图8所示,第一子无机封装层711的折射率小于第二子无机封装层712的折射率,第四子无机封装层714的折射率小于第三子无机封装层713的折射率。由此,发光功能层540发出的出射光从折射率较小的第一子无机封装层711进入折射率较大的第二子无机封装层712时,出射光会在第一子无机封装层711和第二子无机封装层712之间的界面发生折射,从而可降低出射光扩散角度,从而可在显示基板的内部减少或避免相邻子像素之间的串扰;然后,出射光再从折射率较大的第三子无机封装层713进入折射率较小的第四子无机封装层714,并在它们之间的界面发生折射,此时出射光的扩散角度增大,但是由于出射光已经接近显示基板的出光面,不会对相邻子像素造成串扰。

264.在一些示例中,如图8所示,第二子无机封装层712的折射率与第三子无机封装层713的折射率相等。此时,第二子无机封装层712和第三子无机封装层713可采用相同的材料制作。当然,本公开实施例包括但不限于此,第二子无机封装层的折射率与第三子无机封装层的折射率也可不等。

265.在一些示例中,如图8所示,第一子无机封装层711和第二子无机封装层712采用不同的材料制作;第四子无机封装层714和第三子无机封装层713可采用不同的材料制作。

266.例如,第一子无机封装层711采用氧化硅或氮氧化硅材料制作,第二子无机封装层712采用氮化硅材料制作;第四子无机封装层714采用氧化硅材料制作,第三子无机封装层713采用氮化硅材料制作。

267.在一些示例中,如图8所示,第一子无机封装层711和第四子无机封装层714可采用相同的材料制作,也可采用不同的材料制作。

268.例如,第一子无机封装层711和第四子无机封装层714均采用氧化硅材料制作;或者,第一子无机封装层711采用氮氧化硅材料制作,第四子无机封装层714采用氧化硅材料制作。

269.在一些示例中,如图8所示,第一子无机封装层711的第一拱形区gx1远离衬底512的上表面具有第一曲率半径,第二子无机封装层712的第一拱形区gx1远离衬底512的上表面具有第二曲率半径,第三子无机封装层713的第一拱形区gx1远离衬底512的上表面具有第三曲率半径,第四子无机封装层714的第一拱形区gx1远离衬底512的上表面具有第四曲率半径,第一曲率半径小于第二曲率半径,第二曲率半径小于第三曲率半径,第三曲率半径小于第四曲率半径。也就是说,在远离驱动基板510的方向上,各个子无机封装层的第一拱形区的曲率半径逐渐增大。

270.在一些示例中,如图8所示,与各子无机封装层的第一拱形区远离衬底的上表面的曲率半径满足的关系类似,各子无机封装层的第二拱形区远离衬底的上表面的曲率半径在远离驱动基板的方向上也逐渐增大。

271.在一些示例中,如图8所示,与各子无机封装层的第一拱形区远离衬底的上表面的

曲率半径满足的关系类似,各子无机封装层的第三拱形区远离衬底的上表面的曲率半径在远离驱动基板的方向上也逐渐增大。

272.在一些示例中,如图8所示,第一子无机封装层711的第一拱形区gx1,第二拱形区gx2和第三拱形区gx3的形状相同;第二子无机封装层712的第一拱形区gx1,第二拱形区gx2和第三拱形区gx3的形状相同;第三子无机封装层713的第一拱形区gx1,第二拱形区gx2和第三拱形区gx3的形状相同;第四子无机封装层714的第一拱形区gx1,第二拱形区gx2和第三拱形区gx3的形状相同。

273.在一些示例中,如图8所示,第四子无机封装层714的第一拱形区的虚设圆心位于第一子无机封装层711远离衬底512的上表面和第四子无机封装层714靠近衬底512的下表面之间。需要说明的是,上述的虚设圆心是指以第一拱形区远离衬底的上表面的弧线作虚拟圆形的圆心。

274.在一些示例中,如图8所示,第一子无机封装层711在垂直于驱动基板510的方向上具有第一厚度th1,第二子无机封装层712在垂直于驱动基板510的方向上具有第二厚度th2,第三子无机封装层713在垂直于驱动基板510的方向上具有第三厚度th3,第四子无机封装层714在垂直于驱动基板510的方向上具有第四厚度th4,第一厚度th1大于第二厚度th2,第二厚度th2大于第三厚度th3,第三厚度th3大于第四厚度th4。也就是说,在远离驱动基板510的方向上,各个子无机封装层的厚度逐渐减小。

275.在一些示例中,如图8所示,第一厚度th1与第二厚度th2的差值和第三厚度th3与第四厚度th4的差值的比例范围为1.5-2倍;也就是说,第一厚度th1、第二厚度th2、第三厚度th3和第四厚度th4满足以下公式:th1-th2=m*(th3-th4),m的取值范围为1.2-2。由此,该显示基板可更好地避免相邻子像素产生串扰。

276.在一些示例中,如图8所示,第二厚度th2和第三厚度th3之和与第一厚度th1的比例范围为0.8

ꢀ‑ꢀ

1.2;也就是说,第一厚度th1、第二厚度th2和第三厚度th3满足以下公式:(th2+th3)=n*th1,n的取值范围为0.8-1.2。由此,该显示基板可更好地避免相邻子像素产生串扰。

277.在一些示例中,如图8所示,第一厚度的范围为1000-1200纳米,第二厚度的范围为500-660纳米,第三厚度的范围480-560纳米,第四厚度的范围为180-260纳米。

278.在一些示例中,第一子无机封装层的材料包括氧化硅或氮氧化硅,第二子无机封装层的材料包括氮化硅,第三子无机封装层的材料包括氮化硅,第四子无机封装层的材料包括氧化硅。当然,本公开实施例包括但不限于此,各个子无机封装层的材料也可为其他合适的材料。

279.在一些示例中,第一厚度为1100纳米,第二厚度的范围为580纳米,第三厚度的范围520纳米,第四厚度的范围为220纳米。当然,本公开实施例包括但不限于此,各个子无机封装层的厚度还可为其他数值。

280.在一些示例中,如图8所示,封装层560还包括有机封装层720,有机封装层720位于无机封装层710远离驱动基板510的一侧。有机封装层720包括第一区域7201、第二区域7202和第三区域7203,第一区域7201的平均厚度小于第二区域7202的平均厚度,第二区域7202的平均厚度小于第三区域7203的平均厚度。由此,该有机封装层可更好地与后续形成的具有不同厚度的彩膜片进行匹配。

281.在一些示例中,如图8所示,该显示基板500还包括彩膜层570,彩膜层570位于封装层560远离驱动基板510的一侧;彩膜层570包括第一彩色滤光片571、第二彩色滤光片572和第三彩色滤光片573。

282.例如,第一彩色滤光片571、第二彩色滤光片572和第三彩色滤光片573可为不同颜色的彩色滤光片。

283.例如,第一彩色滤光片571、第二彩色滤光片572和第三彩色滤光片573可分别具有不同的厚度。当然,本公开实施例包括但不限于此。

284.在一些示例中,如图8所示,第一彩色滤光片571和第二彩色滤光片572存在第一交叠区op1,第二彩色滤光片572和第三彩色滤光片573存在第二交叠区op2,第三彩色滤光片573和第一彩色滤光片571存在第三交叠区op3。当两个不同颜色的滤光片产生交叠时,交叠区的光透过率较低,因此可作为黑矩阵进行使用。由此,该显示基板的第一交叠区、第二交叠区和第三交叠区均可作为黑矩阵使用,起到遮光的效果。当然,本公开实施例包括但不限于此,相邻的彩色滤光片也可不交叠,额外在相邻的彩色滤光片之间形成黑矩阵。

285.在一些示例中,如图8所示,第一交叠区op1、第二交叠区op2和第三交叠区op3在驱动基板510上的正投影与相邻两个阳极525之间的间隔区522在驱动基板510上的正投影交叠,从而可作为黑矩阵使用,起到遮光的效果。需要说明的是,图8所示的显示基板仅采用了两个彩色滤光片进行交叠的方式来形成相当于黑矩阵的交叠区,但是本公开实施例提供的显示基板还可采用三个彩色滤光片进行交叠的方式来形成相当于黑矩阵的交叠区。

286.在一些示例中,如图8所示,第一交叠区op1、第二交叠区op2和第三交叠区op3在驱动基板510上的正投影与凸起部525b在驱动基板510上的正投影交叠。

287.在一些示例中,如图8所示,第一交叠区op1在第二方向上的尺寸大于第二交叠区op2在第二方向上的尺寸,第二交叠区op2在第二方向上的尺寸大于第三交叠区op3在第二方向上的尺寸。

288.在一些示例中,如图8所示,第一交叠区op1在第二方向上的尺寸范围为400-600纳米,第二交叠区op2在第二方向上的尺寸范围为250-350纳米,第三交叠区op3在第二方向上的尺寸范围为100-200纳米。

289.在一些示例中,如图8所示,第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸大于第二彩色滤光片572在垂直于驱动基板510的方向上的平均尺寸,且小于第三彩色滤光片573在垂直于驱动基板510的方向上的平均尺寸。需要说明的是,上述的平均尺寸是指彩色滤光片上各个部分在垂直于驱动基板的方向上的尺寸的算术平均值。

290.在一些示例中,如图8所示,第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸的范围为2.3-2.6微米,第二彩色滤光片572在垂直于驱动基板510的方向上的平均尺寸的范围为1.7-1.95微米,第三彩色滤光片573在垂直于驱动基板510的方向上的平均尺寸的范围为2.3-2.7微米。

291.在一些示例中,如图8所示,第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸与第二彩色滤光片572在垂直于驱动基板510的方向上的平均尺寸的差值和第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸与第三彩色滤光片573在垂直于驱动基板510的方向上的平均尺寸的差值之比的范围为2

ꢀ‑ꢀ

3。

292.图9为本公开一实施例提供的一种显示基板中的第一彩色滤光片的示意图。如图8

和图9所示,第一彩色滤光片571包括第一边缘部571a、第二边缘部571b和位于第一边缘部571a和第二边缘部571b之间的中间部571c,中间部571c在垂直于驱动基板510的方向上的平均尺寸小于第一边缘部571a在垂直于驱动基板510的方向上的平均尺寸和第二边缘部571b在垂直于驱动基板510的方向上的平均尺寸。

293.在一些示例中,如图8所示,第一彩色滤光片571包括与第二彩色滤光片572接触的第一接触面571c,第二彩色滤光片572包括与第三彩色滤光片573接触的第二接触面572c,第三彩色滤光片573包括与第一彩色滤光片571接触的第三接触面573c,第一接触面571c在垂直于驱动基板510的第二方向上的尺寸与第二接触面572c在第二方向上的尺寸相等,且小于第三接触面573c在第二方向上的尺寸。

294.在一些示例中,如图8所示,第一彩色滤光片571与驱动基板510远离阳极层520的表面的距离大于第三彩色滤光片573与驱动基板510远离阳极层520的表面的距离,且小于第二彩色滤光片572与驱动基板510远离阳极层520的表面的距离。

295.在一些示例中,如图8所示,第一彩色滤光片为红色滤光片,第二彩色滤光片为绿色滤光片,第三彩色滤光片为蓝色滤光片。当然,本公开实施例包括但不限于此,第一彩色滤光片、第二彩色滤光片和第三彩色滤光片也可为其他颜色的彩色滤光片。

296.在一些示例中,彩膜层570的材料包括干燥剂,从而可起到防止外界水氧进入彩膜层下方的膜层的效果。

297.在一些示例中,彩膜层570包括铝元素。

298.在一些示例中,如图8所示,该显示基板500还包括保护层580,位于彩膜层570远离驱动基板510的一侧。保护层580可以起到保护彩膜层570的效果,使得彩膜层570的滤光性能在长期使用过程中保持稳定,从而可提高显示基板的显示质量。

299.在一些示例中,如图8所示,该显示基板500还包括玻璃盖板590,位于彩膜层570远离驱动基板510的一侧。

300.在一些示例中,如图8所示,第一子无机封装层711的平坦区ptq在第二方向上具有第一宽度,第二子无机封装层712的平坦区ptq在第二方向上具有第二宽度,第三子无机封装层713的平坦区ptq在第二方向上具有第三宽度,第四子无机封装层714的平坦区ptq在第二方向上具有第四宽度,第一宽度大于第二宽度,第二宽度大于第三宽度,第三宽度大于第四宽度。也就是说,第一宽度、第二宽度、第三宽度和第四宽度逐渐减小。

301.图10为本公开一实施例提供的另一种显示基板的局部结构示意图。如图8和图10所示,第一子无机封装层711的平坦区ptq靠近第二拱形区gx2的边缘、第二子无机封装层712的平坦区ptq靠近第二拱形区gx2的边缘、第三子无机封装层713的平坦区ptq靠近第二拱形区gx2的边缘和第四子无机封装层714的平坦区ptq靠近第二拱形区gx2的边缘的第一连线l1与驱动基板510远离阳极层520的表面之间的夹角为第一夹角;第一子无机封装层711的第二拱形区gx2的顶点、第二子无机封装层712的第一拱形区gx1的顶点、第三子无机封装层713的第二拱形区gx2的顶点和第四子无机封装层714的第二拱形区gx2的顶点的第二连线l2与驱动基板510远离阳极层520的表面之间的夹角为第二夹角,第一夹角小于第二夹角。

302.在一些示例中,如图8和图10所示,第一夹角的范围为60-85度,第二夹角的范围为85-89度。

303.在一些示例中,如图8和图10所示,第一连线l1和第二连线的l2交点位于驱动基板510之内。

304.图11为本公开一实施例提供的一种驱动基板的结构示意图。如图11所示,该驱动电路514包括半导体层102、第一导电层301、第二导电层302、第三导电层303和第四导电层304;半导体层102位于衬底512之中;第一导电层301位于半导体层102上;第二导电层302位于第一导电层301远离衬底512的一侧;第三导电层303位于第二导电层302远离衬底512的一侧;第四导电层304第三导电层303远离衬底512的一侧。

305.在一些示例中,如图11所示,第一连线l1和第二连线l2的交点位于第三导电层303远离衬底512的上表面与阳极层520之间。

306.在一些示例中,如图11所示,第一连线l1与第二连线l2的交点与像素限定层530的突起结构535远离衬底512的上表面的顶点之间距离大于第一子无机封装层711在第一方向上的厚度。

307.在一些示例中,如图11所示,第一连线l1与第二连线l2的交点与像素限定层530的突起结构535远离衬底512的上表面的顶点之间距离小于第一子无机封装层711在第一方向上的厚度和第二子无机封装层712在第一方向上的厚度之和。

308.在一些示例中,如图11所示,第一子无机封装层711的第二拱形区gx2靠近双拱间隔区jgq的边缘、第二子无机封装层712的第二拱形区gx2靠近双拱间隔区jgq的边缘、第三子无机封装层713的第二拱形区gx2靠近双拱间隔区jgq的边缘和第四子无机封装层714的第二拱形区gx2靠近双拱间隔区jgq的边缘的第三连线l3与驱动基板510远离阳极层520的表面之间的夹角为第三夹角,第三夹角小于第二夹角。

309.在一些示例中,如图11所示,第一连线l1和第三连线l3的交点位于第二导电层302远离衬底512的上表面与第三导电层303靠近衬底512的下表面之间。

310.在一些示例中,如图11所示,第二连线l2和第三连线l3的交点位于第一导电层301靠近衬底512的下表面与衬底512远离第一导电层301的下表面之间。

311.在一些示例中,如图11所示,第一子无机封装层711的第三拱形区gx3远离双拱间隔区jgq的边缘、所述第二子无机封装层712的第三拱形区gx3远离双拱间隔区jgq的边缘、所述第三子无机封装层713的第三拱形区gx3远离双拱间隔区jgq的边缘和所述第四子无机封装层714的第三拱形区gx3远离双拱间隔区jgq的边缘的第四连线l4与驱动基板510远离阳极层520的表面之间的夹角为第四夹角,第四夹角小于第二夹角。

312.在一些示例中,如图11所示,第一连线l1与第四连线l4的交点位于衬底512远离第一导电层301的一侧。

313.在一些示例中,如图11所示,第三连线l3与第四连线l4的交点位于第二导电层302远离衬底512的上表面与第三导电层303靠近衬底512的下表面之间。

314.图12为本公开一实施例提供的一种显示基板的局部结构示意图。如图12所示,彩膜层570还包括黑矩阵574,位于第一彩色滤光片571、第二彩色滤光片572和第三彩色滤光片573中任意相邻的两个之间。

315.在一些示例中,如图12所示,黑矩阵574在驱动基板510上的正投影与相邻两个阳极525之间的间隔区522在驱动基板510上的正投影交叠。

316.在一些示例中,如图12所示,该显示基板500还包括保护层580,位于彩膜层570远

离驱动基板510的一侧。保护层580可以起到保护彩膜层570的效果,使得彩膜层570的滤光性能在长期使用过程中保持稳定,从而可提高显示基板的显示质量。

317.在一些示例中,如图12所示,该显示基板500还包括玻璃盖板590,位于彩膜层570远离驱动基板510的一侧。

318.本公开一实施例还提供一种显示装置,包括上述任一项所述的显示基板。图13为本公开一实施例提供的一种显示装置的示意图。如图13所示,该显示装置900包括上述的显示基板500。由此,该显示装置具有与显示基板的有益技术效果对应的技术效果。

319.例如,在该显示基板中,由于阳极包括主体部和凸起部,并且凸起部在垂直于驱动基板的方向上的尺寸大于主体部在垂直于驱动基板的方向上的尺寸,因此位于两个阳极之间,且与阳极的边缘部分交叠的像素限定层可形成与凸起部对应的突起结构。在形成发光功能层时,发光功能层中的至少部分子功能层(例如电荷产生层)可更好地在突起结构所在的位置断开,即相邻两个阳极对应的发光部中的至少部分子功能层不连接,从而可有效地避免相邻子像素之间的漏电和串扰。另一方面,此时的像素限定层的突起结构的高度也更高,从而可更好地起到像素限定的作用,从光学上减少和避免相邻子像素之间的串扰。由此,该显示基板也可减少甚至避免相邻子像素之间的串扰,因而具有较好的显示品质。

320.又例如,由于显示基板中的驱动基板可采用半导体制作工艺进行制作,从而可将用于驱动各个像素进行发光和显示的像素驱动电路集成在驱动基板之中。由此,该显示装置可提供一种微型的显示装置,并具有分辨率高、亮度高、色彩丰富、驱动电压低、响应速度快、功耗低等优点。

321.例如,该显示装置900可为可穿戴显示装置,例如智能手表、智能眼镜等。当然,本公开实施例包括但不限于此,该显示装置也可为其他具有显示功能的电子产品,例如手机、电视、导航仪、电子相册、电子画框、电脑显示器等。

322.图14为本公开一实施例提供的一种显示装置的平面图。如图14所示,该显示装置900包括显示区910和位于显示区910周围的周边区920;该显示装置900的周边区920包括走线区930。显示区910可用于进行发光显示,而走线区930可用于将各种驱动线或者信号线从显示区910引出。

323.图15为本公开一实施例提供的另一种显示装置的示意图。如图15所示,该显示装置900包括的显示基板500不包括彩膜层。此时,该显示装置900还包括对置基板800,对置基板800与显示基板500相对设置;对置基板800包括玻璃盖板810和位于玻璃盖板810上的彩膜层570,彩膜层570包括第一彩色滤光片571、第二彩色滤光片572和第三彩色滤光片573。由此,可先分别制作显示基板和对置基板,然后再将显示基板和对置基板对准,从而形成上述的显示装置。并且,该显示装置具有与显示基板的有益技术效果对应的技术效果。

324.例如,在该显示基板中,由于阳极包括主体部和凸起部,并且凸起部在垂直于驱动基板的方向上的尺寸大于主体部在垂直于驱动基板的方向上的尺寸,因此位于两个阳极之间,且与阳极的边缘部分交叠的像素限定层可形成与凸起部对应的突起结构。在形成发光功能层时,发光功能层中的至少部分子功能层(例如电荷产生层)可更好地在突起结构所在的位置断开,即相邻两个阳极对应的发光部中的至少部分子功能层不连接,从而可有效地避免相邻子像素之间的漏电和串扰。另一方面,此时的像素限定层的突起结构的高度也更高,从而可更好地起到像素限定的作用,从光学上减少和避免相邻子像素之间的串扰。由

此,该显示基板也可减少甚至避免相邻子像素之间的串扰,因而具有较好的显示品质。

325.又例如,由于显示基板中的驱动基板可采用半导体制作工艺进行制作,从而可将用于驱动各个像素进行发光和显示的像素驱动电路集成在驱动基板之中。由此,该显示装置可提供一种微型的显示装置,并具有分辨率高、亮度高、色彩丰富、驱动电压低、响应速度快、功耗低等优点。

326.例如,该显示装置900可为可穿戴显示装置,例如智能手表、智能眼镜等。当然,本公开实施例包括但不限于此,该显示装置也可为其他具有显示功能的电子产品,例如手机、电视、导航仪、电子相册、电子画框、电脑显示器。

327.在一些示例中,如图15所示,第一彩色滤光片571和第二彩色滤光片572存在第一交叠区op1,第二彩色滤光片572和第三彩色滤光片573存在第二交叠区op2,第三彩色滤光片573和第一彩色滤光片571存在第三交叠区op3。当两个不同颜色的滤光片产生交叠时,交叠区的光透过率较低,因此可作为黑矩阵进行使用。由此,该显示基板的第一交叠区、第二交叠区和第三交叠区均可作为黑矩阵使用,起到遮光的效果。当然,本公开实施例包括但不限于此,相邻的彩色滤光片也可不交叠,额外在相邻的彩色滤光片之间形成黑矩阵。

328.在一些示例中,如图15所示,第一交叠区op1、第二交叠区op2和第三交叠区op3在驱动基板510上的正投影与相邻两个阳极525之间的间隔区522在驱动基板510上的正投影交叠。需要说明的是,图14所示的显示基板仅采用了两个彩色滤光片进行交叠的方式来形成相当于黑矩阵的交叠区,但是本公开实施例提供的显示基板还可采用三个彩色滤光片进行交叠的方式来形成相当于黑矩阵的交叠区。

329.在一些示例中,如图15所示,第一交叠区op1在第二方向上的尺寸大于第二交叠区op2在第二方向上的尺寸,第二交叠区op2在第二方向上的尺寸大于第三交叠区op3在第二方向上的尺寸。

330.在一些示例中,如图15所示,第一交叠区op1在第二方向上的尺寸范围为400-600纳米,第二交叠区op2在第二方向上的尺寸范围为250-350纳米,第三交叠区op3在第二方向上的尺寸范围为100-200纳米。

331.在一些示例中,如图15所示,第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸大于第二彩色滤光片572在垂直于驱动基板510的方向上的平均尺寸,且小于第三彩色滤光片573在垂直于驱动基板510的方向上的平均尺寸。

332.在一些示例中,如图15所示,第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸的范围为2.3-2.6微米,第二彩色滤光片572在垂直于驱动基板510的方向上的平均尺寸的范围为1.7-1.95微米,第三彩色滤光片573在垂直于驱动基板510的方向上的平均尺寸的范围为2.3-2.7微米。

333.在一些示例中,如图15所示,第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸与第二彩色滤光片572在垂直于驱动基板510的方向上的平均尺寸的差值和第一彩色滤光片571在垂直于驱动基板510的方向上的平均尺寸与第三彩色滤光片573在垂直于驱动基板510的方向上的平均尺寸的差值之比的范围为2

ꢀ‑ꢀ

3。

334.在一些示例中,如图10和图15所示,第一彩色滤光片571包括第一边缘部571a、第二边缘部571b和位于第一边缘部571a和第二边缘部571b之间的中间部571m,中间部571m在垂直于驱动基板510的方向上的平均尺寸小于第一边缘部571a在垂直于驱动基板510的方

向上的平均尺寸和第二边缘部571b在垂直于驱动基板510的方向上的平均尺寸。

335.在一些示例中,如图15所示,第一彩色滤光片571包括与第二彩色滤光片572接触的第一接触面571c,第二彩色滤光片572包括与第三彩色滤光片573接触的第二接触面572c,第三彩色滤光片573包括与第一彩色滤光片571接触的第三接触面573c,第一接触面在垂直于驱动基板510的第二方向上的尺寸与第二接触面在第二方向上的尺寸相等,且小于第三接触面在第二方向上的尺寸。

336.在一些示例中,如图15所示,第一彩色滤光片571与驱动基板510远离阳极层520的表面的距离大于第三彩色滤光片573与驱动基板510远离阳极层520的表面的距离,且小于第二彩色滤光片572与驱动基板510远离阳极层520的表面的距离。

337.在一些示例中,如图15所示,第一彩色滤光片为红色滤光片,第二彩色滤光片为绿色滤光片,第三彩色滤光片为蓝色滤光片。当然,本公开实施例包括但不限于此,第一彩色滤光片、第二彩色滤光片和第三彩色滤光片也可为其他颜色的彩色滤光片。

338.在一些示例中,彩膜层570的材料包括干燥剂,从而可起到防止外界水氧进入彩膜层下方的膜层的效果。

339.在一些示例中,彩膜层570包括铝元素。

340.本公开至少一个实施例还提供一种显示基板。图16为本公开一实施例提供的一种显示基板的平面示意图。如图16所示,该显示装置900包括设置在显示区域910中的呈阵列排布的多个像素单元pu,例如,该多个像素单元pu中的至少一个可以包括一个上述的驱动电路和一个上述的阳极。

341.例如,如图16所示,该显示装置900还包括制备在衬底中的行驱动电路200,该行驱动电路200被配置为向显示装置900中的多个像素单元pu中的驱动电路提供第一扫描信号scan1、第二扫描信号scan2以及发光控制信号en。例如,该行驱动电路200设置在围绕显示区域910的周边区域920中。

342.本公开至少一个实施例还提供一种显示基板。图17为本公开一实施例提供的一种显示基板的局部剖面示意图。如图17所示,该显示基板500包括驱动基板510,该驱动基板510包括驱动电路514,该驱动电路514与阳极525电连接,以用于与阳极525接触的发光功能层540发光。需要说明的是,图17所示的显示基板中阳极、发光功能层、封装层等结构可采用上述实施例提供的显示基板中的相关设计。

343.例如,如图17所示,该驱动基板510包括晶体管t,晶体管t包括栅电极g、源电极s和漏电极d。三个电极分别对应三个电极连接部。例如,栅电极g与栅电极连接部610g电连接,源电极s与源电极连接部610s电连接,漏电极d与漏电极连接部610d电连接。例如,三个电极均是通过钨过孔605与三个电极连接部对应电连接。

344.例如,如图17所示,源电极连接部610s通过钨过孔与阳极525电连接。例如,源电极连接部610s通过钨过孔与金属反射层593电连接,同时,阳极525通过无机绝缘层624中的过孔624a与金属反射层593电连接。在晶体管t处于导通状态,由电源线提供的电信号可经过晶体管t的源电极s、源电极连接部610s、金属反射层593传输到阳极525。由于阳极525与阴极550之间形成电压差,在二者之间形成电场,空穴和电子被注入到发光功能层540中,发光功能层540在该电场作用下发光。可以理解的是,晶体管t中,源电极s和漏电极d的位置可互换(对应地,源电极连接部610s和漏电极连接部610d的位置也可互换)。

345.例如,栅电极连接部610g、源电极连接部610s和漏电极连接部610d的材料可以包括金属材料。例如,如图17所示,在栅电极连接部610g、源电极连接部610s和漏电极连接部610d每个的至少一侧(例如上侧和/或下侧)可以设置抗氧化层607,这样能有效防止这些电极连接部被氧化,提高其导电性能。

346.例如,如图17所示,该显示基板500还包括用于限定发光功能层540的像素限定层530,该像素限定层530将有机发光功能层540限定在其像素开口535中,避免彼此相邻的子像素之间的串扰。

347.需要说明的是,在图17所示的显示基板500中,无机绝缘层624中的过孔624a可以设置在阳极525与金属反射层593的边缘区域之间。例如,在一些示例中,发光功能层540在驱动基板510上的正投影和过孔624a在驱动基板510上的正投影均位于金属反射层593在驱动基板510上的正投影内,同时,发光功能层540在驱动基板510上的正投影和过孔624a在驱动基板510上的正投影之间不存在交叠,从而金属反射层对发光功能层540发出的光进行反射时,过孔624a对该反射过程基本没有影响。

348.图18为本公开一实施例提供的一种显示基板中驱动电路的等效示意图;图19为本公开一实施例提供的一种显示基板中驱动电路的平面示意图。如图18和图19所示,该驱动电路514包括驱动晶体管140、第一晶体管110、第二晶体管120以及第三晶体管130。需要说明的是,在一些实施例中,驱动电路也可以不包括第三晶体管130,本公开的实施例对此不作限定。

349.例如,驱动晶体管140包括控制极143、第一极141和第二极142,且该驱动晶体管140被配置为根据驱动晶体管140的控制极143的电压,控制流经驱动晶体管140的第一极141和驱动晶体管140的第二极142的用于驱动发光元件le发光的驱动电流。发光元件le可以根据驱动电流的大小发出不同强度的光。

350.需要说明的是,本公开的实施例中采用的晶体管的源极、漏极在结构上可以是对称的,所以其源极、漏极在结构上可以是没有区别的。在本公开的实施例中,为了区分晶体管除栅极之外的两极,直接描述了其中一极为第一极,另一极为第二极,所以本公开的实施例中全部或部分晶体管的第一极和第二极根据需要是可以互换的。例如,本公开的实施例中所述的晶体管的第一极可以为源极,第二极可以为漏极;或者,晶体管的第一极为漏极,第二极为源极。以下各实施例以晶体管的第一极为漏极,第二极为源极为例进行说明,不再赘述。

351.例如,第一晶体管110连接到驱动晶体管140的控制极143,且被配置为响应于第一扫描信号scan1将数据信号data写入驱动晶体管140的控制极143。

352.例如,第二晶体管120连接到驱动晶体管140的控制极143,且被配置为响应于第二扫描信号scan2将数据信号data写入驱动晶体管140的控制极143。

353.例如,第三晶体管130连接到驱动晶体管140的第一极141,且被配置为响应于发光控制信号en将第一电源电压elvdd施加到驱动晶体管140的第一极141。例如,本公开的实施例中的第一电源电压elvdd为高电平电压,例如,第一电源电压elvdd为5v。

354.如图18所示,在一些实施例中,第一晶体管110的第一极111(例如,漏极)以及第二晶体管120的第一极121(例如,漏极)连接以得到公共电极,并通过该公共电极与驱动晶体管140的控制极143连接。

355.在上述实施例中,还提供了第一扫描信号线sl1、第二扫描信号线sl2、数据线dl、第一电源电压线vl1以及发光控制线el等以提供相应的电信号。第一晶体管110的控制极113被配置为从第一扫描信号线sl1接收第一扫描信号scan1,第一晶体管110的第二极112(例如,源极)被配置为从数据线dl接收数据信号data。第二晶体管120的控制极123被配置为从第二扫描信号线sl2接收第二扫描信号scan2,第二晶体管120的第二极122(例如,源极)被配置为从数据线dl接收数据信号data。第三晶体管130的控制极133被配置为从发光控制线el接收发光控制信号en,第三晶体管130的第一极131(例如,漏极)被配置为从第一电源电压线vl1接收第一电源电压elvdd,第三晶体管130的第二极132(例如,源极)和驱动晶体管140的第一极141(例如,漏极)连接。

356.驱动晶体管140的第二极142(例如,源极)被配置为和发光元件le的第一极连接。例如,当发光元件le为oled时,驱动晶体管140的第二极142可以和该oled的阳极连接。例如,该发光元件le的第二极被配置为接收第四电源电压vcom。例如,本公开的实施例中的第四电源电压vcom为低电平电压。

357.例如,在本公开的实施例中,发光元件le可以采用oled,当多个像素单元构成显示面板中的像素阵列时,多个像素单元中的多个发光元件oled的第二极(例如,阴极)可以电连接在一起,例如分别连接到同一个电极或一体形成,以接收第四电源电压vcom,即多个像素单元中的多个发光元件oled采用共阴极连接方式。

358.例如,发光元件oled可以为各种类型,例如顶发射、底发射等,可以发红光、绿光、蓝光或白光等,本公开的实施例对此不作限制。

359.例如,如图18所示,驱动电路还包括存储电容cst,以存储写入到驱动晶体管140的控制极143的数据信号data,从而使得驱动晶体管140可以根据该存储的数据信号data的电压控制驱动发光元件le的驱动电流的大小。存储电容cst的第一极和驱动晶体管140的控制极143连接,存储电容cst的第二极被配置为接收第三电源电压avss。例如,本公开的实施例中的第三电源电压avss为低电平电压。需要说明的是,在本公开的实施例中,第三电源电压avss可以和第四电源电压vcom相同,例如,第三电源电压avss可以和第四电源电压vcom均接地,本公开的实施例包括但不限于此。

360.如图18所示,在本公开的一些实施例中,第一晶体管110可以采用p型mos晶体管,第二晶体管120、第三晶体管130以及驱动晶体管140可以采用n型mos晶体管,例如,第一晶体管110、第二晶体管120、第三晶体管130以及驱动晶体管140形成在衬底中。

361.例如,如图18所示,第一晶体管110的第三级被配置为接收第二电源电压vdd,例如,第一晶体管110的第三级和第二电源电压线vl2连接以接收第二电源电压vdd。

362.例如,第二晶体管120、第三晶体管130以及驱动晶体管140的第三极被配置为接地(gnd)。需要说明的是,在本公开的实施例中,一个晶体管的第三极为与该晶体管的控制极(栅极)113相对的一极,以下各实施例与此相同,不再赘述。

363.在本公开的实施例中,由于第一晶体管110和第二晶体管120采用具有相反半导体型的mos晶体管,所以第一晶体管110和第二晶体管120可以构成具有互补特性的传输门开关。在这种情形中,例如,可以使得提供至第一晶体管110的第一扫描信号scan1和提供至第二晶体管120的第二扫描信号scan2彼此互为反相信号,这样就可以保证第一晶体管110和第二晶体管120在同一时刻总有一个处于导通状态,从而可以没有电压损失地将数据信号

data传输至存储电容cst,从而可以提高该驱动电路的可靠性和稳定性。

364.如图19所示,在本公开的实施例中,将沿第一晶体管110的第一极111至第一晶体管110的第二极112的方向称为第一方向d1,将沿第二晶体管120的第一极121至第二晶体管120的第二极122的方向称为第二方向d2,将沿第三晶体管130的第一极131至第三晶体管130的第二极132的方向称为第三方向d3,将沿驱动晶体管140的第一极141至驱动晶体管140的第二极142的方向称为第四方向d4。需要说明的是,图1-图15中的第一方向与本实施例提供的第一方向不同,图1-图15中的第二方向与本实施例提供的第二方向可以相同,也可以不同。

365.例如,第一方向d1和第二方向d2中的至少一个和第四方向d4相交。例如,在驱动电路包括第三晶体管130的情形下,第一方向d1、第二方向d2以及第三方向d3中的至少一个和第四方向d4相交。例如,第四方向d4为图19中从左至右的横向方向。

366.在驱动电路中,由于驱动晶体管140的尺寸相对于其它开关晶体管(例如,第一晶体管110、第二晶体管120以及第三晶体管130)一般较大,所以在布局晶体管的位置时,可以将该驱动晶体管140沿第四方向d4布置,同时使得第一方向d1、第二方向d2以及第三方向d3中的至少一个和第四方向d4相交,这样可以使得四个晶体管的布局更紧凑,从而可以减小该显示基板500所占用的布局面积,从而可以使得该显示基板500更易于实现高ppi。

367.在本公开的一些实施例中,可以使得第一方向d1和第二方向d2均和第四方向d4相交;又例如,可以使得第一方向d1、第二方向d2以及第三方向d3均和第四方向d4相交。例如,如图19所示,第四方向d4为横向方向,第一方向d1、第二方向d2以及第三方向d3均为图3中的与横向方向垂直的纵向方向。

368.例如,在本公开的一些实施中,第一方向d1和第二方向d2均和第四方向d4垂直;又例如,第一方向d1、第二方向d2以及第三方向d3均和第四方向d4垂直。对于显示装置的显示区域中的多个像素单元按照多行多列方式排布的情形,采用这种方式可以使得该显示基板500的布局更紧凑,从而可以进一步减小该显示基板500所占用的布局面积,从而可以使得该显示基板500更易于实现高ppi。

369.例如,如图19所示,第一晶体管110包括沿第一方向d1延伸的第一有源区114,第一有源区114包括第一晶体管110的第一极111、第一晶体管110的第二极112、以及第一晶体管110的第一极111和第一晶体管110的第二极112之间形成的沟道区。

370.第二晶体管120包括沿第二方向d2延伸的第二有源区124,第二有源区124包括第二晶体管120的第一极121、第二晶体管120的第二极122、以及第二晶体管120的第一极121和第二晶体管120的第二极122之间形成的沟道区。

371.第三晶体管130包括沿第三方向d3延伸的第三有源区134,第三有源区134包括第三晶体管130的第一极131、第三晶体管130的第二极132、以及第三体管130的第一极131和第三晶体管130的第二极132之间形成的沟道区。

372.驱动晶体管140包括沿第四方向d4延伸的第四有源区144,第四有源区144包括第四晶体管140的第一极141、第四晶体管140的第二极142、以及第四体管140的第一极141和第四晶体管140的第二极142之间形成的沟道区。

373.例如,本公开的实施例提供的显示基板500中的衬底为硅基衬底,上述第一有源区114、第二有源区124、第三有源区134和第四有源区144均为硅基衬底中的掺杂区,这些掺杂

区例如通过离子注入工艺或离子扩散工艺得到,对于非晶硅,p型掺杂可以通过掺杂硼(b)实现,n型掺杂可以通过掺杂磷(p)或砷(as)实现,本公开的实施例对此不作限制。

374.例如,在本公开的一些实施例中,第一有源区114与第二有源区124的掺杂类型相反。例如,第一有源区114的掺杂类型为p型,第二有源区124的掺杂类型为n型。

375.如图19所示,第一有源区114的两个端部和第二有源区124的两个端部在第四方向d4上彼此对齐,并且例如,第一有源区114的两个端部和第二有源区124彼此相邻布置。采用这种方式可以简化该显示基板500的布局设计。

376.第一有源区114沿第一方向d1的一个边缘与第二有源区124沿第二方向d2的一个边缘的连线和第四方向d4平行;第一有源区114沿第一方向d1的另一个边缘与第二有源区124沿第二方向d2的另一个边缘的连线和第四方向d4平行。采用这种方式可以简化该显示基板500的布局设计。

377.与用于非显示用途的硅基模拟cmos电路相比,本公开的实施例提供的显示基板500中的用于发光元件le的驱动电流要小1到2个数量级。驱动晶体管140在饱和状态下的电流特性为:其中,id为驱动晶体管140提供的驱动电流,w/l为驱动晶体管140的宽长比,k为一常数值,v

gs4

为驱动晶体管140的栅极和源极之间的电压差,v

th

为驱动晶体管140的阈值电压。

378.由上面的公式可以看出,要实现较低的驱动电流,则驱动晶体管140在尺寸设计时就要增大l值,这不利于减小采用该驱动晶体管140的显示基板500的布局面积。

379.本公开的一些实施例提供的驱动电路514 通过对第一有源区114、第二有源区124、第三有源区134以及第四有源区144的掺杂浓度之间的相对关系进行调整,可以改善或避免上述问题。

380.例如,第四有源区144的掺杂浓度小于第三有源区134的掺杂浓度。例如,第三有源区134的掺杂浓度约为10

17

cm-3

,第四有源区144的掺杂浓度约为10

13

cm-3

,第四有源区144的掺杂浓度比第三有源区134的掺杂浓度小4个数量级。本公开的实施例通过降低第四有源区144的掺杂浓度,在不改变驱动晶体管140的尺寸(例如,宽长比w/l不变)的情形下,可以使得驱动晶体管140输出更小的驱动电流,输出的驱动电流的变化更平缓,从而使得采用该驱动晶体管140的驱动电路驱动发光元件le(例如,oled)进行发光时的灰阶值可以获得较好的均匀性。

381.例如,在本公开的一些实施例提供的显示基板500中,第一有源区114以及第二有源区124中的至少一个的掺杂浓度大于第三有源区134的掺杂浓度。

382.例如,第一有源区114以及第二有源区124的掺杂浓度均大于第三有源区的掺杂浓度。例如,第一有源区114以及第二有源区124的掺杂浓度约为10

20

cm-3

,在这种情形下,第一有源区114以及第二有源区124的掺杂浓度比第三有源区134的掺杂浓度大3个数量级。

383.如图18所示,第一晶体管110和第二晶体管120在驱动电路里是用作开关晶体管的,所以需要具有良好的开关特性。当第一有源区114或/和第二有源区124的掺杂浓度较大时,可以获得较大的驱动电流且该驱动电流的变化更快速,从而使得该第一晶体管110或/

和第二晶体管120具有更好的开关特性。

384.例如,在本公开的实施例中,第一晶体管110为第一半导体型mos晶体管,第二晶体管、第三晶体管以及驱动晶体管均为第二半导体型mos晶体管,第一半导体型和第二半导体型相反。例如,第一半导体型为p型,第二半导体型为n型,本公开的实施例包括但不限于此。

385.如图19所示,本公开的一些实施例提供的显示基板500还包括用于传输第一扫描信号scan1的第一扫描信号线sl1以及用于传输第二扫描信号scan2的第二扫描信号线sl2,第一扫描信号线sl1与第二扫描信号线sl2平行设置。

386.例如,第一扫描信号线sl1和第一晶体管110的控制极113连接以提供第一扫描信号scan1,第二扫描信号线sl2和第二晶体管120的控制极123连接以提供第二扫描信号scan2。

387.例如,第一扫描信号线sl1以及第二扫描信号线sl2的延伸方向均与第四方向d4平行。第一扫描信号线sl1在衬底的正投影与第二扫描信号线sl2在衬底的正投影平行,例如,均和第四方向d4平行。

388.例如,驱动电路514在衬底512的正投影所在的区域为像素区域,第一扫描信号线sl1和第二扫描信号线sl2并列位于像素区域的一侧。

389.如图19所示,本公开的一些实施例提供的显示基板500还包括用于传输数据信号data的数据线dl,第二扫描信号线sl2在衬底的正投影与数据线dl在衬底的正投影至少部分重叠。例如,第二扫描信号线sl2与数据线dl在垂直于衬底的方向上重叠。例如,如图19所示,可以把图19所在的平面看做衬底所在的平面,则垂直于衬底即垂直于图19所在的平面。本公开的实施例通过使得第二扫描信号线sl2与数据线dt在垂直于衬底的方向上重叠,可以使得该数据线dl不占用额外的布局面积,从而可以进一步减小该显示基板500所占用的布局面积,更有利于实现高ppi。

390.如图19所示,本公开的一些实施例提供的显示基板500还包括用于传输第一电源电压elvdd的第一电源电压线vl1以及用于传输发光控制信号en的发光控制线el。

391.例如,第一电源电压线vl1和发光控制线el的部分延伸方向与第四方向d4平行,第一扫描信号线sl1、第二扫描信号线sl2、第一电源电压线vl1以及发光控制线el在衬底的正投影沿与第四方向d4的垂直方向依次排布。

392.需要说明的是,在本公开的一些实施例提供的显示基板500中,如图19所示,使得第一电源电压线vl1在衬底的正投影位于第二扫描信号线sl2在衬底的正投影和发光控制线el在衬底的正投影之间,由于第一电源电压线vl1传输的第一电源电压elvdd为直流信号,而第二扫描信号线sl2传输的第二扫描信号scan2以及发光控制线el传输的发光控制信号en均为跳变信号,所以采用上述排布方式可以有效屏蔽第二扫描信号scan2与发光控制信号en之间的相互干扰。

393.如图19所示,本公开的一些实施例提供的显示基板500还包括用于传输第二电源电压vdd的第二电源电压线vl2,第一晶体管110的第三极和第二电源电压线vl2电连接以接收第二电源电压vdd。例如,本公开的实施例中的第二电源电压vdd为高电平电压,例如,第二电源电压为5v。

394.例如,第一晶体管110为p型mos晶体管,其沟道区为p型掺杂。如图19所示,与第一晶体管110的控制极(栅极)113相对的第三极接收第二电源电压vdd。例如,第二晶体管120、

第三晶体管130以及驱动晶体管140均为n型mos晶体管,其沟道区为n型掺杂,第二晶体管120、第三晶体管130以及驱动晶体管140的第三极均配置为接地(gnd)。

395.例如,第二电源电压线vl2在衬底的正投影位于第一电源电压线vl1在衬底的正投影以及发光控制线el在衬底的正投影之间,且第二电源电压线vl2的部分延伸方向与第四方向d4平行。

396.如图19所示,第二电源电压线vl2在沿第四方向d4延伸时,有一个弯折区域;另外,发光控制线el在沿第四方向d4延伸时,也有一个弯折区域,且第二电源电压线vl2与发光控制线el的弯折方向不同。采用这种走线方式例如可以为下文中描述的第一转接电极ae1留出布局空间。

397.例如,如图19所示,第一晶体管110以及第二晶体管120均设置在第二扫描信号线sl2与发光控制线el之间,且第一晶体管110和第一电源电压线vl1以及第二电源电压线vl2相交,且第二晶体管120和第一电源电压线vl1以及第二电源电压线vl2相交。

398.例如,第一晶体管110的第一有源区114在衬底上的正投影以及第二晶体管120的第二有源区124在衬底上的正投影均位于第二扫描信号线sl2在衬底上的正投影与发光控制线el在衬底上的正投影之间。

399.第一晶体管110的第一有源区114在衬底上的正投影与第一电源电压线vl1在衬底上的正投影相交,且第一晶体管110的第一有源区114在衬底上的正投影与第二电源电压线vl2在衬底上的正投影相交。

400.第二晶体管120的第二有源区124在衬底上的正投影与第一电源电压线vl1在衬底上的正投影相交,且第二晶体管120的第二有源区124在衬底上的正投影与第二电源电压线vl2在衬底上的正投影相交。

401.如图19所示,本公开的一些实施例提供的显示基板500还包括设置在发光控制线el的第一侧的第一转接电极ae1,以及从发光控制线el的第一侧延伸至发光控制线el的第二侧的第二转接电极ae2。

402.例如,第二转接电极ae2在衬底的正投影与发光控制线el在衬底上的正投影交叉。第一转接电极ae1的两个端部分别和第一晶体管110的第一极111以及第二晶体管120的第一极121电连接,第一转接电极ae1和第二转接电极ae2电连接,且第二转接电极ae2和驱动晶体管140的控制极143电连接。

403.例如,第二转接电极ae2的延伸方向与第一转接电极ae1的延伸方向垂直,并且和第四方向d4垂直。

404.由于第二转接电极ae2连接存储电容cst,驱动电路在工作中该第二转接电极ae2上的电平可能会有较大的波动,该波动可能会对第一电源电压线vl1造成串扰,产生噪声。在本公开的实施例提供的显示基板500中,利用第二电源电压线vl2将第一电源电压线vl1和第二转接电极ae2间隔开,从而可以降低第二转接电极ae2上的电平波动对第一电源电压线vl1造成的串扰,隔绝噪声。

405.另外,本公开的一些实施例提供的显示基板500通过延长第一晶体管110的第一有源区114以及延长第二晶体管120的第二有源区124,从而为第二电源电压线vl2留出布线通道。

406.例如,本公开的实施例提供的驱动电路(矩形形状)的布局尺寸大致为4.5um

×

2.9um。

407.图20a-20e分别示出了图19中所示的显示基板500的各层布局的平面图。

408.图20a示出了第一晶体管110的第一有源区114、第二晶体管120的第二有源区124、第三晶体管130的第三有源区134以及驱动晶体管140的第四有源区144,可以将图4a示出的层称为有效显示(aa)层。

409.图20b示出了第一晶体管110的控制极113、第二晶体管120的控制极123、第三晶体管130的控制极133以及驱动晶体管140的控制极143。可以将4b示出的层称为第一导电层,下文中将对第一导电层进一步描述。例如,第一导电层的材料可以采用多晶硅。

410.图20c示出了第一电源电压线vl1、第二电源电压线vl2、发光控制线el、数据线dl、接地线gnd、第一转接电极ae1等。可以将图20c示出的层称为第一金属层(metal1)。

411.图20d示出了第二转接电极ae2、连接第一扫描信号线sl1与第一晶体管110的电极、连接第二扫描信号线sl2与第二晶体管120的电极。可以将图20d示出的层称为第二金属层(metal2)。

412.图20e示出了第一扫描信号线sl1以及第二扫描信号线sl2,可以将图20e示出的层称为第三金属层(metal3)。

413.需要说明的是,在本公开的实施例中为了示意清楚在图19中并没有示意出存储电容cst,下面结合图21-图23e对图18中的所示出的存储电容cst进行进一步描述。

414.如图21所示,图21中所示的区域850为设置存储电容cst的区域。需要说明的是,为了示意清楚,图21中并没有示出全部结构的对应标记,省略的部分可以参考图19中的对应标记。

415.图22为存储电容cst的布局图,图23a-图23d为对应图22的各层布局的平面图,图23e为存储电容cst的截面示意图。

416.图22示出了4层结构,分别为第三金属层metal3、第四金属层metal4、辅助金属层metal4'、第五金属层metal5;另外还示出了第一过孔v1以及第二过孔v2,在下文中将结合截面示意图对第一过孔v1以及第二过孔v2进行描述,这里不再赘述。

417.例如,图23a示出了第三金属层metal3,例如,该第三金属层和图20e中示出的层是同一层。如图23a所示,该第三金属层metal3包括两部分,分别为充当第一电容c1的第一极的电极811和充当第一电容c1的第二极的电极812。例如,电极811被配置为接收第三电源电压avss;电极812通过第二过孔v2和第五金属层metal5中的电极840电连接,从而实现和驱动晶体管140的控制极143电连接。

418.电极811包括多个条状电极,电极812包括多个条状电极,电极811的多个条状电极和电极812的多个条状电极相互交替排布,且电极811和电极812以及之间的间隔部分形成第一电容c1。例如,该第一电容c1为存储电容cst的一部分,例如,该第一电容c1和下文中的第二电容c2并联从而形成存储电容cst。

419.例如,图23b示出了位于第四金属层metal4的电极820,例如,电极820为一个面状电极,该电极820充当第二电容c2的第一极。

420.例如,图23c示出了位于辅助金属层metal4'的电极830,例如,电极830为一个面状电极,该电极830充当第二电容c2的第二极。

421.例如,图23d示出了位于第五金属层metal5的电极840,以及第一过孔v1和第二过

孔v2。

422.图23e示出了上述存储电容cst的部分结构的截面示意图,如图23e所示,位于第五金属层metal5的电极840通过第一过孔v1和位于辅助金属层metal4'的电极830电连接;另外,位于第五金属层metal5的电极840通过第二过孔v2和位于第三金属层metal3的电极812电连接。需要说明的是,第二过孔v2会贯穿第四金属层metal4,图23e中未示出。

423.如图23e所示,位于第四金属层metal4的电极820和位于辅助金属层metal4'的电极830以及之间的间隔部分形成第二电容c2;例如,上文中所述的第一电容c1以及该第二电容c2并联共同构成存储电容cst。

424.在本公开的实施例中,如图23e所示,在第四金属层metal4和第五金属层metal5之间设置辅助金属层metal4',从而可以使得第四金属层metal4与辅助金属层metal4'之间的间距例如为第四金属层metal4与第五金属层metal5之间的间距的约1/10,从而可以有效地增大该第二电容c2单位面积内的电容值。

425.如图18和图19所示,本公开的实施例还提供一种显示基板500,包括衬底以及形成在衬底上的至少一个驱动电路。驱动电路包括驱动晶体管140、第一晶体管110、第二晶体管120以及第三晶体130。

426.驱动晶体管140包括控制极143、第一极141和第二极142,且被配置为,根据驱动晶体管140的控制极143的电压,控制流经驱动晶体管140的第一极141和驱动晶体管140的第二极142的用于驱动发光元件le发光的驱动电流。

427.第一晶体管110连接到驱动晶体管140的控制极143,且被配置为响应于第一扫描信号scan1将数据信号data写入驱动晶体管140的控制极143。第二晶体管120连接到驱动晶体管140的控制极143,且被配置为响应于第二扫描信号scan2将数据信号data写入驱动晶体管140的控制极143。第三晶体管130连接到驱动晶体管140的第一极141,且被配置为响应于发光控制信号en将第一电源电压elvdd施加到驱动晶体管140的第一极141。

428.该显示基板500还包括用于传输第一扫描信号scan1的第一扫描信号线sl1以及用于传输第二扫描信号scan2的第二扫描信号线sl2,用于传输第一电源电压elvdd的第一电源电压线vl1以及用于传输发光控制信号en的发光控制线el;第一扫描信号线sl1、第二扫描信号线sl2、第一电源电压线vl1以及发光控制线el在衬底的正投影沿与第四方向d4的垂直方向依次排布。

429.例如,沿第一晶体管110的第一极111至第一晶体管110的第二极112的方向为第一方向d1,沿第二晶体管120的第一极121至第二晶体管120的第二极122的方向为第二方向d2,沿第三晶体管130的第一极131至第三晶体管130的第二极132的方向为第三方向d3,沿驱动晶体管140的第一极141至驱动晶体管140的第二极142的方向为第四方向d4,第一方向d1、第二方向d2以及第三方向d3均和第四方向d4相交。例如,第一方向d1、第二方向d2以及第三方向d3均和第四方向d4垂直。

430.本公开至少一个实施例提供的显示基板,通过设计中的优化的布图布线设计处理,可以实现5.45um

×

13.6um的亚像素面积,实现了高的分辨率(ppi)和像素电路阵列的优化排布,并具有较好的显示效果。

431.图24a是本公开至少一实施例提供的显示基板的框图。如图24a所示,该显示基板10包括阵列分布的多个子像素100、多条扫描线11和多条数据线12。每个子像素100包括发

光元件和驱动该发光元件的像素电路。多条扫描线11和多条数据线12彼此交叉在显示区中定义出阵列分布的多个像素区,每个像素区中设置一个子像素100的像素电路。该像素电路例如为常规的像素电路,例如为2t1c(即两个晶体管和一个电容)像素电路、4t2c、5t1c、7t1c等ntmc(n、m为正整数)像素电路,并且不同的实施例中,该像素电路还可以进一步包括补偿子电路,该补偿子电路包括内部补偿子电路或外部补偿子电路,补偿子电路可以包括晶体管、电容等。例如,根据需要,该像素电路还可以进一步包括复位电路、发光控制子电路、检测电路等。例如,该显示基板还可以包括位于非显示区中的栅极驱动子电路13和数据驱动子电路14。该栅极驱动子电路13通过扫描线11与像素电路连接以提供各种扫描信号,该数据驱动子电路14通过数据线12与像素电路连接以提供数据信号。其中,图24a中示出的栅极驱动子电路13和数据驱动子电路14,扫描线11和数据线12在显示基板中的位置关系只是示例,实际的排布位置可以根据需要进行设计。

432.例如,显示基板10还可以包括控制电路(未示出)。例如,该控制电路配置为控制数据驱动子电路14施加该数据信号,以及控制栅极驱动子电路施加该扫描信号。该控制电路的一个示例为时序控制电路(t-con)。控制电路可以为各种形式,例如包括处理器和存储器,存储器包括可执行代码,处理器运行该可执行代码以执行上述检测方法。

433.例如,处理器可以是中央处理单元(cpu)或者具有数据处理能力和/或指令执行能力的其它形式的处理装置,例如可以包括微处理器、可编程逻辑控制器(plc)等。

434.例如,存储装置可以包括一个或多个计算机程序产品,所述计算机程序产品可以包括各种形式的计算机可读存储介质,例如易失性存储器和/或非易失性存储器。易失性存储器例如可以包括随机存取存储器(ram)和/或高速缓冲存储器(cache)等。非易失性存储器例如可以包括只读存储器(rom)、硬盘、闪存等。在计算机可读存储介质上可以存储一个或多个计算机程序指令,处理器可以运行该程序指令期望的功能。在计算机可读存储介质中还可以存储各种应用程序和各种数据。

435.该像素电路根据需要可以包括驱动子电路、数据写入子电路、补偿子电路和存储子电路,根据需要还可以包括发光控制子电路、复位电路等。

436.图24b示出了一种像素电路的示意图。如图24b所示,该像素电路包括数据写入子电路111、驱动子电路112和存储子电路113。

437.数据写入子电路111与存储子电路113的第一端电连接,并配置为响应于控制信号(第一控制信号sel)将数据信号vd传输至存储子电路113的第一端。存储子电路113的第二端例如配置为接收第二电源电压vss。

438.驱动子电路112包括控制电极150、第一电极151和第二电极152,驱动子电路的控制电极150与存储子电路的第一端电连接,驱动子电路112的第一电极151配置为接收第一电源电压vdd,驱动子电路112的第二电极152与第一节点s电连接,并与发光元件120的第一电极121连接。驱动子电路112配置为响应于存储子电路的第一端的电压驱动发光元件120发光。该发光元件120的第二电极122例如配置为接收第一公共电压vcom1。

439.在本公开至少一些实施例中,如图24b所示,该像素电路还包括偏置子电路114。该偏置子电路114包括控制端、第一端和第二端,该偏置子电路114的控制端配置为接收偏置信号;该偏置子电路114的第一端例如配置为接收第二电源电压vss,该偏置子电路114的第二端与第一节点s电连接。例如该偏置信号为第二公共电压vcom2。例如,该偏置信号vcom2

为恒定电压信号,例如为0.8v-1v;该偏置子电路114在该偏置信号的作用下为常开状态,配置为提供恒定电流,从而使得施加至发光元件120的电压与数据信号成线性关系,有助于对灰阶实现精细的控制,从而提高显示效果。后文将结合具体电路对此进行进一步说明。

440.例如,当数据信号(电压)vd由高变低时,写入发光元件120的第一电极121的灰阶电压需要快速变化,该偏置子电路114还可以允许发光元件120的第一电极121迅速地释放电荷,从而实现较好的动态对比度。

441.本公开的实施例中采用的晶体管均可以为薄膜晶体管或场效应晶体管或其他特性相同的开关器件,本公开的实施例中均以金属-氧化物半导体场效应晶体管为例进行说明。这里采用的晶体管的源极、漏极在结构上可以是对称的,所以其源极、漏极在结构上可以是没有区别的。在本公开的实施例中,为了区分晶体管除栅极之外的两极,直接描述了其中一极为第一极,另一极为第二极。此外,按照晶体管的特性区分可以将晶体管分为n型和p型晶体管。当晶体管为p型晶体管时,开启电压为低电平电压(例如,0v、-5v、-10v或其他合适的电压),关闭电压为高电平电压(例如,5v、10v或其他合适的电压);当晶体管为n型晶体管时,开启电压为高电平电压(例如,5v、10v或其他合适的电压),关闭电压为低电平电压(例如,0v、-5v、-10v或其他合适的电压)。

442.本公开实施例提供的显示基板可以采用刚性基板,例如玻璃基板、硅基板等,也可以由具有优良的耐热性和耐久性的柔性材料形成,例如聚酰亚胺(pi)、聚碳酸酯(pc)、聚乙烯对苯二甲酸乙二醇酯(pet)、聚乙烯、聚丙烯酸酯、多芳基化合物、聚醚酰亚胺、聚醚砜、聚乙二醇对苯二甲酸酯(pet)、聚乙烯(pe)、聚丙烯(pp)、聚砜(psf)、聚甲基丙烯酸甲酯(pmma)、三醋酸纤维素(tac)、环烯烃聚合物(cop)和环烯烃共聚物(coc)等。本公开的实施例均以硅基板为例进行说明,也即像素结构制备于硅基板上,然而,本公开实施例对此不作限制。

443.例如,该像素电路包括互补型金属氧化物半导体电路(cmos电路),也即该像素电路制备于单晶硅衬底基板上。有赖于成熟的cmos集成电路技术,硅基工艺可以实现较高的精度(例如ppi可以达到6500甚至一万以上)。

444.例如,当显示基板由于工艺波动导致子像素中的发光元件120的第一电极121与第二电极122发生短路,导致发光元件120的第一电极121的电压过高(例如第一公共电压vcom1为高电位)或过低(例如第一公共电压vcom1为低电位),从而在第一节点s处引发闩锁效应,造成cmos电路失效,导致显示基板出现暗线等不良。

445.在一些示例中,例如,该数据写入子电路包括第一数据写入晶体管p1,驱动子电路包括驱动晶体管n2;例如,第一数据写入晶体管为p型金属-氧化物半导体场效应晶体管(pmos),驱动晶体管n2为n型金属-氧化物半导体场效应晶体管(nmos),该驱动晶体管n2的栅极、第一极、第二极分别作为该驱动子电路112的控制电极150、第一电极151和第二电极152。在这种情形,例如当提供给发光元件120的第二电极122的第一公共电压vcom1为低电位,且发光元件120的第一电极121与第二电极122发生短路,将导致与该第一电极121直接连接的驱动晶体管的第二极的电位过低。

446.图24c示出了该像素电路形成闩锁效应的示意图。该驱动晶体管n2的n型有源区(如第二极)、p型硅基衬底、该第一数据写入晶体管p1所在的n型阱区以及该第一数据写入晶体管p1的p型有源区(如第一极)形成彼此连接的两个寄生晶体管q1、q2,构成的n-p-n-p

结构。当驱动晶体管n2的第二极(也即第一节点s处)的电位过低,导致该驱动晶体管n2的第二极(n型重掺杂区)与p型衬底之间的pn结(发射结)正偏,q1导通,会提供足够大的电流使得寄生晶体管q2导通,又反过来向寄生晶体管q1反馈电流,形成恶性循环,最后导致大部分的电流从vdd直接通过寄生晶体管到vss,而不受晶体管栅压的控制,造成cmos像素电路失效;并且该闩锁效应会导致寄生晶体管q2不断从发射极,也即从数据线上抽取电流,从而导致与该数据线连接的一列子像素失效,造成显示基板出现暗线等不良,极大地影响了显示效果。

447.在本公开至少一些实施例中,至少一个子像素还包括电阻器,该电阻器连接于该驱动子电路112的第二电极152与该发光元件120的第一电极121之间,可以起到升高或降低第一节点s电位的作用,从而可以缓解或避免闩锁效应,提高电路的可靠性,并提高显示效果。

448.图25a为本公开至少一实施例提供的像素电路的示意图。如图25a所示,该像素电路还包括电阻器130,电阻器130的第一端131与驱动子电路112的第二电极152电连接,第二端132与发光元件120的第一电极121电连接,也即驱动子电路112的第二电极152通过电阻器130与发光元件120的第一电极121电连接。

449.例如,该电阻器130为恒定电阻或可变电阻,也可以是其它器件(如晶体管)形成的等效电阻。

450.例如,该电阻器130与驱动子电路112的控制电极150同层绝缘设置,且所述电阻器的电阻率高于所述驱动子电路的控制电极的电阻率。例如,电阻器的电阻率为该控制电极的电阻率的十倍以上。

451.需要说明的是,本公开中所称的“同层设置”是指两种(或两种以上)结构通过同一道沉积工艺形成并通过同一道构图工艺得以图案化而形成的结构,它们的材料可以相同或不同。例如,形成同层设置的多种结构的前驱体的材料是相同的,最终形成的材料可以相同或不同。本公开中的“一体的结构”是指两种(或两种以上)结构通过同一道沉积工艺形成并通过同一道构图工艺得以图案化而形成的彼此连接的结构,它们的材料可以相同或不同。

452.通过这种设置,可以使得驱动子电路控制电极与电阻器在同一构图工艺中形成,从而节省工艺。

453.例如,电阻器和所述驱动子电路的控制电极的材料均为多晶硅材料,且电阻器的掺杂浓度低于控制电极的掺杂浓度,因此电阻器具有比控制电极高的电阻率。例如,电阻器可以是本征多晶硅或轻掺杂多晶硅,控制电极为重掺杂多晶硅。

454.在另一些示例中,控制电极和电阻器的材料可以不同。例如,控制电极和电阻器的材料可以分别包括金属以及该金属对应的金属氧化物。例如,该金属可以包括金(au)、银(ag)、铜(cu)、铝(al)、钼(mo)、镁(mg)、钨(w)以及以上金属组合而成的合金材料。

455.在本公开至少一实施例中,该数据写入子电路111可以包括由互补的两个晶体管彼此并联构成的传输门电路;该控制信号包括反相的两个控制信号。该数据写入子电路111采用传输门结构的电路可以有助于使数据信号没有损失地传输到存储子电路113的第一端。

456.例如,数据写入子电路包括第一控制电极、第二控制电极、第一端和第二端,数据写入子电路的第一控制电极和第二控制电极分别配置为接收第一控制信号和第二控制信

号,数据写入子电路的第一端配置为接收数据信号,数据写入子电路的第二端与存储子电路的第一端电连接,并配置为响应于所述第一控制信号和所述第二控制信号将所述数据信号传输至所述存储子电路的第一端。

457.需要注意的是,在本公开实施例的说明中,第一节点s并非一定表示实际存在的部件,而是表示电路图中相关电路连接的汇合点。

458.需要说明的是,在本公开的实施例的描述中,符号vd既可以表示数据信号端又可以表示数据信号的电平,同样地,符号sel既可以表示控制信号,也可以表示控制信号端,符号vcom1、vcom2既可以表示第一公共电压、第二公共电压,也可以表示第一公共电压端和第二公共电压端;符号vdd既可以表示第一电压端又可以表示第一电源电压,符号vss既可以表示第二电压端又可以表示第二电源电压。以下各实施例与此相同,不再赘述。

459.图25b示出了图24a所示像素电路的一种具体实现示例的电路图。如图25b所示,该数据写入子电路111包括彼此并联的第一数据写入晶体管p1和第二数据写入晶体管n1。该第一数据写入晶体管p1和第二数据写入晶体管n1分别为p型金属-氧化物半导体场效应晶体管(pmos)和n型金属-氧化物半导体场效应晶体管(nmos)。该控制信号包括互为反相的第一控制信号sel和第二控制信号sel_b,该第一数据写入晶体管p1的栅极作为该数据写入子电路的第一控制电极,并配置为接收该第一控制信号sel,该第二数据写入晶体管n1的栅极作为该数据写入子电路的第二控制电极,并配置为接收该第二控制信号sel_b。该第二数据写入晶体管n1的第一极和第一数据写入晶体管p1的第一极电连接作为该数据写入子电路的第一端,并配置为接收数据信号vd;第二数据写入晶体管n1的第二极与第一数据写入晶体管p1的第二极电连接作为该数据写入子电路的第二端,并与驱动子电路112的控制电极150电连接。

460.例如,该第一数据写入晶体管p1和第二数据写入晶体管n1大小相同,具有相同的沟道宽长比。

461.该数据写入子电路111利用了晶体管互补的电学特性,无论传输高电平还是低电平,都具有较低的开态电阻,从而具有电学信号传输完整性的优势,可以将数据信号vd没有损失地传输至存储子电路113的第一端。

462.例如,如图25b所示,该驱动子电路112包括驱动晶体管n2,例如,该驱动晶体管n2为nmos。该驱动晶体管n2的栅极、第一极和第二极分别作为驱动子电路112的控制电极、第一电极和第二电极。

463.例如,该存储子电路113包括存储电容cst,该存储电容cst包括第一电容电极141和第二电容电极142,该第一电容电极141和第二电容电极142分别作为该存储子电路113的第一端和第二端。

464.例如,该电阻器130包括电阻r。例如,驱动子电路112的第二电极152与衬底基板之间形成pn结,电阻器130的阻值配置为当驱动晶体管n2工作在饱和区时,也即该像素电路工作以驱动发光元件120发光时,该pn结关断。在这种情形,即便发光元件120的两个电极之间发生短路,由于该电阻器130上存在压降,可以对该第二电极152的电位进行保护,从而避免了闩锁效应的发生。

465.例如,发光元件120具体实现为有机发光二极管(oled)。例如,发光元件120可以为顶发射结构的oled,可以发红光、绿光、蓝光或白光等。例如,该发光元件120为微型oled

(micro oled)。本公开的实施例对发光元件的具体结构不作限制。例如,该发光元件120的第一电极121为oled的阳极,第二电极122为oled的阴极,也即该像素电路为共阴极结构。然而,本公开实施例对此不作限制,根据电路结构的变化,该像素电路也可以是共阳极结构。

466.例如,该偏置子电路114包括偏置晶体管n3,该偏置晶体管n3的栅极、第一极和第二极分别作为偏置子电路114的控制端、第一端和第二端。

467.图25c示出了图25b所示像素电路的信号时序图,以下将结合图25b所示的信号时序图对图25c所示的像素电路的工作原理进行说明。例如,第二数据写入晶体管、驱动晶体管、偏置晶体管均为n型晶体管,第一数据写入晶体管为p型管,然而本公开实施例对此不做限制。

468.图25c示出了各信号在连续两个显示周期t1和t2中的波形图,例如该数据信号vd在显示周期t1为高灰阶电压,在显示周期t2为低灰阶电压。

469.例如,如图25c所示,每一帧图像的显示过程包括数据写入阶段1以及发光阶段2。该像素电路的一种工作过程包括:在数据写入阶段1,第一控制信号sel和第二控制信号sel_b均为开启信号,第一数据写入晶体管p1和第二数据写入晶体管n1导通,数据信号vd经第一数据写入晶体管p1和第二数据写入晶体管n1传输至驱动晶体管n2的栅极;在发光阶段2,第一控制信号sel和第二控制信号sel_b均为关闭信号,由于存储电容cst的自举效应,存储电容cst两端的电压保持不变,驱动晶体管n2工作在饱和状态且电流不变,并驱动发光元件120发光。当像素电路从显示周期t1进入到显示周期t2,数据信号vd由高灰阶电压变为低灰阶电压,偏置晶体管n3在第二公共电压vcom2的控制下产生稳定的漏极电流,该漏极电流在oled的显示灰阶需要快速变化时,可以快速泄放oled阳极存储的电荷。例如,该放电过程发生于显示周期t2的数据写入1,因此在该显示周期t2的发光阶段2,该oled阳极的电压得以快速下降,从而实现较好的动态对比度,提高了显示效果。

470.例如,当该第一节点s与发光元件120直接电连接时,电压v0直接加载到该发光元件120的第一电极121上,例如为oled的阳极电压;当第一节点s通过电阻器130与该发光元件120电连接,由于流过发光元件120的电流极小,因此该第一节点s的电压可以近似等于该发光元件120的第一电极121的电压;也即使得发光元件120的第一电极121的电压与数据信号(数据电压)vd成线性关系,从而可以实现对灰阶实现精细的控制,提高了显示效果。

471.例如,第一控制信号sel和第二控制信号sel_b为差分互补信号,振幅相同,相位相反。这样有助于提高电路的抗干扰性能。例如,该第一控制信号sel和第二控制信号sel_b可以由同一栅驱动电路单元(如goa单元)输出,从而简化电路。

472.例如,如图24a所示,显示基板10还可以包括数据驱动电路13和扫描驱动电路14。数据驱动电路13配置为根据需要(例如输入显示装置的图像信号)可发出数据信号,例如上述数据信号vd。扫描驱动电路14配置为输出各种扫描信号,例如包括上述第一控制信号sel和第二控制信号sel_b,其例如为集成电路芯片(ic)或者为直接制备在显示基板上的栅驱动电路(goa)。

473.例如,该显示基板采用硅基板作为衬底基板101,该像素电路、数据驱动电路13和扫描驱动电路14都可以集成于该硅基板上。在此情形下,由于硅基电路可以实现较高的精度,该数据驱动电路13和扫描驱动电路14例如也可以形成于对应于该显示基板的显示区的区域中,而并不一定位于非显示区。

474.例如,显示基板10还包括控制电路(未示出)。例如,该控制电路配置为控制数据驱动电路13施加该数据信号vd,以及控制栅极驱动电路13施加各种扫描信号。该控制电路的一个示例为时序控制电路(t-con)。控制电路可以为各种形式,例如包括处理器和存储器,存储器包括可执行代码,处理器运行该可执行代码以执行上述检测方法。

475.例如,处理器可以是中央处理单元(cpu)或者具有数据处理能力和/或指令执行能力的其它形式的处理装置,例如可以包括微处理器、可编程逻辑控制器(plc)等。

476.例如,存储装置可以包括一个或多个计算机程序产品,所述计算机程序产品可以包括各种形式的计算机可读存储介质,例如易失性存储器和/或非易失性存储器。易失性存储器例如可以包括随机存取存储器(ram)和/或高速缓冲存储器(cache)等。非易失性存储器例如可以包括只读存储器(rom)、硬盘、闪存等。在计算机可读存储介质上可以存储一个或多个计算机程序指令,处理器121可以运行该程序指令期望的功能。在计算机可读存储介质中还可以存储各种应用程序和各种数据,例如在上述检测方法中获取的电特性参数等。

477.以下以采用图25b所示像素电路为例对本公开至少一实施例提供的显示基板进行示例性说明,然而本公开实施例并不限于此。

478.图26a为本公开至少一个实施例提供的显示基板10的示意图。例如,如图26a所示,该显示基板10包括衬底基板101,多个子像素100位于该衬底基板101上。多个子像素100布置为子像素阵列,该子像素阵列的行方向为第一方向d1,列方向为第二方向d2,第一方向d1与第二方向d2交叉,例如正交。图26a中示例性地示出了两行六列子像素,也即两个像素行20和六个像素列30,并用虚线框分别示出了彼此间隔的三个像素列的区域。

479.例如,衬底基板101可以为刚性基板,例如玻璃基板、硅基板等,也可以由具有优良的耐热性和耐久性的柔性材料形成,例如聚酰亚胺(pi)、聚碳酸酯(pc)、聚乙烯对苯二甲酸乙二醇酯(pet)、聚乙烯、聚丙烯酸酯、多芳基化合物、聚醚酰亚胺、聚醚砜、聚乙二醇对苯二甲酸酯(pet)、聚乙烯(pe)、聚丙烯(pp)、聚砜(psf)、聚甲基丙烯酸甲酯(pmma)、三醋酸纤维素(tac)、环烯烃聚合物(cop)和环烯烃共聚物(coc)等。本公开实施例均以该衬底基板101为硅基板为例进行说明,然而本公开实施例并不限于此。

480.例如,该衬底基板101包括单晶硅或者高纯度硅。像素电路通过cmos半导体工艺形成于衬底基板10上,例如,通过掺杂工艺在衬底基板101中形成晶体管的有源区(包括晶体管的沟道区、第一极和第二极),并通过硅氧化工艺或者化学气相淀积工艺(cvd)形成各绝缘层、以及通过溅射工艺形成多个导电层从而形成走线结构等。各晶体管的有源区位于衬底基板101的内部。

481.图26b示出了图26a沿剖面线i-i’的剖视图。为了清楚起见,图26b中省略了一些没有直接连接关系的走线或电极结构。

482.例如,如图26b所示,该显示基板10包括衬底基板101、依次位于衬底基板101上的第一绝缘层201、多晶硅层102、第二绝缘层202、第一导电层301、第三绝缘层203、第二导电层302、第四绝缘层204、第三导电层303、第五绝缘层205和第四导电层304。以下将对该显示基板10中的结构分层次进行说明,图26b将作为一个参照并一并得到说明。

483.为了清楚起见并方便说明,图27a示出了该显示基板10位于第一导电层301以下的部分,也即衬底基板101以及其上的第一绝缘层201和多晶硅层102,包括各晶体管(p1、n1-n3)、存储电容cst以及电阻器130;图27b示出了图27a中一个子像素100的放大示意图;为了

清楚起见,在图27a中还对应示出了图26a中剖面线i-i’。图28a-图28e示出了图27a所示的基板结构的形成过程。

484.如图27b所示,例如,在平行于衬底基板101的板面的方向上,第一数据写入晶体管p1和驱动晶体管n2位于存储电容cst的相对两侧,例如,在第二方向d2上位于该存储电容cst的相对两侧。

485.结合参考图24c,这种设置有助于拉大第一数据写入晶体管p1与驱动晶体管n2的距离,从而增大寄生电路的电阻,进一步降低了cmos电路的闩锁效应的风险。

486.例如,存储电容140的第二电容电极142的材料为导体或半导体。例如,结合图26b和图27b所示,存储电容140的第二电容电极142为衬底基板101的第一区401;例如,该衬底基板101为p型硅基衬底,该第二电容电极142的材料为p型单晶硅。当第一电容电极141上施加电压,衬底基板101中位于该第一电容电极141下方的半导体性质的第一区401形成反型区而变为导体,从而与该第一区401两侧的接触孔区(如图4b所示的接触孔区145a、145b)形成电连接。在这种情形,并未对该第一区401进行额外掺杂等处理。

487.在另一示例中,该第一区401例如为衬底基板101中的导体化区域,例如重掺杂区域,从而可以使得第二电容电极142获得稳定的较高的导电率。

488.例如,该衬底基板101还包括第二区402,该第二区402为衬底基板101中的n型阱区。如图27b所示,例如,第一数据写入晶体管p1和电阻器130在第二方向d2上并排设置于第二区402中。将多晶硅材料的电阻器130设置于n型衬底中有助于减少寄生效应,提高电路特性。

489.例如,在平行于衬底基板101的板面的方向上,电阻器(r)130与第一数据写入晶体管p1位于第二电容电极142的同一侧。例如,在平行于衬底基板101的板面的方向上,驱动晶体管n2和偏置晶体管n3位于第二电容电极142的同一侧。

490.例如,如图27b所示,第一数据写入晶体管p1和第二数据写入晶体管p1在第一方向d1上并排设置,并关于沿第二方向d2的对称轴对称。例如,第一数据写入晶体管p1的栅极160和第二数据写入晶体管n1的栅极170在第一方向d1并排设置,并关于沿第二方向d2的对称轴对称。

491.例如,电阻器130为u型结构,例如为不对称的u型结构,例如该u型结构的两个分支的长度不等。例如,如图27b所示,电阻器130的第二端132更靠近驱动晶体管n2。

492.将电阻器130设置为u型结构有助于节省电阻器所占用的版图面积,从而提高版图的空间利用率,有助于提高显示基板的分辨率。例如,在相同的空间内,u型结构的电阻器可以增大电阻器的长度,从而得到期望的电阻值。

493.此外,将电阻器130设计为非对称结构同样是为了合理利用版图空间,例如,如图27b所示,该u型电阻器较短分支的上方设计了接触孔区411a,该接触孔区411a在第一方向d1上与该电阻器130的第二端132并列。例如,该接触孔区411a为n型重掺杂区(n+)。例如,该接触孔区411是为了对第一数据写入晶体管p1所在的阱区401进行偏置,从而避免闩锁效应和衬底偏置效应引起的阈值电压变化,提高电路的稳定性。例如,参照图26b,通过将p型衬底101进行低压偏置,n型阱区402进行高压偏置,可以使得二者之间的寄生pn结反偏, 对器件进行电性隔离,并降低器件之间的寄生效应,提高电路的稳定性。

494.例如,u型结构的开口朝向第一电容电极141,电阻器130的第一端131和第二端132

分别位于u型结构的两个端部。如图所示,该电阻器130的第一端131设置有接触孔区133,用于与驱动晶体管n2的栅极150电连接;该电阻器130第二端132设置有接触孔区134,用于与发光元件120的第一电极121电连接。

495.例如,该电阻器130的材料包括多晶硅材料,该接触孔区133、134为掺杂区,用于降低接触电阻;该电阻器130除该接触孔区以外的主体区域例如为本征区或低掺杂区,从而得到期望的电阻值。

496.例如,存储电容140的第一电容电极141与电阻器130同层绝缘设置,且都包括多晶硅材料;存储电容140的第一电容电极141的掺杂浓度高于电阻器130的主体区的掺杂浓度。例如,该电阻器130的主体区为本征多晶硅材料。

497.例如,各晶体管p1、n1-n3的栅极160、170、150、180与存储电容140的第一电容电极141同层设置,均包括多晶硅材料。例如,如图27b所示,驱动晶体管n2的栅极150与第一电容电极141彼此连接为一体的结构。

498.图27b中还分别示出了各晶体管p1、n1-n3的有源区p1a、n1a、n2a和n3a,并示出了第一数据写入晶体管p1的第一极161和第二极162,第二数据写入晶体管n1的第一极171和第二极172,驱动晶体管n2的第一极151和第二极152,偏置晶体管n3的第一极181和第二极182。

499.图27b中还分别示出了第一数据写入晶体管p1的栅极接触区165、第一接触区163和第二极接触区164,第二数据写入晶体管n1的栅极接触区175、第一接触区173和第二极接触区174,驱动晶体管n2的栅极接触区155、第一接触区153和第二极接触区154,以及偏置晶体管n3的栅极接触区185、第一接触区183和第二极接触区184。例如,各第一极接触区为所对应的第一极用于形成电接触的区域,各第二极接触区为对应的第二极接触区为用于形成电接触的区域,各栅极接触区为对应的栅极用于形成电接触的区域。

500.例如,第一数据写入晶体管p1的有源区p1a与第二数据写入晶体管n1的有源区n1a在第一方向d1并排设置,并关于沿第二方向d2的对称轴对称。

501.如图27b所示,驱动晶体管n2的有源区n2a的面积相较于其它晶体管的有源区的面积大,可以获得较大的宽长比,有助于提高驱动晶体管n2的驱动能力,从而提高显示效果。

502.如图27b所示,对于有源区较大的晶体管,如驱动晶体管n2和偏置晶体管n3,由于有足够空间,可以在其第一极和第二极上分别设置至少两个接触孔区,从而可以与待连接结构获得充分的接触并形成并联结构,从而降低接触电阻。

503.图27b中还示出了与第一电容电极141上的接触孔区144以及配置为与第二电容电极142电连接的接触孔区145a、145b。如图27b所示,第一电容电极141和第二电容电极142分别对应设置至少两个接触孔区以降低接触电阻。

504.结合参考图27a,在第一方向d1上相邻的两个子像素100中晶体管(例如包括各晶体管的形状、尺寸等)以及存储电容、电阻器的分布关于沿第二方向d2的对称轴对称,也即该两个子像素中对应的结构分别关于沿第二方向d2的对称轴对称。在第二方向d2上相邻的两个子像素100中晶体管的分布关于第一方向轴对称。

505.这种对称设置可以尽量提高工艺误差的均一性,从而提高显示基板的均一性。此外,这种对称设置使得基板中一些同层设置且可以彼此连接的结构可以一体形成,相较于分开设置,可以使得像素布局更加紧凑,提高空间的利用率,从而提高了显示基板的分辨

率。

506.例如,如图27a所示,在第一方向d1上相邻的两个子像素100的第二区402为一体的结构,在第二方向d2上相邻的两个子像素100的第二区402为一体的结构,也即该相邻的四个子像素100中的第一数据写入晶体管n1和电阻器130位于同一阱区。相较于分别设置独立的阱区,这种设置可以在满足设计规则的前提下使得像素的排布更加紧凑,有助于提高显示基板的分辨率。

507.例如,如图27a所示,在第二方向d2上相邻的两个子像素的第一数据写入晶体管p1的有源区p1a彼此连接为一体的结构,也即该两个第一数据写入晶体管p1的有源区p1a位于同一第二区402的同一掺杂区a1(p阱)中,且该两个第一数据晶体管p1的第一极彼此连接为一体的结构,以接收同一数据信号vd。

508.例如,如图27a所示,在第二方向d2上相邻的两个子像素的第二数据写入晶体管n1的有源区n1a彼此连接为一体的结构,也即该两个第二数据写入晶体管n1的有源区n1a位于衬底基板101的同一掺杂区a2(n阱)中,且该两个第二数据写入晶体管n1的第一极彼此连接为一体的结构,以接收同一数据信号vd。

509.例如,如图27a所示,在第一方向d1上相邻的两个子像素100的第一数据写入晶体管p1的栅极或者第二数据写入晶体管n2的栅极彼此连接为一体的结构。

510.由于对于每行像素,第一数据写入晶体管p1的栅极都配置为接收同一第一控制信号sel,第二数据写入晶体管n1的栅极都配置为接收同一第二控制信号sel_b。又由于在第一方向d1上相邻的两个子像素的晶体管镜像对称,在第一方向d1上交替出现两个子像素的第一写入晶体管p1相邻的情形与第二写入晶体管n1相邻的情形。因此相邻两个第一数据写入晶体管p1的栅极可以直接连接为一体的结构,形成第一控制电极组191,相邻的第二数据写入晶体管n1的栅极可以直接连接为一体的结构,形成第二控制电极组192。这种设置可以在满足设计规则的前提下使得像素的排布更加紧凑,有助于提高显示基板的分辨率。

511.如图27a所示,对于第一方向d1上相邻的两个子像素100,当它们的驱动晶体管n2相邻的情形,两个驱动晶体管n2的有源区n2a彼此连接为一体的结构,也即该两个驱动晶体管n2的有源区n2a位于衬底基板101的同一掺杂区b(n阱)中,且该两个驱动晶体管n2的第一极彼此连接为一体的结构,形成第三控制电极组193,以接收同一第一电源电压vdd;当它们的偏置晶体管n3相邻的情形,两个偏置晶体管n3的栅极彼此连接为一体的结构,以接收同一第二公共电压vcom2;两个偏置晶体管n3的有源区n3a彼此连接为一体的结构,也即该两个偏置晶体管n3的有源区n3a位于衬底基板101的同一掺杂区c(n阱)中,且该两个偏置晶体管n3的第一极彼此连接为一体的结构,以接收同一第二电源电压vss。

512.这种设置可以在满足设计规则的前提下使得像素的排布更加紧凑,有助于提高显示基板的分辨率。

513.图28a-图28d示出了图27a所示的基板结构的形成过程,为了清楚起见,图中仅示出了两行两列子像素,也即相邻的四个子像素100。以下结合图28a-28d对本公开实施例提供的显示基板的形成过程进行示例性说明,然而这并不作为对本公开的限制。

514.例如,提供一块硅基衬底基板,例如其材料为p型单晶硅。n型晶体管(例如驱动晶体管)可以直接在该p型硅衬底上制作,也即该p型衬底充当该n型晶体管的沟道区,有利于发挥nmos器件高速的优势,提高了电路性能。

515.如图28a所示,例如,在p型硅衬底基板上进行n型掺杂,形成n型阱区,也即第二区402,以作为第一数据写入晶体管p1和电阻器130的衬底。

516.例如,在第一方向d1上相邻的两个子像素的第二区402可以彼此连接,在第二方向d2上相邻的两个子像素的第二区402可以彼此连接。例如,在进行该n型掺杂时对该衬底基板101上不掺杂的区域进行遮挡。

517.结合图27b和图28b所示,例如,在该衬底基板101上形成第一绝缘层201,接着在该第一绝缘层201上形成多晶硅层102。

518.该第一绝缘层201包括各晶体管的栅极绝缘层,还包括存储电容cst的介质层104。该多晶硅层102包括第一电容电极141、电阻器130以及各晶体管(p1、n1-n3)的栅极150、160、170、180。

519.该第一数据写入晶体管p1的栅极位于该第二区402,该n型阱区充当该p型晶体管的沟道区。该电阻器130也位于该第二区402,将多晶硅材料的电阻器130形成于n型衬底中有助于减少寄生效应,提高电路特性。各n型晶体管直接形成在p型衬底上。

520.如图28b所示,在第一方向d1上相邻的两个子像素中的多晶硅层的图案关于沿第二方向d2的对称轴对称;在第二方向d2上相邻的两个子像素中的多晶硅层的图案关于沿第一方向d1的对称轴对称。

521.例如,在第一方向d1上相邻的两个子像素的第一数据写入晶体管p1和第二数据写入晶体管n1的栅极可以分别一体成型。

522.例如,通过热氧化法在衬底基板上形成该第一绝缘层。例如,该第一绝缘层的材料为硅的氮化物、氧化物或氮氧化物。

523.例如,通过化学气相淀积工艺(pvd)在该第一绝缘层上形成多晶硅材料层,然后对该多晶硅材料层进行光刻工艺形成该多晶硅层102。

524.图28c示出了衬底基板的掺杂窗口区103(左图),并在图28b所示基板结构上示出了该掺杂窗口区(右图)。例如,该掺杂为重掺杂,以在衬底基板上形成用于电连接的接触孔区。例如,该掺杂窗口区包括各晶体管的源极区和漏极区。例如,该掺杂窗口区还包括衬底的各接触孔区以及电阻器130的接触孔区,例如包括图27b所示的接触孔区400a、400b、411a、411b、145a、145b、133、134。例如,由于晶体管的栅极由多晶硅材料形成,也需要对该多晶硅栅极进行掺杂。在进行掺杂时,需要形成阻挡层以遮挡非掺杂区域,而仅仅暴露出相应的掺杂窗口区及非晶硅区。

525.需要说明的是,图28c仅对各掺杂窗口区进行了示意,在实际进行掺杂工艺时再设置相应的阻挡层/掩模层暴露相应的掺杂窗口区及多晶硅区进行掺杂即可。例如,该阻挡层/掩模层的材料可以是光刻胶或者氧化物材料。

526.如图28d所示,对应电阻器130形成阻挡层135。为了保护电阻器130的阻值,需要在掺杂过程中对电阻器130进行遮挡以避免电阻器130因掺杂而被破坏。该阻挡层135遮挡住了电阻器130的主体部分,仅暴露出电阻器130两端的接触孔区133、134。

527.例如,该阻挡层135可以是硅的氮化物、氧化物或者氮氧化物,也可以是光刻胶材料。待掺杂工艺结束后,该阻挡层135可以保留在显示基板中,也可以去除。

528.在另一些示例中,该电阻器130的阻挡层135也可以在掺杂时同其它区域的阻挡层/掩模层一同形成,本公开实施例对此不作限制。

529.例如,在掺杂过程中,需要分别进行n型掺杂和p型掺杂,例如以形成n型晶体管的源极区和漏极区以及p型晶体管的源极区和漏极区。在进行n型掺杂工艺时,需要形成阻挡层不进行n型掺杂的区域遮挡;在进行p型掺杂工艺时,需要形成阻挡层将不进行p型掺杂的区域遮挡。

530.图28e中用不同的阴影图案(左图)示出了n型掺杂区sn和p型掺杂区sp,并在图28d所示的基板上示出了该n型掺杂区sn和p型掺杂区sp(右图)。该n型掺杂区sn和p型掺杂区sp在图27b中也示出,可以一并参照。

531.例如,进行n型掺杂工艺包括形成阻挡层覆盖该p型掺杂区sp,并覆盖n型掺杂区sn中除掺杂窗口区及多晶硅区以外的区域,仅保留n型掺杂区sn中的掺杂窗口区以及多晶硅区,也即该sn区与图28c所示掺杂窗口区103及多晶硅区的重叠区域;然后进行n型掺杂工艺。对照图27b,通过该n型掺杂工艺可以形成晶体管n1-n3的栅极以及第一极和第二极,以及接触孔区411a、411b、145a、145b。该n型掺杂工艺可例如可以为离子注入工艺,掺杂元素例如可以是硼元素。

532.例如,进行p型掺杂工艺包括形成阻挡层覆盖该n型掺杂区sn,并覆盖p型掺杂区sp中除掺杂窗口区及多晶硅区以外的区域,仅保留p型掺杂区sp中的掺杂窗口区及多晶硅区,也即该sp区与图28c所示掺杂窗口区103及多晶硅区的重叠区域;然后进行p型掺杂工艺。对照图27b,通过该p型掺杂工艺可以形成晶体管p1的栅极、第一极和第二极,以及接触孔400a、400b、133、134。该p型掺杂工艺可例如可以为离子注入工艺,掺杂元素例如可以是磷元素。

533.在掺杂过程中,例如采用离子注入工艺,多晶硅图案可以充当掩模,使得离子对于硅基衬底的注入正好发生在该多晶硅的两侧,从而形成了各晶体管的第一极和第二极,实现了自对准。此外,原本电阻较高的多晶硅经过掺杂工艺电阻率降低,可以形成各晶体管的栅极以及该第一电容电极。因此,采用多晶硅材料作为电阻器及栅极材料具有多种有益效果,并节省了工艺成本。

534.如此,就形成了图27a所示的显示基板的结构,包括各晶体管p1、n1-n3以及电阻器130、存储电容cst。

535.例如,在第一方向d1上相邻的两个子像素中相应的晶体管、电阻器及存储电容cst分别关于沿第二方向d2的对称轴对称;在第二方向d2上相邻的两个子像素中相应的晶体管、电阻器及存储电容cst分别关于沿第一方向d1的对称轴对称。

536.需要说明的是,在本实施例中,存储电容cst为场效应形成的电容,在第一电容电极141上施加电压后,衬底基板101中位于该第一电容电极141下方的区域产生反型电荷,将该存储电容cst的下极板,也即第二电容电极142导体化。

537.在另一些实施例中,也可以预先对衬底基板101位于该第一电容电极141下方的区域进行导体化处理(例如掺杂处理)形成该第二电容电极142。本公开实施例对此不作限制。

538.在图27a所示的基板上依次形成第二绝缘层202、第一导电层301、第三绝缘层203、第二导电层302、第四绝缘层204、第三导电层303、第五绝缘层205和第四导电层304,就形成了图26a所示的显示基板。

539.图29a和图29b分别示出了第一导电层301的图案以及该第一导电层301设置于图27a所示基板结构上的情形,图29c示出了图29b沿剖面线iv-iv’的剖视图;图29b中还示出

了第二绝缘层202中的过孔,该过孔与图27b中的各接触区一一对应,用于将各接触孔区与第一导电层301中的图案电连接。为了清楚起见,图中仅示出了两行六列子像素,并用虚线框示出了一个子像素100的区域;此外在图29b中还对应示出了图26a中剖面线i-i’所在的位置。

540.如图29a所示,在第一方向d1上相邻的两个子像素中的第一导电层的图案关于沿第二方向d2的对称轴对称;在第二方向d2上相邻的两个子像素中的第一导电层的图案关于沿第一方向d1的对称轴对称。以下将以一个子像素为例对该第一导电层的图案进行示例性说明。

541.如图29a所示,该第一导电层301包括连接电极313,该连接电极313用于将电阻器130的第一端131与驱动子电路112的第二电极152电连接。

542.例如,结合参考图29b,该连接电极313的第一端通过第二绝缘层202中的过孔225与电阻器130的第一端131电连接;该连接电极313的第二端包括第一支部331和第二支部332,结合图26b,该第一支部331通过第二绝缘层202中的过孔226a与驱动晶体管n2的第一极151电连接,该第二支部332通过第二绝缘层202中的过孔226b与偏置晶体管n3的第一极181电连接。

543.例如,如图29b所示,在第二方向d2上,该过孔225与过孔226a分别位于第一电容电极141的相对两侧;也即该连接电极313在衬底基板101上的正投影在第二方向d2上穿过该第一电容电极141在衬底基板101上的正投影。

544.例如,该过孔226a和过孔226b可以设置为至少两个,以降低接触电阻。

545.例如,结合参考图29a和图29b,该第一导电层301还包括连接电极314,该连接电极314通过第二绝缘层202中的过孔229与电阻器130的第二端132电连接,该连接电极314用于与发光元件120的第一电极121电连接。

546.例如,该连接电极314为l型,其一个分支与电阻器130的第二端132电连接,另一分支用于与发光元件120的第一电极121电连接。

547.例如,结合图29b和图29c所示,该第一导电层301还包括第三电容电极315,该第三电容电极315与第一电容电极141在垂直于衬底基板的方向上重叠。该第三电容电极315通过第二绝缘层202中的过孔227与接触孔区145a电连接,以与第二电容电极142电连接;也即,在垂直于衬底基板的方向上,第二电容电极142和第三电容电极315分别位于第一电容电极141的两侧,且彼此电连接,从而形成并联电容的结构,增大存储电容cst的电容值。

548.例如,结合图29b和图29c所示,该第一导电层301还包括第四电容电极316,该第四电容电极316与第一电容电极141及第二电容电极142在垂直于衬底基板的方向上均重叠。该第四电容电极316通过第二绝缘层202中的过孔228与接触孔区145b电连接,以与第二电容电极142电连接。该第四电容电极316可以进一步增大存储电容cst的电容值,提高电路性能。

549.例如,第三电容电极315和第四电容电极316在第一方向d1上位于连接电极313的两侧。

550.例如,如图29a所示,在第一方向上d1相邻的两个子像素中相邻的第三电容电极315可以一体形成以接收同一第二电源电压vss,在第一方向上d1相邻的两个子像素中相邻的第四电容电极316可以一体形成以接收同一第二电源电压vss。

551.例如,该过孔227和过孔228可以分别至少设置两个以降低接触电阻;例如,该至少两个过孔227沿第二方向d2排列,该至少两个过孔228沿第二方向d2排布。

552.例如,该第一导电层301还包括连接电极317,该连接电极317用于将数据写入子电路的第二端与存储子电路的第一端电连接,也即将第一数据写入晶体管p1的第二极161、第二数据写入晶体管n1的第二极171以及第一电容电极141电连接。

553.结合参考图29a和图29b,该连接电极317包括三个端部,例如为t型结构。结合参考图26b,该连接电极317的第一端通过第二绝缘层202中的过孔261a与第一数据写入晶体管p1的第二极电连接,该连接电极317的第二端通过第二绝缘层202中的过孔261b与第二数据写入晶体管n1的第二极电连接,该连接电极317的第三端通过第二绝缘层202中的过孔261c与第一电容电极141电连接。

554.例如,如图29b所示,在第二方向d2上,连接电极314与连接电极317的第三端至少部分重叠。这种设置使得像素布局更为紧凑,从而提高了显示基板的空间利用率,提高了显示基板的分辨率。

555.结合参考图29a和图29b,该第一导电层301还包括第一扫描线连接部311和第二扫描线连接部312,该第一扫描线连接部311用于与第一扫描线电连接以使得该第一数据写入晶体管p1的栅极接收第一控制信号sel。该第二扫描线连接部312用于与第二扫描线电连接以使得该第二数据写入晶体管n1的栅极接收第一控制信号sel_b。

556.例如,该第一扫描线连接部311通过第二绝缘层202中的过孔221与第一数据写入晶体管p1的栅极电连接,第二扫描线连接部312通过第二绝缘层202中的过孔222与第二数据写入晶体管n1的栅极电连接。

557.例如,如图29a所示,在第一方向d1上相邻的子像素共用第一扫描线连接部311或第二扫描线连接部312。

558.如图29a所示,该第一导电层301还包括数据线连接部245(本公开第三连接电极的一个示例),该数据线连接部245用于与数据线电连接,以使得该第一数据写入晶体管p1的第一极和第二数据写入晶体管n1的第一极接收到数据线传输的数据信号vd。

559.如图29b所示,该数据线连接部245通过第二绝缘层202中的过孔223与第一数据写入晶体管p1的第一极161电连接,通过第二绝缘层202中的孔224与第二数据写入晶体管n1的第一极171电连接。

560.例如,如图29a所示,多个数据线连接部245在第一方向d1上间隔排布,例如位于两个子像素行的分界处。例如,在第二方向d2上相邻的两个子像素共用一个数据线连接部245。

561.参考图29a和图29b,该第一导电层301还包括连接电极318,该连接电极318通过第二绝缘层202中的过孔230与驱动晶体管n2的第一极电连接。

562.参考图27a和图27b,该第一导电层301还包括连接电极319a、319b、319c,这些连接电极均是为了对晶体管的衬底进行偏置而设置,例如用于将n型衬底连接至第一电源电压端以接收第一电源电压vdd(高电压),或者用于将p型衬底连接至第二电源电压端以接收第二电源电压vss(低电压),由此可以避免衬偏效应等寄生效应,提高电路的稳定性。

563.结合参考图27b,该连接电极319a、319b分别通过第二绝缘层202中的过孔262a、262b与衬底基板101中的第二区(n阱区)402中的接触孔区411a、411b电连接,该连接电极

319a和319b用于连接到第一电压端vdd以对该第一数据写入晶体管p1的n型衬底进行偏置。该连接电极319c通过第二绝缘层202中的过孔262c与衬底基板101中的接触孔区400a电连接,该连接电极319c用于连接到第二电压端vss以对与第二数据写入晶体管n1所在的p型衬底进行偏置。

564.结合参考图29a-29b,该第一导电层301还包括偏置电压线250,该偏置电压线250沿第一方向d1延伸,并通过第二绝缘层202中的过孔263与偏置晶体管n3的栅极电连接,以提供第二公共电压vcom2。

565.结合参考图27b、图29a-29b,该第一导电层301还包括电源线260(本公开第九电源线的一个示例),该电源线260沿第一方向d1延伸,用于传输第二电源电压vss。该电源线260通过第二绝缘层202中的过孔264a与偏置晶体管n3的第一极电连接以提供第二的电源电压vss,并通过第二绝缘层202中的过孔264b与衬底基板101中的接触孔区400b电连接,以对与第二数据写入晶体管n1所在的p型衬底(本公开的第二掺杂区的一个示例)进行偏置。

566.图30a示出了第二导电层302的示意图,图30b在第一导电层301的基础上示出了第二导电层302,图30b中还示出了第三绝缘层203中的过孔,该第三绝缘层203中的过孔用于连接第一导电层301中的图案和第二导电层302中的图案。为了清楚起见,图中仅示出了四行六列子像素,并用虚线示出了两个子像素行的分界线;此外在图30b中还对应示出了图26a中剖面线i-i’所在的位置。

567.如图30a所示,在第一方向d1上相邻的两个子像素中的第二导电层的图案关于沿第二方向d2的对称轴对称;在第二方向d2上相邻的两个子像素中的第二导电层的图案关于沿第一方向d1的对称轴对称。以下将以一个子像素为例对该第二导电层的图案进行示例性说明。

568.如图30a所示,该第二导电层302包括沿第一方向d1延伸的电源线270a、270b、280a、280b,该电源线270a、270b用于传输第二电源电压vss,该电源线280a、280b用于传输第一电源电压vdd。该电源线270a、280a、270b、280b在第二方向d2上一一交替排列。

569.结合参考图26b、图30a和图30b,该电源线270a(本公开第一电源线的一个示例)通过第三绝缘层203中的多个过孔235与第一导电层301中的电源线260电连接,从而形成并联结构,有效降低了走线上的电阻;该多个过孔235沿第一方向d1排列。例如,该电源线270b通过第三绝缘层203中的过孔236与第四电容电极316电连接以提供该第二电源电压vss;例如,多个过孔236沿第二方向d2排列。例如,该电源线270b还通过第三绝缘层203中的过孔267与第三电容电极315电连接以提供该第二电源电压vss;例如,多个过孔267沿第二方向d2排列。

570.例如,在第二方向d2上,电源线270b(本公开第七电源线的一个示例)的平均线宽大于电源线270a的平均线宽,这是由于与该电源线270b电连接的第四电容电极316与第三电容电极315均具有较大的面积,将电源线270b设置为具有较大的宽度可以便于与第四电容电极316之间和第三电容电极315形成多个连接孔236、267,从而有效降低接触电阻。

571.结合参考图30a和图30b,该电源线280a(本公开第二电源线的一个示例)通过第三绝缘层203中的过孔237与第一导电层301中的连接电极318(本公开第五连接电极的一个示例)电连接,从而连接到驱动晶体管n2的第一极以提供第一电源电压vdd。该电源线280b通过第三绝缘层203中的过孔238与第一导电层301中的连接电极319a电连接,从而对衬底基

板101中的第二区(n阱区)402(本公开的第一掺杂区的一个示例)进行高压偏置;例如,多个过孔238沿第二方向d2排列。