一种基于多层PCB的小型化大功率电桥的制作方法

一种基于多层pcb的小型化大功率电桥

技术领域

1.本发明是一种基于多层pcb的小型化大功率电桥,属于无源电路技术领域。

背景技术:

2.电桥作为无源电路中的关键器件之一,具有功分、合成、移相的作用,在如今的通信系统中应用十分广泛,在天线馈电系统中可用于波束形成,在平衡式放大器中可以改善 输入输出驻波比(vswr),在正交相移键控(qpsk)发射机中可以确定其相位误差,亦可以作为功率放大器的合成器等,并且电桥四端口均匹配可以方便集成在系统中。目前市面上的电桥主要有两种形式,分别为传统型电桥和表面贴装电桥,传统型电桥包括同轴型电桥,腔体型电桥,每个臂长度为四分之一波长,尺寸较大,且结构单一难以实现小型化,而表面贴装电桥具有小型化,高集成度的特点,在各种组件模块内应用广泛,但是功率容量小,散热较差,如何通过选择合适介质材料以及合理布局实现大功率是目前迫切需要解决的问题。

技术实现要素:

3.本发明提出的是一种基于多层pcb的小型化大功率电桥,其目的在于为了满足大功率射频电路需求,设计了一款满足大功率,低损耗、高隔离的小型化表面贴装3db电桥,工作频率0.7-2ghz,可承受连续波100w。

4.本发明的技术解决方案:一种基于多层pcb的小型化大功率电桥,其结构包括壳体、电路板,壳体的四个端点连接输入端、隔离端、耦合端和直通端,所述电路板由多层pcb结构压合构成,从上往下依次是上盖板、上介质材料、上压合胶膜、上铜箔电路线、中央介质材料、下铜箔电路线、下压合胶膜、下介质材料和下盖板,所述的铜箔电路线为带状线结构。

5.所述所述多层pcbpcb结构压合技术,选用罗杰斯板材。

6.所述上介质材料和下介质材料材质为rogers 4003板材,所述中央介质材料材质为rogers 5880板材,所述上压合胶膜和下压合胶膜材质为rogers 4450b半固化片。

7.所述上铜箔电路线和下铜箔电路线采用蛇形带状线印刷在中间介质基板两侧,进行宽边耦合。

8.所述上铜箔电路线和下铜箔电路线线宽为0.9mm。

9.所述壳体外壁四周进行半孔化处理,设有l型槽,表面镀银,厚度为0.01mm,电桥整体外形长度为20mm,宽度为6mm,厚度为3mm。

10.所述电桥测试用底部测试架的尺寸与电桥尺寸相同,采用介质覆铜板,上层为铜箔,介质材质为rogers 5880板材,厚度为0.254mm,铜箔四角进行l型槽挖槽处理。

11.所述电桥在印制板和腔体上进行挖槽安装而直接安装在印制板上,实现表面贴装化。

12.本发明的有益效果:(1)本发明采取多层pcb压合技术,选用成本低廉的罗杰斯板材,工艺成本大大减小,同时多层介质填充的方式使得电路的有效介电常数增大,明显缩小了体积,实现了小型

化目的;(2)本发明采取蛇形带状线宽边耦合结构,实现了强耦合,消除了分布参数,比传统集总参数表面贴装无源电路的损耗低、隔离度高、驻波小,提高了系统性能;(3)本发明无需在印制板和腔体上进行挖槽安装而直接安装在印制板上,实现了表面贴装化,方便和优化了微带电路和系统的设计和实现,并且使其应用层面大大增加,应用领域更加广泛。

附图说明

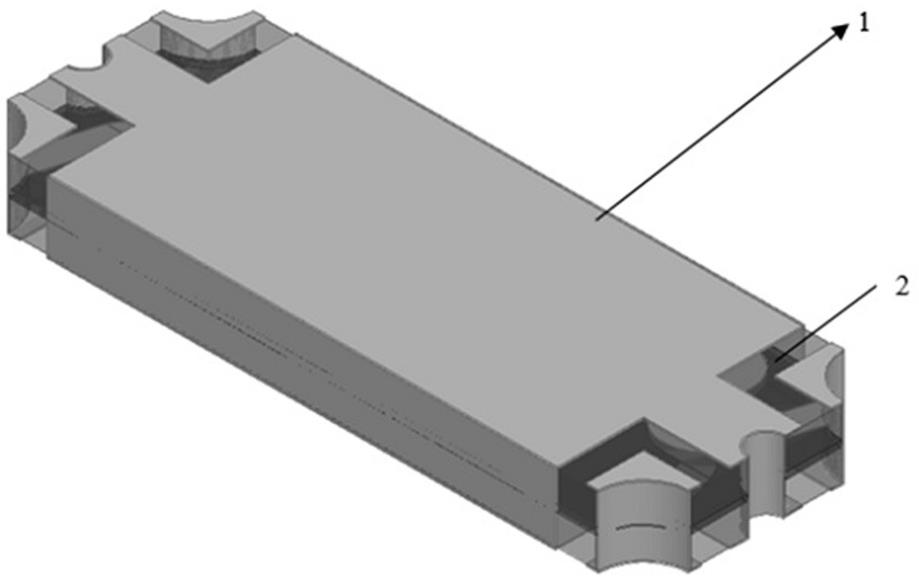

13.图1表面贴装电桥整体示意图;图2底部测试架;图3为内部蛇形带状线;图4为表面贴装电桥多层pcb结构图;图5为驻波仿真结果;图6为隔离度和耦合度仿真结果;图7为相位差和插入损耗仿真结果;图8-11为不同频率点的功率容量仿真结果;图12为热损耗仿真结果。

14.图中1是上盖板、2是l型槽、3是l型槽、4是方形金属板、5是侧边集总端口馈电处、6是输入端、7是隔离端、8、9是输出端、10、14是介质材料,11、13是压合胶膜,12是中央介质材料。

具体实施方式

15.下面结合附图对本发明技术方案进一步说明如图1 所示,本实施例所述的3db 电桥采用表面贴装的封装形式,外壁四周进行半孔化处理,表面镀银,厚度为0.01mm,电桥整体外形长度为20mm,宽度为6mm,厚度为3mm, 1为上盖板, 2为l型槽,便于馈电处良好接触和接地。

16.如图2 所示,底部测试架与电桥尺寸相似,采用介质覆铜板,上层为铜箔,介质基板为rogers 5880板材,选用常规厚度0.254mm,铜箔同样进行挖槽处理3, 4为方形金属板,实现电桥与测试架金属互联, 5为侧边集总端口馈电处。

17.如图3所示,电路结构采用蛇形带状线印刷在中间介质基板两侧,进行宽边耦合,宽边耦合电桥具有插损小、耐功率高、带宽宽等优点,因此常被用于设计大功率3db电桥,6和7分别为输入端和隔离端,8和9分别为两个输出端,幅度相等,相位差为90度,耦合线计算常用奇偶模模型分析法,奇偶模特征阻抗,满足公式(1)和公式(2):z0e=1/(ve*ce)

ꢀꢀꢀ

(1)z0o=1/(vo*co)

ꢀꢀꢀ

(2)其中ve和vo分别为偶模奇模传输速度,ce和co分别为偶模奇模单位长度电容。根据传输线理论,耦合系数c可由公式(3)推导得到:c=20log((ze

‑ꢀ

zo)/( ze+zo)

ꢀꢀꢀꢀ

(3)奇模偶模阻抗与端口阻抗关系需满足公式(4):

z=√(ze*zo)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(4)根据公式(3)、(4)可以推导出3db电桥的偶奇模特征阻抗分别为ze=120.91,zo=20.68,然后根据宽边耦合结构的层介质材料及层厚度进行分析计算,可确定微带线参数,宽边耦合层间介质厚度和介电常数确定了其耦合带线的特征阻抗。3db电桥的电长度是工作频率的四分之一波长,因此板材介质的相对介电常数越高,其物理长度越短,越容易实现小型化。但是同时板材介电常数越高,耦合带线的线宽越窄,导致耦合器的导体损耗更大,不利于实现低插损,不利于承受大功率,考虑到大功率的承受能力,本专利线宽设置为0.9mm,高于理论计算线宽,耐功率能力进一步提高。

18.如图4所示,电桥采用多层pcb压合技术,将铜箔、半固化片和已制作图形的芯板(覆铜板)按一定顺序叠合,然后在高温高压条件下将其粘结为一体,考虑大功率散热问题,选用散热较好的两款材料rogers 4003(10,14)和rogers 5880(12),同时板芯与板芯之间要用rogers 4450b半固化片(11,13),防止pcb板受热后各层涨缩系数差异导致的扭曲变形以及绝缘和贴合作用。

19.图5-8为电桥的s参数仿真结果,从图中可以看出各个端口匹配良好,驻波比在1.4以下,隔离度在-17db以下,耦合度在3db左右,3端口和4端口相位差在90度左右,平均插损在0.5左右。

20.图9-11为电桥功率容量仿真结果,通过给输入端口馈100w功率,仿真不同频率点0.7ghz、1.2ghz和2ghz下场强大小,从图中可以看出最大场强小于空气击穿场强3e6v/m,则认为电桥能抗住100w大功率。

21.图12为电桥热耗散仿真结果,根据电桥插入损耗0.5db左右,即耗散约5%的功率,推出100w连续波中有5w功率转化为热,再依据rogers 5880热导率为0.2 w/m/℃和rogers 4003热导率为0.71 w/m/℃进行热力学仿真,因此通过给电桥初始工作温度70度下,从图中可以看出温度上升了30度,温度处在电桥温度承受范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1