半导体结构及其制作方法、存储器与流程

1.本技术涉及半导体技术领域,特别是涉及一种半导体结构及其制作方法、存储器。

背景技术:

2.随着半导体芯片的不断发展,其关键尺寸不断减小。但由于光刻机的限制,其尺寸缩小存在极限,因此如何在一片晶圆上做出更高存储密度的芯片,是众多科研工作者和半导体从业人员的研究方向。

3.目前已知的芯片,已经开始由平面向三维方向发展。部分企业已经开发了具有很高存储密度的gaa(gate all around,环绕栅极)结构的存储器芯片。然而,为了实现更低的生成成本和更高的企业利润,更高存储密度的结构仍待开发。

技术实现要素:

4.基于此,本技术实施例提供一种半导体结构及其制作方法。

5.一种半导体结构,包括:

6.衬底;

7.至少一个有源层单元,所述有源层单元包括层叠设置的多层有源层以及设置在相邻有源层之间的隔离层,所述有源层包括第一图形、第二图形以及沟道图形,所述第一图形与所述第二图形中的其中一者为源极图形,另一者为漏极图形,所述沟道图形连接所述第一图形与所述第二图形,各层所述有源层的第一图形在远离所述沟道图形一侧呈阶梯状分布,且相邻第一图形之间具有所述隔离层,相邻第二图形之间具有所述隔离层;

8.多个栅极结构,分别环绕于各所述沟道图形外周;

9.多个第一接触结构,分别位于各所述第一图形上方;

10.多个电容结构,分别位于各所述第一接触结构上方。

11.在其中一个实施例中,所述半导体结构还包括第一图形化层,所述第一图形化层覆盖于顶层的所述有源层上表面,定义所述有源层的位置。

12.在其中一个实施例中,所述第一图形化层上表面与顶部的所述栅极结构的上表面齐平。

13.在其中一个实施例中,同一所述有源层单元内,所述多个有源层的第一接触结构排列成两排,相邻两个所述第一接触结构分别位于不同排。

14.在其中一个实施例中,

15.所述半导体结构还包括第二图形化层,所述第二图形化层具有第二开口,所述第二开口定义出第一接触孔的形状及位置,所述多个第一接触结构位于不同的所述第一接触孔内。

16.在其中一个实施例中,

17.各层所述有源层的第二图形在远离所述沟道图形一侧呈阶梯状分布,

18.所述半导体结构还包括:

19.多个第二接触结构,分别位于各所述第二图形上方;

20.多个第三接触结构,分别位于顶部的各所述栅极结构的上方。

21.所述多个第一接触结构、多个第二接触结构以及多个第三接触结构均位于不同的所述第一接触孔内。

22.在其中一个实施例中,所述半导体结构还包括第三图形化层,所述第三图形化层具有第三开口,所述第三开口定义出第二接触孔的形状及位置,所述电容结构填充所述第二接触孔。

23.在其中一个实施例中,所述电容结构包括第一电极层、绝缘介质层以及第二电极层,所述第一电极层位于所述第二接触孔内,所述绝缘介质层位于所述第一电极层表面以及所述第三图形化层表面,所述第二电极层位于所述绝缘介质层表面。

24.在其中一个实施例中,所述第二电极层包括tin层以及gesi层,所述tin层位于所述绝缘介质层表面,所述gesi层位于所述tin层表面且填满所述第二接触孔。

25.一种半导体结构的制作方法,包括:

26.提供衬底;

27.于所述衬底上形成至少一个有源层单元,所述有源层单元包括层叠设置的多层有源层以及设置在相邻有源层之间的隔离层,所述有源层包括第一图形、第二图形以及沟道图形,所述第一图形与所述第二图形中的其中一者为源极图形,另一者为漏极图形,所述沟道图形连接所述第一图形与所述第二图形,各层所述有源层的第一图形在远离所述沟道图形一侧呈阶梯状分布,且相邻第一图形之间具有所述隔离层,且相邻第二图形之间具有所述隔离层;

28.环绕于各所述沟道图形外周均形成栅极结构;

29.于各所述第一图形上方均形成第一接触结构;

30.于各所述第一接触结构上方均形成电容结构。

31.在其中一个实施例中,所述于所述衬底上形成至少一个有源层单元,包括:

32.于所述衬底上交替形成牺牲材料层与半导体材料层,以形成多组基础材料层,所述基础材料层包括所述牺牲材料层与所述半导体材料层;

33.依次对各组基础材料层进行刻蚀,形成多组图形化材料层,各组所述图形化材料层在其至少一侧均呈阶梯状分布;

34.将各组所述图形化材料层的被刻蚀侧,通过第一介质层填满;

35.于顶层的所述图形化材料层的上表面及所述第一介质层的上表面形成第一图形化层,所述第一图形化层定义所述有源层的位置;

36.基于所述第一图形化层刻蚀各组所述图形化材料层,以形成多个有源层;

37.去除各个所述有源层的沟道图形之间的所述牺牲材料层,剩余的所述牺牲材料层形成所述隔离层。

38.在其中一个实施例中,所述环绕于各所述沟道图形外周均形成栅极结构,包括:

39.于各所述沟道图形外周表面以及所述第一图形化层上表面均形成栅极材料层;

40.以所述第一图形化层为抛光停止层,对所述栅极材料层进行化学机械抛光,以形成所述栅极结构。

41.在其中一个实施例中,所述第一图形化层定义多列所述沟道图形的位置,

42.所述以所述第一图形化层为抛光停止层,对所述栅极材料层进行化学机械抛光,以形成所述栅极结构之后,还包括:

43.于所述第一图形化层的上表面以及顶部的所述栅极结构的上表面形成第二介质层,所述第二介质层具有第一开口,所述第一开口暴露出两组所述沟道图形之间的位置;

44.基于所述第二介质层,刻蚀其下方的结构,分隔各列所述沟道图形,以形成多个所述有源层单元;

45.于所述第二介质层表面以及各所述有源层单元之间的区域内形成第三介质层。

46.在其中一个实施例中,所述于各所述有源层的所述第一图形上方均形成第一接触结构,包括:

47.于所述第一图形化层上方形成第二图形化层,所述第二图形化层具有第二开口,所述第二开口定义出第一接触孔的形状及位置,第一接触孔用于形成所述第一接触结构;

48.基于所述第二图形化层,刻蚀其下层结构,以形成所述第一接触孔;

49.于所述第二图形化层以及所述第一接触孔内形成接触材料层;

50.以所述第二图形化层为抛光停止层,对所述接触材料层进行化学机械抛光,以于不同的所述第一接触孔内分别形成多个所述第一接触结构。

51.在其中一个实施例中,

52.各层所述有源层的第二图形在远离所述沟道图形一侧呈阶梯状分布,

53.所述第一接触孔还用于形成多个第二接触结构以及多个第三接触结构,多个第二接触结构分别位于各所述有源层的所述第二图形上方,多个第三接触结构分别位于顶部的所述栅极结构的上方;

54.以所述第二图形化层为抛光停止层,对所述接触材料层进行化学机械抛光,以于不同的所述第一接触孔内分别形成多个所述第一接触结构的同时,还形成多个所述第二接触结构以及多个所述第三接触结构。

55.在其中一个实施例中,所述于各所述第一接触结构上方均形成电容结构,包括:

56.于第二图形化层上表面以及所述第一接触结构上表面形成第四介质层;

57.于所述第四介质层上表面形成第三图形化层,所述第三图形化层具有第三开口,所述第三开口定义出第二接触孔的形状及位置;

58.基于所述第三图形化层,刻蚀所述第四介质层,以形成多个所述第二接触孔;

59.于各所述第二接触孔内形成第一电极层;

60.于所述第一电极层表面以及所述第三图形化层表面形成绝缘介质层;

61.于所述绝缘介质层表面形成第二电极层。

62.在其中一个实施例中,所述第二电极层包括tin层以及gesi层,

63.所述于所述绝缘介质层表面形成第二电极层,包括:

64.于所述绝缘介质层表面形成所述tin层;

65.于所述tin层表面形成所述gesi层,所述gesi层填满所述第二接触孔。

66.一种存储器,包括上述任一半导体结构。

67.上述半导体结构及其制作方法、存储器,由于同一有源层单元包括多层层叠设置的有源层,可以在相同面积上,形成更多的存储单元,从而在结构维度有效增加存储密度。并且,本实施例第一图形在远离沟道图形一侧成阶梯状分布,从而使得电容结构可以通过

第一接触结构垂直立于晶体管的源极或者漏极上,进而使得电容结构的设置不会增加存储单元在衬底晶圆上的面积占比,从而可以进一步增加存储密度。

附图说明

68.为了更清楚地说明本技术实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

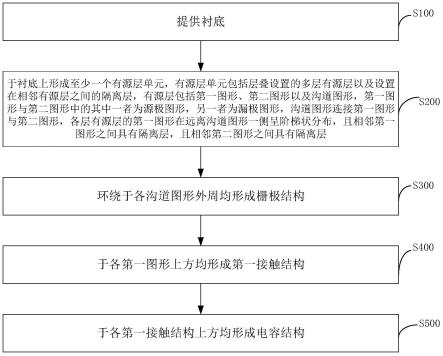

69.图1为一实施例中提供的半导体结构的制作方法的流程图;

70.图2-图30为一实施例中提供的半导体结构制作过程中结构示意图;

71.图31为图30的部分分解结构示意图。

具体实施方式

72.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本技术的公开内容更加透彻全面。

73.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

74.应当明白,当元件或层被称为“在...上”、“与...相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在...上”、“与...直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。

75.应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层、掺杂类型和/或部分,这些元件、部件、区、层、掺杂类型和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层、掺杂类型或部分与另一个元件、部件、区、层、掺杂类型或部分。因此,在不脱离本技术教导之下,下面讨论的第一元件、部件、区、层、掺杂类型或部分可表示为第二元件、部件、区、层或部分;举例来说,可以将第一掺杂类型成为第二掺杂类型,且类似地,可以将第二掺杂类型成为第一掺杂类型;第一掺杂类型与第二掺杂类型为不同的掺杂类型,譬如,第一掺杂类型可以为p型且第二掺杂类型可以为n型,或第一掺杂类型可以为n型且第二掺杂类型可以为p型。

76.空间关系术语例如“在...下”、“在...下面”、“下面的”、“在...之下”、“在...之上”、“上面的”等,在这里可以用于描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在...下面”和“在...下”可包括上和下两个取向。此外,器件也可以包括另外地取向(譬如,旋转90度或其它取向),并且在此使用的空间描述语相应地被解释。

77.在此使用时,单数形式的“一”、“一个”和“所述/该”也可以包括复数形式,除非上

下文清楚指出另外的方式。还应当理解的是,术语“包括/包含”或“具有”等指定所陈述的特征、整体、步骤、操作、组件、部分或它们的组合的存在,但是不排除存在或添加一个或更多个其他特征、整体、步骤、操作、组件、部分或它们的组合的可能性。

78.本技术的实施例不应当局限于其示意图所示的区的特定形状,而是包括由于例如制造技术导致的形状偏差。

79.在一个实施例中,请参阅图1,提供一种半导体结构的制作方法,包括如下步骤:

80.步骤s100,请参阅图2,提供衬底100;

81.步骤s200,请参阅图17,于衬底100上形成至少一个有源层单元,有源层单元包括层叠设置的多层有源层210以及设置在相邻有源层之间的隔离层220,有源层210包括第一图形211、第二图形212以及沟道图形213,第一图形211与第二图形212中的其中一者为源极图形,另一者为漏极图形,沟道图形213连接第一图形211与第二图形212,各层有源层210的第一图形211在远离沟道图形213一侧呈阶梯状分布,且相邻第一图形之间具有隔离层220,且相邻第二图形212之间具有隔离层220;

82.步骤s300,请参阅图19,环绕于各沟道图形213外周均形成栅极结构300;

83.步骤s400,请参阅图27,于各第一图形211上方均形成第一接触结构410;

84.步骤s500,请参阅图30以及图31,于各第一接触结构410上方均形成电容结构500。

85.例如,在步骤s100中,作为示例,衬底100的材料可以为硅。当然,其也可以为其他半导体材料,如锗、锗硅、碳化硅、氮化镓等。

86.在步骤s200中,有源层单元的数量可以为一个,也可以为多个(一个以上)。

87.每个有源层单元包括层叠设置的多层有源层210。例如,有源层210的数量为两个或者两个以上。每个有源层210包括第一图形211、第二图形212以及沟道图形213。沟道图形213位于第一图形211与第二图形212之间,而连接二者。第一图形211为源极图形时,第二图形212为漏极图形。第一图形211为漏极图形时,第二图形212为源极图形。沟道图形213在栅极结构300的控制电压的作用下,在第一图形211与第二图形212间形成导电沟道,从而导通源极与漏极,进行实现电容结构500的充放电。

88.同时,每个有源层单元还包括一个或者多个隔离层220。各个相邻的有源层210之间均设有隔离层220。例如,隔离层220位于各个相邻的有源层210的第一图形211之间,以及各个相邻的有源层210的第二图形212之间,以将各个有源层210形成的晶体管的源极以及漏极绝缘隔离,从而将各个晶体管与对应的电容结构500形成不同的存储单元。

89.在步骤s300中,栅极结构300环绕在各沟道图形213外周,从而与各个有源层210形成晶体管。每个有源层210均与环绕在其沟道图形213外周的栅极结构300形成一个晶体管。多个有源层210形成多个晶体管。

90.在步骤s400中,各有源层210的第一图形211上方均形成第一接触结构410,从而将各个有源层210形成的晶体管均连接对应的电容结构500。这里第一图形211可以为源极图形,也可为漏极图形。

91.在步骤s500中,电容结构500形成在第一接触结构410的上方,从而不会增加存储单元在衬底晶圆上的面积占比。

92.在本实施例中,由于同一有源层单元包括多层层叠设置的有源层210,可以在相同面积上,形成更多的存储单元,从而从结构维度有效增加存储密度。并且,本实施例第一图

形211在远离沟道图形213一侧成阶梯状分布,从而使得电容结构500可以通过第一接触结构410垂直立于晶体管的源极或者漏极上,进而使得电容结构500的设置不会增加存储单元在衬底晶圆上的面积占比,从而可以进一步增加存储密度。

93.在一个实施例中,请参阅图图2至图18,步骤s200包括:

94.步骤s210,请参阅图图4,于衬底100上交替形成牺牲材料层2201与半导体材料层2101,以形成多组基础材料层10,基础材料层10包括牺牲材料层2201与半导体材料层2101;

95.步骤s220,请参阅图图11,依次对各组基础材料层10进行刻蚀,形成多组图形化材料层20,各组图形化材料层20在其至少一侧呈阶梯状分布;

96.步骤s230,请参阅图图13,将各组图形化材料层20的被刻蚀侧,通过第一介质层610填满;

97.步骤s240,请参阅图图16,于顶层的图形化材料层20的上表面及第一介质层610的上表面形成第一图形化层700,第一图形化层700定义有源层210的位置;

98.步骤s250,请参阅图图16,基于第一图形化层700刻蚀各组图形化材料层20,以形成多个有源层210;

99.步骤s260,请参阅图图17,去除各个有源层210沟道图形213之间的牺牲材料层2201,剩余的牺牲材料层2201形成隔离层220。

100.在步骤s210中,牺牲材料层2201可以包括但不限于为inp层,半导体材料层可以包括但不限于为ingaas层。

101.例如,作为示例,请参阅图3,在此之前还可以对衬底100进行热氧化,从而形成氧化层以对衬底100进行隔离保护。之后可以形成刻蚀停止层,以在后后续刻蚀各组基础材料层10时,起到刻蚀停止作用。刻蚀停止层可以包括一层,也可以包括多层。例如,可以在氧化层上形成氮化物层,以作为第一刻蚀停止层,之后再在氮化物层上形成inalas层,以作为第二刻蚀停止层。

102.之后,可以刻蚀停止层(如在inalas层)上形成交替形成牺牲材料层与半导体材料层,以形成多组基础材料层10。

103.例如,一组基础材料层10可以包括一个牺牲材料层2201以及一个半导体材料层2101。

104.在步骤s220中,例如,作为示例,请参阅图5至图7,可以是首先形成一个最小图形化光阻31。然后,基于最小图形化光阻31,刻蚀位于最顶层的一组基础材料层10,形成位于最顶层的一组图形化材料层20,去除最小图形化光阻31。之后,请参阅图8至图10,形成面积大于最小图形化光阻3131的、覆盖最顶层图形化材料层20的次小图形化光阻32,基于次小图形化光阻32,刻蚀位于第二层的一组基础材料层10,形成位于第二层的一组图形化材料层20,去除次小图形化光阻32。之后,形成面积逐渐增大,且覆盖在先形成的图形化材料层20的相应图形化光阻,从而从上至下依次刻蚀各组基础材料层10,形成各组图形化材料层20,请参阅图11。

105.上述示例中,通过形成尺寸依次增大的图形化光阻,依次对各组基础材料层10进行刻蚀,从而形成在其至少一侧呈阶梯状分布的各组图形化材料层20。

106.可以理解的是,对各组基础材料层10进行刻蚀的方式并不限于此。

107.例如也可以通过形成尺寸依次减小的图形化光阻,刻蚀各组基础材料层10,形成

各组图形化材料层20。

108.此时,可以首先于结构顶部形成一个最大图形化光阻;然后基于最大图形化光阻,刻蚀位于最顶层的一组基础材料层10,形成第一中间图形,以将最大图形化光阻的图形转移。

109.之后,对最大图形化光阻进行收缩(shrink)处理,于结构顶部形成面积小于最大图形化光阻的次大图形化光阻,次大图形化光阻与最大图形化光阻的图形之间存在阶梯,次大图形化光阻暴露第一中间图形位于其两侧的部分,第一中间图形暴露第二层(最顶层之下的那一层)基础材料层10位于其两侧的部分;基于次大图形化光阻,刻蚀两侧暴露的第一中间图形以及位于第二层的一组基础材料层10,刻蚀时,牺牲材料层与半导体材料层分别刻蚀,且互为刻蚀停止,从而使得次大图形化光阻与与最大图形化光阻的之间的阶梯,转移至最顶层基础材料层10与第二层基础材料层10。

110.之后,依次进行收缩(shrink)处理形成面积逐渐减小的图形化光阻,且按照上述方式刻蚀,从而将各图形化光阻之间的阶梯,转移至各组基础材料层10之间,从而形成呈阶梯状分布的各组图形化材料层20。

111.在步骤s230中,请参阅图12,可以首先沉积第一介质材料层611,然后,请参阅图13,对其进行回刻或者化学机械抛光(chemical mechanical polishing,cmp),从而形成第一介质层610,以填满各组图形化材料层200的被刻蚀侧。第一介质层610可以包括,但不限于为sio2层。

112.例如,作为示例,可以在最顶层的半导体材料层2101表面形成图形化的抛光停止层,然后沉积高于剖光停止层的第一介质材料层。之后,对第一介质层材料进行停止于抛光停止层的化学机械抛光,从而形成第一介质层610。

113.或者,作为另一示例,也可以将最顶层的半导体材料层2101做的足够厚,从而通过控制化学机械抛光时间,来使得刻蚀停止在最顶层的半导体材料层2101,从而形成第一介质层610。

114.在步骤s240中,第一图形化层700材料可以为氧化铝(alo),其作为图形化的掩膜层而定义有源层210的位置。第一图形化层700的中间部分遮盖其下层局部区域,该部分定义了沟道图形的位置。同时,第一图形化层700的两端部分遮盖其下层区域,从而分布定义第一图形与第二图形的位置。

115.例如,请参阅图14,可以通过顶层的图形化材料层20的上表面及第一介质层610的上表面沉积第一图形化层700的第一材料层701。然后,请参阅图15,于第一材料层701表面形成第一图形化光阻40。然后,基于第一图形化光阻40刻蚀第一材料层701,以形成第一图形化层700,请参阅图16。

116.在步骤s250中,请继续参阅图16,基于第一图形化层700及其上的第一图形化光阻40,刻蚀各组图形化材料层20,以形成多个有源层210,之后去除第一图形化光阻40。未被第一图形化层700遮盖的部分被刻蚀去除,而被第一图形化层700遮盖的各层半导体材料层2101形成各层有源层210。例如,第一图形化层700的中间部分遮盖的各层半导体材料层2101形成各层有源层210的沟道图形213,第一图形化层700的两端部分遮盖的各层半导体材料层2101分别形成各层有源层210的第一图形211与第二图形212的位置。

117.在步骤s260中,请参阅图17,各层沟道图形213之间的牺牲材料层2201被去除,从

而使得沟道图形213悬空设置。同时,各层沟道图形213两侧的被第一图形化层700遮盖的牺牲材料层2201形成隔离层220。

118.在一个实施例中,步骤s300包括:

119.步骤s310,请参阅图18,于各沟道图形213外周表面以及第一图形化层700上表面均形成栅极材料层300a;

120.步骤s320,请参阅图19,以第一图形化层700为抛光停止层,对栅极材料层300a进行化学机械抛光,以形成栅极结构300。

121.在步骤s310中,栅极材料层300a可以包括栅绝缘材料层、第一金属阻挡材料层以及第一金属材料层。

122.例如,可以首先在各沟道图形213外周表面以及第一图形化层700上表面均形成栅绝缘材料层,然后再在栅绝缘材料层表面形成第一金属阻挡材料层(如tin层),此时沟道图形213之间仍然具有间隙。之后,再在第一金属阻挡材料层表面形成第一金属材料层(如金属钨层)。此时,第一金属材料层可以将沟道图形213之间的间隙可以被填满,进而使得相邻的栅极结构300相连。

123.在步骤s320中,请参阅图19,对栅极材料层300a进行化学机械抛光之后,第一图形化层700上表面的栅极材料层300a被去除,剩余的栅极材料层300a形成各晶体管的栅极结构300,第一图形化层700上表面与顶部的栅极结构300的上表面齐平。

124.例如,栅极结构300包括栅绝缘层、第一金属阻挡层以及第一金属层。化学机械剖光后,剩余的栅绝缘材料层形成各晶体管的栅绝缘层,剩余的第一金属阻挡材料层形成各晶体管的第一金属阻挡层以及剩余的第一金属材料层形成各晶体管的第一金属层。

125.在一个实施例中,第一图形化层700定义多列沟道图形213的位置。此时,步骤s320之后,还包括:

126.步骤s330,于第一图形化层700的上表面以及顶部的栅极结构300的上表面形成第二介质层620,第二介质层620具有第一开口,第一开口暴露出两组沟道图形213之间的位置;

127.步骤s340,基于第二介质层620,刻蚀其下方的结构,分隔各列沟道图形,以形成多个有源层单元;

128.步骤s350,于第二介质层620表面以及各有源层单元之间的区域内形成第三介质层630。

129.在步骤s330中,第二介质层620可以包括但不限于为sio2层。

130.例如,请参阅图20至图22,可以首先于第一图形化层700的上表面以及顶部的栅极结构300的上表面形成第二介质材料层621,然后于第二介质材料层621上形成图形化光刻胶50。然后,基于图形化光刻胶50,刻蚀第二介质材料层621,以形成第二介质层620。

131.在步骤s340中,请参阅图22,此时,用于形成第二介质层620的图形化光刻胶50也可以不去除,基于第二介质层620以及其上的图形化光刻胶50进行刻蚀,分隔各列沟道图形,以形成多个有源层单元。两组沟道图形213之间的被第二介质层620暴露的部分被刻蚀去除,从而形成多个有源层单元。每个有源层单元中包括一列沟道图形213。

132.在步骤s350中,请参阅图23,可以先去除用于形成第二介质层620的图形化光刻胶。然后于第二介质层620表面以及各有源层单元之间的区域内形成第三介质层630。第三

介质层630可以将各个有源层单元绝缘隔离,其可以包括但不限于为sio2层。作为示例,图23中的第三介质层630的材料与第二介质层620相同,而显示成了一层。

133.在一个实施例中,步骤s400包括:

134.步骤s410,请参阅图25至图27,于第一图形化层700上方形成第二图形化层800,第二图形化层800具有第二开口,第二开口定义出第一接触孔的形状及位置,第一接触孔用于形成第一接触结构410;

135.步骤s420,请参阅图25,基于第二图形化层800,刻蚀其下层结构,以形成第一接触孔;

136.步骤s430,请参阅图26,于第二图形化层800以及第一接触孔内形成接触材料层400a;

137.步骤s440,请参阅图27,以第二图形化层800为抛光停止层,对接触材料层400a进行化学机械抛光,以于不同的第一接触孔内分别形成多个第一接触结构410。

138.在步骤s410中,第二图形化层800可以包括但不限于为sin层。当衬底100上形成多个有源层单元时,例如,请参阅图23至图25,可以在第三介质层630表面沉积第二图形化层800的第二材料层801,然后于第二材料层表面形成第二图形化光阻60,然后基于第二图形化光阻60刻蚀第二材料层801,以形成第二图形化层800。

139.在步骤s420中,请参阅图25,第二图形化层800的下层结构可以包括第三介质层630、第二介质层620、第一图形化层700、以及第一介质层610。由于各层有源层210的端部呈阶梯状分布,从而使得对填充的第一介质层610刻蚀之后各层有源层210的第一图形211可以同时被暴露,从而形成多个具有不同深度的第一接触孔。之后,去除第二图形化光阻60。

140.在步骤s430中,请参阅图26,接触材料层400a可以包括第二金属阻挡材料层以及第二金属材料层。

141.例如,可以首先在第二图形化层800以及第一接触孔内形成第二金属阻挡材料层(如tin层)。之后,再在第二金属阻挡材料层表面形成第二金属材料层(如金属钨层)。此时,第一接触孔可以被填满。

142.在步骤s440中,请参阅图27,对接触材料层400a进行化学机械抛光之后,第二图形化层800上表面的接触材料层400a被去除,剩余在至少部分第一接触孔内的接触材料层400a形成各晶体管的第一接触结构410。此时,第二图形化层800同时起到掩膜与抛光停止层的作用。

143.例如,第一接触结构410包括第二金属阻挡层以及第二金属层。化学机械剖光后,剩余在各个第一接触孔内的第二金属阻挡材料层形成各晶体管的第二金属阻挡层,剩余在各个第一接触孔内的的第二金属材料层形成各晶体管的第二金属层。

144.作为示例,同一有源层单元内,多个有源层210的第一接触结构410排列成两排,相邻两个第一接触结构410分别位于不同排。

145.此时,可以有效增大各个电容结构500间的距离,从而降低各电容结构500之间的耦合作用,从而降低各电容结构500之间的相互影响。

146.在一个实施例中,各层有源层210的第二图形212在远离沟道图形一侧也呈阶梯状分布。作为示例,可以在通过前文介绍的实施方式,在步骤s220中,对各组基础材料层10的两侧同时进行刻蚀,以使得刻蚀后的各组图形化材料层20在其相对的两侧均呈阶梯状分

布。

147.同时,第二图形化层800的第二开口定义的第一接触孔,还可以用于形成多个第二接触结构420,多个第二接触结构420分别位于各有源层210的第二图形212上方,从而连接位线结构(未图示)。此时,步骤s420可以在沟道图形213的两侧,在呈阶梯状的各层第一图形211与呈阶梯状的各层第二图形212上方均形成第一接触孔。

148.请参阅图27,对接触材料层400a进行化学机械抛光之后,第二接触结构420与第一接触结构410同时形成。各第一图形211上方的第一接触孔内形成高度不同的第一接触结构410。各第二图形212上方的第一接触孔内形成高度不同的第二接触结构420。

149.同时,第二图形化层800的第二开口定义的第一接触孔,还可以用于形成多个第三接触结构430,多个第三接触结构430分别位于顶部的栅极结构300的上方,从而连接字线结构(未图示)。例如,每个有源层单元的位于顶部的栅极结构300上层结构(包括第三介质层630、第二介质层620以及第一图形化层700)均可以被刻蚀。对接触材料层400a进行化学机械抛光之后,第三接触结构430、第二接触结构420与第一接触结构410同时形成。

150.在一个实施例中,步骤s500包括:

151.步骤s510,请参阅图28,于第二图形化层800上表面以及第一接触结构410上表面形成第四介质层640;

152.步骤s520,请参阅图29,于第四介质层640上表面形成第三图形化层900,第三图形化层900具有第三开口,第三开口定义出第二接触孔的形状及位置;

153.步骤s530,请参阅图29,基于第三图形化层900,刻蚀第四介质层640,以形成多个第二接触孔;

154.步骤s540,于各第二接触孔内形成第一电极层;

155.步骤s550,于第一电极层表面以及第三图形化层900表面形成绝缘介质层;

156.步骤s560,请参阅图30,于绝缘介质层表面形成第二电极层510。

157.在步骤s510中,第四介质层640可以包括但不限于为sio2层。

158.在步骤s520中,第三图形化层900可以包括但不限于为sin层。

159.例如可以在第四介质层640上表面沉积第三图形化层900的第三材料层,然后于第三材料层表面形成第三图形化光阻,然后基于第三图形化光阻刻蚀第三材料层,以形成第三图形化层900。之后,去除第三图形化光阻。

160.在步骤s530中,第三图形化层900作为掩膜,刻蚀第四介质层640。第二接触孔的数量与第一接触结构410的数量相同,且各第二接触孔的位置与各第一接触结构410的位置相对应,每个第二接触孔均暴露一个第一接触结构410。

161.在步骤s540中,作为示例,第一电极层可以包括但不限于为tin层。

162.例如,可以首先在第三图形化层900以及第二接触孔内形成第一电极材料层。然后,以第三图形化层900为抛光停止层,对第一电极材料层进行化学机械抛光,去除第三图形化层900表面的第一电极材层,剩余保留在第二接触孔内的第一电极材料层形成第一电极层。

163.当然,在其他实施例中,第一电极层的形式并不限于此,例如其也可以由第二接触孔内延伸至第三图形化层900的部分表面上,只要保证各个第二接触孔内的第一电极层相互绝缘即可。

164.在步骤s550中,绝缘介质层可以包括但不限于为hfo2。

165.在步骤s560中,作为示例,第二电极层510包括tin层531以及gesi层532。此时,本步骤可以包括:

166.步骤s561,于绝缘介质层表面形成tin层531;

167.步骤s562,于tin层531表面形成gesi层532,gesi层532填满第二接触孔。

168.当然,第二电极层510的形式并不限于此,在其他示例中,第二电极层的材料也可以为其他导电材料,或者,第二导电层的层数也并不限于为两层,其也可以为一层或者多层。

169.本实施例中,绝缘介质层与第二电极层510为各个电容结构500共用,从而降低了工艺复杂性。

170.应该理解的是,虽然图1的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,图1中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

171.在一个实施例中,请参阅图30以及图31,还提供一种半导体结构,包括衬底100、至少一个有源层单元、多个栅极结构300、多个第一接触结构410以及多个电容结构500。

172.每个有源层单元均包括层叠设置的多层有源层210以及设置在相邻有源层210之间的隔离层220。

173.有源层210包括第一图形211、第二图形212以及沟道图形213。第一图形211与第二图形212中的其中一者为源极图形,另一者为漏极图形。沟道图形213连接第一图形211与第二图形212。

174.各层有源层210的第一图形211在远离沟道图形213一侧呈阶梯状分布,且相邻第一图形211之间具有隔离层220,相邻第二图形211之间具有隔离层220。

175.多个栅极结构300分别环绕于各沟道图形213外周。

176.多个第一接触结构410分别位于各第一图形213上方。

177.多个电容结构500分别位于各第一接触结构410上方。

178.在一个实施例中,半导体结构还包括第一图形化层700。第一图形化层700覆盖于顶层的有源层210上表面,定义有源层210的位置。

179.在一个实施例中,第一图形化层700上表面与顶部的栅极结构300的上表面齐平。

180.在一个实施例中,同一有源层单元内,多个有源层210的第一接触结构410排列成两排,相邻两个第一接触结构410分别位于不同排。

181.此时,可以有效增大各个电容结构500间的距离,从而降低各电容结构500之间的耦合作用,从而降低各电容结构500之间的相互影响。

182.在一个实施例中,半导体结构还包括第二图形化层800。第二图形化层800具有第二开口,第二开口定义出第一接触孔的形状及位置,多个第一接触结构位于不同的第一接触孔内。

183.在一个实施例中,各层有源层210的第二图形212在远离沟道图形一侧呈阶梯状分

布。且半导体结构还包括多个第二接触结构420与多个第三接触结构430。多个第二接触结构420分别位于各第二图形212上方。多个第三接触结构430分别位于顶部的各栅极结构300的上方。多个第一接触结构410、多个第二接触结构420以及多个第三接触结构430均位于不同的第一接触孔内。

184.在一个实施例中,半导体结构还包括第三图形化层900,第三图形化层900具有第三开口,第三开口定义出第二接触孔的形状及位置,电容结构500填充第二接触孔。

185.在一个实施例中,电容结构500包括第一电极层、绝缘介质层以及第二电极层510。第一电极层位于第二接触孔内,绝缘介质层位于第一电极层表面以及第三图形化层900表面,第二电极层510位于绝缘介质层表面。

186.在一个实施例中,第二电极层510包括tin层531以及gesi层532,tin层531位于绝缘介质层表面,gesi层532位于tin层531表面且填满第二接触孔。

187.关于半导体结构的具体限定可以参见上文中对于半导体结构的制作方法的限定,在此不再过多赘述。

188.在一个实施例中,还提供一种存储器,该存储器可包括上述任一实施方式中的反熔丝结构。例如,该存储器可以是动态随机存取存储器(dynamic random access memory,dram),但不限于此。

189.在本说明书的描述中,参考术语“一个实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

190.上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

191.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1