一种化学掺杂碳制备高阻值埋嵌式电阻的方法与流程

1.本发明涉及电子材料及电子元器件技术领域,特别是涉及一种埋嵌式薄膜电阻材料及其制备方法。

背景技术:

2.电子产品的速度、功能、性能和便携性不断提高,对集成电路封装尺寸小型化,高集成化要求越来越高,为了满足集成电路内部元件的数量和嵌入式无源元件的急剧增加趋势与有限的印制电路板面积的矛盾。一种解决方案是将这些无源元件嵌入印刷电路板。嵌入式无源元件具有表面空间小、安装成本低、信号质量高以及通过最小化焊点数量和布线距离降低寄生效应。嵌入式薄膜电阻(embedded thin film resistance,etfr)作为嵌入式无源元件之一,在节省印制电路板(printed circuit board,pcb)空间方面发挥着重要作用。

3.目前,集成电阻的制造路线包括丝网印刷金属厚膜电阻、蚀刻金属薄膜电阻、磁控溅射薄膜电阻、化学镀金属薄膜电阻、气溶胶喷射打印。典型的如ti-n,ni-cr,ta-n,ni-p和ta-si,由于其高可靠性,较低的tcr和对pcb制造工艺的适应性,已被选为集成电阻材料。其中ni-cr埋阻材料的生产经过多次蚀刻工艺调整,电阻误差高于15%,无法生产高精度电阻;ni-p因其在高频和脉冲加热下的特定高电阻稳定性、在柔性聚酰亚胺基板上具有优异的机械柔韧性以及其制造程序的简单性而引起了相当大的关注,但ni-p薄膜材料因其较低方阻在电阻值超过10kω的嵌入式电阻器中的应用有限。为了改善电阻器在高频下寄生效应的影响,电阻器宽度应尽可能小,因而集成电阻材料的方阻值应尽可能大。因此,ni-p合金作为etfr材料的性能仍有待进一步提高,如更低的tcr、高阻值和高精度薄膜电阻的要求。

4.基于上述对高方阻电阻需求,本发明提供了一种化学掺杂碳制备高阻值埋嵌式电阻的方法。通过使用阻值添加剂促使形成ni-p-c的三元合金,提高ni-p的阻值。通过hfss电磁场仿真模拟高阻值ni-p-c在解决寄生效应方面具有明显的优势,因而在高频应用场景下具有很好的前景。

技术实现要素:

5.本发明所要解决的技术问题是针对目前埋嵌薄膜ni-p电阻材料低方阻导致在阻值超过10kω的嵌入式电阻器中的应用有限,提供一种化学掺杂碳制备高阻值埋嵌式电阻的方法。通过c原子半径小以间隙原子的形式进入ni晶格,随着c元素的增加,进而解决形成的ni-p膜层松软电性能不稳定的问题,并同时实现c元素的增加,会使薄膜的非晶成分增长,引起无序的原子排布增加,从而增大薄膜的方阻值,得到高方阻电阻,最终高方阻和减小阻值误差等效果,实现高频高速条件下降低寄生效应的要求。

6.为解决上述技术问题,本发明提供一种化学掺杂碳制备高阻值埋嵌式电阻的方法,包括如下步骤:

7.步骤1:印制电路图形化

8.采用印制电路制作工艺在覆铜板表面制作电阻图形,得到图形化的印制电路板;

9.步骤2:氯化亚锡敏化/水解

10.将图形化的印制电路板浸泡于氯化亚锡水溶液中进行敏化,敏化后将图形化印制电路板浸泡于去离子水中进行水解,将图形化印制电路板基材表面沉积一层微溶于水的亚锡盐凝胶状物sn2(oh)3cl;

11.步骤3:氯化钯活化

12.将基材表面沉积了sn2(oh)3cl的图形化印制电路板浸泡于氯化钯pdcl2水溶液中,使得sn2(oh)3cl将氯化钯溶液的pd

2+

离子还原为pd原子并沉积于图形化印制电路板的基材表面,从而形成了化学镀活化中心;

13.步骤4:图形制作

14.在经过步骤3处理过后的图形化印制电路板表面贴胶带,使用电阻图形胶带遮住无需制作埋嵌式电阻区域,露出埋嵌式电阻制作区域;

15.步骤5:化学镀埋嵌式电阻

16.在埋嵌式电阻制作区域进行化学镀,得到镍含量为52~82%、磷含量为8~29%、碳含量4~11%、氧含量3.5~8%的化学镀液,化学镀液的配方中各组分浓度为:硫酸镍或氯化镍10-55g/l,次亚磷酸钠10~50g/l,缓冲液2~20g/l,络合剂5~40g/l,阻值调节剂0~4ml/l,镀液配制完成时采用ph值调节剂调节ph值为4.5~6.5之间,镀液使用过程保持温度为70~90摄氏度之间;

17.步骤6:退火

18.在120~200摄氏度温度下,对于步骤5所得的碳掺杂镍磷合金埋嵌电阻进行热处理30分钟以上,得到阻值稳定的埋嵌式电阻。

19.作为优选方式,步骤5中所述缓冲液为醋酸钠或醋酸钾中的至少一种。

20.作为优选方式,步骤5中所述络合剂为柠檬酸钠、丁二酸、硫脲、dl苹果酸或乳酸、三乙胺中的至少一种。

21.作为优选方式,步骤5中所述阻值调节剂为二乙烯三胺或β-丙氨酸中的至少一种。

22.作为优选方式,步骤5中所述ph调节剂为氨水、氢氧化钠、氢氧化钾、冰醋酸中的至少一种。

23.作为优选方式,步骤6退火处理具体为将经过去离子水清洗后的电阻放入烘箱烘干至表面干燥。

24.需要说明的是锡元素为多价阳离子,所以制备sncl2水溶液时,需要加入一定量的浓盐酸以防止sncl2水溶液中的sn

2+

氧化成sn

4+

;配制pdcl2时难溶于水,也需要加入一定量的浓盐酸以增加pdcl2的溶解性。

25.上述技术方案中:所述ph值缓冲剂为醋酸钠或醋酸钾,所起的作用就是恒定镀液ph值在设定的范围,所述络合剂为柠檬酸,丁二酸,硫脲,dl苹果酸或乳酸中的一种或者多种,所起的作用就是络合ni

2+

,在化学镀液中释放固定量的ni

2+

;所述ph值调节剂为氨水,氢氧化钠或者氢氧化钾中的一种或者多种,作用就是调节ph值到所需的值;所述阻值调节剂为二乙烯三胺或β-丙氨酸中的一种或者多种,所起的作用就是使得化学镀液形成的是碳掺杂的ni-p薄膜。

26.镀液中通过添加阻值调节剂使得小原子半径的非金属元素碳可以改善ni-p薄膜结构,从而提高电阻层材料的电阻率,电阻层材料方块电阻随着镀液配方中阻值调节剂的含量增加而增加。

27.本发明制备的埋嵌式电阻材料是多孔结构,含镍含量为52-82%,磷含量为8-29%,碳含量4-11%,氧含量3.5-8%,通过化学镀方法并且使用在线监控技术沉积得到的碳掺杂镍磷薄膜,经实验表面,具有方块电阻大(最高可达731ω/sq),阻值稳定性好等特点,为镍磷电阻的改性研究做出实验推进,并制作工艺简单,易于在印制电路企业推广。

附图说明:

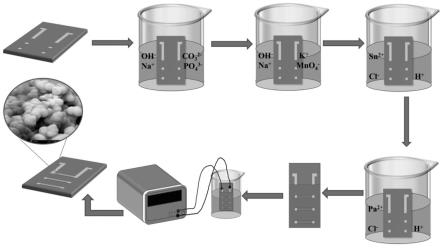

28.图1为本发明实施方式的化学掺杂碳制备高阻值埋嵌式电阻的制备方法的流程图;

29.图2(a-e)分别为二乙烯三胺浓度为0,1,2,3,4ml/l下化学掺杂碳制备高阻值埋嵌式电阻材料sem图,(f)为二乙烯三胺2ml/l侧视图;可明显看出本发明化学掺杂碳后多孔结构晶包大小的区别。

30.图3为本发明所制备的埋嵌式薄膜电阻材料的eds图。横坐标为能量,单位为kev;纵坐标为强度,单位为c/s;图中主要成分为ni,p,c元素。

31.图4为本发明埋嵌式薄膜电阻材料的方块电阻值随阻值调节剂的含量变化图。横坐标为二乙烯三胺的含量,单位为ml/l,纵坐标为方块电阻阻值为ω/sq.。

32.图5为埋嵌式薄膜电阻材料层压前后的电阻沉积区的阻值影响情况和层压后sem图;

33.图6为埋嵌式薄膜电阻材料的电阻温度系数(tcr)随温度的变化曲线情况和tcr测试后sem图;

34.图7为埋嵌式电阻不同方阻和贴片式电阻的寄生电阻的寄生电阻的仿真结果变化曲线情况。

具体实施方式:

35.实施例提供一种化学掺杂碳制备高阻值埋嵌式电阻的方法,包括如下步骤:

36.步骤1:印制电路图形化

37.采用印制电路制作工艺在覆铜板表面制作电阻图形,得到图形化的印制电路板;

38.步骤2:氯化亚锡敏化/水解

39.将图形化的印制电路板浸泡于氯化亚锡水溶液中进行敏化,敏化后将图形化印制电路板浸泡于去离子水中进行水解,将图形化印制电路板基材表面沉积一层微溶于水的亚锡盐凝胶状物sn2(oh)3cl;

40.步骤3:氯化钯活化

41.将基材表面沉积了sn2(oh)3cl的图形化印制电路板浸泡于氯化钯pdcl2水溶液中,使得sn2(oh)3cl将氯化钯溶液的pd

2+

离子还原为pd原子并沉积于图形化印制电路板的基材表面,从而形成了化学镀活化中心;

42.步骤4:图形制作

43.在经过步骤3处理过后的图形化印制电路板表面贴胶带,使用电阻图形胶带遮住

无需制作埋嵌式电阻区域,露出埋嵌式电阻制作区域;

44.步骤5:化学镀埋嵌式电阻

45.在埋嵌式电阻制作区域进行化学镀,得到镍含量为52~82%、磷含量为8~29%、碳含量4~11%、氧含量3.5~8%的化学镀液,化学镀液的配方中各组分浓度为:硫酸镍或氯化镍10-55g/l,次亚磷酸钠10~50g/l,缓冲液2~20g/l,络合剂5~40g/l,阻值调节剂0~4ml/l,镀液配制完成时采用ph值调节剂调节ph值为4.5~6.5之间,镀液使用过程保持温度为70~90摄氏度之间;

46.步骤5中所述缓冲液为醋酸钠或醋酸钾中的至少一种。

47.步骤5中所述络合剂为柠檬酸钠、丁二酸、硫脲、dl苹果酸或乳酸、三乙胺中的至少一种。

48.步骤5中所述阻值调节剂为二乙烯三胺或β-丙氨酸中的至少一种。

49.步骤5中所述ph调节剂为氨水、氢氧化钠、氢氧化钾、冰醋酸中的至少一种。

50.步骤6:退火

51.在120~200摄氏度温度下,对于步骤5所得的碳掺杂镍磷合金埋嵌电阻进行热处理30分钟以上,得到阻值稳定的埋嵌式电阻。

52.退火处理具体为将经过去离子水清洗后的电阻放入烘箱烘干至表面干燥。

53.对比例

54.采用macdermid incorporated公司提供的埋嵌式电阻制备工艺制备埋嵌式薄膜电阻具体过程如下:

55.(1)基板碱性除油:

56.除油配方为:碳酸钠35g/l,磷酸钠50g/l,氢氧化钠25g/l;

57.第一步:将配好的化学除油溶液,置于恒温水浴锅中,调节水浴锅为预设值温度为50-60℃;

58.第二步:待温度上升到预设温度后,将样品放入除油溶液中,并将除油溶液烧杯放在超声波清洗机,超声清洗5-15min;

59.第三步:除油完毕后,取出基板用去离子水将样品双面冲洗3次之后,放入有去离子水的烧杯中,超声清洗2min;

60.(2)氯化亚锡敏化水解

61.将碱性除油后的印制电路基板浸泡于氯化亚锡水溶液中敏化,敏化工艺条件为:

62.表1敏化液

63.氯化亚锡(sncl2.h2o)40g/l浓盐酸10ml/l温度室温时间4min

64.将敏化后的基板取出放置于去离子水中水解3min,水解生成微溶于水的亚锡盐凝胶状物sn2(oh)3cl并均匀的沉积在基材表面上,sn2(oh)3cl作为还原剂在活化处理是把活化剂氯化钯溶液的pd

2+

离子还原为pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

65.最后将敏化水解后的基板取出后用去离子水清洗两次。

66.(3)氯化钯活化:

67.将上步骤中去离子水清洗后的基板浸泡于氯化钯水溶液中进行还原反应,sn

2+

离子把氯化钯水溶液中的pd

2+

离子还原为pd原子,pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。活化工艺条件见表2:

68.表2活化液

69.氯化钯0.5g/l浓盐酸10ml/l温度室温时间3min

70.(4)化学镀电阻材料

71.将上述基板放置于镀液中,使用的水浴锅稳定镀液温度,并将搅拌速度100-200r/min有助于镀液的反应。其工艺条件见表3:

72.表3化学镀埋嵌式薄膜ni-p电阻材料工艺条件:

73.硫酸镍33g/l次亚磷酸钠40g/l缓冲液(醋酸钠)10g/l络合剂(柠檬酸)23.4g/l温度(水浴)90℃时间10min

74.(5)去离子水冲

75.将化学镀电阻材料化学镀10min后,使用去离子水冲洗埋嵌电阻,然后使用真空烘干箱30℃烘干30min。

76.(6)测试方阻

77.将上述步骤埋嵌电阻,使用四探针测试仪测试方块电阻并至少测试不同位置三次取平均值,方块电阻阻值为17.1ω/sq.。

78.将电阻材料放置于120℃热处理30min,电阻方阻为17.1ω/sq.。

79.由上述对比实施方案可以看出,采用基本配方所制备的埋嵌式电阻制备工艺所制备的埋嵌式电阻,方阻很小仅为17.1ω/sq.。

80.实施例1

81.使用0.2mm的双面覆铜板中环氧树脂为基材材料作为化学镀绝缘基板,

82.步骤1:印制电路图形化

83.采用印制电路制作工艺在覆铜板表面制作电阻图形,得到图形化的印制电路板;

84.印制电路图形化过后进行基板碱性除油:

85.除油配方为:碳酸钠35g/l,磷酸钠50g/l,氢氧化钠25g/l;

86.第一步:将配好的化学除油溶液,置于恒温水浴锅中,调节水浴锅为预设值温度为50℃;

87.第二步:待温度上升到预设温度后,将样品放入除油溶液中,并将除油溶液烧杯放在超声波清洗机,超声清洗10min;

88.第三步:除油完毕后,取出基板用去离子水将样品双面冲洗3次之后,放入有去离

子水的烧杯中,超声清洗2min;

89.步骤2:氯化亚锡敏化水解

90.将碱性除油后的印制电路基板浸泡于氯化亚锡水溶液中敏化,

91.敏化工艺条件见表4:

92.表4敏化液

93.氯化亚锡(sncl2.h2o)40g/l浓盐酸10ml/l温度室温时间4min

94.将敏化后的基板取出放置于去离子水中水解3min,水解生成微溶于水的亚锡盐凝胶状物sn2(oh)3cl并均匀的沉积在基材表面上,sn2(oh)3cl作为还原剂在活化处理是把活化剂氯化钯溶液的pd

2+

离子还原为pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

95.最后将敏化水解后的基板取出后用去离子水清洗两次。

96.步骤3:氯化钯活化:

97.将上步骤中去离子水清洗后的基板浸泡于氯化钯水溶液中进行还原反应,sn

2+

离子把氯化钯水溶液中的pd

2+

离子还原为pd原子,pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

98.活化工艺条件见表5:

99.表5活化液

100.氯化钯0.5g/l浓盐酸10ml/l温度室温时间3min

101.步骤4:图形制作

102.在经过步骤3处理过后的图形化印制电路板表面贴胶带,使用电阻图形胶带遮住无需制作埋嵌式电阻区域,露出埋嵌式电阻制作区域;

103.步骤5:化学镀埋嵌式电阻

104.在埋嵌式电阻制作区域进行化学镀,镀液配制完成时采用ph值调节剂氨水调节ph值为4.5,

105.步骤(5)使用工艺条件见表6:

106.表6化学镀埋嵌式薄膜电阻材料工艺条件

107.硫酸镍33g/l次亚磷酸钠40g/l缓冲液(醋酸钠)10g/l络合剂(柠檬酸)23.4g/l阻值调节剂(二乙烯三胺)0.5ml/l温度(水浴)90℃

时间10min

108.将步骤5中化学镀电阻材料化学镀10min后,使用去离子水冲洗使用去离子水冲洗埋嵌电阻,然后使用真空烘干箱30℃烘干30min。

109.步骤6:退火

110.在120摄氏度温度下,对于步骤5所得的碳掺杂镍磷合金埋嵌电阻进行热处理30分钟以上,得到阻值稳定的埋嵌式电阻。

111.步骤7:测试

112.然后将埋嵌式电阻材料,使用四探针测试仪测试方块电阻并至少测试不同位置三次取平均值,方块电阻阻值为609ω/sq.,后再120℃温度对电阻材料进行热处理30min,再使用四探针测试仪测试方块电阻并至少测试不同位置三次取平均值,方块电阻阻值为578ω/sq.。

113.从上述具体实施例1可看出,采用本发明提供的印制电路板用埋嵌式方阻的方法制备的埋嵌电阻材料的方阻比基础配方提供的埋嵌式电阻制备的埋嵌式电阻方阻大很多,且经过热处理后,阻值稳定(热偏差小于6%)。使用层压测试对材料进行测试,层压测试工艺见表7如下:

114.表7层压测试工艺条件

[0115][0116]

得到方阻值为563ω/sq.,说明层压对本发明所制备的埋嵌式电阻的方阻影响很小。同时使用胶带法检查制备的埋嵌式电阻结合力,结果表面结合力良好。

[0117]

实施例2

[0118]

步骤1:印制电路图形化

[0119]

采用印制电路制作工艺在覆铜板表面制作电阻图形,得到图形化的印制电路板;

[0120]

印制电路图形化过后进行基板碱性除油:

[0121]

除油配方为:碳酸钠35g/l,磷酸钠50g/l,氢氧化钠25g/l;

[0122]

第一步:将配好的化学除油溶液,置于恒温水浴锅中,调节水浴锅为预设值温度为50℃;

[0123]

第二步:待温度上升到预设温度后,将样品放入除油溶液中,并将除油溶液烧杯放在超声波清洗机,超声清洗10min;

[0124]

第三步:除油完毕后,取出基板用去离子水将样品双面冲洗3次之后,放入有去离子水的烧杯中,超声清洗2min;

[0125]

步骤2:氯化亚锡敏化水解

[0126]

将碱性除油后的印制电路基板浸泡于氯化亚锡水溶液中敏化,

[0127]

敏化工艺条件见表8:

[0128]

表8敏化液

[0129]

氯化亚锡(sncl2.h2o)40g/l浓盐酸10ml/l温度室温时间4min

[0130]

将敏化后的基板取出放置于去离子水中水解3min,水解生成微溶于水的亚锡盐凝胶状物sn2(oh)3cl并均匀的沉积在基材表面上,sn2(oh)3cl作为还原剂在活化处理是把活化剂氯化钯溶液的pd

2+

离子还原为pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

[0131]

最后将敏化水解后的基板取出后用去离子水清洗两次。

[0132]

步骤3:氯化钯活化:

[0133]

将上步骤中去离子水清洗后的基板浸泡于氯化钯水溶液中进行还原反应,sn

2+

离子把氯化钯水溶液中的pd

2+

离子还原为pd原子,pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

[0134]

活化工艺条件见表9:

[0135]

表9活化液

[0136]

氯化钯0.5g/l浓盐酸10ml/l温度室温时间3min

[0137]

步骤4:图形制作

[0138]

在经过步骤3处理过后的图形化印制电路板表面贴胶带,使用电阻图形胶带遮住无需制作埋嵌式电阻区域,露出埋嵌式电阻制作区域;

[0139]

步骤5:化学镀埋嵌式电阻

[0140]

在埋嵌式电阻制作区域进行化学镀,镀液配制完成时采用ph值调节剂氢氧化钠调节ph值为5.5之间,

[0141]

步骤(5)使用工艺条件见表10:

[0142]

表10化学镀埋嵌式薄膜电阻材料工艺条件

[0143]

氯化镍55g/l次亚磷酸钠50/l缓冲液(醋酸钾)20g/l络合剂(丁二酸)40g/l阻值调节剂(二乙烯三胺)2ml/l温度(水浴)85℃时间8min

[0144]

将步骤5中化学镀电阻材料化学镀8min后,使用去离子水冲洗使用去离子水冲洗

埋嵌电阻,然后使用真空烘干箱30℃烘干30min。

[0145]

步骤6:退火

[0146]

在200摄氏度温度下,对于步骤5所得的碳掺杂镍磷合金埋嵌电阻进行热处理30分钟以上,得到阻值稳定的埋嵌式电阻。

[0147]

步骤7:测试

[0148]

然后将埋嵌式电阻材料,使用四探针测试仪测试方块电阻并至少测试不同位置三次取平均值,方块电阻阻值为731ω/sq。

[0149]

实施例3

[0150]

设计直线型埋嵌电阻,能实现高阻值在线监控,验证碳掺杂镍磷埋嵌薄膜电阻材料的广泛应用性并验证层压对电阻的影响。

[0151]

步骤1:印制电路图形化

[0152]

采用印制电路制作工艺在覆铜板表面制作直线型电阻图形,得到图形化的印制电路板;

[0153]

印制电路图形化过后进行基板碱性除油:

[0154]

除油配方为:碳酸钠35g/l,磷酸钠50g/l,氢氧化钠25g/l;

[0155]

第一步:将配好的化学除油溶液,置于恒温水浴锅中,调节水浴锅为预设值温度为50℃;

[0156]

第二步:待温度上升到预设温度后,将样品放入除油溶液中,并将除油溶液烧杯放在超声波清洗机,超声清洗10min;

[0157]

第三步:除油完毕后,取出基板用去离子水将样品双面冲洗3次之后,放入有去离子水的烧杯中,超声清洗2min;

[0158]

步骤2:氯化亚锡敏化水解

[0159]

将碱性除油后的印制电路基板浸泡于氯化亚锡水溶液中敏化,

[0160]

敏化工艺条件见表11:

[0161]

表11敏化液

[0162]

氯化亚锡(sncl2.h2o)40g/l浓盐酸10ml/l温度室温时间4min

[0163]

将敏化后的基板取出放置于去离子水中水解3min,水解生成微溶于水的亚锡盐凝胶状物sn2(oh)3cl并均匀的沉积在基材表面上,sn2(oh)3cl作为还原剂在活化处理是把活化剂氯化钯溶液的pd

2+

离子还原为pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

[0164]

最后将敏化水解后的基板取出后用去离子水清洗两次。

[0165]

步骤3:氯化钯活化:

[0166]

将上步骤中去离子水清洗后的基板浸泡于氯化钯水溶液中进行还原反应,sn

2+

离子把氯化钯水溶液中的pd

2+

离子还原为pd原子,pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

[0167]

活化工艺条件见表12:

[0168]

表12活化液

[0169]

氯化钯0.5g/l浓盐酸10ml/l温度室温时间3min

[0170]

步骤4:图形制作

[0171]

在经过步骤3处理过后的图形化在印制电路板上贴干膜,使用电阻图形掩膜版曝光,显影后在需要制作电阻的区域除去干膜,以备下一步化学镀电阻薄膜材料;

[0172]

步骤5:化学镀埋嵌式电阻

[0173]

在埋嵌式电阻制作区域进行化学镀,镀液配制完成时采用ph值调节剂调节ph值为5,

[0174]

步骤(5)使用工艺条件见表13:

[0175]

表13化学镀埋嵌式薄膜电阻材料工艺条件

[0176][0177][0178]

将步骤5中化学镀电阻材料化学镀使用keithley2400 source meter仪器在线监控电压为5.4mv时,使用去离子水冲洗使用去离子水冲洗埋嵌电阻,然后使用真空烘干箱30℃烘干30min。

[0179]

步骤6:退火

[0180]

在160摄氏度温度下,对于步骤5所得的碳掺杂镍磷合金埋嵌电阻进行热处理30分钟以上,得到阻值稳定的埋嵌式电阻。

[0181]

步骤7:测试

[0182]

然后将埋嵌式电阻材料,使用keithley2400 source meter仪器测试埋嵌电阻两端的阻值见表14。

[0183]

表14

[0184]

电阻位置层压前ω层压后ω1241.6231.3762228.432225.3253221.035218.0254228.189223.1975238.752231.3576228.052219.354

[0185]

层压前后电阻如图5所示。层压测试结束后采用keithley2400 source meter仪器

测试电阻沉积区电阻阻值,图5可看出,埋嵌电阻阻值变化小表明层压对埋嵌电阻阻值影响较小。并且镀层没有发生破裂起皮等不良现象,说明层压对镍磷镀层形貌没有影响。

[0186]

实施例4

[0187]

使用环氧树脂基材,在其图形化上形成埋嵌式电阻,其制备流程如下:

[0188]

验证碳掺杂镍磷埋嵌薄膜电阻材料的广泛应用性及电阻的热稳定性。

[0189]

步骤1:印制电路图形化

[0190]

采用印制电路制作工艺在覆铜板表面制作电阻图形,得到图形化的印制电路板;

[0191]

步骤1印制电路图形化过后进行基板碱性除油:

[0192]

除油配方为:碳酸钠35g/l,磷酸钠50g/l,氢氧化钠25g/l;

[0193]

第一步:将配好的化学除油溶液,置于恒温水浴锅中,调节水浴锅为预设值温度为50℃;

[0194]

第二步:待温度上升到预设温度后,将样品放入除油溶液中,并将除油溶液烧杯放在超声波清洗机,超声清洗10min;

[0195]

第三步:除油完毕后,取出基板用去离子水将样品双面冲洗3次之后,放入有去离子水的烧杯中,超声清洗2min;

[0196]

步骤2:氯化亚锡敏化水解

[0197]

将碱性除油后的印制电路基板浸泡于氯化亚锡水溶液中敏化,

[0198]

敏化工艺条件见表15:

[0199]

表15敏化液

[0200]

氯化亚锡(sncl2.h2o)40g/l浓盐酸10ml/l温度室温时间4min

[0201]

将敏化后的基板取出放置于去离子水中水解3min,水解生成微溶于水的亚锡盐凝胶状物sn2(oh)3cl并均匀的沉积在基材表面上,sn2(oh)3cl作为还原剂在活化处理是把活化剂氯化钯溶液的pd

2+

离子还原为pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

[0202]

最后将敏化水解后的基板取出后用去离子水清洗两次。

[0203]

步骤3:氯化钯活化:

[0204]

将上步骤中去离子水清洗后的基板浸泡于氯化钯水溶液中进行还原反应,sn

2+

离子把氯化钯水溶液中的pd

2+

离子还原为pd原子,pd原子并附着于图形化印制电路板的基材表面,从而形成了化学镀活化中心。

[0205]

活化工艺条件见表16:

[0206]

表16活化液

[0207]

氯化钯0.5g/l浓盐酸10ml/l温度室温时间3min

[0208]

步骤4:图形制作

[0209]

在经过步骤3处理过后的图形化印制电路板表面贴胶带,使用电阻图形胶带遮住无需制作埋嵌式电阻区域,露出埋嵌式电阻制作区域;

[0210]

步骤5:化学镀埋嵌式电阻

[0211]

在埋嵌式电阻制作区域进行化学镀,镀液配制完成时采用ph值调节剂氨水调节ph值为6;

[0212]

步骤(5)使用工艺条件见表17:

[0213]

表17化学镀埋嵌式薄膜电阻材料工艺条件

[0214]

氯化镍40g/l次亚磷酸钠35.2/l缓冲液(醋酸钾)14g/l络合剂(柠檬酸钠)36g/l阻值调节剂(二乙烯三胺)4ml/l温度(水浴)90℃监控电压3.4min

[0215]

将步骤5中化学镀电阻材料化学镀8min后,使用去离子水冲洗使用去离子水冲洗埋嵌电阻,然后使用真空烘干箱30℃烘干30min。

[0216]

步骤6:退火

[0217]

在120摄氏度温度下,对于步骤5所得的碳掺杂镍磷合金埋嵌电阻进行热处理30分钟以上,得到阻值稳定的埋嵌式电阻。

[0218]

步骤7:测试

[0219]

采用keithley2400 source meter仪器测试埋嵌电阻沉积区电阻随温度从20℃到120℃改变所引起的阻值变化,如图6所示,电阻沉积区电阻阻值随温度升高在增加,图6所示tcr测试对镀层表面没有影响,可知温度的变化对电阻沉积区电阻影响小,可用于制作埋嵌电阻,电阻热稳定好。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1