半导体芯片结构制造方法、半导体载板及半导体芯片结构与流程

1.本发明涉及一种半导体芯片结构制造方法、半导体载板及半导体芯片结构。

背景技术:

2.目前全球正遭遇半导体供应短缺的问题,特别是计算机芯片,由于芯片是一切电子产品的大脑,随着全球半导体短缺的加剧,消费者势必面临各种电子产品(如电视、手机、汽车、游戏机等)的价格上涨和产品短缺的问题。随着生产从因冠状病毒大流行而导致的暂时延迟中渐渐恢复正常,因大流行而改变习惯所驱动的新的需求激增意味着现在已达到危机点,但是,没有迹象表明供应充足,也没有需求下降的迹象。

3.因此,当前正迫切需要一种以有功效且高效率的方式制造半导体芯片结构的方法。

技术实现要素:

4.本发明的目的是提供一种以有功效且高效率的方式制造半导体芯片结构的半导体芯片结构制造方法,以及配合此制造方法所制造的半导体载板及半导体芯片结构。

5.为达上述目的,依据本发明的一种半导体芯片结构的制造方法,包括:在工艺载板的表面上提供彼此拼接的多个切片单元,其中各个切片单元分别从晶圆制造而得,并且分别包括具有轮廓的基板,且相邻两个切片单元之间形成间隙;平坦化这些切片单元的顶部;在这些切片单元上分别形成电路,以便将这些切片单元转变成多个电路切片单元;以及至少切割这些电路切片单元,以形成多个彼此独立的半导体芯片结构;其中,这些切片单元的平面尺寸分别不小于所对应的半导体芯片结构的平面尺寸,或者这些切片单元的这些平面尺寸分别不小于对应的这些半导体芯片结构的这些平面尺寸的倍数。

6.在一个实施例中,该基板为单晶硅基板、多晶硅基板、soi(silicon on insulator)基板、sic基板、蓝宝石基板、iii-v族化合物基板、ii-vi族化合物基板、或i-iii-vi族化合物基板。

7.在一个实施例中,该iii-v族化合物基板为gaas基板、gan基板、inp基板、gap基板、gasb基板、inas基板、或insb基板。

8.在一个实施例中,该ii-vi族化合物基板为cdte基板、cds基板、znte基板、znse基板、或zns基板。

9.在一个实施例中,该i-iii-vi族化合物基板为cuinse2基板或cigs基板。

10.在一个实施例中,工艺载板为玻璃基板。

11.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的切片单元的步骤中,这些切片单元直接接合于该工艺载板。

12.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的切片单元的步骤中,这些切片单元经由阳极接合方式、熔合接合方式、或直接接合方式直接接合于该工艺载板。

13.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的切片单元的步骤中,

这些切片单元经由中间材料间接接合于该工艺载板。

14.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的切片单元的步骤中,这些切片单元以黏着剂接合方式、玻璃胶接合方式、低熔点玻璃接合方式、金属接合方式、共晶接合方式、或介电接合方式,间接接合于该工艺载板。

15.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的切片单元的步骤中,这些切片单元经由黏着层、铟、锡、或sno-zno-p2o5的低熔点玻璃,间接接合于该工艺载板。

16.在一个实施例中,该黏着层的热膨胀系数等于或接近该基板的热膨胀系数。

17.在一个实施例中,该黏着层为剥离层。

18.在一个实施例中,该黏着层由聚酰亚胺(pi,polyimide)制成。

19.在一个实施例中,该黏着层的数量为复数个,分别连接这些切片单元。

20.在一个实施例中,该黏着层的数量为单一个,连接这些切片单元。

21.在一个实施例中,进一步包含:在在该工艺载板的该表面上提供彼此拼接的切片单元的步骤之前,切割各个切片单元为复数个芯片单元,并维持这些切片单元的轮廓,其中这些芯片单元的平面尺寸分别等于对应的这些半导体芯片结构的平面尺寸。

22.在一个实施例中,进一步包含:在切割各个切片单元为这些芯片单元之前,在该切片单元的底面上贴上膜层。

23.在一个实施例中,在贴上该膜层的步骤中,各个芯片单元的尺寸等于各个半导体芯片结构的尺寸。

24.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的这些切片单元的步骤中,各个切片单元的尺寸等于或受限于直径为6英寸、8英寸或12英寸的圆形。

25.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的这些切片单元的步骤中,该基板的该轮廓被定义为多边形轮廓。

26.在一个实施例中,该多边形轮廓为四边形轮廓、五边形轮廓、六边形轮廓、或八边形轮廓。

27.在一个实施例中,进一步包含:在在该工艺载板的该表面上提供彼此拼接的这些切片单元的步骤之前,切割各个切片单元,以便将该轮廓从圆形轮廓改变成多边形轮廓。

28.在一个实施例中,该工艺载板的平面尺寸不小于各个切片单元的该平面尺寸的倍数。

29.在一个实施例中,进一步包含:在在该工艺载板的该表面上提供彼此拼接的这些切片单元的步骤之前、之中或之后,研磨对应的该切片单元的该基板。

30.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的这些切片单元的步骤中,各个切片单元的该基板定义有厚度,该厚度大于0.4mil(10nm)且不大于100μm。

31.在一个实施例中,其中各个切片单元的该基板的该厚度的范围为40nm至60nm。

32.在一个实施例中,在该工艺载板的该表面上提供彼此拼接的这些切片单元的步骤中,这些切片单元的这些基板的这些平面尺寸彼此相等。

33.在一个实施例中,进一步包含:在平坦化这些切片单元的这些顶部的步骤中,填充密封材料在相邻的两个切片单元之间的间隙中。

34.在一个实施例中,该密封材料为钝化层。

35.在一个实施例中,该钝化层包含氧化硅(siox)和/或氮化硅(sinx)。

36.在一个实施例中,该钝化层包含al2o3、sio2、ta2o5或tio2,或包含上述材料的任意组合。

37.在一个实施例中,该密封材料的热膨胀系数与该基板的热膨胀系数相同。

38.在一个实施例中,该密封材料的热膨胀系数不大于10ppm/k且不小于0.01ppm/k。

39.在一个实施例中,该密封材料的热膨胀系数的范围为2.5~6ppm/k。

40.在一个实施例中,该密封材料利用旋涂玻璃(sog)工艺或旋涂掺杂(sod)工艺形成于该基板及该间隙。

41.在一个实施例中,进一步包含:在填充该密封材料在相邻的两个切片单元之间的该间隙中的步骤之后,研磨这些切片单元的这些顶部的表面,使这些顶部的表面共同定义共平面。

42.在一个实施例中,进一步包含:在填充该密封材料在相邻的两个切片单元之间的该间隙中的步骤中,形成钝化层覆盖于该密封材料之上。

43.在一个实施例中,研磨这些切片单元的这些顶部的表面,使这些顶部的表面共同定义该共平面的步骤中,在形成该共平面时,该钝化层持续覆盖于该密封材料上。

44.在一个实施例中,在这些切片单元上形成这些电路的步骤之前,各个切片单元的该基板为不具有电路的裸基板、或具有部分电路的半成品基板。

45.在一个实施例中,在这些切片单元上形成这些电路的步骤中,形成这些电路的工艺包含蒸镀或沉积、微影、退火、旋涂玻璃或掺杂(扩散或离子植入)、或上述步骤的任意组合。

46.在一个实施例中,进一步包含:在形成这些半导体芯片结构的步骤之前或之中,利用激光处理切割这些电路切片单元以形成边界凹口,定义这些半导体芯片结构的轮廓。

47.在一个实施例中,在切割这些电路切片单元的步骤中,对应于这些电路切片单元的这些半导体芯片结构互相连接成一体,然后被切割成个别的半导体芯片结构。

48.在一个实施例中,在切割这些电路切片单元的步骤中,对应于这些电路切片单元的这些半导体芯片结构直接被切割成个别的半导体芯片结构。

49.在一个实施例中,在形成这些半导体芯片结构的步骤中,这些半导体芯片结构具有相同的平面尺寸。

50.在一个实施例中,电路化的这些芯片单元的数量大于100。

51.在一个实施例中,电路化的这些芯片单元的数量大于1000。

52.在一个实施例中,各个半导体芯片结构包含该工艺载板的对应部分。

53.在一个实施例中,各个半导体芯片结构为具有一组电路的芯片或具有集成电路系统的芯片。

54.为达上述目的,依据本发明的半导体载板包括工艺载板、以及复数个切片单元,其中切片单元接合于工艺载板的表面上且彼此拼接,各切片单元包括基板,基板具有轮廓且相邻两个切片单元之间形成间隙;其中,各切片单元分别从晶圆制造而得,且工艺载板的热膨胀系数至少接近于基板的热膨胀系数。

55.在一个实施例中,各切片单元的该基板定义有厚度,厚度大于0.4mil、且不大于100μm。

56.在一个实施例中,各切片单元定义有外接圆,其与晶圆共同定义轴心。

57.在一个实施例中,半导体载板进一步包含黏着层,其形成于这些切片单元与工艺载板之间。

58.在一个实施例中,黏着层的材料为聚酰亚胺(pi,polyimide)。

59.在一个实施例中,工艺载板的材料为玻璃。

60.在一个实施例中,各切片单元的基板为裸基板。

61.在一个实施例中,这些切片单元的顶部通过平坦化处理。

62.在一个实施例中,这些切片单元上分别形成电路,以便将这些切片单元转变成多个电路切片单元。

63.在一个实施例中,其中这些电路切片单元包括薄膜电路。

64.在一个实施例中,其中这些电路切片单元包括晶体管。

65.为达上述目的,依据本发明的半导体芯片结构,经由切割如上所述的电路切片单元后,形成多个彼此独立的半导体芯片结构的其中之一。

66.承上所述,本发明的半导体芯片结构制造方法先在工艺载板上设置分别从晶圆制造而得的多个切片单元,然后在切片单元上分别形成电路,而形成多个电路切片单元,接着切割电路切片单元,以形成多个彼此独立的半导体芯片结构,其中切片单元的平面尺寸分别不小于对应的半导体芯片结构的平面尺寸。另外,本发明的半导体载板及半导体芯片结构可以利用上述方法制造而得。因此,本发明的半导体芯片结构制造方法能够以有功效且高效率的方式制造半导体载板,并进一步制造出半导体芯片结构。本发明的优点在于产品的多样性、工艺预算的可控性、满足不同应用的要求。

附图说明

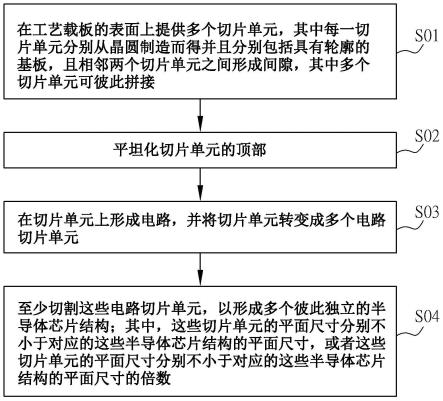

67.图1为本发明的一个实施例的半导体芯片结构制造方法的流程图。

68.图2a为本发明的一个实施方式的半导体载板的上视图。

69.图2b为在图2a所示的切片单元具有预定芯片单元的示意图。

70.图3a为本发明另一实施方式的半导体载板的上视图。

71.图3b为在图3a所示的切片单元具有预定芯片单元的示意图。

72.图4a为本发明的另一实施方式的半导体载板的上视图。

73.图4b为在图4a所示的切片单元具有预定芯片单元的示意图。

74.图5为俯视图,显示数个切片单元互相拼接并设置于工艺载板的表面上。

75.图6a为如图5所示的切片单元沿剖面线aa的剖面图,其中不同切片单元设置于单一个黏着层上。

76.图6b为如图5所示的切片单元沿剖面线aa的剖面图,其中不同切片单元分别设置于不同黏着层上。

具体实施方式

77.以下将参照相关附图,说明依据本发明优选实施例的半导体芯片结构制造方法、半导体载板及半导体芯片结构,其中相同的组件将以相同的附图标记加以说明。以下的附图只是示意,并不代表真实的尺寸与比例。

78.本发明涉及一种以有功效且高效率的方式来制造半导体芯片结构的方法,包括至

少四个主要工艺、程序或阶段,如图1所示,所述的半导体芯片结构制造方法包括:(a)在工艺载板的表面上提供多个切片单元,其中每一切片单元分别从晶圆制造而得,并且分别包括具有轮廓的基板,且相邻两个切片单元之间形成间隙,且其中多个切片单元可彼此拼接(步骤s01);(b)平坦化切片单元的顶部(步骤s02);(c)在切片单元上形成电路,并将切片单元转变成多个电路切片单元(步骤s03);以及(d)至少切割这些电路切片单元,以形成多个彼此独立的半导体芯片结构;其中,这些切片单元的平面尺寸分别不小于对应的这些半导体芯片结构的平面尺寸,或者这些切片单元的平面尺寸分别不小于对应的这些半导体芯片结构的平面尺寸的倍数(步骤s04)。

79.以下举例说明本发明的几个实施方式。

80.在步骤s01中,各切片单元2分别从晶圆制造而得,且各切片单元2包含基板,其中工艺载板1的热膨胀系数至少接近于各切片单元的基板的热膨胀系数。其中,将复数个切片单元2接合于工艺载板1上的结构,即形成半导体载板sc(如图2a、图3a、图4a所示)。

81.在步骤s01中,工艺载板1上设置有多个彼此拼接的切片单元2,各个切片单元2的基板的轮廓可以是圆形或多边形。如图2a及图2b所示,切片单元2的基板的轮廓是四边形(正方形);如图3a及图3b所示,切片单元2的基板的轮廓是五边形;如图4a及图4b所示,切片单元2的基板的轮廓是六边形。

82.在一些实施例中,基板可以是例如但不限于单晶硅基板、多晶硅基板、soi(silicon on insulator)基板、iv-iv族化合物基板、蓝宝石基板、iii-v族化合物基板、ii-vi族化合物基板、或i-iii-vi族化合物基板,其中,iv-iv族化合物基板包括sic(碳化硅)基板,iii-v族化合物基板包括gaas(砷化镓)基板、gan(氮化镓)基板、inp(磷化铟)基板、gap(磷化镓)基板、gasb(砷化镓)基板、inas(砷化铟)基板、或insb(锑化铟)基板,ii-vi族化合物基板包括cdte(碲化镉)基板、cds(硫化镉)基板、znte(碲化锌)基板、znse(硒化锌)基板、或zns(硫化锌)基板,i-iii-vi族化合物基板包括cuinse2(cis,硒化铜铟)基板或cigs(硒化铜铟镓)基板,以上说明仅为列示,并不限制。

83.在一些实施例中,工艺载板1可以是例如但不限于玻璃基板。在其他实施例中,工艺载板1可以是热膨胀系数接近所选择基板的热膨胀系数的相对应材料。

84.在一些实施例中,切片单元2可以是直接接合或间接接合于工艺载板2上。在一个实施方式中,这些切片单元2可以是经由阳极接合方式、熔合接合方式、或直接接合方式直接接合于工艺载板1上。在另一实施方式中,这些切片单元2可以是经由中间材料间接接合于工艺载板1上。

85.承上所述,在间接接合的实施方式中,这些切片单元2可以利用黏着剂(adhesive)接合方式、玻璃胶(glass-frit)接合方式、低熔点玻璃(low-melting glass)接合方式、金属接合方式、共晶(eutectic)接合方式、或介电(dielectric)接合方式,间接接合于工艺载板1。具体来说,这些切片单元2可以通过黏着剂、铟(indium)、锡(tin)、或sno-zno-p2o5的低熔点玻璃,间接接合于工艺载板1上。其中,黏着剂的热膨胀系数(cte,coefficient of thermal expansion)至少接近于(优选为等于)基板的热膨胀系数。此外,黏着剂会形成黏着层3,黏着层3可以是剥离层,其例如但不限于由聚酰亚胺(pi,polyimide)制成;其中,黏着层3可以在真空室中形成。

86.另外,图5为俯视图,显示几个切片单元2互相拼接并设置于工艺载板1的表面上,

图6a为如图5所示的切片单元2沿剖面线aa的剖面图,其中不同切片单元设置于单一个黏着层3上,图6b为如图5所示的切片单元2沿剖面线aa的剖面图,其中不同切片单元2分别设置于不同黏着层3上。

87.如图6a所示,当这些切片单元2通过黏着剂间接接合于工艺载板1时,黏着剂可以形成单一个黏着层3,其同时连接所有切片单元2,并将所有切片单元2间接接合至工艺载板1。另外,如图6b所示,当这些切片单元2通过黏着剂间接接合于工艺载板1时,黏着剂可以形成复数个黏着层3,其分别连接对应的这些切片单元2,例如以一对一的方式设置,以便分别将所有切片单元2间接接合至工艺载板1。上述黏着剂包括但不限于具有流动性的液体、具有黏滞性的流体、或具有弹性的弹性体。

88.在一些实施例中,各个切片单元2可以包括复数个预定的芯片单元21,并维持这些切片单元2的轮廓。如图2b、图3b及图4b所示,各切片单元2包括复数个预定的芯片单元21,且可维持切片单元2的轮廓,例如为四边形轮廓(如图2b)、五边形轮廓(如图3b)、或六边形轮廓(如图4b),但本发明不限于此。

89.在一些实施例中,基板的轮廓被定义为多边形轮廓,其中,多边形轮廓可以是四边形轮廓、五边形轮廓、六边形轮廓、或八边形轮廓,但本发明不限于此。

90.在一些实施例中,如图5及图6a或图6b所示,以两个相邻的切片单元2为例,其中一个切片单元2的一边与另一个切片单元2的相对边相邻设置。具体来说,各个切片单元2的尺寸由直径为6英寸、8英寸或12英寸、或以上的圆形切边所形成,亦即基板的多边形轮廓可以与晶圆共同定义轴心;当基板的多边形轮廓定义外接圆时,该外接圆可被定义在直径为6英寸、8英寸或12英寸(或其他尺寸)晶圆的边界内,而具有圆形轮廓的基板可以是6英寸、8英寸或12英寸(或其他尺寸)的晶圆本身。

91.在一些实施例中,在步骤s01之前或之中,还可以包括切割各个切片单元2、并将各切片单元2的轮廓从圆形轮廓变成多边形轮廓;另外,在将各个切片单元2切割成复数个芯片单元21之前,还可以在各个切片单元2的底面上贴上膜层。

92.在一些实施例中,每个芯片单元21的尺寸可以选择性地等于或不等于每个半导体芯片结构的尺寸,其依据设计的最大灵活性和晶圆(基板)的利用率而定。在本实施方式中,每个芯片单元21的尺寸等于每个半导体芯片结构的尺寸,但本发明不限于此。

93.在一些实施例中,各切片单元2的基板具有厚度,其大于0.4mil(10nm)且不大于100μm;具体来说,各切片单元2的基板的厚度的范围可以是40nm至60nm,举例而言,从soi(silicon on insulator)晶圆制造取得的基板,其厚度可以是40nm至60nm。在一些实施例中,切片单元2的尺寸可以是晶圆的原始尺寸,或是晶圆切割后的尺寸。若将切片单元2的平面尺寸修整到小于工艺载板1的平面尺寸但大于半导体芯片结构的平面尺寸,则可以加速半导体芯片结构的整个制造过程并增加有效工作区域的覆盖率。另外,如果将切片单元2的平面尺寸修整到与半导体芯片结构的平面尺寸相同,则在整个制造过程开始时便可以提供不同产品的最终尺寸。

94.在步骤s01之前,本实施例的半导体芯片结构制造方法还包含将各个切片单元2切割为复数个芯片单元21,并维持这些切片单元2的轮廓,其中各个芯片单元21的平面尺寸分别近似于(优选是等于)对应的半导体芯片结构的平面尺寸。换言之,各芯片单元21的平面尺寸实质上等于(例如略大于)对应的半导体芯片结构的平面尺寸。

95.在一些实施例中,每个芯片单元21的尺寸可以等于每个半导体芯片结构的尺寸,但本发明不限于此。在步骤s01之前或之中,工艺载板1的平面尺寸大于各个切片单元2的平面尺寸;进一步而言,工艺载板1的平面尺寸等于各个切片单元2的平面尺寸的倍数,或大于(略大于)各个切片单元2的平面尺寸的倍数,用以容纳这些切片单元2。

96.在一些实施例中,在步骤s01之前、之中或之后,本实施例的半导体芯片结构制造方法进一步包含研磨对应的切片单元2的基板。

97.在一些实施例中,这些切片单元2的基板的平面尺寸可以选择性地彼此相等或不相等。举例而言,这些切片单元2的基板的平面尺寸彼此相等,但本发明不限于此。

98.在步骤s02中,如图5、图6a及图6b所示,本实施例的半导体芯片结构制造方法进一步包含:填充密封材料在相邻的两个切片单元2之间的间隙g中。

99.在步骤s02中,密封材料例如但不限于钝化层4,如图5、图6a及图6b所示。

100.在步骤s02中,密封材料利用平坦化工艺形成于基板及间隙g,其中平坦化工艺例如但不限于旋涂玻璃(sog)工艺或旋涂掺杂(sod)工艺,而所形成的钝化层4可以例如但不限于包含氮氧化硅(sioxny)、氧化硅(siox)和/或氮化硅(sinx)。应注意,钝化层4的材料不限于上述材料,举例而言,钝化层4也可以例如但不限于包含al2o3、sio2、ta2o5或tio2,或上述材料的任意组合。

101.在步骤s02中,密封材料的热膨胀系数大致为相同或相近于切片单元2的基板的热膨胀系数。在一些实施例中,密封材料的热膨胀系数可以选择性配合玻璃或soi晶圆。举例而言,密封材料的热膨胀系数可以是例如但不限于不大于10ppm/k且不小于0.01ppm/k,优选地,密封材料的热膨胀系数的范围为2.5~6ppm/k。

102.在步骤s02中,本实施例的半导体芯片结构制造方法进一步包含:在填充密封材料在相邻的两个切片单元2之间的间隙g中的步骤之后,研磨这些切片单元2的顶部表面,使这些顶部的表面共同定义一个共平面。具体来说,各个切片单元2可以包括一个以上的顶部表面,而由所有切片单元2共同定义的共平面可以是由所有切片单元2的最高表面所共同定义的共平面。

103.承上所述,在本实施方式中,钝化层4可以形成于密封材料之上以便覆盖密封材料,而在研磨步骤中,在形成共平面时,钝化层4持续覆盖于密封材料上。

104.在步骤s03之前或之中,各个切片单元2的基板为不具有电路的裸基板、或具有部分电路的半成品基板。

105.在步骤s03中,在切片单元2上形成电路的工艺包含蒸镀或沉积(例如但不限于pecvd)、微影(或称黄光微影或uv微影,其至少包括光罩、曝光、蚀刻等步骤)、退火、平坦化(例如但不限于旋涂玻璃、旋涂掺杂)、或掺杂(例如但不限于扩散或离子植入)、或上述步骤的任意组合。其中,所形成的电路可以包含薄膜线路和/或薄膜晶体管,本发明不限于此。步骤s03完成后会获得电路切片单元。

106.在步骤s04之前或之中,本实施例的半导体芯片结构制造方法进一步包含:利用激光处理切割这些电路切片单元以形成边界凹口,由此定义半导体芯片结构的轮廓。在一些实施例中,对应于这些电路切片单元的这些半导体芯片结构互相连接成一体,然后被切割成个别的半导体芯片结构。在另一实施例中,对应于这些电路切片单元的这些半导体芯片结构直接被切割成个别的半导体芯片结构。

107.详细而言,半导体芯片结构的轮廓可以在步骤s01到步骤s04之中确定,甚至可以在步骤s01之前确定。无论何时或如何定义半导体芯片结构的轮廓,这些半导体芯片结构都会在步骤s04结束时完成将其分成个别单元。此外,由多个半导体芯片结构定义的切片单元的轮廓如同本发明实施例所述。

108.在步骤s04中,这些半导体芯片结构可以选择地具有相同的平面尺寸。在一些实施例中,这些半导体芯片结构具有相同的平面尺寸。当然,在其他实施例中,这些半导体芯片结构也可以具有不同的平面尺寸,或是部分相同部分不相同,本发明不限于此。

109.在步骤s04中,这些电路芯片单元的数量大于100个或大于1000个。

110.在步骤s04中,若在上述步骤s01至步骤s04之中同时切割工艺载板1,则各个半导体芯片结构也包含工艺载板1的对应部分。在另一实施例中,步骤s04进一步包含:在切割成个别的半导体芯片结构之前,从这些半导体芯片结构移除工艺载板1,其中,各个半导体芯片结构不包含工艺载板1的对应部分。

111.在步骤s04中,各个半导体芯片结构包含薄膜电路。

112.在步骤s04中,各该半导体芯片结构包含晶体管,其中,晶体管可以是薄膜晶体管(tft)和/或互补式金氧半(cmos)晶体管。

113.在步骤s04中,各个半导体芯片结构为电源管理集成电路(pmic)。在步骤s04中,各个半导体芯片结构为具有一组电路的芯片或具有集成电路系统的芯片。

114.综上所述,本发明的半导体芯片结构的制造方法先在工艺载板上设置多个切片单元,然后在切片单元上分别形成电路以形成电路切片单元,接着切割电路切片单元,以形成多个彼此独立的半导体芯片结构,其中切片单元的平面尺寸分别不小于所对应的半导体芯片结构的平面尺寸,或为其倍数。因此,本发明的半导体芯片结构制造方法能够以有功效且高效率的方式制造半导体芯片结构。本发明的优点在于产品的多样性、制造预算的可控性、满足不同应用的要求。

115.以上所述仅为举例性,而非为限制性。任何未脱离本发明的精神与范畴,而对其进行的等效修改或变更,均应包含于随附的权利要求范围中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1