电子装置的制作方法

电子装置

1.相关申请的交叉引用

2.本技术要求于2021年5月17日在韩国知识产权局提交的韩国专利申请no.10-2021-0063200的权益,该韩国专利申请的全部公开内容通过引用并入本文以用于所有目的。

技术领域

3.实施例涉及一种包括热界面材料层的电子装置和半导体封装件。

背景技术:

4.近年来,随着电子产品小型化和高性能化的趋势,电子产品在运行过程中产生的热量不断增加。因此,随着电子产品产生的热量逐渐增加,可能难以开发出高性能的电子产品。

技术实现要素:

5.根据示例实施例,一种电子装置,包括:基板,所述基板具有彼此相对的第一表面和第二表面;第一板,所述第一板具有面对所述基板的所述第一表面的第一内表面和与所述第一内表面相对的第一外表面,所述第一板包括至少一个第一通孔和至少一个第二通孔;第一半导体封装件和第二半导体封装件,所述第一半导体封装件和所述第二半导体封装件均安装在所述基板的所述第一表面上,设置在所述基板的所述第一表面与所述第一板的所述第一内表面之间,并且彼此间隔开;第一热界面材料层,所述第一热界面材料层设置在所述第一半导体封装件与所述第一板之间,接触所述第一半导体封装件的上表面和所述第一板的所述第一内表面,并且填充所述至少一个第一通孔的至少一部分;以及第二热界面材料层,所述第二热界面材料层设置在所述第二半导体封装件与所述第一板之间,接触所述第二半导体封装件的上表面和所述第一板的所述第一内表面,并且填充所述至少一个第二通孔的至少一部分。所述第一热界面材料层的侧表面和所述第二热界面材料层的侧表面中的至少一者暴露于所述第一板的所述第一内表面与所述基板的所述第一表面之间的空白空间。

6.根据示例实施例,一种电子装置,包括:基板,所述基板具有彼此相对的第一表面和第二表面;第一板,所述第一板具有面对所述基板的所述第一表面的第一内表面和与所述第一内表面相对的第一外表面,所述第一板包括多个前通孔;多个前半导体封装件,所述多个前半导体封装件分别安装在所述基板的所述第一表面上,彼此间隔开,并且位于所述基板的所述第一表面与所述第一板的所述第一内表面之间;以及多个前热界面材料层,所述多个前热界面材料层与所述第一板的所述第一内表面以及所述多个前半导体封装件中的每一者接触,并且位于所述多个前半导体封装件与所述第一板的所述第一内表面之间。所述多个前通孔与所述多个前半导体封装件交叠,所述多个前半导体封装件包括具有不同厚度的第一前半导体封装件和第二前半导体封装件,所述多个前通孔包括与所述第一前半

导体封装件交叠的至少一个第一前通孔和与所述第二前半导体封装件交叠的至少一个第二前通孔,所述多个前热界面材料层包括:与所述第一板和所述第一前半导体封装件接触的第一前热界面材料层,以及与所述第一板和所述第二前半导体封装件接触的第二前热界面材料层,所述第一板包括:具有位于距所述基板的所述第一表面第一高度水平处的基底表面的基底区域,以及具有位于距所述基板的所述第一表面低于所述第一高度水平的第二高度水平处的第一突出表面并且与所述第一前半导体封装件交叠的第一突出区域,所述第一内表面包括所述基底表面和所述第一突出表面,并且所述第一前热界面材料层与所述第一突出区域的所述第一突出表面接触。

7.根据示例实施例,一种电子装置,包括:基板,所述基板具有彼此相对的第一表面和第二表面;板,所述板具有面对所述基板的所述第一表面的内表面和与所述内表面相对的外表面,所述板包括至少一个通孔;半导体封装件,所述半导体封装件与所述至少一个通孔交叠,安装在所述基板的所述第一表面上,并且位于所述基板的所述第一表面与所述板的所述内表面之间;以及热界面材料层,所述热界面材料层填充所述至少一个通孔的至少一部分并且与所述半导体封装件和所述板接触。所述板包括与所述半导体封装件交叠的封装件交叠区域,所述板的所述内表面包括在所述封装件交叠区域中位于不同高度水平处的第一区域和第二区域,所述第一区域和所述第二区域与所述热界面材料层接触,并且所述热界面材料层的侧表面暴露于所述板的所述内表面与所述基板的所述第一表面之间的空白空间。

附图说明

8.通过参考附图详细描述示例性实施例,对于本领域技术人员而言特征将变得显而易见,在附图中:

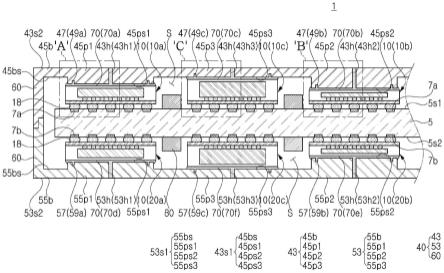

9.图1、图2a、图2b和图2c是根据示例实施例的电子装置的图;

10.图3a和图3b是根据示例实施例的电子装置的一些组件的图;

11.图4是根据示例实施例的电子装置的一些组件的另一示例的图;

12.图5a是根据示例实施例的电子装置的一些组件的另一示例的图;

13.图5b是根据示例实施例的电子装置的一些组件的另一示例的图;

14.图6是根据示例实施例的电子装置的一些组件的另一示例的图;

15.图7a是根据示例实施例的电子装置的一些组件的另一示例的图;

16.图7b是根据示例实施例的电子装置的一些组件的另一示例的图;

17.图8是根据示例实施例的电子装置的一些组件的另一示例的图;

18.图9、图10a、图10b是根据修改示例的电子装置的示意图;

19.图11a是根据修改示例的电子装置的一些组件的示例的图;

20.图11b是根据修改示例的电子装置的一些组件的另一示例的图;

21.图11c是根据修改示例的电子装置的一些组件的另一示例的图;

22.图12是根据示例实施例的电子装置的一些组件的另一示例的图;

23.图13a和图13b是根据示例实施例的存储设备的示例的示意性透视图;

24.图14a和图14b是根据示例实施例的存储设备的另一示例的示意性透视图;

25.图15是应用了根据示例实施例的电子装置的系统的示意图;以及

26.图16是应用了根据示例实施例的存储设备的数据中心的图。

具体实施方式

27.下文将参考图1、图2a、图2b和图2c描述示例实施例。图1是根据示例实施例的电子装置的截面图,图2a是图1中由“a”指示的区域的局部放大图,图2b是图1中由“b”指示的区域的局部放大图,并且图2c是图1中由“c”指示的区域的局部放大图。

28.参考图1和图2a至图2c,根据示例实施例的电子装置1可以包括具有彼此相对的第一表面5s1和第二表面5s2的基板5、壳体40、多个半导体封装件10和多个热界面材料层70。电子装置1还可以包括安装在基板5上的无源元件80,例如,电容器。

29.基板5可以是印刷电路板(pcb)或模块基板。多个半导体封装件10和多个热界面材料层70可以安装在基板5的第一表面5s1和第二表面5s2上。

30.壳体40可以包括第一板43。第一板43可以具有面对基板5的第一表面5s1的第一内表面43s1和与第一内表面43s1相对的第一外表面43s2。第一板43可以包括多个前通孔43h。在第一板43中,多个前通孔43h可以从第一内表面43s1贯穿到第一外表面43s2。多个前通孔43h可以包括至少一个第一通孔43h1、至少一个第二通孔43h2和至少一个第三通孔43h3。

31.壳体40还可以包括第二板53。第一板43和第二板53可以由能够散热的材料形成,例如金属材料或石墨材料。在一些实施例中,第一板43和第二板53可以分别被称为第一散热板和第二散热板。

32.第二板53可以具有面对基板5的第二表面5s2的第二内表面53s1和与第二板53的第二内表面53s1相对的第二外表面53s2。第二板53可以包括多个后通孔53h。注意,在整个说明书中,“前”和“后”用于区分组件之间的相对位置,并且它们可以是可互换的,例如,或被替换为“第一”和“第二”。

33.在第二板53中,多个后通孔53h可以从第二内表面53s1贯穿到第二外表面53s2。在第二板53中,多个后通孔53h可以包括至少一个第四通孔53h1、至少一个第五通孔53h2和至少一个第六通孔53h3。壳体40还可以包括连接第一板43和第二板53的连接部分60。

34.第一板43可以包括基底区域(base region)45b、与第一半导体封装件10a交叠的第一封装件交叠区域(图3a中的10e)、与第二半导体封装件10b交叠的第二封装件交叠区域(图4中的图10e')、和与第三半导体封装件10c交叠的第三封装件交叠区域45p3。

35.第一板43可以包括至少一个具有突出表面45ps的突出区域45p。例如,在第一板43中,第一封装件交叠区域可以包括具有第一突出表面45ps1的第一突出区域45p1,并且第二封装件交叠区域可以包括具有第二突出表面45ps2的第二突出区域45p2。

36.基底区域45b可以具有设置在距基板5的第一表面5s1第一高度水平h1处的基底表面45bs。在第一突出区域45pl中,第一突出表面45ps1可以设置在距基板5的第一表面5s1第二高度水平h2处,第二高度水平h2低于第一高度水平h1,例如,第二高度水平h2可以小于第一高度水平h1。在第二突出区域45p2中,第二突出表面45ps2可以位于距基板5的第一表面5s1第三高度水平h3处,第三高度水平h3低于第二高度水平h2,例如,第三高度水平h3可以小于第二高度水平h2。第三封装件交叠区域45p3可以具有设置在与基底表面45bs基本相同的第一高度水平h1处的封装件交叠表面45ps3。

37.在第一板43中,第一内表面43s1可以包括基底表面45bs、第一突出表面45ps1和第

二突出表面45ps2以及封装件交叠表面45ps3。

38.第二板53可以包括具有基底表面55bs的基底区域55b、与第四半导体封装件20a交叠的第四封装件交叠区域、与第五半导体封装件20b交叠的第五封装件交叠区域、以及与第六半导体封装件20c交叠并且具有封装件交叠表面55ps3的第六封装件交叠区域55p3。在第二板53中,第四封装件交叠区域可以包括具有第一突出表面55ps1的第一突出区域55p1,并且第五封装件交叠区域可以包括具有第二突出表面55ps2的第二突出区域55p2。在第二板53中,第二内表面53s1可以包括基底表面55bs、第一突出表面55ps1和第二突出表面55ps2以及封装件交叠表面55ps3。由于根据第一板43的第一内表面43s1可以容易地理解第二板53的第二内表面53s1,因此将省略对第二板53的第二内表面53s1的详细描述。

39.第一板43还可以包括前雕刻(engraved)图案47。第二板53还可以包括后雕刻图案57。例如,第一板43的前雕刻图案47可以包括第一雕刻图案49a、第二雕刻图案49b和第三雕刻图案49c,并且第二板53的后雕刻图案57可以包括第四雕刻图案59a、第五雕刻图案59b和第六雕刻图案59c。在示例实施例中,在平面图中,雕刻图案47和57均可以具有闭合环,例如环形,例如,雕刻图案47和57均可以具有四边形(quadrangular)形状(图3a和图4)。

40.在第一板43中,第一雕刻图案49a、第二雕刻图案49b和第三雕刻图案49c可以是形成在第一板43的第一内表面43sl中的雕刻图案。例如,在第一板43中,可以通过使第一板43的第一内表面43s1的一部分沿垂直方向远离基板5的第一表面5s1凹陷,来形成第一雕刻图案49a、第二雕刻图案49b和第三雕刻图案49c。在这种情况下,垂直方向可以是垂直于基板5的第一表面5s1的方向。

41.在第一板43中,第一雕刻图案49a可以设置在第一内表面43s的第一突出表面45psl上,例如,第一雕刻图案49a可以沿着第一突出表面45psl的外缘延伸;第二雕刻图案49b可以设置在第一内表面43s的第二突出表面45ps2上,例如,第二雕刻图案49b可以沿着第二突出表面45ps2的外缘延伸;并且第三雕刻图案49c可以设置在第一内表面43s的封装件交叠表面45ps3上。第一突出区域45p1的边缘与第一雕刻图案49a之间的距离可以小于第一突出区域45p1的中心与第一雕刻图案49a之间的距离。第二突出区域45p2的边缘与第二雕刻图案49b之间的距离可以小于第二突出区域45p2的中心与第二雕刻图案49b之间的距离。

42.在第二板53中,第四雕刻图案59a、第五雕刻图案59b和第六雕刻图案59c可以是形成在第二板53的第二内表面53s1中的雕刻图案。例如,在第二板53中,可以通过使第二板53的第二内表面53s1的一部分沿垂直方向远离基板5的第二表面5s2凹陷,来形成第四雕刻图案59a、第五雕刻图案59b和第六雕刻图案59c。

43.在第二板53中,第四雕刻图案59a可以设置在第二内表面53s的第一突出表面55ps1上,并且第五雕刻图案59b可以设置在第二内表面53s的第二突出表面55ps2上,并且第六雕刻图案59c可以设置在第二内表面53s的封装件交叠表面55ps3上。

44.多个半导体封装件10可以通过连接图案18电连接到基板5的焊盘7a和7b。多个半导体封装件10可以包括安装在基板5的第一表面5s1上的前半导体封装件10a、10b和10c。多个半导体封装件10还可以包括安装在基板5的第二表面5s2下方的后半导体封装件20a、20b和20c。

45.前半导体封装件10a、10b和10c可以分别安装在基板5的第一表面5s1上,并且可以

设置在基板5的第一表面5s1和第一板43的第一内表面43s1之间。后半导体封装件20a、20b和20c可以分别安装在基板5的第二表面5s2上,并且可以设置在基板5的第二表面5s2和第二板53的第二内表面53s1之间。

46.前半导体封装件10a、10b和10c可以包括第一半导体封装件10a、第二半导体封装件10b和第三半导体封装件10c。后半导体封装件20a、20b和20c可以包括第四半导体封装件40a、第五半导体封装件50b和第六半导体封装件20c。

47.在示例实施例中,多个半导体封装件10当中的至少两个半导体封装件可以是不同类型的半导体封装件。例如,多个半导体封装件10中的一个半导体封装件可以是控制器半导体封装件,而另一个半导体封装件可以是存储器半导体封装件。

48.在示例实施例中,多个半导体封装件10当中的至少三个半导体封装件可以包括不同类型的半导体芯片。例如,多个半导体封装件10中的一个半导体封装件可以是控制器半导体封装件,另一个半导体封装件可以是第一存储器半导体封装件,而又一个半导体封装件可以是第二存储器半导体封装件。例如,第一半导体封装件10a、第二半导体封装件10b和第三半导体封装件10c中的一个半导体封装件可以是控制器半导体封装件,另一个半导体封装件可以是第一存储器半导体封装件,而又一个半导体封装件可以是第二存储器半导体封装件。第一存储器半导体封装件可以是非易失性存储器,例如,nand闪存;并且第二存储器半导体封装件可以是易失性存储器,例如,动态随机存取存储器(dram)。多个半导体封装件10中的任何一个半导体封装件可以是功率半导体,例如,功率管理集成电路(pmic)。

49.多个半导体封装件10均可以包括封装基板、安装在封装基板上的一个或多个半导体芯片、以及在封装基板上密封一个或多个半导体芯片的密封剂。密封剂可以包括绝缘材料,例如,诸如环氧树脂模塑料(emc)的树脂。例如,第一半导体封装件10a可以包括封装基板12a、安装在封装基板12a上的一个或多个半导体芯片14a、以及在封装基板12a上密封一个或多个半导体芯片14a的密封剂16a。第二半导体封装件10b可以包括封装基板12b、安装在封装基板12b上的一个或多个半导体芯片14b、以及在封装基板12b上密封一个或多个半导体芯片14b的密封剂16b。第三半导体封装件10c可以包括封装基板12c、安装在封装基板12c上的一个或多个半导体芯片14c、以及在封装基板12c上密封一个或多个半导体芯片14c的密封剂16c。例如,半导体芯片14a至14c中的每一者的宽度可以小于对应的雕刻图案47的闭合环的直径。

50.在第一板43中,包括具有第一突出表面45ps1的第一突出区域45p1的第一封装件交叠区域可以与第一半导体封装件10a交叠,包括具有第二突出表面45ps2的第二突出区域45p2的第二封装件交叠区域可以与第二半导体封装件10b交叠,并且具有封装件交叠表面45ps3的第三封装件交叠区域45p3可以与第三半导体封装件10c交叠。

51.在第二板53中,包括具有第一突出表面55ps1的第一突出区域55p1的第四封装件交叠区域可以与第四半导体封装件20a交叠,包括具有第二突出表面55ps2的第二突出区域55p2的第五封装件交叠区域可以与第五半导体封装件20b交叠,并且具有封装件交叠表面55ps3的第六封装件交叠区域55p3可以与第六半导体封装件20c交叠。

52.第一半导体封装件10a可以与第一雕刻图案49a和至少一个第一通孔43hl交叠,例如,第一半导体封装件10a的宽度可以大于第一雕刻图案49a的闭合环的直径。第二半导体封装件10b可以与第二雕刻图案49b和至少一个第二通孔43h2交叠,例如,第二半导体封装

件10b的宽度可以大于第二雕刻图案49b的闭合环的直径。第三半导体封装件10c可以与第三雕刻图案49c和至少一个第三通孔43h3交叠,例如,第三半导体封装件10c的宽度可以大于第三雕刻图案49c的闭合环的直径。第四半导体封装件20a可以与第四雕刻图案59a和至少一个第四通孔53h1交叠,例如,第四半导体封装件20a的宽度可以大于第四雕刻图案59a的闭合环的直径。第五半导体封装件20b可以与第五雕刻图案59b和至少一个第五通孔53h2交叠,例如,第五半导体封装件20b的宽度可以大于第五雕刻图案59b的闭合环的直径。第六半导体封装件20c可以与第六雕刻图案59c和至少一个第六通孔53h3交叠,例如,第六半导体封装件20c的宽度可以大于第六雕刻图案59c的闭合环的直径。

53.多个热界面材料层70可以彼此间隔开。多个热界面材料层70可以包括设置在前半导体封装件10a、10b和10c与第一板43之间的前热界面材料层70a、70b和70c。多个热界面材料层70可以包括设置在后半导体封装件20a、20b和20c与第二板53之间的后热界面材料层70d、70e和70f。

54.前热界面材料层70a、70b和70c中的至少一者的侧表面可以被基板5的第一表面5s1与第一板43之间的空白空间s暴露。例如,前热界面材料层70a、70b和70c的侧表面可以被空白空间s暴露。后热界面材料层70d、70e和70f中的至少一者的侧表面可以暴露于基板5的第二表面5s2和第二板53之间的空白空间s。例如,后热界面材料层70d、70e和70f的侧表面可以暴露于空白空间s。空白空间s可以是充满空气的空间。因此,热界面材料层70的侧表面可以暴露于空气。

55.前热界面材料层70a、70b和70c可以包括第一热界面材料层70a、第二热界面材料层70b和第三热界面材料层70c。

56.第一热界面材料层70a可以设置在第一半导体封装件10a与第一板43之间,并且可以与第一半导体封装件10a的上表面和第一板43的第一内表面43s1接触。第一热界面材料层70a的至少一部分可以接触第一突出表面45ps1和第一半导体封装件10a的上表面。第一热界面材料层70a还可以包括:例如完全填充至少一个第一通孔43h1的至少一部分的第一部分70p1,以及例如完全填充第一雕刻图案49a的至少一部分的第二部分70p2。第一热界面材料层70a可以覆盖第一突出区域45p1的侧表面的至少一部分。第一热界面材料层70a的侧表面70s1的至少一部分可以具有弯曲形状。第一热界面材料层70a的至少一部分可以接触第一半导体封装件10a的上表面的边缘的至少一部分。第一半导体封装件10a的侧表面10ae可以被基板5的第一表面5s1与第一板43之间的空白空间s暴露。

57.第二热界面材料层70b可以设置在第二半导体封装件10b与第一板43之间,并且可以与第二半导体封装件10b的上表面和第一板43的第一内表面43s1接触。第二热界面材料层70b的至少一部分可以接触第二突出表面45ps2和第二半导体封装件10b的上表面。第二热界面材料层70b还可以包括:填充至少一个第二通孔43h2的至少一部分的第一部分70p1,以及填充第二雕刻图案49b的至少一部分的第二部分70p2。当相对于基板5的第一表面5s1观察时,第二热界面材料层70b的下表面可以设置在与第一热界面材料层70a的下表面不同的高度水平处。例如,第二热界面材料层70b的下表面可以设置在例如相对于基板5的第一表面5s1而言比第一热界面材料层70a的下表面低的高度水平处。第二热界面材料层70b可以覆盖第二突出区域45p2的侧表面的至少一部分。第二热界面材料层70b的侧表面70s2的至少一部分可以具有弯曲形状。第二热界面材料层70b的至少一部分可以接触第二半导体

封装件10b的上表面的边缘的至少一部分。第二半导体封装件10b的侧表面10be可以被基板5的第一表面5s1与第一板43之间的空白空间s暴露。

58.第三热界面材料层70c可以设置在第三半导体封装件10c与第一板43之间,并且可以与第三半导体封装件10c的上表面和第一板43的第一内表面43s1接触。第三热界面材料层70c还可以包括填充至少一个第三通孔43h3的至少一部分的第一部分70p1和填充第三雕刻图案49c的至少一部分的第二部分70p2。当相对于基板5的第一表面5s1观察时,第三热界面材料层70c的下表面可以设置在与第一热界面材料层70a的下表面和第二热界面材料层70b的下表面不同的高度水平处。例如,第三热界面材料层70c的下表面可以设置在例如相对于基板5的第一表面5s1而言比第一热界面材料层70a的下表面和第二热界面材料层70b的下表面高的水平处。

59.后热界面材料层70d、70e和70f可以包括第四热界面材料层70d、第五热界面材料层70e和第六热界面材料层70f。第四热界面材料层70d可以设置在第四半导体封装件20a与第二板53之间,并且可以与第四半导体封装件20a的上表面和第二板53的第二内表面53s1接触。第四热界面材料层70d还可以包括:填充至少一个第四通孔53h1的至少一部分的部分,以及填充第四雕刻图案59a的至少一部分的部分。第四热界面材料层70d可以具有与第一热界面材料层70a镜像对称的结构。

60.第五热界面材料层70e可以设置在第五半导体封装件20b与第二板53之间,并且可以与第五半导体封装件20b的上表面和第二板53的第二内表面53s1接触。第五热界面材料层70e还可以包括:填充至少一个第五通孔53h2的至少一部分的部分,以及填充第五雕刻图案59b的至少一部分的部分。第五热界面材料层70e可以具有与第二热界面材料层70b镜像对称的结构。

61.第六热界面材料层70f设置在第六半导体封装件20c与第二板53之间,并且可以与第六半导体封装件20c的上表面和第二板53的第二内表面53s1接触。第六热界面材料层70f还可以包括:填充至少一个第六通孔53h3的至少一部分的部分,以及填充第六雕刻图案59c的至少一部分的部分。第六热界面材料层70f可以具有与第三热界面材料层70c镜像对称的结构。

62.在上述实施例中,半导体封装件10当中的具有不同类型的半导体封装件可以具有不同的形状和/或不同的尺寸。例如,当从上方观察时,半导体封装件10可以分为:具有正方形形状或接近正方形的形状的半导体封装件,以及具有长方形(rectangle)形状或接近长方形的形状的半导体封装件。在半导体封装件10当中,一个或多个半导体封装件可以具有正方形形状或接近正方形的形状,并且一个或多个半导体封装件可以具有长方形形状或接近长方形的形状。例如,第一半导体封装件10a可以具有正方形形状或接近正方形的形状,而第二半导体封装件10b可以具有长方形形状或接近长方形的形状。

63.根据示例实施例,热界面材料层70的形成可以包括:用壳体40覆盖其上安装有半导体封装件10的基板5,然后将液体热界面材料(tim)注入第一板43的前通孔43h中,并固化注入的液体热界面材料(tim),将液体热界面材料(tim)注入第二板53的后通孔53h中,并固化注入的液体热界面材料(tim)。

64.第一板43的雕刻图案47和第二板53的雕刻图案57可以防止注入的液体热界面材料tim流到半导体封装件10的侧表面。因此,可以稳定地形成热界面材料层70且没有缺陷。

此外,由于第一板43的雕刻图案47和第二板53的雕刻图案57,半导体封装件10的上表面与热界面材料层70之间的接触面积可以增加。因此,可以改善电子装置1的散热特性。

65.在下文中,将参考图3a和图3b描述第一板43的面对第一半导体封装件10a的第一封装件交叠区域10e的说明性示例,并且将参考图4描述第一板43的面对第二半导体封装件10b的第二封装件交叠区域10e'的说明性示例。图3a是第一板43的第一封装件交叠区域10e的俯视图,并且图3b是示出从下方观察的第一板43的第一封装件交叠区域10e的示意性透视图。

66.参考图3a、图3b和图4,在第一板43中,第一封装件交叠区域10e和第二封装件交叠区域10e'可以被具有基底表面45bs的基底区域45b围绕。具有第一突出表面45ps1的第一突出区域45p1和具有第一突出表面(图2b中的45ps2)的第二突出区域45p2可以具有从基底区域45b突出的形状。

67.第一雕刻图案49a和第二雕刻图案49b均可以具有四边形的环形。例如,在平面图中,第一通孔43h1可以例如完全被第一雕刻图案49a围绕。例如,在平面图中,第二通孔43h2可以例如完全被第二雕刻图案49b围绕。

68.第一雕刻图案49a与第一突出区域45pl的边缘之间的距离可以小于第一雕刻图案49a与第一突出区域45pl的中心之间的距离。第二雕刻图案49b与第二突出区域45p2的边缘之间的距离可以小于第二雕刻图案49b与第二突出区域45p2的中心之间的距离。

69.当从上方观察时,第一突出区域45p1的边缘可以被第一半导体封装件10a的边缘围绕(参见图1)。第一半导体封装件(图1的10a)的边缘可以与图3a中由附图标记10e指示的第一封装件交叠区域10e的边缘相同。第二突出区域45p2的边缘可以被第二半导体封装件(图1的10b)的边缘围绕。第二半导体封装件(图1的10b)的边缘可以与图4中由附图标记10e'指示的第二封装件交叠区域10e'的边缘相同。

70.如图1至图2c所示,在示例中,在每个热界面材料层70中,第一部分70p1可以分别填充通孔43h和53h,并且可以具有平坦的上表面70u。然而,实施例不限于此。在下文中,将参考图5a和图5b描述每个热界面材料层70中的第一部分70p1的修改示例。图5a和图5b均是示意性地示出图2a的第一热界面材料层70a的修改示例的图。

71.在修改示例中,参考图5a,第一热界面材料层70a的第一部分70p1可以被修改为具有从第一外表面43s2延伸且具有凹形的上表面70ua。第一热界面材料层70a的上表面70ua可以具有凹的弯曲形状。

72.在修改示例中,参考图5b,第一热界面材料层70a的第一部分70p1可以被修改为具有设置在低于第一外表面43s2的水平高度且为凹形的上表面70ub。第一热界面材料层70a的上表面70ub可以具有凹的弯曲形状。第一热界面材料层70a的第一部分70p1可以部分地填充第一通孔43h1。

73.接下来,将分别参考图6、图7a和图7b描述通孔43h的各种修改示例。图6、图7a和图7b是示出根据示例实施例的电子装置中的通孔43h的修改示例的俯视图。

74.例如,与图1至图5b示出单个通孔43h与一个半导体封装件交叠相比,在修改示例中,参考图6,可以有多个通孔43h'与一个半导体封装件交叠。例如,如图6所示,被具有单环形状的雕刻图案47围绕的通孔43h'可以为多个。例如,图4中的第二通孔43h2可以被替换为多个第二通孔43h2'。因此,图1中描绘的第一通孔43h1的数目可以为单个或多个,第二通孔

43h2的数目可以为单个或多个,第三通孔43h3的数目可以为单个或多个,第四通孔53h1的数目可以为单个或多个,第五通孔53h2的数目可以为单个或多个,并且第六通孔53h3的数目可以为单个或多个。

75.例如,与图3a至图4示出一个环形雕刻图案47具有均匀厚度相比,在修改示例中,参考图7a,一个环形雕刻图案47a可以包括具有第一宽度的第一部分47_1a和具有小于第一宽度的第二宽度的第二部分47_2a。当从上方观察时,如图7a所示,雕刻图案47a可以具有彼此相对的第一侧47s1和第二侧47s2以及彼此相对的第三侧47s3和第四侧47s4。第一侧47s1和第二侧47s2中的每一侧可以比第三侧47s3和第四侧47s4中的每一侧大,例如,在纵向上更长。在雕刻图案47a中,例如在与纵向正交的方向上具有相对大的宽度的第一部分47_1a可以设置在第一侧47s1和第二侧47s2中的每一侧的中央部分。

76.在修改示例中,参考图7b,当从上方观察时,参考图7a描述的具有第一宽度的第一部分47_1a可以被修改为使得具有第一宽度的部分47_1b和具有第二宽度的部分47_2b被重复布置。因此,在任一雕刻图案47b中,图7a中描绘的第一侧47s1和第二侧47s2的各自的中间部分可以被替换为重复布置且具有不同宽度的部分47_1b和47_2b。

77.接下来,将参考图8描述通孔43h的另一修改示例。图8是沿着图4的线i-i'截取的第一板43的截面图,以描述根据示例实施例的电子装置中的通孔43h的另一修改示例。

78.在修改示例中,参考图8,上述每个雕刻图案(图1的47)可以具有凹陷到均匀深度的形状。然而,实施例不限于此。例如,上述图1中的雕刻图案47中的至少一者可以包括凹陷到不同深度的区域。例如,如图8所示,任一雕刻图案47c可以包括:从第一板43的突出表面45ps凹陷到第一深度的第一区域47_1c,以及凹陷到比第一深度浅的第二深度的第二区域47_2c。

79.接下来,将参考图9、图10a和图10b描述根据修改实施例的电子装置。图9是示意性地示出根据修改示例的电子装置的截面图,图10a是图9中由“a1”指示的区域的局部放大图,并且图10b是图9中由“a2”指示的区域的局部放大图。

80.参考图9、图10a和图10b,上述第一板43和第二板53还可以包括浮雕(embossed)图案50。例如,第一板43可以包括:设置在上述与第一半导体封装件10a交叠的第一封装件交叠区域(图3a中的10e)的第一突出表面45ps1下方的第一浮雕图案50a,设置在与第二半导体封装件10b交叠的第二封装件交叠区域(图4中的10e')的第二突出表面45ps2下方的第二浮雕图案50b,以及设置在与第三半导体封装件10c交叠的第三封装件交叠区域45p3的封装件交叠表面45ps3下方的第三浮雕图案50c。第二板53可以包括:设置在与第四半导体封装件20a交叠的第四封装件交叠区域的第一突出表面55ps1上的第四浮雕图案50d、设置在与第五半导体封装件20b交叠的第五封装件交叠区域的第二突出表面55ps2上的第五浮雕图案50e,以及设置在与第六半导体封装件20c交叠的第六封装件交叠区域55p3的封装件交叠表面55ps3上的第六浮雕图案50f。

81.在示例中,第一板43可以一体地形成。例如,第一浮雕图案50a可以具有从第一突出表面45ps1连续延伸而没有边界面的形状。

82.在另一示例中,浮雕图案50可以以附接形式形成。例如,第一浮雕图案50a可以附接到第一突出表面45ps1以形成与第一突出表面45ps1的界面。浮雕图案50可以包括金属材料或石墨材料。

83.每个浮雕图案50可以包括被一个环形雕刻图案47围绕的第一浮雕部分51和围绕一个雕刻图案47的第二浮雕部分52中的至少一者。第二浮雕部分52可以具有环形并且可以围绕雕刻图案47。例如,第一浮雕图案50a可以包括被第一雕刻图案49a围绕的第一浮雕部分51和围绕第一雕刻图案49a的第二浮雕部分52。

84.在一些实施例中,第一板43和第二板53可以包括雕刻图案47和57以及浮雕图案50中的至少一者。例如,可以省略雕刻图案47,并且第一板43和第二板53可以包括浮雕图案50。

85.在一些实施例中,在将液体热界面材料(tim)注入到第一板43和第二板53的通孔43h和53h中并固化注入的液体热界面材料(tim)期间,雕刻图案47和57以及浮雕图案50中的至少一者可以防止注入的液体热界面材料(tim)流到半导体封装件10的侧表面,因此,可以稳定且没有缺陷地形成热界面材料层70。

86.图11a、图11b和图11c是用于描述参考图9、图10a和图10b描绘的任一浮雕图案50的各种示例的俯视图。图11a、图11b和图11c是向图4的俯视图添加了一个浮雕图案的俯视图,并且下面将省略图4中描绘的内容,并且将主要参考任一浮雕图案50进行描述。

87.在示例中,参考图11a,任一浮雕图案50可以包括被环形雕刻图案47围绕的第一浮雕部分51a和围绕一个雕刻图案47的第二浮雕部分52。通孔43h可以穿过第一浮雕部分51a。浮雕图案50可以与雕刻图案47间隔开。

88.第一浮雕部分51a可以具有条形。例如,当封装件交叠区域10e'具有矩形(rectangular)形状时,第一浮雕部分51a可以具有在封装件交叠区域10e'的纵向或伸长方向上延伸的条形形状或矩形形状。

89.在另一示例中,参考图11b,任一浮雕图案50可以包括被环形雕刻图案47围绕的第一浮雕部分51b以及围绕一个雕刻图案47的第二浮雕部分52。第一浮雕部分51b可以包括:四边形形状的第一部分51b_1,以及从四边形形状的第一部分51b_1的拐角朝向四边形的环形的雕刻图案47的拐角延伸的第二部分51b_2。

90.在另一示例中,参考图11c,任一浮雕图案50可以包括被环形雕刻图案47围绕的第一浮雕部分51c和围绕该一个雕刻图案47的第二浮雕部分52。第二浮雕部分52可以与雕刻图案47间隔开,并且第一浮雕部分51c可以连接到雕刻图案47。例如,第一浮雕部分51c可以包括与雕刻图案47间隔开的第一部分51c_1,以及从第一部分51c_1延伸、具有大于第一部分51c_1的宽度的宽度并且连接到雕刻图案47的第二部分51b_2。

91.接下来,参考图12,将描述可以替代图1的任何一个半导体封装件10或者可以被包括在半导体封装件10中的半导体封装件110。图12是示意性地示出根据示例实施例的电子装置的一些组件的另一示例的图。

92.参考图12,可以提供可以替代图1的任何一个半导体封装件10或者可以被包括在半导体封装件10中的第七半导体封装件110。参考图1描述的第一至第六半导体封装件10a、10b、10c、20a、20b和20c可以具有平坦上表面。在示例中,第七半导体封装件110可以替代具有平坦上表面的第一至第六半导体封装件10a、10b、10c、20a、20b和20c中的任何一者。

93.第七半导体封装件110可以包括封装基板112、安装在封装基板上的一个或多个半导体芯片114、在封装基板112上密封一个或多个半导体芯片114的密封剂116以及在封装基板112上覆盖密封剂116的散热结构118。散热结构118可以由金属材料或石墨材料形成。在

示例中,第七半导体封装件110的上表面可以包括中央部分、低于中央部分的边缘部分以及中心部分与边缘部分之间的倾斜部分。

94.第一板43可以包括与第七半导体封装件110交叠并且包括中央部分145p1和围绕中央部分145p1的边缘部分145p2的突出区域145p1。第一板43的突出区域145p1可以包括中央部分145p1的第一突出表面145ps1、边缘部分145p2的第二突出表面145ps2、以及第一突出表面145ps1与第二突出表面145ps2之间的倾斜表面145ps3。第一突出表面145ps1、第二突出表面145ps2和倾斜表面145ps3可以构成上述第一板43的第一内表面(图1中的43s1)。

95.第一板43还可以包括形成在第二突出表面145p2上的第七雕刻图案149a。第一板43还可以包括穿过突出区域145p1的中央部分145p1的第七通孔143h。

96.多个热界面材料层70可以包括位于第一板43与第七半导体封装件110之间的第七热界面材料层170a。第七热界面材料层170a可以包括:覆盖第七半导体封装件110的上表面的中间部分的第一部分170a1,覆盖第七半导体封装件110的上表面的倾斜部分的第二部分170a2,以及覆盖第七半导体封装件110的上表面的边缘部分的第三部分170a3。

97.第七热界面材料层170a还可以包括填充第七通孔143h的至少一部分的第一部分170p1和填充第七雕刻图案149a的至少一部分的第二部分170p2。

98.上述电子装置1可以包括存储设备。将描述电子装置1的存储设备的示例性示例。图13a和图13b是示出根据示例实施例的电子装置的示例的示意性透视图。

99.参考图13a和图13b,电子装置301可以是存储设备,例如,固态硬盘设备。电子装置301可以包括具有彼此相对的第一表面305s1和第二表面305s2的基板305、多个封装件308和壳体340。

100.壳体340可以类似于参考图1描述的壳体40。例如,壳体340可以包括第一板343、第二板353以及连接第一板343和第二板353的连接部分360。第一板343和第二板353可以由能够散热的材料(例如,金属材料或石墨材料)形成。

101.第一板343可以具有面对基板305的第一表面305s1的第一内表面和与第一内表面相对的第一外表面。第一板343可以包括多个通孔343h。在第一板343中,多个通孔343h可以从第一内表面贯穿到第一外表面。多个通孔343h可以包括第一通孔343h1、第二通孔343h2、第三通孔343h3和第四通孔343h4。

102.第二板353可以具有面对基板305的第二表面305s2的第二内表面353s1和与第二内表面353s1相对的第二外表面。第二板353可以包括多个通孔353h。在第二板353中,多个通孔353h可以从第二内表面353s1贯穿到第二外表面。在第二板353中,多个通孔353h可以包括第五通孔353h1、第六通孔353h2和第七通孔353h3。

103.第一板343和第二板353可以包括可以分别对应于上述突出区域45p和雕刻图案47的突出区域455p和雕刻图案457。

104.多个封装件308均可以包括安装在基板305上的半导体封装件310以及位于半导体封装件310上的热界面材料层370。热界面材料层370可以与上述热界面材料层70基本相同。

105.因此,每个热界面材料层370可以包括第一部分370p1和第二部分370p2,其分别对应于上述每个热界面材料层70的第一部分(图2a中的70p1)和第二部分70p2。在图13a和图13b中,由附图标记370p1和370p2表示的部分可以指示半导体封装件被热界面材料层370覆盖。多个封装件308可以包括设置在基板305的第一表面305s1上的前封装件308a、308b和

308c。前封装件308a、308b和308c可以包括第一存储器封装件308a、第二存储器封装件308b和控制封装件308c。多个封装件308还可以包括设置在基板305的第二表面305s2上的后封装件308d和308e。后封装件308d和308e可以包括:与第一存储器封装件308a相同类型的第三存储器封装件308d,以及与第二存储器封装件308b相同类型的第四存储器封装件308e。

106.每个第一存储器封装件308a可以包括可以是第一存储器的半导体封装件310,并且每个第二存储器封装件308b可以包括可以是第二存储器的半导体封装件310。控制封装件308c可以包括可以是控制器的半导体封装件310。控制封装件308c可以包括控制器,并且第一存储器封装件308a和第三存储器封装件308d可以包括用于在控制封装件308c的控制下存储数据的非易失性存储器。第一存储器封装件308a和第三存储器封装件308d可以包括具有二维(2d)结构或三维(3d)垂直nand(v-nand)结构的闪存,但也可以包括其他类型的非易失性存储器,例如,相变随机存取存储器(pram)和/或电阻式随机存取存储器(rram)。

107.第二存储器封装件308b和第四存储器封装件308e可以是缓冲存储器,其用于减小外部主机与用作数据存储空间的第一存储器封装件308a和第三存储器封装件308d之间的速度差异。第二存储器封装件308b和第四存储器封装件308e也可以用作一种高速缓冲存储器,并且还可以在第一存储器封装件308a和第三存储器封装件308d的控制操作中提供用于临时存储数据的空间。第二存储器封装件308b和第四存储器封装件308e可以是易失性存储器,例如,dram。

108.基板305可以包括连接器302,该连接器302包括耦接到外部主机的多个引脚。连接器302中的多个引脚的数目和排列可以根据电子装置301与外部主机之间的通信接口而变化。电子装置301可以通过经连接器302从外部主机供应的电力来操作。电子装置301还可以包括将从外部主机供应的电力分配给控制封装件308c以及第一存储器封装件308a和第二存储器封装件308b的电力管理集成电路(pmic)390a和390b。pmic 390a和390b可以分别安装在基板305的第一表面305s1和第二表面305s2上。一些热界面材料层370可以覆盖pmic 390a和390b中的每一者的上表面。电子装置301还可以包括安装在基板305上的无源元件380,例如,电容器。

109.图14a和图14b是示出根据示例实施例的电子装置的另一示例的示意性透视图。

110.参考图14a和图14b,电子装置401可以是存储模块,例如,dram模块。电子装置401可以包括具有彼此相对的第一表面405s1和第二表面405s2的基板405、多个封装件408和散热壳体440。基板405可以包括连接器402,该连接器402包括耦接到外部主机的多个引脚。散热壳体440可以类似于参考图1描述的壳体40。例如,散热壳体440可以包括第一板443、第二板453以及连接第一板443和第二板453的连接部分460。散热壳体440还可以包括用于固定第一板443和第二板453的夹具495。第一板443和第二板453可以由能够散热的材料(例如,金属材料或石墨材料)形成。

111.第一板443可以具有面对基板405的第一表面405s1的第一内表面和与第一内表面相对的第一外表面。第二板453可以具有面对基板405的第二表面405s2的第二内表面和与第二内表面相对的第二外表面。第一板443和第二板453可以包括多个通孔443h。多个通孔443h可以包括多个第一通孔443h1和多个第二通孔443h2。第一板443和第二板453可以包括分别对应于上述的突出区域45p和雕刻图案47的突出区域和雕刻图案。

112.多个封装件408均可以包括安装在基板405上的半导体封装件410,以及位于半导

体封装件410上的热界面材料层470。热界面材料层470可以与上述热界面材料层70基本相同。因此,每个热界面材料层470可以包括第一部分470p1和第二部分470p2,其分别对应于上述每个热界面材料层70的第一部分(图2a中的70p1)和第二部分70p2。在图14a和图14b中,由附图标记470p1和470p2指示的部分可以指半导体封装件被热界面材料层470覆盖。电子装置401还可以包括安装在基板405上的无源元件480,例如,电容器。多个封装件408可以包括:设置在基板405的第一表面405s1上的第一封装件408a和第二封装件408b,以及设置在基板405的第二表面405s2上的第三封装件408c。

113.每个第一封装件408a可以包括第一存储器半导体封装件410a和覆盖第一存储器半导体封装件410a的上表面的第一热界面材料层470a,第二封装件408b可以包括控制半导体封装件410b和覆盖控制半导体封装件410b的上表面的第二热界面材料层470b,并且第三封装件408c可以包括第二存储器半导体封装件410c和覆盖第二存储器半导体封装件410c的上表面的第三热界面材料层470c。第一存储器半导体封装件410a和第二存储器半导体封装件410c可以是dram,并且控制半导体封装件410b可以是能够控制第一存储器半导体封装件410a和第二存储器半导体封装件410c的寄存器或控制器。

114.图15是示出应用了根据示例实施例的电子装置的系统1000的图。图15的系统1000基本上可以是移动系统,例如,便携式通信终端(例如,移动电话)、智能电话、平板个人计算机(pc)、可穿戴设备、医疗保健设备或物联网(iot)设备。然而,图15的系统1000不一定限于移动系统,并且可以是个人计算机(pc)、膝上型计算机、服务器、媒体播放器或诸如导航设备的车载设备等。

115.参考图15,系统1000可以包括主处理器1100、存储器1200a和1200b以及存储设备1300a和1300b。另外,系统1000可以包括图像捕获装置1410、用户输入装置1420、传感器1430、通信装置1440、显示器1450、扬声器1460、供电装置1470和连接接口1480中的至少一者。

116.存储设备1300a和1300b可以是图13a和图13b所示的电子装置301。存储器1200a和1200b可以是图14a和图14b所示的电子装置401的存储模块。因此,存储设备1300a和1300b以及存储器1200a和1200b中的至少一者可以是根据参考图1至图14b描述的示例实施例中的任一者的电子装置。

117.主处理器1100可以控制系统1000的整体操作,更具体地,可以控制系统1000中包括的其他组件的操作。主处理器1100可以实现为通用处理器、专用处理器或应用处理器。

118.主处理器1100可以包括至少一个中央处理单元(cpu)核1110,并且还可以包括被配置为控制存储器1200a和1200b和/或存储设备1300a和1300b的控制器1120。在一些实施例中,主处理器1100还可以包括加速器1130,其是用于诸如人工智能(ai)数据运算的高速数据运算的专用电路。加速器1130可以包括图形处理单元(gpu)、神经处理单元(npu)和/或数据处理单元(dpu),并且可以被实现为物理上独立于主处理器1100的其他组件的芯片。

119.存储器1200a和1200b可以用作系统1000的主存储装置。尽管存储器1200a和1200b可以包括易失性存储器,例如,静态随机存取存储器(sram)和/或dram,但存储器1200a和1200b也可以包括非易失性存储器,例如,闪存、pram和/或rram。存储器1200a和1200b也可以与主处理器1100实现在同一封装件中。

120.存储设备1300a和1300b可以用作被配置为不管是否被供电都用于存储数据的非

易失性存储设备,并且与存储器1200a和1200b相比可以具有更大的存储容量。存储设备1300a和1300b可以包括存储控制器(strg ctrl)1310a和1310b、以及在存储控制器1310a和1310b的控制下存储数据的非易失性存储器(nvm)1320a和1320b。尽管nvm 1320a和1320b可以包括具有二维(2d)结构或三维(3d)结构的v-nand闪存,但nvm 1320a和1320b可以包括其他类型的nvm,例如,pram和/或rram。例如,在存储设备1300a和1300b中,非易失性存储器1320a和1320b可以是参考图13a和图13b描述的第一存储器封装件308a和第三存储器封装件308d,并且存储控制器1310a和1310b可以是控制封装件308c。

121.存储设备1300a和1300b可以与主处理器1100物理分开并被包括在系统1000中,或者也可以与主处理器1100实现在同一封装件中。此外,存储设备1300a和1300b可以具有如图13a和图13b中所描述的固态硬盘(ssd)的类型,并且可以通过接口(例如,下面将描述的连接接口1480)可拆卸地与系统1000的其他组件组合。存储设备1300a和1300b可以是应用标准协议的设备,例如,通用闪存(ufs)、嵌入式多媒体卡(emmc)或快速非易失性存储器(nvme),不限于此。

122.图像捕获装置1410可以捕获静止图像或运动图像。图像捕获装置1410可以包括相机、摄像机和/或网络摄像头。

123.用户输入装置1420可以接收由系统1000的用户输入的各种类型的数据,并且包括触摸板、键区、键盘、鼠标和/或麦克风。

124.传感器1430可以检测可以从系统1000的外部获取的各种类型的物理量,并且将检测到的物理量转换成电信号。传感器1430可以包括温度传感器、压力传感器、照度传感器、位置传感器、加速度传感器、生物传感器和/或陀螺仪。

125.通信装置1440可以根据各种通信协议向系统1000外部的其他设备发送信号和从系统1000外部的其他设备接收信号。通信装置1440可以被实现为包括天线、收发器和/或调制解调器。

126.显示器1450和扬声器1460可以用作被配置为分别向系统1000的用户输出视觉信息和听觉信息的输出装置。

127.供电装置1470可以适当地转换从内置在系统1000中的电池(未示出)和/或外部电源供应的电力,并将转换后的电力供应给系统1000的每个组件。

128.连接接口1480可以提供系统1000与外部设备之间的连接,该外部设备连接到系统1000并且能够向系统1000发送数据和从系统1000接收数据。连接接口1480可以通过使用诸如以下各种接口方案来实现:高级技术附件(ata)、串行ata(sata)、外部sata(e-sata)、小型计算机系统接口(scsi)、串行连接scsi(sas)、外围组件互连(pci)、快速pci(pcie)、nvme、ieee 1394、通用串行总线(usb)接口、安全数字(sd)卡接口、多媒体卡(mmc)接口、emmc接口、ufs接口、嵌入式ufs(eufs)接口和紧凑型闪存(cf)卡接口。

129.参考图16,数据中心3000是收集各种类型的数据并提供服务的设施,并且也可以被称为数据存储中心。数据中心3000可以是用于运行搜索引擎和数据库的系统,并且可以是在诸如银行或政府机构的公司中使用的计算系统。数据中心3000可以包括应用服务器3100至3100n和存储服务器3200至3200m。根据示例实施例,可以不同地选择应用服务器3100至3100n的数目和存储服务器3200至3200m的数目,并且应用服务器3100至3100n的数目和存储服务器3200至3200m的数目可以不同。

130.应用服务器3100或存储服务器3200可以包括处理器3110和3210中的至少一者以及存储器3120和3220中的至少一者。以存储服务器3200为示例进行描述,处理器3210可以控制存储服务器3200的整体操作,并且访问存储器3220以执行加载在存储器3220中的指令和/或数据。存储器3220可以是双倍数据速率(ddr)同步dram(sdram)、高带宽存储器(hbm)、混合存储立方体(hmc)、双列直插式存储模块(dimm)、optane dimm和/或非易失性dimm(nvdimm)。根据示例实施例,可以不同地选择存储服务器3200中包括的处理器3210的数目和存储器3220的数目。在示例实施例中,处理器3210和存储器3220可以提供处理器-存储器对。在示例实施例中,处理器3210的数目和存储器3220的数目也可以彼此不同。处理器3210可以包括单核处理器或多核处理器。存储服务器3200的以上描述可以类似地应用于应用服务器3100。根据示例实施例,应用服务器3100可以不包括存储设备3150。存储服务器3200可以包括至少一个存储设备3250。根据示例实施例,可以不同地选择存储服务器3200中包括的存储设备3250的数目。

131.应用服务器3100至3100n和存储服务器3200至3200m可以通过网络3300彼此通信。网络3300可以使用光纤通道(fc)或以太网来实现。在这种情况下,fc是用于相对高速的数据传输的介质,并且可以使用提供高性能和/或高可用性的光开关。根据网络3300的访问方法,可以将存储服务器3200至3200m设置为文件存储、块存储或对象存储。

132.在示例实施例中,网络3300可以是仅存储网络(storage-only network),例如,存储区域网络(san)。例如,san可以是使用fc网络并且根据fc协议(fcp)实现的fc-san。作为另一示例,san可以是使用tcp/ip网络并根据iscsi(tcp/ip上的scsi或互联网scsi)协议实现的ip-san。在其他实施例中,网络3300可以是普通网络,例如tcp/ip网络。例如,可以根据诸如以太网上的fc(fcoe)、网络连接存储(nas)、fabrics上的nvme(nvme over fabrics,nvme-of)的协议来实现网络3300。

133.在下文中,将主要描述应用服务器3100和存储服务器3200。应用服务器3100的描述可以应用于其他应用服务器3100n,并且存储服务器3200的描述也可以应用于其他存储服务器3200m。

134.应用服务器3100可以通过网络3300将用户或客户请求存储的数据存储到存储服务器3200至3200m之一中。另外,应用服务器3100可以通过网络3300从存储服务器3200至3200m之一获取用户或客户请求读取的数据。例如,应用服务器3100可以被实现为网络服务器或数据库管理系统(dbms)。

135.应用服务器3100可以通过网络3300访问另一应用服务器3100n中包括的存储器3120n或存储设备3150n,和/或可以通过网络3300访问存储服务器3200-3200m中包括的存储器3220-3220m或存储设备3250-3250m。因此,应用服务器3100可以对应用服务器3100-3100n和/或存储服务器3200-3200m中存储的数据执行各种操作。例如,应用服务器3100可以执行用于在应用服务器3100-3100n和/或存储服务器3200-3200m之间移动或复制数据的命令。在这种情况下,数据可以从存储服务器3200-3200m的存储设备3250-3250m经由存储服务器3200-3200m的存储器3220-3220m被传送到应用服务器3100-3100n的存储器3120-3120n,或者被直接移动到应用服务器3100-3100n的存储器3120-3120n。通过网络3300移动的数据可以是为了安全或隐私的加密数据。

136.以存储服务器3200为示例进行描述,接口(i/f)3254可以在处理器3210与控制器

(ctrl)3251之间提供物理连接,和/或在网络接口卡(nic)3240与控制器3251之间提供物理连接。例如,接口3254可以以直接连接存储(das)方法来实现,以用专用电缆直接连接存储设备3250。而且,例如,可以以诸如以下各种接口方法来实现接口3254:高级技术附件(ata)、串行ata(sata)、外部sata(e-sata)、小型计算机系统接口(scsi)、串行连接scsi(sas)、外围组件互连(pci)、快速pci(pcie)、快速nvm(nvme)、ieee 1394、通用串行总线(usb)、安全数字(sd)卡、多媒体卡(mmc)、嵌入式多媒体卡(emmc)、通用闪存(ufs)、嵌入式通用闪存(eufs)、和/或紧凑型闪存(cf)卡接口。

137.存储服务器3200还可以包括交换机(switch)3230和网络接口卡(nic)3240。在处理器3210的控制下,交换机3230可以选择性地将处理器3210与存储设备3250连接,或者选择性地将nic 3240与存储设备3250连接。

138.在示例实施例中,nic 3240可以包括网络接口卡、网络适配器等。nic3240可以通过有线接口、无线接口、蓝牙接口、光学接口等连接到网络3300。nic 3240可以包括内部存储器、数字信号处理器(dsp)、主机总线接口等,并且可以通过主机总线接口连接到处理器3210和/或交换机3230。主机总线接口可以被实现为上述接口3254的示例之一。在一些示例实施例中,nic3240可以与处理器3210、交换机3230和存储设备3250中的至少一者集成在一起。

139.在存储服务器3200-3200m或应用服务器3100-3100n中,处理器向存储设备3150-3150n和3250-3250m或存储器3120-3120n和3220-3220m发送命令以编程或读取数据。在这种情况下,数据可以是通过纠错码(ecc)引擎纠错后的数据。数据是已经由数据总线反相(dbi)或数据掩码(dm)处理过的数据,并且可以包括循环冗余码(crc)信息。数据可以是为了安全或隐私的加密数据。

140.存储设备3150-3150n和3250-3250m可以响应于从处理器接收的读取命令,向nand闪存器件3252-3252m发送控制信号和命令/地址信号。因此,当从nand闪存器件3252-3252m读取数据时,读取使能(re)信号可以作为数据输出控制信号被输入,以将数据输出到dq总线。可以使用re信号生成数据选通信号(dqs)。可以根据写入使能(we)信号的上升沿或下降沿将命令和地址信号锁存在页面缓冲器中。

141.控制器3251可以控制存储设备3250的整体操作。在示例实施例中,控制器3251可以包括静态随机存取存储器(sram)。控制器3251可以响应于写入命令将数据写入到nand闪存器件3252中,或者可以响应于读取命令从nand闪存器件3252读取数据。例如,可以从存储服务器3200中的处理器3210、另一存储服务器3200m中的处理器3210m、或应用服务器3100-3100n中的处理器3110-3110n提供写入命令和/或读取命令。dram 3253可以临时存储(缓冲)要写入到nand闪存器件3252的数据或从nand闪存器件3252读取的数据。此外,dram 3253可以存储元数据。在这种情况下,元数据是用户数据或由控制器3251生成的用于管理nand闪存器件3252的数据。存储设备3250可以包括用于安全或隐私的安全元件(se)。

142.存储设备3150-3150n和3250-3250m可以是根据上述实施例的存储设备,例如,图13a和图13b的电子装置301。例如,在存储设备3150-3150n和3250-3250m中,nand闪存器件3252-3252m可以是参考图13a和图13b描述的第一存储器封装件308a和第三存储器封装件308d,并且控制器3251-3251m可以是参考图13a和图13b描述的控制封装件308c,并且dram3253-3253m可以是参考图13a和图13b描述的第二存储器封装件308b和第四存储器封

装件308e。

143.通过总结和回顾,示例实施例提供了一种可以改进散热特性的电子装置。也就是说,根据示例实施例,可以提供一种包括位于多个半导体封装件与板之间的热界面材料层的电子装置。热界面材料层可以通过经由板的通孔注入液体然后固化而形成。此外,设置在板的内表面上的图案(例如,雕刻图案)可以防止液体热界面材料流到半导体封装件的侧表面。上述的包括多个半导体封装件、板和热界面材料层的电子装置可以更有效地散热。

144.示例实施例已在本文中被公开,并且尽管采用了特定术语,但它们仅以一般性和描述性意义被使用和解释,而不是为了限制的目的。在一些情况下,如在提交本技术时本领域普通技术人员将显而易见的,结合特定实施例描述的特征、特性和/或元件可以单独使用,或与结合其他实施例描述的特征、特性和/或元件组合使用,除非另有特别说明。因此,本领域的技术人员将理解,在不背离如所附权利要求中阐述的本发明的精神和范围的情况下,可以进行形式和细节上的各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1