半导体结构及其制造方法与流程

本发明关于一种半导体结构及一种半导体结构的制造方法。

背景技术:

1、一般而言,半导体结构的基板上通常具有绝缘层与位于绝缘层上的介电层。然而,半导体结构的半导体层通常在绝缘层上形成的速率与在介电层上形成的速率相同。举例来说,在绝缘层与介电层中的开口形成半导体层时,由于沉积特性的关系,半导体层无法完全填满开口,使得形成在开口中的半导体层具有长条状的缝隙。由于缝隙的产生,造成半导体层产生漏电及效能不佳等问题,因此降低了半导体结构的整体效能。

技术实现思路

1、本发明的一技术态样为一种半导体结构的制造方法。

2、根据本发明一实施方式,一种半导体结构的制造方法包括:在绝缘层上形成介电层;蚀刻绝缘层及介电层,使绝缘层及介电层中具有开口,其中绝缘层的内侧壁与底部以及介电层的内侧壁从开口中裸露;注入复数个掺杂物于绝缘层的内侧壁与底部以及介电层的内侧壁上;以及在开口中及介电层上形成半导体层,其中半导体层形成在绝缘层上的第一生长速率不同于半导体层形成在介电层上的第二生长速率。

3、在本发明一实施方式中,上述形成半导体层使用平衡控制沉积(balance controldeposition,bcd)法。

4、在本发明一实施方式中,上述第一生长速率快于第二生长速率。

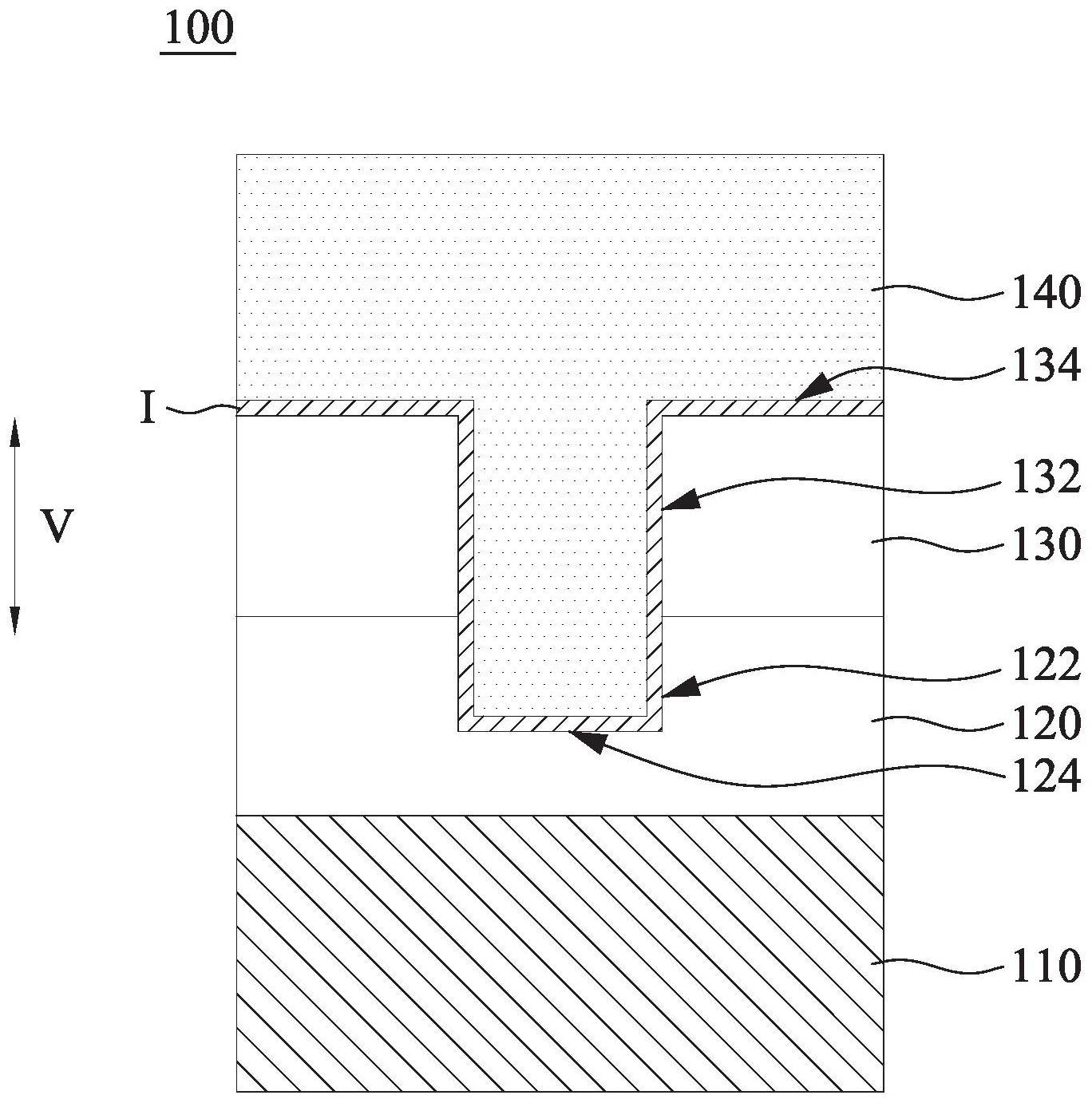

5、在本发明一实施方式中,上述半导体层的第一生长速率快于半导体层直接形成于绝缘层的生长速率。

6、在本发明一实施方式中,上述半导体层的第二生长速率慢于半导体层直接形成于介电层的生长速率。

7、在本发明一实施方式中,上述注入掺杂物于绝缘层的内侧壁与底部以及介电层的内侧壁上使用硼、磷、砷或锗。

8、本发明的另一技术态样为一种半导体结构。

9、根据本发明一实施方式,一种半导体结构包括绝缘层、介电层以及半导体层。绝缘层具有底部及邻接底部的内侧壁。介电层位于绝缘层上。介电层的内侧壁以及绝缘层的底部与内侧壁被注入复数个掺杂物。半导体层覆盖介电层以及绝缘层的底部与内侧壁。掺杂物配置以使半导体层形成在绝缘层上的第一生长速率不同于半导体层形成在介电层上的第二生长速率。

10、在本发明一实施方式中,上述半导体结构还包括基板。绝缘层位于基板与介电层之间。

11、在本发明一实施方式中,上述绝缘层与介电层具有不同材质。

12、在本发明一实施方式中,上述介电层的内侧壁与绝缘层的内侧壁在垂直方向上大致对齐。

13、在本发明上述实施方式中,半导体结构具有绝缘层、介电层以及半导体层,并且半导体结构的掺杂物配置以使半导体层形成在绝缘层上的第一生长速率不同于半导体层形成在介电层上的第二生长速率。因此,当半导体层形成在开口中时,半导体层将不具有长条状的缝隙,可改善半导体层漏电及效能不佳等问题,因此提高了半导体结构的整体效能。

技术特征:

1.一种半导体结构的制造方法,其特征在于,包含:

2.根据权利要求1所述的方法,其中形成该半导体层使用平衡控制沉积法。

3.根据权利要求1所述的方法,其中该第一生长速率快于该第二生长速率。

4.根据权利要求1所述的方法,其中该半导体层的该第一生长速率快于该半导体层直接形成于该绝缘层的生长速率。

5.根据权利要求1所述的方法,其中该半导体层的该第二生长速率慢于该半导体层直接形成于该介电层的生长速率。

6.根据权利要求1所述的方法,其中注入该些掺杂物于该绝缘层的该内侧壁与该底部以及该介电层的该内侧壁上使用硼、磷、砷或锗。

7.一种半导体结构,其特征在于,包含:

8.根据权利要求7所述的半导体结构,其中,还包含:

9.根据权利要求7所述的半导体结构,其中该绝缘层与该介电层具有不同材质。

10.根据权利要求7所述的半导体结构,其中该介电层的该内侧壁与该绝缘层的该内侧壁在垂直方向上大致对齐。

技术总结

一种半导体结构的制造方法包括:在绝缘层上形成介电层;蚀刻绝缘层及介电层,使绝缘层及介电层中具有开口,其中绝缘层的内侧壁与底部以及介电层的内侧壁从开口中裸露;注入复数个掺杂物于绝缘层的内侧壁与底部以及介电层的内侧壁上;以及在开口中及介电层上形成半导体层,其中半导体层形成在绝缘层上的第一生长速率不同于半导体层形成在介电层上的第二生长速率。当半导体层形成在开口中时,半导体层将不具有长条状的缝隙,可改善半导体层漏电及效能不佳等问题,因此提高了半导体结构的整体效能。

技术研发人员:高庆良,吴文杰,柯立苓

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!