集成芯片的制作方法

1.本发明实施例是关于集成芯片及其形成方法,特别是关于具有双蚀刻停止层结构(dual etch-stop layer structure)的集成芯片及其形成方法。

背景技术:

2.现今的集成芯片包括数百万个半导体装置。所述半导体装置通过在集成芯片上的装置上方形成的后端(back-end-of-the-line,beol)金属互连层电性互连。一般的集成芯片包括多个后端金属互连层,所述后端金属互连层包括与金属接触物(contacts)(亦即,导孔(vias))垂直耦合在一起的不同尺寸的金属线。一般的集成芯片亦包括多个介电层,所述介电层使一些金属线及/或导孔彼此电性隔离。

技术实现要素:

3.一实施例是关于一种集成芯片。所述集成芯片包括基板。第一导线(conductive wire)在第一介电层内(within),且所述第一介电层在基板上方。第一蚀刻停止层在第一介电层上方。第二蚀刻停止层在第一蚀刻停止层上方。导电导孔(conductive via)在第二介电层内,所述第二介电层在第二蚀刻停止层上方。其中,导电导孔延伸穿过(extends through)第二蚀刻停止层并沿着第一蚀刻停止层至第一导线。其中,第二蚀刻停止层的第一下表面在第一蚀刻停止层的上表面上。其中,第二蚀刻停止层的第二下表面在第一导线的上表面上。

4.另一实施例是关于一种集成芯片。所述集成芯片包括基板。第一金属线(metal wire)第一介电层内,所述第一介电层在基板上方。第一蚀刻停止层在第一介电层上方。第一蚀刻停止层包括第一介电质。第二蚀刻停止层在第一蚀刻停止层上方。第二蚀刻停止层包括不同于第一介电质的第二介电质。金属导孔(metal via)在第二介电层内,且第二介电层在第二蚀刻停止层上方。其中,金属导孔延伸穿过第二蚀刻停止层并沿着第一蚀刻停止层至第一金属线的上表面。其中,第二蚀刻停止层位于第一蚀刻停止层的上表面及侧壁上。

5.又另一实施例是关于一种集成芯片的形成方法。所述集成芯片的形成方法包括形成第一介电层在基板上方。形成第一蚀刻停止层在第一介电层上方。形成第一硬遮罩在第一蚀刻停止层上方。根据第一硬遮罩,使第一蚀刻停止层及第一介电层图案化,以在第一蚀刻停止层且在第一介电层中形成第一导线开口(wire opening),其中通过第一蚀刻停止层的第一对侧壁(pair of sidewalls)且通过第一介电层的第二对侧壁来定义(defined)第一导线开口。沉积第一金属在第一导线开口中,以形成第一金属线。形成第二蚀刻停止层在第一蚀刻停止层上方、第一金属线上方以及介于第一蚀刻停止层的第一对侧壁之间。使第二蚀刻停止层图案化,以直接在第一金属线上方形成导孔开口。沉积第二金属在导孔开口中,以形成金属导孔。

附图说明

6.根据以下的详细说明并配合所附图式阅读,能够最好的理解本公开的态样。在此强调的是,根据本产业的标准作业,各种部件未必按照比例绘制。事实上,可能任意的放大或缩小各种部件的尺寸,以做清楚的说明。

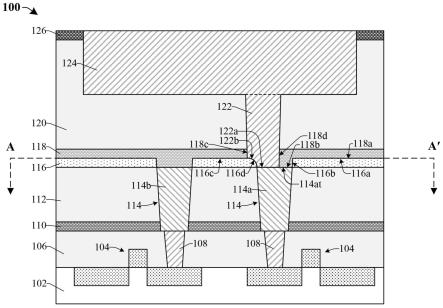

7.图1显示出集成芯片的一些实施例的剖面图,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。

8.图2显示出集成芯片的一些实施例的俯视图,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。

9.图3显示出集成芯片的一些实施例的另一剖面图,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。

10.图4显示出集成芯片的一些实施例的三维视图,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。

11.图5显示出集成芯片的一些实施例的剖面图,所述集成芯片包括第一蚀刻停止层及第二蚀刻停止层,其中第二蚀刻停止层具有弯曲的下表面。

12.图6显示出集成芯片的一些实施例的剖面图,所述集成芯片包括第一蚀刻停止层及第二蚀刻停止层,其中金属导孔与第一金属线对齐(aligned)。

13.图7显示出集成芯片的一些替代实施例的剖面图,所述集成芯片包括第一蚀刻停止层及第二蚀刻停止层,其中金属导孔与第一金属线对齐。

14.图8显示出集成芯片的一些实施例的剖面图,所述集成芯片包括第一蚀刻停止层及第二蚀刻停止层,其中第二蚀刻停止层具有弯曲的侧壁。

15.图9显示出集成芯片的一些替代实施例的剖面图,所述集成芯片包括第一蚀刻停止层及第二蚀刻停止层,其中第二蚀刻停止层具有弯曲的侧壁。

16.图10显示出集成芯片的一些实施例的剖面图,所述集成芯片包括第一蚀刻停止层及第二蚀刻停止层,其中第一蚀刻停止层沿着第一金属线的两侧壁(opposing sidewalls)延伸。

17.图11至图26显示出用于形成集成芯片的方法的一些实施例的剖面图,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。

18.图27显示出用于形成集成芯片的方法的一些实施例的流程图,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。

19.其中,附图标记说明如下:

20.100,300,500,600,700,800,900,1100,1200,1300,1400,1500,1600,1700,1800,1900,2000,2100,2200,2300,2400,2500,2600:剖面图

21.102:基板

22.104:半导体装置

23.106:基底介电层

24.108:接触物

25.110:基底蚀刻停止层

26.112:第一层间介电层

27.114:金属线

28.114a:第一金属线

29.114at,116d,118t,122d,122e:上表面

30.114b:第二金属线

31.116:第一蚀刻停止层

32.116a:第一上表面

33.116b,118c:第一侧壁

34.116c:第二上表面

35.116f,122c,118e:下表面

36.118:第二蚀刻停止层

37.118a,122a:第一下表面

38.118b,122b:第二下表面

39.118d:第二侧壁

40.120:第二层间介电层

41.122:金属导孔

42.124:额外金属线

43.1202:第一硬遮罩

44.1204:第二硬遮罩

45.1206:第一抗反射涂布层

46.1208:第一光阻遮罩

47.126:第三蚀刻停止层

48.1402:下导线开口

49.1402a:第一下导线开口

50.1502:第一金属

51.1902:第三硬遮罩

52.1904:第二抗反射涂布层

53.1906:第二光阻遮罩

54.200:俯视图

55.2102:第三抗反射涂布层

56.2104:第三光阻遮罩

57.2202:导孔开口

58.2302:上导线开口

59.2502:第二金属

60.2700:方法

61.2702,2704,2706,2708,2710,2712,2714,2716,2718,2820,2722:步骤400:三维视图

具体实施方式

62.以下的公开内容提供许多不同的实施例或范例,以实施所提供的发明标的中的不同部件。以下叙述组件及排列方式的特定范例,以简化本公开。当然,这些特定的范例仅为

范例,而非用以限定。举例而言,若是本公开叙述了将第一部件形成于第二部件上方(over)或上(on),即表示其可能包括前述第一部件与前述第二部件是以直接接触(in direct contact)的方式来形成的实施例,且亦可能包括了将其他部件形成于前述第一部件与前述第二部件之间,而使前述第一部件与前述第二部件可能未直接接触的实施例。另外,在不同范例中,本公开可能重复使用元件符号及/或标记。这些重复是为了简化与清晰的目的,并非用以限定在此所讨论的不同实施例及/或配置之间有特定的关系。

63.再者,本文所用的空间相关用词,诸如:「之下(beneath)」、「下方(below)」、「下(lower)」、「之上(above)」、「上部(upper)」及其类似用语,是用于简化如图式所示的一元件或部件与另一(些)元件或部件的关系的描述。除了如图式所示的方向之外,这些空间相关用词旨在涵盖使用中或操作中的装置的不同方位。设备可以其他方向定向(旋转90度或在其他方向),且本文所用的空间相关用词可相应地解释。

64.许多集成芯片(integrated chip)包括在基板上方的互连(interconnect)结构。举例而言,互连结构可以包括在基板上方的第一金属线及第二金属线。第一介电层可以使第一金属线与第二金属线横向分离(laterally separate)且电性隔离(electrically isolate)。再者,金属导孔可以在第一金属线上方,并且可以延伸穿过第二介电层及蚀刻停止层至第一金属线的顶部(top)。此外,第三金属线可以在金属导孔上方。第三金属线可以穿过(through)金属导孔电性连接到第一金属线,并且第一金属线可以沿着基板电性连接到一或多个半导体装置。

65.在一些集成芯片中,通过使第二介电层及蚀刻停止层图案化,以在第二介电层及蚀刻停止层中形成导孔开口,并随后在沉积金属在导孔开口中,而形成金属导孔在第一金属线上方。在一些情况下,当使第二介电层及蚀刻停止层图案化以形成导孔开口时,可能会发生未对准(misalignment)(举例而言,覆盖偏移(overlay shift))。由于未对准,图案化可能会损坏或移除围绕(around)第一金属线的一些下方的(underlying)第一介电层。结果是,导孔开口及金属导孔因此可以延伸到第一介电层中。对第一介电层造成的损坏会减少介于第一金属线与第二金属线之间的横向距离(lateral distance)。减少介于第一金属线及第二金属线之间的横向距离会对第一介电层的可靠性产生负面影响。举例而言,可能会降低第一介电层的时间相关介电击穿(time dependent dielectric breakdown,tddb)。结果是,集成芯片的可靠性可能较低。此外,减少介于第一金属线及第二金属线之间的横向距离还可能增加介于第一金属线及第二金属线之间的电容(capacitance),从而可能增加集成芯片的电阻-电容(resistance-capacitance,rc)延迟(delay)。结果是,集成芯片的性能可能较低。

66.本公开的各种实施例关于一种使用双蚀刻停止层(dual etch-stop layer)的集成芯片的形成方法,配置所述双蚀刻停止层以减少未对准损坏并提高集成芯片的可靠性及性能。在一些实施例中,所述形成方法包括根据第一蚀刻停止层,使第一介电层图案化以定义第一互连开口。形成金属在开口内,以定义第一金属线,同时使第一蚀刻停止层保持(kept)在一位置来覆盖(cover)第一介电层的顶部。随后形成第二蚀刻停止层在第一蚀刻停止层上方且介于第一蚀刻停止层的侧壁之间。形成第二介电层在第二蚀刻停止层上。随后使用蚀刻剂来使第二介电层及第二蚀刻停止层图案化,以定义暴露第一金属线的第二互连开口。配置蚀刻剂为以比第一蚀刻停止层更高的速率蚀刻第二介电层及第二蚀刻停止

层。由于蚀刻速率的差异,第一蚀刻停止层可以防止第二互连开口的未对准导致对第一介电层的损坏。

67.因为第一蚀刻停止层可以防止第一介电层受到损坏,所以可以维持第一介电层的可靠性。举例而言,可以不减少第一介电层的tddb。此外,因为第一蚀刻停止层可以防止导孔开口延伸到第一介电层中,所以可以保持介于第一金属线及第二金属线之间的距离。因此,介于第一金属线及第二金属线之间的电容可能不会增加,因此集成芯片的rc延迟可能较低。

68.图1显示出了集成芯片的一些实施例的剖面图100,所述集成芯片包括第一蚀刻停止层116及在第一蚀刻停止层116上方的第二蚀刻停止层118。举例而言,图1的剖面图100可由图2的a-a’线段撷取。

69.集成芯片包括沿着基板102的多个半导体装置104。基底(base)介电层106在基板102上方,并且多个接触物108延伸穿过基底介电层106。多个接触物108可以电性连接到多个半导体装置104中的任何一者。基底蚀刻停止层110在基底介电层106上方,且第一层间介电(interlayer dielectric,ild)层112在基底蚀刻停止层110上方。

70.多个金属线114在第一ild层112及基底蚀刻停止层110内。举例而言,第一金属线114a及与第一金属线114a相邻的(adjacent)第二金属线114b在第一ild层112内。第一ild层112及基底蚀刻停止层110使第一金属线114a与第二金属线114b横向分离及电性隔离。第一金属线114a及第二金属线114b延伸穿过第一ild层112及基底蚀刻停止层110至多个接触物108的下方的接触物。通过接触物108,第一金属线114a及第二金属线114b可以电性连接到多个半导体装置104中的任何一者。

71.再者,第一蚀刻停止层116在第一ild层112上方,并且第二蚀刻停止层118在第一蚀刻停止层116上方。第二蚀刻停止层118也在第一金属线114a及第二金属线114b上方。第二蚀刻停止层118的第一下表面(lower surface)118a在第一蚀刻停止层116的第一上表面(top surface)116a上,且第二蚀刻停止层118的第二下表面118b在第一金属线114a的上表面114at上。再者,第二蚀刻停止层118在第一蚀刻停止层116的第一侧壁116b上。在一些实施例中,第二蚀刻停止层118的第一侧壁118c直接在蚀刻停止层116的第二上表面116c上方,第二蚀刻停止层118的第二侧壁118d相对于第一侧壁118c,第二蚀刻停止层118的第二侧壁118d直接在第一金属线114a的上表面114at上方。在一些实施例中,第二蚀刻停止层118的第二侧壁118d具有比第二蚀刻停止层118的第一侧壁118c更大的高度(greater height)。第一蚀刻停止层116包括第一介电材料,且第二蚀刻停止层118包括不同于第一介电材料的第二介电材料。

72.第二ild层120在第二蚀刻停止层118上方,第三蚀刻停止层126在第二ild层120上方,金属导孔122在第二ild层120内,且额外(additional)金属线124在第二ild层120内。金属导孔122延伸穿过第二ild层120且沿着(along)第二蚀刻停止层118的侧壁(举例而言,第一侧壁118c、第二侧壁118d)延伸。金属导孔122进一步沿着第一蚀刻停止层116的一或多个表面(举例而言,上表面116d)到第一金属线114a的上表面114at。金属导孔122可以从第一金属线114a横向偏移(offset)(举例而言,未对准)。举例而言,第一金属线114a可以沿第一垂直线(vertical line)居中(centered),所述第一垂直线与沿着金属导孔122居中的第二垂直线横向分离。在一些实施例中,金属导孔122的第一下表面122a在第一金属线114a的上

表面114at上,且金属导孔122的第二下表面122b在第一蚀刻停止层116的上表面(upper surface)116d上。在一些实施例中,通过第一蚀刻停止层116,金属导孔122与第一ild层112垂直分离。

73.当形成金属导孔122在第一金属线114a上方时,使第二ild层120、第二蚀刻停止层118及第一蚀刻停止层116图案化,以形成导孔开口(via opening)(未显示出)。相对于第一蚀刻停止层116,图案化制程对于第二ild层120及第二蚀刻停止层118可以是高度选择性的(highly selective)(例如,可以以实质上(substantially)比第一蚀刻停止层116更快的速率来移除第二ild层120及第二蚀刻停止层118)。因此,即使在未对准的情况下,第一蚀刻停止层116也可以防止图案化制程损坏下方的第一ild层112。举例而言,如果在图案化制程中发生未对准,则图案化制程可能如同第一蚀刻停止层116的上表面116d的弯曲形状所反映的形状来改变第一蚀刻停止层116的一部分。然而,由于图案化制程的选择性,图案化制程可能不会延伸穿过第一蚀刻停止层116至下方的第一ild层112。

74.因此,因为第一蚀刻停止层116可以防止第一ild层112受到损坏,所以可以维持第一ild层112的可靠性。举例而言,可以不减少第一ild层112的tddb。再者,因为第一蚀刻停止层116可以防止导孔开口及金属导孔122因此延伸到第一ild层112中,所以可以维持介于第一金属线114a及第二金属线114b之间的距离。因此,介于第一金属线114a及第二金属线114b之间的电容可能不会增加,所以集成芯片的rc延迟可能较低。

75.图2显示出了集成芯片的一些实施例的俯视图200,所述集成芯片包括第一蚀刻停止层116及在第一蚀刻停止层116上方的第二蚀刻停止层118。

76.在这些实施例中,第二蚀刻停止层118在第一金属线114a上方、第二金属线114b上方以及在介于第一蚀刻停止层116的侧壁之间延伸。举例而言,第二蚀刻停止层118从在第一蚀刻停止层116的第一侧壁116b上延伸至与第一侧壁116b相对的第一蚀刻停止层116的第二侧壁116e上。再者,第二蚀刻停止层118具有一长度,所述长度沿着下方的第一金属线114a及第二金属线114b的长度延伸。在一些实施例中,第二蚀刻停止层118的长度可以近似(approximately)等于第一金属线114a及第二金属线114b的长度。在一些实施例中,金属导孔122的长度小于第二蚀刻停止层118的长度。在一些实施例中,金属导孔122的长度可以大约等于金属导孔122的宽度。

77.图3显示出了集成芯片的一些实施例的另一剖面图300,所述集成芯片包括第一蚀刻停止层116及在第一蚀刻停止层116上方的第二蚀刻停止层118。举例而言,图3的剖面图300可由图2的b-b’线段撷取。

78.在这些实施例中,第二蚀刻停止层118在第一金属线114a的上表面114at上。并且沿着第一金属线114a的上表面114at在金属导孔122的两侧(opposite sides)延伸。金属导孔122延伸穿过第二蚀刻停止层118至第一金属线114a的上表面114at。

79.虽然图1、图2及图3显示出了在互连的第一层(first level)(举例而言,在紧接(immediately over)在接触层(contact level)上方的第一金属层(metal level))上的第一蚀刻停止层116及第二蚀刻停止层118,但是应当理解的是,第一蚀刻停止层116及第二蚀刻停止层118可以在互连的任何其他层上实施。举例而言,可以实施第一蚀刻停止层116及第二蚀刻停止层118在互连的第二金属层、第三金属层、第四金属层或一些其他合适的层上。

80.图4显示出了集成芯片的一些实施例的三维视图400,所述集成芯片包括第一蚀刻停止层116及在第一蚀刻停止层116上方的第二蚀刻停止层118。

81.在这些实施例中,第二蚀刻停止层118以封闭环形(closed loop)(举例而言,沿着第二蚀刻停止层118的上表面)围绕(surrounds)金属导孔122。再者,第二蚀刻停止层118在金属导孔122的第一对相对侧壁及金属导孔122的第二对相对侧壁上,且第二蚀刻停止层118沿着金属导孔122的第一对相对侧壁及金属导孔122的第二对相对侧壁延伸。在一些实施例中,第二蚀刻停止层118沿着金属导孔122的侧壁,从第二蚀刻停止层118的上表面118t垂直延伸(extends vertically)至下方的第一金属线114a的上表面114at。

82.应当注意的是,为了简要说明,在图4中仅显示出了基底蚀刻停止层110、第一ild层112、多个金属线114、第一蚀刻停止层116、第二蚀刻停止层118及金属导孔122。

83.图5显示出了集成芯片的一些实施例的剖面图500,所述集成芯片包括第一蚀刻停止层116及第二蚀刻停止层118,其中第二蚀刻停止层118具有弯曲的第二下表面118b。

84.在这些实施例中,第一金属线114a的上表面114at是弯曲的(举例而言,凹入的((concave))。第二蚀刻停止层118a具有第一下表面118a及第二下表面118b。第二蚀刻停止层118的第二下表面118b在第一金属线114a的弯曲上表面114at上,且因此第二蚀刻停止层118的第二下表面118b也是弯曲的(举例而言,凸出的(convex))。再者,金属导孔122的第一下表面122a在第一金属线114a的弯曲上表面114at上,且因此第一下表面122a也是弯曲的(举例而言,凸出的)。在一些实施例中,因为第一金属线114a的上表面114at是弯曲的,所以第二蚀刻停止层118的第二下表面118b低于第一蚀刻停止层116的下表面(bottom surface)116f。

85.由于在形成第一金属线114a之后,第一金属线114a受到凹入(举例而言,参照图16及图17),第一金属线114a可以具有弯曲的上表面114at。举例而言,凹入制程可以比沿着第一金属线114a的侧面(sides)更快地移除沿着第一金属线114a的中心的第一金属线114a的一部分,导致在凹入制程之后,第一金属线114a的顶表面114at为弯曲的。

86.图6显示出了集成芯片的一些实施例的剖面图600,所述集成芯片包括第一蚀刻停止层116及第二蚀刻停止层118,其中金属导孔122与第一金属线114a对齐(aligned)。

87.在这些实施例中,金属导孔122的侧壁与下方的第一金属线114a的侧壁对齐。在一些实施例中,金属导孔122的侧壁及第一金属线114a的侧壁可以近似于共面(coplanar)。再者,在一些实施例中,金属导孔122的侧壁在第一蚀刻停止层116的侧壁上。在一些实施例中,金属导孔122的侧壁可以与第一蚀刻停止层116的侧壁直接接触。

88.在一些实施例中,由于在金属导孔122形成制程中很少或没有未对准,所以金属导孔122的侧壁可以与第一金属线114a的侧壁对准。

89.图7显示出了集成芯片的一些替代实施例的剖面图700,所述集成芯片包括第一蚀刻停止层116及第二蚀刻停止层118,其中金属导孔122与第一金属线114a对齐。

90.在这些实施例中,金属导孔122与第一金属线114a对齐,使得金属导孔122不从第一金属线114a横向偏移。再者,金属导孔122的下表面122c在第一金属线114a的上表面114at上,且金属导孔122的下表面122c窄于第一金属线114a的上表面114at。此外,第二蚀刻停止层118的下表面118e可以在第一金属线114a的上表面114at上并且在金属导孔122的两侧上。此外,第二蚀刻停止层118的下表面118e可以沿着第一金属线114a的上表面114at

围绕金属导孔122。换句话说,第二蚀刻停止层118可以围绕介于第一蚀刻停止层116的侧壁之间的金属导孔122。

91.在这些实施例中,由于在金属导孔122形成制程中很少或没有未对准,所以金属导孔122可以与第一金属线114a对齐。再者,由于金属导孔122的轮廓(profile)(例如,金属导孔122的侧壁的角度),所以金属导孔122的下表面122c可以比第一金属线114a的上表面114at更窄。举例而言,金属导孔122沿着金属导孔122的顶部可以比沿着金属导孔122的底部更宽,使得金属导孔122沿金属导孔122的深度变窄。因此,在金属导孔122与第一金属线114a相交(meet)的深度处,金属导孔122的下表面122c的宽度可以小于第一金属线114a的上表面114at的宽度。

92.图8显示出了集成芯片的一些实施例的剖面图800,所述集成芯片包括第一蚀刻停止层116及第二蚀刻停止层118,其中第二蚀刻停止层118具有弯曲的侧壁。

93.在这些实施例中,第二蚀刻停止层118具有沿着金属导孔122的弯曲(举例而言,凹入的)侧壁。举例而言,在一些实施例中,第二蚀刻停止层118的第一侧壁118c及第二蚀刻停止层118的第二侧壁118d是弯曲的。再者,金属导孔122还具有沿着第二蚀刻停止层118的弯曲侧壁(例如,第一侧壁118c、第二侧壁118d)的弯曲侧壁(举例而言,凸出的)。在一些实施例中,金属导孔122与下方的第一金属线114a对齐。在一些实施例中,第二蚀刻停止层118的弯曲侧壁(例如,第一侧壁118c、第二侧壁118d)在第一蚀刻停止层116上方。在一些实施例中,金属导孔122具有一或多个上表面(举例而言,上表面122d、上表面122e),所述一或多个上表面在第二ild层120的一或多个下表面上。金属导孔122的弯曲侧壁定义了从金属导孔122的侧壁向外延伸(extends outward)以横向越过(laterally past)第二ild层120的侧壁的凸部(protrusion)。在一些实施例中,限制(confined)凸部在介于第一蚀刻停止层116的上表面及第二ild层120的下表面之间。

94.因为用于在第二蚀刻停止层118中形成开口的蚀刻可以具有等向性(isotropic)特性(举例而言,横向分量(lateral component)),所以第二蚀刻停止层118可以具有弯曲的侧壁。举例而言,可以使用湿式蚀刻制程,以形成开口在第二蚀刻停止层118中,且湿式蚀刻制程可以在垂直方向及横向方向之两者上蚀刻第二蚀刻停止层118。

95.图9显示出了集成芯片的一些替代性实施例的剖面图900,所述集成芯片包括第一蚀刻停止层116及第二蚀刻停止层118,其中第二蚀刻停止层118具有弯曲的侧壁。

96.在这些实施例中,第二蚀刻停止层118具有沿着金属导孔122的弯曲(举例而言,凹入的)侧壁。金属导孔122还具有沿着第二蚀刻停止层118的弯曲侧壁的弯曲的(举例而言,凸出的)侧壁。再者,在这些实施例中,金属导孔122与下方的第一金属线114a未对准(例如,偏移)。在一些实施例中,第二蚀刻停止层118的弯曲的第一侧壁118c在第一蚀刻停止层116上方,且相对于弯曲的第一侧壁118c的第二蚀刻停止层118的第二侧壁118d在第一金属线114a上方。在一些实施例中,弯曲的第二侧壁118d可以具有比弯曲的第一侧壁118c更大的高度。在一些实施例中,金属导孔122具有一或多个上表面(例如,上表面122d、上表面122e),所述一或多个上表面在第二ild层120的一或多个下表面上。

97.同样地,因为用于在第二蚀刻停止层118中形成开口的蚀刻可以具有等向性特性(例如,横向分量),所以第二蚀刻停止层118可以具有弯曲的侧壁。举例而言,可以使用湿式蚀刻制程,以形成开口在第二蚀刻停止层118中,且湿式蚀刻制程可以在垂直方向及横向方

向之两者上蚀刻第二蚀刻停止层118。

98.图10显示出了集成芯片的一些实施例的剖面图1000,所述集成芯片包括第一蚀刻停止层116及第二蚀刻停止层118,其中第一蚀刻停止层116沿着第一金属线114a的两侧壁(opposing sidewalls)延伸。

99.在这些实施例中,第一金属线114a的上表面114at与第一蚀刻停止层116的上表面116a近似于共面(例如,在化学机械抛光(chemical mechanical polishing,cmp)制程的公差(tolerance)中共面)。在一些实施例中,第一金属线114a的两侧壁可以与第一蚀刻停止层116的侧壁直接接触。在一些实施例中,第二蚀刻停止层118的下表面118e从第一蚀刻停止层116上方延伸至第一金属线114a上方。在一些实施例中,第一金属线114a在第一蚀刻停止层116的第一侧壁上且在相对于第一侧壁的第一蚀刻停止层116的第二侧壁上。

100.由于在形成第一金属线114a之后,可以不使第一金属线114a凹入(举例而言,参照图16),因此第一蚀刻停止层116可以沿着第一金属线114a的两侧壁延伸。

101.在一些实施例中,金属导孔122可以在第一金属线114a的上表面上,并且可以与第一金属线114a不对准。此外,第一蚀刻停止层116的上表面可能因为导孔未对准而弯曲。举例而言,当使第二蚀刻停止层118图案化,以形成导孔开口在第二蚀刻停止层118中时,图案化制程可能影响第一蚀刻停止层116,从而形成第一蚀刻停止层116的弯曲上表面。

102.在一些实施例中,基板102可以举例而言,包括硅(silicon)、一些iii-v材料、一些其他半导体材料或其类似物。

103.在一些实施例中,多个半导体装置104可以举例而言是或包括金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)、双极接面晶体管(bipolar junction transistors,bjt)、接面场效晶体管(junction field-effect transistors,jfet)、鳍式场效晶体管(fin field-effect transistors,finfet)、全绕式栅极场效晶体管(gate-all-around field-effect transistors,gaa fet)、一些其他合适的半导体装置或其类似物中的任何装置。

104.在一些实施例中,基底介电层106可以举例而言包括碳化硅(silicon carbide)(例如,sic)、二氧化硅(silicon dioxide)(例如,sio2)、碳氧化硅(silicon oxycarbide)(例如,sioc)、碳氢化硅(silicon carbon hydrogen)(例如,sich)、氮化硅(silicon nitride)(例如,sin)、碳氮化硅(silicon carbonitride)(例如,sicn)、氧氮化硅(silicon oxynitride)(例如,sion)、氧碳氮化硅(silicon oxycarbonitride)(例如,siocn)、氧化铝(aluminum oxide)(例如,alo)、氧氮化铝(aluminum oxynitride)(例如,alon)、氮化铝(aluminum nitride)(例如,aln)或一些其他合适的介电质中的任何材料。

105.在一些实施例中,多个接触物108可以举例而言包括钽(tantalum)(例如,ta)、氮化钽(tantalum nitride)(例如,tan)、氮化钛(titanium nitride)(例如,tin)、铜(copper)(例如,cu)、钴(cobalt)(例如,co)、钌(ruthenium)(例如,ru)、钼(molybdenum)(例如,mo)、铱(iridium)(例如,ir)、钨(tungsten)(例如,w)或一些其他合适的导电材料中的任何材料。

106.在一些实施例中,基底蚀刻停止层110可以举例而言包括碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氧氮化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氮氧化铝(例如,alon)、氧化铝(例如,alo)或

一些其他合适的介电质中的任何材料。

107.在一些实施例中,第一ild层112、第二ild层120及第三蚀刻停止层126可以举例而言包括碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或一些其他合适的介电质中的任何材料。

108.第一蚀刻停止层116包括第一介电材料,且第二蚀刻停止层118包括不同于第一介电材料的第二介电材料。在一些实施例中,第一蚀刻停止层116及/或第二蚀刻停止层118可以举例而言包括碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氧氮化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或一些其他合适的介电质中的任何材料。

109.在一些实施例中,多个金属线114、金属导孔122及额外金属线124可以举例而言包括钽(例如,ta)、氮化钽(例如,tan)、氮化钛(例如,tin)、铜(例如,cu)、钴(例如,co)、钌(例如,ru)、钼(例如,mo)、铱(例如,ir)、钨(例如,w)或一些其他合适的导电材料中的任何材料。

110.图11至图26显示出用于形成集成芯片的方法的一些实施例的剖面图1100~2600,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。虽然图11至图26是关于一种方法来描述的,但是将应理解的是,在图11至图26中公开的结构不限于这种方法,而是可以作为独立于所述方法(independent of the method)的结构单独存在(stand alone)。

111.如图11的剖面图1100所示,沿着基板102形成多个半导体装置104,形成基底介电层106在基板102上方,并且形成多个接触物108在基底介电层106中。

112.多个半导体装置104可以举例而言,通过离子植入(ion implantation)制程、沉积制程、图案化制程或一些其他合适的制程中的任何制程来形成。

113.基底介电层106可以举例而言,通过化学气相沉积(chemical vapor deposition,cvd)制程、物理气相沉积(physical vapor deposition,pvd)制程、原子层沉积(atomic layer deposition,ald)制程、旋转涂布(spin on)制程或其他一些合适的制程中的任何制程,来沉积碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或其他合适的介电质中的任何材料在基板102上方。

114.多个接触物108可以举例而言,通过使基底介电层106图案化;沉积一或多个金属在经图案化的基底介电层106上方;以及平坦化一或多个金属来形成。举例而言,图案化可以包括干式蚀刻制程。一或多个金属可以举例而言,包括钽(例如,ta)、氮化钽(例如,tan)、氮化钛(例如,tin)、铜(例如,cu)、钴(例如,co)、钌(例如,ru)、钼(例如,mo)、铱(例如,ir)、钨(例如,w)或一些其他合适的导电材料中的任何材料,且可以通过cvd制程、pvd制程、ald制程、电化学镀(electrochemical plating,ecp)制程、溅镀(sputtering)制程、旋转涂布制程或一些其他合适的制程中的任何制程来沉积。举例而言,平坦化制程可以是或包括化

学机械平坦化(chemical mechanical planarization,cmp)或一些其他合适的平坦化制程。

115.如图12的剖面图1200所示,形成基底蚀刻停止层110在基板102上方;形成第一层间介电(ild)层112在基底蚀刻停止层110上方;形成第一蚀刻停止层116在第一ild层112上方;形成第一硬遮罩1202在第一蚀刻停止层116上方;形成第二硬遮罩1204在第一硬遮罩1202上方;形成第一抗反射涂布(anti-reflective coating,arc)层1206在第二硬遮罩1204上方;并且形成第一光阻遮罩1208在第一arc层1206上方。

116.基底蚀刻停止层110可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或其他一些合适的制程中的任何制程,来沉积碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氮氧化铝(例如,alon)、氧化铝(例如,alo)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约20至400摄氏度(degrees celsius)或一些其他合适的数值。此外,基底蚀刻停止层110的厚度可以举例而言,是大约10到1000埃(angstroms)或一些其他合适的数值。

117.第一ild层112可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或其他一些合适的制程中的任何制程,来沉积碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约25至400摄氏度或一些其他合适的数值。此外,第一ild层112的厚度可以举例而言,是大约10到800埃或一些其他合适的数值。

118.第一蚀刻停止层116可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或其他一些合适的制程中的任何制程,来沉积碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约25至400摄氏度或一些其他合适的数值。此外,第一蚀刻停止层116的厚度可以举例而言,是大约10到800埃或一些其他合适的数值。

119.第一硬遮罩1202及第二硬遮罩1204可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或其他一些合适的制程中的任何制程,来沉积氮化钛(titanium nitride)(例如,tin)、氧化钛(titanium oxide)(例如,tio)、钨(例如w)、掺杂钨的碳(tungsten doped carbon)(例如,wdc)、氧化铪(hafnium oxide)(例如,hfo)、氧化锆(zirconium oxide)(例如,zro)、氧化锌(zinc oxide)(例如,zno)、氧化钛锆(titanium zirconium oxide)(例如,tizro)、碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、碳氧化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约50至400摄氏度或一些其他合适的数值。此外,第一硬遮罩1202的厚度及/或第二硬遮罩1204的厚度可以举例而言,是大约30到500埃或一些其他合适的数值。

120.第一arc层1206可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程、或其他一些合适的制程中的任何制程,来沉积一些有机聚合物(organic polymer)、一些无机聚合物(inorganic polymer)或一些其他合适的材料在基板102上方而形成。

121.第一光阻遮罩1208可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或一些其他合适的制程中的任何制程,来沉积光阻在基板102上方并随后使光阻显影而形成。

122.如图13的剖面图1300所示,根据第一光阻遮罩(例如,图12的第一光阻遮罩1208),使第二硬遮罩1204及第一硬遮罩1202图案化。

123.举例而言,图案化可以包括干式蚀刻制程或一些其他合适的蚀刻制程。举例而言,图案化可以包括电感耦合等离子体(inductively coupled plasma,icp)反应性离子蚀刻(reactive ion etching,rie)制程、导电耦合等离子体(conductively coupled plasma,ccp)rie制程或一些其他合适的制程。

124.如图14的剖面图1400所示,根据第一硬遮罩1202,使第一蚀刻停止层116、第一ild层112及基底蚀刻停止层110图案化,以形成多个下导线开口(lower wire openings)1402在第一蚀刻停止层116、第一ild层112及基底蚀刻停止层110中。通过第一蚀刻停止层116的侧壁、第一ild层112的侧壁及基底蚀刻停止层110的侧壁,来定义多个下导线开口1402。举例而言,图案化形成第一下导线开口1402a在第一蚀刻停止层116、第一ild层112及基底蚀刻停止层110中。通过第一蚀刻停止层116的一对(pair of)侧壁、第一ild层112的一对侧壁及基底蚀刻停止层110的一对侧壁,来定义第一下导线开口1402a。

125.在一些实施例中,利用共同的(common)图案化制程,使第一蚀刻停止层116、第一ild层112及基底蚀刻停止层110各自图案化。在一些其他实施例中,以第一图案化制程使第一蚀刻停止层116及第一ild层112图案化,并且以第二图案化制程使基底蚀刻停止层110图案化。

126.使第一蚀刻停止层116及第一ild层112图案化(例如,第一图案化制程)可以包括干式蚀刻制程或一些其他合适的蚀刻制程。举例而言,图案化制程可以包括icp rie制程、ccp rie制程或一些其他合适的制程。举例而言,图案化可以使用甲烷(methane)(例如,ch4)、氟甲烷(fluoromethane)(例如,ch3f)、二氟甲烷(difluoromethane)(例如,ch2f2)、三氟甲烷(trifluoromethane)(例如,chf3)、八氟环丁烷(octafluorocyclobutane)(例如,c4f8)、六氟-1,3-丁二烯(hexafluoro-1,3-butadiene)(例如,c4f6)、四氟甲烷(tetrafluoromethane)(例如,cf4)、氢气(hydrogen)(例如,h2)、溴化氢(hydrogen bromide)(例如,hbr)、一氧化碳(carbon monoxide)(例如,co)、二氧化碳(carbon dioxide)(例如,co2)、氧气(oxygen)(例如,o2)、三氯化硼(boron trichloride)(例如,bcl3)、氯气(chlorine)(例如,cl2)、氮气(nitrogen)(例如,n2)、氦气(helium)(例如,he)、氖气(neon)(例如,ne)、氩气(argon)(例如,ar)或一些其他合适的气体中的任何气体。举例而言,在图案化期间施加的压力可以是大约0.2到120毫托(millitorr)或一些其他合适的数值。举例而言,在图案化期间施加的温度可以是大约0到100摄氏度或一些其他合适的数值。举例而言,在图案化期间施加的功率(power)可以是大约50到3000瓦(watts)。举例而言,在图案化期间施加的偏压(bias voltage)可以是大约0至1200伏(volts)或一些其他合适的数值。

127.在一些实施例中,可以在第一图案化制程期间中及/或之后移除第二硬遮罩1204。举例而言,可以通过干式蚀刻制程消耗第二硬遮罩1204。

128.此外,使基底蚀刻停止层110图案化(例如,第二图案化制程)可以包括湿式蚀刻制程、干式蚀刻制程或一些其他合适的蚀刻制程。举例而言,湿式蚀刻制程可以使用氢氟酸(hydrofluoric acid)、磷酸(phosphoric acid)、氢氧化钾(potassium hydroxide)、四甲基氢氧化铵(tetramethylammonium hydroxide)、硝酸(nitric acid)或一些其他合适的湿式蚀刻剂中的任何蚀刻剂。此外,干式蚀刻制程可以包括举例而言,icp rie制程、ccp rie制程、远程等离子体(remote plasma)蚀刻制程或一些其他合适的制程。举例而言,干式蚀刻制程可以使用甲烷(例如,ch4)、氟甲烷(例如,ch3f)、二氟甲烷(例如,ch2f2)、三氟甲烷(例如,chf3)、八氟环丁烷(例如,c4f8)、六氟-1,3-丁二烯(例如,c4f6)、四氟甲烷(例如,cf4)、氢气(例如,h2)、溴化氢(例如,hbr)、一氧化碳(例如,co)、二氧化碳(例如,co2)、氧气(例如,o2)、三氯化硼(例如,bcl3)、氯气(例如,cl2)、氮气(例如,n2)、氦气(例如,he)、氖气(例如,ne)、氩气(例如,ar)或一些其他合适的气体中的任何气体。举例而言,在干式蚀刻制程期间施加的压力可以是大约0.2到120毫托或一些其他合适的数值。举例而言,在干式蚀刻制程期间施加的温度可以是大约0到100摄氏度或一些其他合适的数值。举例而言,在干式蚀刻制程期间施加的功率可以是大约50到3000瓦。举例而言,在干式蚀刻制程期间施加的偏压可以是大约0至1200伏或一些其他合适的数值。

129.在一些实施例中,在第二图案化制程之后,可以移除第一硬遮罩1202。举例而言,在第二图案化制程之后,可以通过单独的(separate)湿式蚀刻制程或一些其他合适的制程,来移除第一硬遮罩1202。

130.如图15的剖面图1500所示,沉积第一金属1502在基板102上方且在多个下导线开口1402中,以形成多个金属线114在多个下导线开口1402中。举例而言,沉积第一金属1502在第一下导线开口1402a中,以形成第一金属线114a。

131.举例而言,第一金属1502可以包括钽(例如,ta)、氮化钽(例如,tan)、氮化钛(例如,tin)、铜(例如,cu)、钴(例如,co)、钌(例如,ru)、钼(例如,mo)、铱(例如,ir)、钨(例如,w)或一些其他合适的导电材料中的任何材料,且可以通过cvd制程、pvd制程、ald制程、电化学镀(ecp)制程、溅镀制程、旋转涂布制程或一些其他合适的制程中的任何制程来沉积。举例而言,在沉积期间中的温度可以是大约20至400摄氏度或一些其他合适的数值。多个金属线114的厚度可以举例而言为大约10到1000埃或一些其他合适的数值。

132.如图16的剖面图1600所示,在第一金属1502上执行平坦化制程,以进一步定义多个金属线114。还可以在第一蚀刻停止层116上执行平坦化制程,使得第一蚀刻停止层116的上表面与多个金属线114的上表面共面。举例而言,平坦化制程可以是或包括cmp或一些其他合适的平坦化制程。

133.如图17的剖面图1700所示,根据第一蚀刻停止层116(例如,在凹入期间中,第一蚀刻停止层116用作遮罩),使多个金属线114凹入(recessed)。结果是,多个金属线114的上表面低于第一蚀刻停止层116的上表面。举例而言,使第一金属线114a凹入,使得第一金属线114a的上表面低于第一蚀刻停止层116的上表面。

134.在一些实施例中,多个金属线114的上表面在第一蚀刻停止层116的上表面下方(below),并且在凹入之后的第一蚀刻停止层116的下表面上方(above)或者与第一蚀刻停

止层116的下表面齐平(even with)。换句话说,凹入的深度可举例而言,小于或近似等于第一蚀刻停止层116的深度。因为暴露第一ild层112的侧壁可能使第一ild层112容易受到损害,可以使多个金属线114的上表面凹入至高于或者齐平于第一蚀刻停止层116的下表面,使得在金属凹入之后,不暴露及/或未覆盖(not exposed and/or uncovered)第一ild层112的侧壁。

135.举例而言,凹入可以包括湿式蚀刻制程、干式蚀刻制程或一些其他合适的蚀刻制程。举例而言,湿式蚀刻制程可以使用氢氟酸、磷酸、氢氧化钾、四甲基氢氧化铵、硝酸或一些其他合适的湿式蚀刻剂中的任何蚀刻剂。再者,干式蚀刻制程可以举例而言包括icp rie制程、ccp rie制程、远程等离子体蚀刻制程或一些其他合适的制程。举例而言,干式蚀刻制程可以使用甲烷(例如,ch4)、氟甲烷(例如,ch3f)、二氟甲烷(例如,ch2f2)、三氟甲烷(例如,chf3)、八氟环丁烷(例如,c4f8)、六氟-1,3-丁二烯(例如,c4f6)、四氟甲烷(例如,cf4)、氢气(例如,h2)、溴化氢(例如,hbr)、一氧化碳(例如,co)、二氧化碳(例如,co2)、氧气(例如,o2)、三氯化硼(例如,bcl3)、氯气(例如,cl2)、氮气(例如,n2)、氦气(例如,he)、氖气(例如,ne)、氩气(例如,ar)或一些其他合适的气体中的任何气体。举例而言,在干式蚀刻制程期间施加的压力可以是大约0.2到120毫托或一些其他合适的数值。举例而言,在干式蚀刻制程期间施加的温度可以是大约0到100摄氏度或一些其他合适的数值。举例而言,在干式蚀刻制程期间施加的功率可以是大约50到3000瓦。举例而言,在干式蚀刻制程期间施加的偏压可以是大约0至1200伏或一些其他合适的数值。

136.在一些实施例中,凹入导致多个金属线114具有弯曲的上表面(举例而言,参照图5)。这可能是由于沿着多个金属线114的中心比沿着多个金属线114的边缘(edges)更快地使多个金属线114凹入的蚀刻制程。

137.在一些其他实施例中,没有使多个金属线114凹入(举例而言,参照图10)。结果是,多个金属线114的上表面及第一蚀刻停止层116的上表面可以近似共面。

138.如图18的剖面图1800所示,形成第二蚀刻停止层118在第一蚀刻停止层116上方、多个金属线114上方以及介于第一蚀刻停止层116的侧壁之间。举例而言,形成第二蚀刻停止层118在第一蚀刻停止层116上方且在第一金属线114a上方。在一些实施例中,形成第二蚀刻停止层118在第一蚀刻停止层116的上表面及多个金属线114的上表面上。

139.第二蚀刻停止层118可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或其他一些合适的制程中的任何制程,来沉积碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约25至400摄氏度或一些其他合适的数值。此外,第二蚀刻停止层118的厚度可以举例而言,是大约10到800埃或一些其他合适的数值。

140.如图19的剖面图1900所示,形成第二ild层120在第二蚀刻停止层118上方;形成第三蚀刻停止层126在第二ild层120上方;形成第三硬遮罩1902在第三蚀刻停止层126上方;形成第二arc层1904在第三硬遮罩1902上方;并且形成第二光阻遮罩1906在第二arc层1904上方。

141.第二ild层120可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或其

他一些合适的制程中的任何制程,来沉积碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约25至400摄氏度或一些其他合适的数值。此外,第二ild层120的厚度可以举例而言,是大约10到800埃或一些其他合适的数值。

142.第三蚀刻停止层126可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或其他一些合适的制程中的任何制程,来沉积碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、碳氢化硅(例如,sich)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、氧碳氮化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)、氮化铝(例如,aln)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约25至400摄氏度或一些其他合适的数值。此外,第三蚀刻停止层126的厚度可以举例而言,是大约10到800埃或一些其他合适的数值。

143.第三硬遮罩1902可以举例而言通过cvd制程、pvd制程、ald制程、旋转涂布制程或其他一些合适的制程中的任何制程,来沉积氮化钛(例如,tin)、氧化钛(例如,tio)、钨(例如w)、掺杂钨的碳(例如,wdc)、氧化铪(例如,hfo)、氧化锆(例如,zro)、氧化锌(例如,zno)、氧化钛锆(例如,tizro)、碳化硅(例如,sic)、二氧化硅(例如,sio2)、碳氧化硅(例如,sioc)、氮化硅(例如,sin)、碳氮化硅(例如,sicn)、氮氧化硅(例如,sion)、碳氧化硅(例如,siocn)、氧化铝(例如,alo)、氮氧化铝(例如,alon)或其他合适的介电质中的任何材料在基板102上方而形成。在沉积期间中的温度举例而言,可以是大约50至400摄氏度或一些其他合适的数值。此外,第三硬遮罩1902的厚度可以举例而言,是大约30到500埃或一些其他合适的数值。

144.第二arc层1904可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程、或其他一些合适的制程,来沉积一些有机聚合物、一些无机聚合物或一些其他合适的材料在基板102上方而形成。

145.第二光阻遮罩1906可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或一些其他合适的制程来沉积光阻在基板102上方,并随后使光阻显影而形成。

146.如图20的剖面图2000所示,根据第二光阻遮罩(例如,图19的第二光阻遮罩1906),使第三硬遮罩1902图案化。

147.举例而言,图案化可以包括icp rie制程、ccp rie制程或一些其他合适的制程。

148.如图21的剖面图2100所示,形成第三arc层2102在第三蚀刻停止层126上方且在第三硬遮罩1902上方,并且形成第三光阻遮罩2104在第三arc层2102上方。

149.第三arc层2102可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程、或其他一些合适的制程,来沉积一些有机聚合物、一些无机聚合物或一些其他合适的材料在基板102上方而形成。

150.第三光阻遮罩2104可以举例而言,通过cvd制程、pvd制程、ald制程、旋转涂布制程或一些其他合适的制程来沉积光阻在基板102上方,并随后使光阻显影而形成。

151.如图22的剖面图2200所示,根据第三光阻遮罩(例如,图21的第三光阻遮罩2104),使第三蚀刻停止层126及第二ild层120图案化,以形成导孔开口2202在第三蚀刻停止层126

中且在第二ild层120中。举例而言,导孔开口2202直接位于多个金属线114的第一金属线114a上方。通过第三蚀刻停止层126的侧壁及第二ild层120的侧壁定义导孔开口2202。

152.在一些实施例中,在第三光阻遮罩(例如,图21的第三光阻遮罩2104)中的未对准,可能导致导孔开口2202的后续未对准(subsequent misalignment)。举例而言,如图22所示,导孔开口2202可能不与下方的第一金属线114a对齐(举例而言,可能从第一金属线114a横向偏移)。

153.在一些其他实施例中,不会发生第三光阻遮罩(例如,图21的第三光阻遮罩2104)的未对准,因此导孔开口2202可以在下方的第一金属线114a的侧壁之间或与下方的第一金属线114a的侧壁对准(举例而言,参照图6、图7及图8)。

154.举例而言,图案化可以包括干式蚀刻制程或一些其他合适的蚀刻制程。举例而言,图案化可以包括电感耦合等离子体(icp)反应性离子蚀刻(rie)制程、导电耦合等离子体(ccp)rie制程或一些其他合适的制程。举例而言,图案化可以使用甲烷(例如,ch4)、氟甲烷(例如,ch3f)、二氟甲烷(例如,ch2f2)、三氟甲烷(例如,chf3)、八氟环丁烷(例如,c4f8)、六氟-1,3-丁二烯(例如,c4f6)、四氟甲烷(例如,cf4)、氢气(例如,h2)、溴化氢(例如,hbr)、一氧化碳(例如,co)、二氧化碳(例如,co2)、氧气(例如,o2)、三氯化硼(例如,bcl3)、氯气(例如,cl2)、氮气(例如,n2)、氦气(例如,he)、氖气(例如,ne)、氩气(例如,ar)或一些其他合适的气体中的任何气体。举例而言,在图案化期间施加的压力可以是大约0.2到120毫托或一些其他合适的数值。举例而言,在图案化期间施加的温度可以是大约0到100摄氏度或一些其他合适的数值。举例而言,在图案化期间施加的功率可以是大约50到3000瓦。举例而言,在图案化期间施加的偏压可以是大约0至1200伏或一些其他合适的数值。

155.在一些实施例中,导孔开口2202的宽度可以举例而言为大约5至300纳米(nanometers)或一些其他合适的数值。导孔开口2202的高度可以举例而言是大约50到500埃或一些其他合适的数值。介于第二蚀刻停止层118的上表面及第二ild层120的侧壁之间的角度可以举例而言是大约40到90度(degrees)或一些其他合适的数值,其中第二蚀刻停止层118的上表面定义导孔开口2202,且第二ild层120的侧壁定义导孔开口2202。

156.如图23的剖面图2300所示,根据第三硬遮罩1902,使第三蚀刻停止层126及第二ild层120图案化,以形成上导线开口(upper wire opening)2302在第三硬遮罩1902及第二ild层120中。上导线开口2302在导孔开口2202上方,并且通过第三蚀刻停止层126的侧壁、第二ild层120的侧壁及第二ild层120的一或多个下表面来定义。

157.举例而言,图案化可以包括干式蚀刻制程或一些其他合适的蚀刻制程。举例而言,图案化可以包括电感耦合等离子体(icp)反应性离子蚀刻(rie)制程、导电耦合等离子体(ccp)rie制程或一些其他合适的制程。举例而言,图案化可以使用甲烷(例如,ch4)、氟甲烷(例如,ch3f)、二氟甲烷(例如,ch2f2)、三氟甲烷(例如,chf3)、八氟环丁烷(例如,c4f8)、六氟-1,3-丁二烯(例如,c4f6)、四氟甲烷(例如,cf4)、氢气(例如,h2)、溴化氢(例如,hbr)、一氧化碳(例如,co)、二氧化碳(例如,co2)、氧气(例如,o2)、三氯化硼(例如,bcl3)、氯气(例如,cl2)、氮气(例如,n2)、氦气(例如,he)、氖气(例如,ne)、氩气(例如,ar)或一些其他合适的气体中的任何气体。举例而言,在图案化期间施加的压力可以是大约0.2到120毫托或一些其他合适的数值。举例而言,在图案化期间施加的温度可以是大约0到100摄氏度或一些其他合适的数值。举例而言,在图案化期间施加的功率可以是大约50到3000瓦。举例而言,

在图案化期间施加的偏压可以是大约0至1200伏或一些其他合适的数值。

158.在一些实施例中,上导线开口2302的宽度可以举例而言为大约10至300纳米或一些其他合适的数值。上导线开口2302的高度可以举例而言是大约50到500埃或一些其他合适的数值。介于第二ild层120的上表面及第二ild层120的侧壁之间的角度可以举例而言是大约50到90度或一些其他合适的数值,其中第二ild层120的上表面定义上导线开口2302,且第二ild层120的侧壁定义上导线开口2302。

159.虽然图21至图23显示出了在形成上导线开口2302之前形成导孔开口2202,但是将理解的是,在一些替代性实施例中,在形成导孔开口2202之前,可以可选地(alternatively)形成上导线开口2302。

160.如图24的剖面图2400所示,使第二蚀刻停止层118图案化,以使导孔开口2202延伸至第二蚀刻停止层118中并且沿着第一蚀刻停止层116至第一金属线114a的上表面。举例而言,图案化制程使第一金属线114a的上表面未覆盖。通过第二ild层120的侧壁、第二蚀刻停止层118的侧壁以及第一蚀刻停止层116的一或多个侧壁定义导孔开口2202。

161.在一些实施例中,如果导孔开口2202与下方的第一金属线114a未对准,则图案化可延伸穿过第二蚀刻停止层118朝向(toward)第一蚀刻停止层116及下方的第一ild层112。在这些实施例中,图案化可能使第一蚀刻停止层116的上表面未覆盖。然而,相对于第一蚀刻停止层116,图案化制程对第二蚀刻停止层118具有高度选择性(例如,以比第一蚀刻停止层116实质上更快的速率移除第二蚀刻停止层118)。因此,即使在未对准的情况下,第一蚀刻停止层116也可以防止图案化损坏下方的第一ild层112。举例而言,在未对准的情况下,则图案化制程可能如同第一蚀刻停止层116的上表面116d的弯曲形状所反映的形状来改变第一蚀刻停止层116的一部分。然而,由于图案化制程的选择性,图案化制程可能不会延伸穿过第一蚀刻停止层116至下方的第一ild层112。

162.相反地,在一些其他实施例中,如果导孔开口2202没有与下方的第一金属线114a未对准,则图案化可以未覆盖第一金属线114a的整个(entire)上表面(举例而言,参照图6),或者可以不覆盖介于第一金属线114a的侧壁之间的第一金属线114a的上表面的一部分(举例而言,参照图7)。

163.举例而言,图案化可以包括湿式蚀刻制程、干式蚀刻制程或一些其他合适的蚀刻制程。举例而言,所述湿式蚀刻制程可以使用氢氟酸、磷酸、氢氧化钾、四甲基氢氧化铵、硝酸或一些其他合适的湿式蚀刻剂中的任何蚀刻剂。再者,干式蚀刻制程可以举例而言包括icp rie制程、ccp rie制程、远程等离子体蚀刻制程或一些其他合适的制程。举例而言,干式蚀刻制程可以使用甲烷(例如,ch4)、氟甲烷(例如,ch3f)、二氟甲烷(例如,ch2f2)、三氟甲烷(例如,chf3)、八氟环丁烷(例如,c4f8)、六氟-1,3-丁二烯(例如,c4f6)、四氟甲烷(例如,cf4)、氢气(例如,h2)、溴化氢(例如,hbr)、一氧化碳(例如,co)、二氧化碳(例如,co2)、氧气(例如,o2)、三氯化硼(例如,bcl3)、氯气(例如,cl2)、氮气(例如,n2)、氦气(例如,he)、氖气(例如,ne)、氩气(例如,ar)或一些其他合适的气体中的任何气体。举例而言,在干式蚀刻制程期间施加的压力可以是大约0.2到120毫托或一些其他合适的数值。举例而言,在干式蚀刻制程期间施加的温度可以是大约0到100摄氏度或一些其他合适的数值。举例而言,在干式蚀刻制程期间施加的功率可以是大约50到3000瓦。举例而言,在干式蚀刻制程期间施加的偏压可以是大约0至1200伏或一些其他合适的数值。

164.在图案化制程包括湿式蚀刻制程的一些实施例中,由于湿式蚀刻制程具有横向分量(例如,因为具有等向性特性的湿式蚀刻制程),所以第二蚀刻停止层118可以具有弯曲的侧壁(举例而言,参照图8及图9)。

165.再者,在一些实施例中,可以在使第二蚀刻停止层118图案化之后,移除第三硬遮罩1902。举例而言,在使第二蚀刻停止层118图案化之后,可以通过单独的湿式蚀刻制程或一些其他合适的制程移除第三硬遮罩1902。

166.如图25的剖面图2500所示,沉积第二金属2502在基板102上方、在导孔开口2202中且在上导线开口2302中,以形成金属导孔122及额外金属线124在基板102上方。举例而言,金属导孔直接位于第一金属线114a上方。在一些实施例中,金属导孔122与第一金属线114a直接接触并且电性连接到第一金属线114a。

167.举例而言,第二金属2502可以包括钽(例如,ta)、氮化钽(例如,tan)、氮化钛(例如,tin)、铜(例如,cu)、钴(例如,co)、钌(例如,ru)、钼(例如,mo)、铱(例如,ir)、钨(例如,w)或一些其他合适的导电材料中的任何材料,且可以通过cvd制程、pvd制程、ald制程、电化学镀(ecp)制程、溅镀制程、旋转涂布制程或一些其他合适的制程中的任何制程来沉积。举例而言,在沉积期间中的温度可以是大约20至400摄氏度或一些其他合适的数值。金属导孔122及/或额外金属线124的厚度可以举例而言为大约10到1000埃或一些其他合适的数值。

168.如图26的剖面图2600所示,在第二金属2502上执行平坦化制程,以进一步定义额外金属线124。也可以在第三蚀刻停止层126上执行平坦化制程,使得第三蚀刻停止层126的上表面及额外金属线124的上表面共面。举例而言,平坦化制程可以是或包括cmp或一些其他合适的平坦化制程。

169.图27显示出了用于形成集成芯片的方法2700的一些实施例的流程图,所述集成芯片包括第一蚀刻停止层及在第一蚀刻停止层上方的第二蚀刻停止层。虽然方法2700在下文中显示及描述为一系列的步骤或事件,但是应当理解的是,这些步骤或事件的显示顺序不应解释为限制性的。举例而言,可以以不同的顺序发生一些步骤及/或同时发生除了本文显示及/或描述的那些步骤或事件之外的其他步骤或事件。此外,并非所有显示的步骤可能需要用来实施本文描述的一或多个态样或实施例。再者,本文描述的一或多个步骤可以在一或多个单独的步骤及/或阶段中执行。

170.在步骤2702,沿着基板形成多个半导体装置。图11显示出了对应于步骤2702的一些实施例的剖面图1100。

171.在步骤2704,形成第一层间介电(ild)层在基板上方。图12显示出了对应于步骤2704的一些实施例的剖面图1200。

172.在步骤2706,形成第一蚀刻停止层在第一ild层上方。图12显示出了对应于步骤2706的一些实施例的剖面图1200。

173.在步骤2708,使第一蚀刻停止层及第一ild层图案化,以在第一蚀刻停止层及第一ild层中形成第一导线开口。图14显示出了对应于步骤2708的一些实施例的剖面图1400。

174.在步骤2710,形成第一金属线在第一导线开口中。图15及图16显示出了对应于步骤2710的一些实施例的剖面图1500及1600。

175.在步骤2712,使第一金属线凹入,使得第一金属线的上表面低于第一蚀刻停止层的上表面。图17显示出了对应于步骤2712的一些实施例的剖面图1700。

176.在步骤2714,形成第二蚀刻停止层在第一蚀刻停止层上方且在第一金属线上方。图18显示出了对应于步骤2714的一些实施例的剖面图1800。

177.在步骤2716,形成第二ild层在第二蚀刻停止层上方。图19显示出了对应于步骤2716的一些实施例的剖面图1900。

178.在步骤2718,使第二ild层图案化,以在第二ild层中并直接在第一金属线上方形成导孔开口。图21及图22显示出了对应于步骤2718的一些实施例的剖面图2100及2200。

179.在步骤2720,使第二蚀刻停止层图案化,以使导孔开口延伸至第二蚀刻停止层并沿着第一蚀刻停止层延伸到第一金属线的上表面,从而未覆盖第一金属线的上表面。图24显示出了对应于步骤2720的一些实施例的剖面图2400。

180.在步骤2722,形成金属导孔在导孔开口中。图25及图26显示出了对应于步骤2722的一些实施例的剖面图2500及2600。

181.因此,本发明关于一种集成芯片,所述集成芯片包括第一蚀刻停止层及第二蚀刻停止层,以提高集成芯片的可靠性及性能。

182.据此,在一些实施例中,本公开关于一种集成芯片,所述集成芯片包括基板。第一导线(conductive wire)在基板上方的第一介电层内(within)。第一蚀刻停止层在第一介电层上方。第二蚀刻停止层在第一蚀刻停止层上方。导电导孔(conductive via)在位于第二蚀刻停止层上方的第二介电层内。导电导孔延伸穿过(extends through)第二蚀刻停止层并沿着第一蚀刻停止层至第一导线。第二蚀刻停止层的第一下表面在第一蚀刻停止层的上表面上。第二蚀刻停止层的第二下表面在第一导线的上表面上。

183.在一些实施例中,其中第一蚀刻停止层包括第一介电材料,且第二蚀刻停止层包括不同于第一介电材料的第二介电材料。在一些实施例中,其中第二蚀刻停止层的第一侧壁直接位于(directly over)第一蚀刻停止层的上表面上方,且其中第二蚀刻停止层的第二侧壁直接位于第一导线上方,且所述第二侧壁与第一侧壁相对(opposite)。在一些实施例中,其中第二蚀刻停止层在第一蚀刻停止层的第一侧壁上且在与第一侧壁相对的第一蚀刻停止层的第二侧壁上。在一些实施例中,其中第二蚀刻停止层以封闭环形(in a closed loop)围绕(surrounds)导电导孔。在一些实施例中,其中导电通孔在第一蚀刻停止层的第一侧壁上且在与第一侧壁相对的第一蚀刻停止层的第二侧壁上。在一些实施例中,其中第一导线在第一蚀刻停止层的第一侧壁上且在与第一侧壁相对的第一蚀刻停止层的第二侧壁上。在一些实施例中,其中第一导线的上表面低于(below)第一蚀刻停止层的上表面。在一些实施例中,其中导电导孔的上表面在第二介电层的下表面上。

184.在其他实施例中,本公开关于一种集成芯片,所述集成芯片包括基板。第一金属线(metal wire)在基板上方的第一介电层内。第一蚀刻停止层在第一介电层上方。第一蚀刻停止层包括第一介电质。第二蚀刻停止层在第一蚀刻停止层上方。第二蚀刻停止层包括不同于第一介电质的第二介电质。金属导孔(metal via)在第二蚀刻停止层上方的第二介电层内。金属导孔延伸穿过第二蚀刻停止层并沿着第一蚀刻停止层至第一金属线的上表面。第二蚀刻停止层位于第一蚀刻停止层的上表面及侧壁上。

185.在一些实施例中,其中第二蚀刻停止层的下表面低于第一蚀刻停止层的下表面。在一些实施例中,其中第二蚀刻停止层在第一蚀刻停止层的上表面上且在第一金属线的上表面上。在一些实施例中,其中第二蚀刻停止层围绕介于第一蚀刻停止层的侧壁之间的金

属导孔。在一些实施例中,其中第二蚀刻停止层具有第一侧壁及与第一侧壁相对的第二侧壁,其中第一侧壁沿着金属导孔的第一侧(side)延伸,其中第二侧壁沿着金属导孔的第二侧延伸,且其中第一侧壁的高度大于第二侧壁的高度。在一些实施例中,其中第二蚀刻停止层在金属导孔的第一对相对侧壁(pair of opposing sidewalls)上且在金属导孔的第二对相对侧壁上。在一些实施例中,其中金属导孔通过第一蚀刻停止层与第一介电层垂直上地分离(vertically separated)。

186.在又一些实施例中,本公开关于一种用于形成集成芯片的方法。所述方法包括形成第一介电层在基板上方。形成第一蚀刻停止层在第一介电层上方。形成第一硬遮罩在第一蚀刻停止层上方。根据第一硬遮罩,使第一蚀刻停止层及第一介电层图案化,以在第一蚀刻停止层且在第一介电层中形成第一导线开口(wire opening)。通过第一蚀刻停止层的第一对侧壁(pair of sidewalls)及第一介电层的第二对侧壁定义(defined)第一导线开口。沉积第一金属在第一导线开口中,以形成第一金属线。形成第二蚀刻停止层在第一蚀刻停止层上方、第一金属线上方以及介于第一蚀刻停止层的第一对侧壁之间。使第二蚀刻停止层图案化,以直接在第一金属线上方形成导孔开口。沉积第二金属在导孔开口中,以形成金属导孔。

187.在一些实施例中,所述方法更包括在形成第二蚀刻停止层之前,使第一金属线凹入(recessing)至低于第一蚀刻停止层的上表面。在一些实施例中,所述方法更包括在使第二蚀刻停止层图案化之前,形成第二介电层在第二蚀刻停止层上方。在一些实施例中,其中使第二蚀刻停止层图案化,而未覆盖(uncovers)第一金属线的上表面且未覆盖第一蚀刻停止层的上表面。

188.前述内文概述了数个实施例的部件,使得所属技术领域中具有通常知识者可以更佳地了解本公开的态样。所属技术领域中具有通常知识者应可理解的是,他们可轻易地以本公开为基础来设计或修饰其他制程及结构,并以此达到与在本文中介绍的实施例相同的目的及/或达到相同的优点。所属技术领域中具有通常知识者也应理解的是,这些等效的构型并未脱离本公开的精神与范畴,且在不脱离本公开的精神与范畴的情况下,可对本公开进行各种改变、取代或替代。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1