一种低压断路器的一二次回路连接方法与流程

1.本发明涉及断路器技术领域,特别是一种低压断路器的一二次回路连接方法。

背景技术:

2.传统的低压断路器与电操装置通常采用机械安装方式,没有把断路器与电操机构进行功能互补融合。在电机出现异常时,整体设备更换工作时间长,且传统断路器电操装置结构复杂,设备安装所需要的空间较大,无法与断路器进行有效装配,适配性差。

技术实现要素:

3.有鉴于此,本发明的目的是提供一种能够实现断路器的一次导通部分与二次控制部分通过端子排的方式进行连接的方法。

4.本发明采用以下方法来实现:一种低压断路器的一二次回路连接方法,所述方法包括以下步骤:

5.步骤s1、将断路器的一次导通部分和二次控制部分经端子排的方式进行连接;

6.步骤s2、通过断路器上的插座将电源接通至转接板,然后通过转接板实现断路器内部电路的导通;

7.步骤s3、断路器内的主控制器用于接收一次导通部分的信号及反馈,从而实现断路器一次导通部分和二次控制部分的连接关系。

8.进一步的,所述断路器包括基座,所述基座上设置有转接板,所述转接板上设置有插座,所述基座正面上端设置有侧板,所述基座内右侧上下两端均开设有安装孔,所述基座内设置有限位框,所述基座内设置有滑块,且所述滑块设置于所述限位框下方,所述基座后侧面设置有上盖,所述基座上左侧上下两端均开设有将所述基座与所述上盖进行连接的固定孔,所述上盖上设置有手柄。

9.进一步的,所述一次导通部分的电路包括u4芯片、p2插座、p3插座、p1插座和p4插座,所述u4芯片的1号引脚与电阻r19一端连接,所述电阻r19另一端与hp rxd端口连接,所述u4芯片的2号引脚与所述u4芯片的3号引脚串联后与三极管q1的集电极连接,所述三极管q1的发射极接地设置,所述三极管q1的基极与电阻r22一端连接,所述电阻r22另一端与hp txd端口连接设置,所述u4芯片的4号引脚接地设置,所述u4芯片的5号引脚与电容c10一端串联后接地,所述电容c10的另一端与所述u4芯片的8号引脚串联后与vcc m端口连接,所述u4芯片的6号引脚与电阻r14一端连接,所述电阻r14另一端与a端口连接,所述u4芯片的7号引脚与电阻r21一端连接,所述电阻r21另一端与b端口连接;所述p2插座的3号引脚与5号引脚串联后接地,所述p2插座的7号引脚与所述hp rxd端口连接,所述p2插座的11号引脚接地,所述p2插座的12号引脚与电阻r20一端连接,所述电阻r20另一端接地,所述p2插座的6号引脚与hp txd端口连接设置,所述p2插座的4号引脚接地,所述p2插座的1号引脚和所述p2插座的2号引脚串联后与12v端口连接;所述p3插座的1号引脚和2号引脚串联后与n端口连接,所述p3插座的7号引脚与8号引脚串联后与l端口连接;所述p1插座的1号引脚与所述a

端口连接,所述p1插座的2号引脚与b端口连接,所述p1插座的6号引脚与n端口连接;所述p4插座的1号引脚与所述b端口连接,所述p4插座的3号引脚与所述a端口连接,所述p4插座的5号引脚与所述n端口连接,所述p4插座的7号引脚与所述l端口连接。

10.进一步的,所述二次控制部分的电路包括u2芯片、u3芯片、u1芯片、p5插座、p6插座、j10插座、u11芯片、p7插座、p9插座、p10插座、p11插座和j1插座,所述u2芯片的2号引脚与sd/zd端口连接,所述u2芯片的3号引脚与hz端口连接,所述u2芯片的4号引脚与fz端口连接,所述u2芯片的5号引脚经osc in引线与电阻r72一端连接,所述电阻r72与晶振y1并联设置,所述晶振y1一端与电容c41一端连接,所述晶振y1另一端与电容c46一端连接,所述电容c41另一端与所述电容c46另一端均接地设置,所述u2芯片的6号引脚经osc out引线与电阻r72另一端连接,所述u2芯片的7号引脚经reset引线与电容c48一端串联后与电阻r74一端连接,所述电阻r74另一端与vcc-3.3v端口连接,所述电容c48另一端接地,所述u2芯片的8号引脚与sz端口连接,所述u2芯片的9号引脚与n die端口连接,所述u2芯片的10号引脚与sykg端口连接,所述u2芯片的11号引脚与fk端口连接,所述u2芯片的12号引脚与电容c51一端串联后接地,所述u2芯片的13号引脚与电容c51另一端串联后与火线l9一端连接,所述火线l9另一端与vcc-3.3v端口连接,所述电容c51另一端与vdda-3.3v端口连接,所述u2芯片的18号引脚接地,所述u2芯片的19号引脚与vcc-3.3v端口连接,所述u2芯片的20号引脚与mota端口连接,所述u2芯片的21号引脚与motb端口连接,所述u2芯片的22号引脚与led g端口连接,所述u2芯片的23号引脚与led y端口连接,所述u2芯片的24号引脚与led r端口连接,所述u2芯片的25号引脚与u2 tx端口连接,所述u2芯片的26号引脚与u2 rx端口连接,所述u2芯片的30号引脚与电容c9一端连接,所述电容c9另一端接地,所说的u2芯片的31号引脚接地,所述u2芯片的32号引脚与vcc-3.3v端口连接。所述u2芯片的33号引脚与/int rt端口连接,所述u2芯片的34号引脚与spi sck端口连接,所述u2芯片的35号引脚与spi miso端口连接,所述u2芯片的36号引脚与spi mosi端口连接,所述u2芯片的37号引脚与flash cs端口连接,所述u2芯片的38号引脚与wp端口连接,所述u2芯片的39号引脚与bl cog端口连接,所述u2芯片的40号引脚与cs cog端口连接,所述u2芯片的41号引脚与res cog端口连接,所述u2芯片的42号引脚与a0 cog端口连接,所述u2芯片的43号引脚与scl端口连接,所述u2芯片的44号引脚与sda端口连接,所述u2芯片的45号引脚与set端口连接,所述u2芯片的46号引脚与swdio端口连接,所述u2芯片的47号引脚接地,所述u2芯片的48号引脚与vcc-3.3v端口连接,所述u2芯片的49号引脚与swclk端口连接,所述u2芯片的51号引脚与电阻r30一端串联后与p5插座的3号引脚连接,所述u2芯片的52号引脚与电阻r29一端串联后与p5插座的2号引脚连接,所述p5插座的1号引脚接地,所述电阻r29另一端和所述电阻r30另一端串联后与vcc-3.3v端口连接,所述u2芯片的53号引脚与key fz端口连接,所述u2芯片的54号引脚与back端口连接,所述u2芯片的55号引脚与down端口连接,所述u2芯片的56号引脚与up端口连接,所述u2芯片的57号引脚与key hz端口连接,所述u2芯片的58号引脚与s2 int端口连接,所述u2芯片的59号引脚与s4 int端口连接,所述u2芯片的60号引脚与电阻r28一端连接,所述电阻r28另一端与vcc-3.3v端口连接,所述u2芯片的61号引脚与485rx端口连接,所述u2芯片的62号引脚与485tx端口连接,所述u2芯片的63号引脚接地,所述u2芯片的64号引脚与vcc-3.3v端口连接;所述p6插座的1号引脚与s41端口连接,所述p6插座的2号引脚与s21端口连接,所述p6插座的3号引脚接地,所述p6插座的4号引脚与n1端口连

接;所述u3芯片的1号引脚与rs485 rx2端口连接,所述u3芯片的2号引脚与3号引脚串联后与三极管q2的集电极连接,三极管q2的发射极接地,所述三极管q2的基极与电阻r13一端连接,所述电阻r13另一端与u1芯片的6号引脚连接,所述u3芯片的4号引脚接地,所述u3芯片的5号引脚与电容c6一端和电阻r14一端串联,所述电阻r14一端接地,所述u3芯片的6号引脚与电阻r10一端和电阻r7一端连接,所述u3芯片的7号引脚与电阻r14另一端串联后与电阻r11一端连接,所述电阻r11另一端与p12插座的2号引脚连接,所述u3芯片的8号引脚与电容c6另一端串联后与5v端口连接,所述电容c6另一端与电阻r10另一端连接,所述电阻r7另一端与p12插座的1号引脚连接;所述u1芯片的1号引脚与电容c7一端串联后与vcc-3.3v端口连接,所述电容c7另一端接地,所述u1芯片的2号引脚与485rx端口连接,所述u1芯片的3号引脚与485tx端口连接,所述u1芯片的4号引脚接地,所述u1芯片的5号引脚接地,所述u1芯片的7号引脚与电阻r12一端连接,所述电阻r12另一端与rs485 rx2端口连接,所述u1芯片的8号引脚与电容c8一端串联后与5v端口连接所述电容c8另一端接地;所述j10插座的1号引脚与vcc-3.3v端口连接,所述j10插座的2号引脚与swdio端口连接,所述j10插座的3号引脚接地,所述j10插座的4号引脚与swclk端口连接;所述u11芯片的1号引脚与flash cs端口连接,所述u11芯片的2号引脚与spi miso端口连接,所述u11芯片的3号引脚与wp端口连接,所述u11芯片的4号引脚接地,所述u11芯片的5号引脚与spi mosi端口连接,所述u11芯片的6号引脚与spi sck端口连接,所述u11芯片的7号引脚和8号引脚串联后与电容c34一端连接,所述电容c34一端与vcc-3.3v端口连接,所述电容c34另一端接地;所述p9插座的1号引脚与u2 tx端口连接,所述p9插座的2号引脚与u2 rx端口连接,所述p9插座的3号引脚与gnd端口连接,所述p9插座的4号引脚与12v端口连接;所述p10插座的1号引脚和2号引脚串联后与vcc-3.3v端口连接,所述p10插座的3号引脚接地,所述p10插座的4号引脚与set端口连接,所述p10插座的5号引脚与sda端口连接,所述p10插座的6号引脚与scl端口连接,所述p10插座的7号引脚与a0cog端口连接,所述p10插座的8号引脚与res cog端口连接,所述p10插座的9号引脚与cs cog端口连接,所述p10插座的10号引脚与bl cog端口连接;所述p11插座的1号引脚与5v端口连接,所述p11插座的2号引脚接地,所述p11插座的3号引脚与motb端口连接,所述p11插座的4号引脚与mota端口连接,所述p11插座的5号引脚与m-端口连接,所述p11插座的6号引脚与m+端口连接,所述p11插座的7号引脚与vcc-3.3v端口连接,所述p11插座的8号引脚与gnd端口连接,所述p11插座的9号引脚与24v端口连接,所述p11插座的10号引脚与gnd端口连接;所述j1插座的1号引脚与key hz端口连接,所述j1插座的2号引脚与up端口连接,所述j1插座的3号引脚与down端口连接,所述j1插座的4号引脚与back端口连接,所述j1插座的5号引脚与key fz端口连接,所述j1插座的6号引脚与led g端口连接,所述j1插座的7号引脚与led y端口连接,所述j1插座的8号引脚与led r端口连接;所述p7插座的1号引脚与m-端口连接,所述p7插座的2号引脚与m+端口连接,所述p7插座的3号引脚接地,所述p7插座的4号引脚与电阻r24一端连接,所述电阻r24另一端与sz端口连接,所述p7插座的5号引脚与电阻r25一端连接,所述电阻r25另一端sd/zd端口连接,所述p7插座的6号引脚与电阻r26一端连接,所述电阻r26另一端与hz端口连接,所述p7插座的7号引脚与电阻r27一端连接,所述电阻r27另一端与fz端口连接。

11.本发明的有益效果在于:本发明对断路器使用线路上的不同保护需要提供更多选择,多功能一二次回路可以根据线路使用搭配选择,减少浪费,在线路检修上更换节省时

间。

附图说明

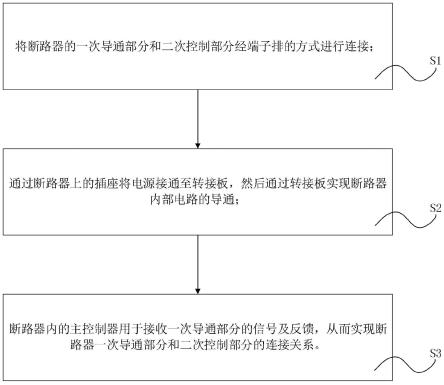

12.图1为本发明方法流程示意图。

13.图2为所述断路器的结构示意图。

14.图3为所述一次导通部分的电路的电路原理图。

15.图4为二次控制部分的电路的电路原理图。

具体实施方式

16.下面结合附图对本发明做进一步说明。

17.请参阅图1所示,本发明提供了一种低压断路器的一二次回路连接方法,所述方法包括以下步骤:

18.步骤s1、将断路器的一次导通部分和二次控制部分经端子排的方式进行连接;

19.步骤s2、通过断路器上的插座将电源接通至转接板,然后通过转接板实现断路器内部电路的导通;

20.步骤s3、断路器内的主控制器用于接收一次导通部分的信号及反馈,从而实现断路器一次导通部分和二次控制部分的连接关系。

21.请参阅图2所示,本发明一实施例中,所述断路器包括基座1,所述基座1上设置有转接板2,所述转接板2上设置有插座21,所述基座1正面上端设置有侧板3,所述基座1内右侧上下两端均开设有安装孔4,所述基座1内设置有限位框5,所述基座1内设置有滑块6,且所述滑块6设置于所述限位框5下方,所述基座1后侧面设置有上盖7,所述基座1上左侧上下两端均开设有将所述基座1与所述上盖7进行连接的固定孔8,所述上盖7上设置有手柄9。断路器是具有热磁式动作保护,转接板2是中转一二次模块之间信号连接作用,提供快速更换与安装,各功能模块切换可以根据需要进行快速安装。

22.请参阅图3所示,本发明一实施例中,所述一次导通部分的电路包括u4芯片、p2插座、p3插座、p1插座和p4插座,所述u4芯片的1号引脚与电阻r19一端连接,所述电阻r19另一端与hp rxd端口连接,所述u4芯片的2号引脚与所述u4芯片的3号引脚串联后与三极管q1的集电极连接,所述三极管q1的发射极接地设置,所述三极管q1的基极与电阻r22一端连接,所述电阻r22另一端与hp txd端口连接设置,所述u4芯片的4号引脚接地设置,所述u4芯片的5号引脚与电容c10一端串联后接地,所述电容c10的另一端与所述u4芯片的8号引脚串联后与vcc m端口连接,所述u4芯片的6号引脚与电阻r14一端连接,所述电阻r14另一端与a端口连接,所述u4芯片的7号引脚与电阻r21一端连接,所述电阻r21另一端与b端口连接;所述p2插座的3号引脚与5号引脚串联后接地,所述p2插座的7号引脚与所述hp rxd端口连接,所述p2插座的11号引脚接地,所述p2插座的12号引脚与电阻r20一端连接,所述电阻r20另一端接地,所述p2插座的6号引脚与hp txd端口连接设置,所述p2插座的4号引脚接地,所述p2插座的1号引脚和所述p2插座的2号引脚串联后与12v端口连接;所述p3插座的1号引脚和2号引脚串联后与n端口连接,所述p3插座的7号引脚与8号引脚串联后与l端口连接;所述p1插座的1号引脚与所述a端口连接,所述p1插座的2号引脚与b端口连接,所述p1插座的6号引脚与n端口连接;所述p4插座的1号引脚与所述b端口连接,所述p4插座的3号引脚与所述a端

口连接,所述p4插座的5号引脚与所述n端口连接,所述p4插座的7号引脚与所述l端口连接。将采集电压与信号汇总板,起信号中转接的作用。

23.请参阅图4所示,本发明一实施例中,所述二次控制部分的电路包括u2芯片、u3芯片、u1芯片、p5插座、p6插座、j10插座、u11芯片、p7插座、p9插座、p10插座、p11插座和j1插座,所述u2芯片的2号引脚与sd/zd端口连接,所述u2芯片的3号引脚与hz端口连接,所述u2芯片的4号引脚与fz端口连接,所述u2芯片的5号引脚经osc in引线与电阻r72一端连接,所述电阻r72与晶振y1并联设置,所述晶振y1一端与电容c41一端连接,所述晶振y1另一端与电容c46一端连接,所述电容c41另一端与所述电容c46另一端均接地设置,所述u2芯片的6号引脚经osc out引线与电阻r72另一端连接,所述u2芯片的7号引脚经reset引线与电容c48一端串联后与电阻r74一端连接,所述电阻r74另一端与vcc-3.3v端口连接,所述电容c48另一端接地,所述u2芯片的8号引脚与sz端口连接,所述u2芯片的9号引脚与n die端口连接,所述u2芯片的10号引脚与sykg端口连接,所述u2芯片的11号引脚与fk端口连接,所述u2芯片的12号引脚与电容c51一端串联后接地,所述u2芯片的13号引脚与电容c51另一端串联后与火线l9一端连接,所述火线l9另一端与vcc-3.3v端口连接,所述电容c51另一端与vdda-3.3v端口连接,所述u2芯片的18号引脚接地,所述u2芯片的19号引脚与vcc-3.3v端口连接,所述u2芯片的20号引脚与mota端口连接,所述u2芯片的21号引脚与motb端口连接,所述u2芯片的22号引脚与led g端口连接,所述u2芯片的23号引脚与led y端口连接,所述u2芯片的24号引脚与led r端口连接,所述u2芯片的25号引脚与u2 tx端口连接,所述u2芯片的26号引脚与u2 rx端口连接,所述u2芯片的30号引脚与电容c9一端连接,所述电容c9另一端接地,所说的u2芯片的31号引脚接地,所述u2芯片的32号引脚与vcc-3.3v端口连接。所述u2芯片的33号引脚与/int rt端口连接,所述u2芯片的34号引脚与spi sck端口连接,所述u2芯片的35号引脚与spi miso端口连接,所述u2芯片的36号引脚与spi mosi端口连接,所述u2芯片的37号引脚与flash cs端口连接,所述u2芯片的38号引脚与wp端口连接,所述u2芯片的39号引脚与bl cog端口连接,所述u2芯片的40号引脚与cs cog端口连接,所述u2芯片的41号引脚与res cog端口连接,所述u2芯片的42号引脚与a0 cog端口连接,所述u2芯片的43号引脚与scl端口连接,所述u2芯片的44号引脚与sda端口连接,所述u2芯片的45号引脚与set端口连接,所述u2芯片的46号引脚与swdio端口连接,所述u2芯片的47号引脚接地,所述u2芯片的48号引脚与vcc-3.3v端口连接,所述u2芯片的49号引脚与swclk端口连接,所述u2芯片的51号引脚与电阻r30一端串联后与p5插座的3号引脚连接,所述u2芯片的52号引脚与电阻r29一端串联后与p5插座的2号引脚连接,所述p5插座的1号引脚接地,所述电阻r29另一端和所述电阻r30另一端串联后与vcc-3.3v端口连接,所述u2芯片的53号引脚与key fz端口连接,所述u2芯片的54号引脚与back端口连接,所述u2芯片的55号引脚与down端口连接,所述u2芯片的56号引脚与up端口连接,所述u2芯片的57号引脚与key hz端口连接,所述u2芯片的58号引脚与s2 int端口连接,所述u2芯片的59号引脚与s4 int端口连接,所述u2芯片的60号引脚与电阻r28一端连接,所述电阻r28另一端与vcc-3.3v端口连接,所述u2芯片的61号引脚与485rx端口连接,所述u2芯片的62号引脚与485tx端口连接,所述u2芯片的63号引脚接地,所述u2芯片的64号引脚与vcc-3.3v端口连接;所述p6插座的1号引脚与s41端口连接,所述p6插座的2号引脚与s21端口连接,所述p6插座的3号引脚接地,所述p6插座的4号引脚与n1端口连接;所述u3芯片的1号引脚与rs485 rx2端口连接,所述u3芯片的

2号引脚与3号引脚串联后与三极管q2的集电极连接,三极管q2的发射极接地,所述三极管q2的基极与电阻r13一端连接,所述电阻r13另一端与u1芯片的6号引脚连接,所述u3芯片的4号引脚接地,所述u3芯片的5号引脚与电容c6一端和电阻r14一端串联,所述电阻r14一端接地,所述u3芯片的6号引脚与电阻r10一端和电阻r7一端连接,所述u3芯片的7号引脚与电阻r14另一端串联后与电阻r11一端连接,所述电阻r11另一端与p12插座的2号引脚连接,所述u3芯片的8号引脚与电容c6另一端串联后与5v端口连接,所述电容c6另一端与电阻r10另一端连接,所述电阻r7另一端与p12插座的1号引脚连接;所述u1芯片的1号引脚与电容c7一端串联后与vcc-3.3v端口连接,所述电容c7另一端接地,所述u1芯片的2号引脚与485rx端口连接,所述u1芯片的3号引脚与485tx端口连接,所述u1芯片的4号引脚接地,所述u1芯片的5号引脚接地,所述u1芯片的7号引脚与电阻r12一端连接,所述电阻r12另一端与rs485 rx2端口连接,所述u1芯片的8号引脚与电容c8一端串联后与5v端口连接所述电容c8另一端接地;所述j10插座的1号引脚与vcc-3.3v端口连接,所述j10插座的2号引脚与swdio端口连接,所述j10插座的3号引脚接地,所述j10插座的4号引脚与swclk端口连接;所述u11芯片的1号引脚与flash cs端口连接,所述u11芯片的2号引脚与spi miso端口连接,所述u11芯片的3号引脚与wp端口连接,所述u11芯片的4号引脚接地,所述u11芯片的5号引脚与spi mosi端口连接,所述u11芯片的6号引脚与spi sck端口连接,所述u11芯片的7号引脚和8号引脚串联后与电容c34一端连接,所述电容c34一端与vcc-3.3v端口连接,所述电容c34另一端接地;所述p9插座的1号引脚与u2 tx端口连接,所述p9插座的2号引脚与u2 rx端口连接,所述p9插座的3号引脚与gnd端口连接,所述p9插座的4号引脚与12v端口连接;所述p10插座的1号引脚和2号引脚串联后与vcc-3.3v端口连接,所述p10插座的3号引脚接地,所述p10插座的4号引脚与set端口连接,所述p10插座的5号引脚与sda端口连接,所述p10插座的6号引脚与scl端口连接,所述p10插座的7号引脚与a0 cog端口连接,所述p10插座的8号引脚与res cog端口连接,所述p10插座的9号引脚与cs cog端口连接,所述p10插座的10号引脚与bl cog端口连接;所述p11插座的1号引脚与5v端口连接,所述p11插座的2号引脚接地,所述p11插座的3号引脚与motb端口连接,所述p11插座的4号引脚与mota端口连接,所述p11插座的5号引脚与m-端口连接,所述p11插座的6号引脚与m+端口连接,所述p11插座的7号引脚与vcc-3.3v端口连接,所述p11插座的8号引脚与gnd端口连接,所述p11插座的9号引脚与24v端口连接,所述p11插座的10号引脚与gnd端口连接;所述j1插座的1号引脚与key hz端口连接,所述j1插座的2号引脚与up端口连接,所述j1插座的3号引脚与down端口连接,所述j1插座的4号引脚与back端口连接,所述j1插座的5号引脚与key fz端口连接,所述j1插座的6号引脚与led g端口连接,所述j1插座的7号引脚与led y端口连接,所述j1插座的8号引脚与led r端口连接;所述p7插座的1号引脚与m-端口连接,所述p7插座的2号引脚与m+端口连接,所述p7插座的3号引脚接地,所述p7插座的4号引脚与电阻r24一端连接,所述电阻r24另一端与sz端口连接,所述p7插座的5号引脚与电阻r25一端连接,所述电阻r25另一端sd/zd端口连接,所述p7插座的6号引脚与电阻r26一端连接,所述电阻r26另一端与hz端口连接,所述p7插座的7号引脚与电阻r27一端连接,所述电阻r27另一端与fz端口连接。使得把采集电压与信号汇总板提供的信号用芯片进行分析处理,经过控制系统的判断下发指令进行工作。

24.以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与

修饰,皆应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1