无源静电放电传感器和用于检测静电放电的方法与流程

无源静电放电传感器和用于检测静电放电的方法

1.优先权要求

2.本技术要求于2021年5月25日提交的法国专利申请no.2105435的优先权,该申请的全部内容在法律允许的最大程度上通过引用结合于此。

技术领域

3.具体实施方式和实施例涉及集成电路,尤其涉及包括静电放电传感器的集成电路。

背景技术:

4.静电放电(esd)可在制造集成电路的步骤期间发生且使集成电路的组件降级。例如,用于等离子体蚀刻的方法可以在集成电路的器件(例如金属氧化物半导体(mos)晶体管)的物理节点上产生电荷。静电放电在装置的物理节点上的累积可在这些节点之间产生电位差,其可在静电放电期间引起存在于所述节点之间的材料的降解(击穿)。

5.这种类型的降解在很大程度上是随机的,并且希望能够检测,标识和量化静电放电现象,例如在测试和表征产品的阶段期间。

6.因此,用于量化集成电路被静电放电损伤的风险的方法,例如根据带电器件模型(cdm),可以包括其中将器件的节点充电到给定电压,然后放电的阶段。根据各个节点的放电动态特性,两个节点之间的电位差可能由于静电放电而产生退化。

7.这里同样希望能够检测,标识和量化静电放电现象。

8.存在对静电放电问题的常规预防解决方案,例如允许经由专用二极管局部地排空静电放电。也就是说,这种类型的预防性和局部解决方案不允许标识和量化静电放电。

9.常规的检测解决方案可以允许标识在测试设备中发生的降级,但是通常不是非常敏感并且具有很少的可能测量。例如,当测试器件是mos晶体管时,可以检测到栅极氧化物的击穿,但是不能单独测量导电区或栅极区的退化。因此,集成电路的组件的特性可以轻微且不可标识的方式个别地偏离,但在整个产品上显著偏离(此偏离通常称为“角效应”),而无需常规解决方案来检测所述偏离。

10.因此,在本领域中需要配备有静电放电传感器的集成电路,该静电放电传感器能够以增加的灵敏度检测各种类型的特性退化和偏差。

技术实现要素:

11.根据一个方面,在这方面提出了一种集成电路,其包括:半导体部件,其包括半导体衬底;互连部件,其包括金属层;以及静电放电传感器,其包括在所述半导体部件中的半导体结构和在所述互连部件中的金属天线网络,所述传感器包括在所述半导体结构中具有电阻性链路或电容性链路或pn结链路的至少一对两个节点;以及天线网络的天线,其具有形状不对称性和/或尺寸不对称性,天线网络的天线分别连接到每对的所述节点。

12.分别连接到每对传感器的两个节点的天线的形状不对称性和尺寸不对称性允许

放大传感器的物理节点上的静电荷的累积的差异,并且因此放大这些节点之间的电势的差异,这可以在静电放电期间产生存在于所述节点之间的材料的劣化。

13.类似地,天线的形状不对称性和尺寸不对称性可以放大对应对的节点的放电动态特性的差异,从而放大在所述节点的放电期间出现的电势的差异,这可以通过静电放电产生存在于所述节点之间的材料的劣化。

14.因此,导致相对弱的静电放电的现象(电荷积累或放电动力学的差异)被放大并且可以通过传感器对的节点之间存在的材料的降解来检测。相对弱的静电放电是可以引起链路特性的偏差而没有可观察到的恶化的静电放电。因此,根据该方面提出的传感器具有增加的灵敏度。

15.此外,传感器的各种可能对的节点之间的各种类型的链路允许具有大量的测量,这可以表示产生静电放电的各种现象。例如,一个节点可以专用于在它们之间具有给定链路(电阻性,电容性,pn结)的单对两个节点,或者相对地,该节点可以属于在它们之间具有不同或不同链路(电阻性,电容性,pn结)的数对两个节点。

16.根据一种实现方式,分别连接到每对节点的天线在大小上具有不对称性,其中它们的表面积的比率大于或等于10。实际上,连接到传感器对的两个节点的两个天线之间的尺寸差异(不对称性)在该对的两个节点上的电荷积累之间引入了基本上成比例的差异。天线的尺寸也影响该对节点的放电动态。

17.根据一种实现方式,分别连接到每对节点的天线在形状上具有不对称性,其中一个天线具有包括分支的耙的形状,所述分支适于穿过对应金属层级中的若干表面单元,而另一个天线具有仅覆盖对应金属层级中的一个表面单元的板的形状。

18.实际上,耙形比板形延伸更大的伸展,这允许在各个区域中比板的局部位置更全面地积累电荷。因此,连接到传感器对的两个节点的两个天线之间的形状差异(不对称性)在此也引入该对的两个节点上的电荷累积之间的差异。

19.根据一个实施方式,集成电路包括多个静电放电传感器,每个传感器的天线网络位于对应的金属层。例如,这允许标识一层金属是否比另一层更可能引起静电放电。

20.根据一个实施方式,半导体结构包括位于半导体衬底前表面上的多晶硅条。

21.根据一个实施方式,所述至少一对传感器包括具有电阻性链路的一对两个节点,多晶硅条在所述对的节点之间形成电阻性链路。

22.根据一个实施方式,电介质层位于多晶硅条和半导体衬底之间,所述至少一对传感器包括具有电容性链路的一对两个节点,多晶硅条、电介质层和半导体衬底的重叠在所述对的节点之间形成电容性链路。

23.根据一个实施方式,半导体结构包括半导体衬底中的至少一个掺杂区。

24.根据一个实施方式,所述至少一个掺杂区包括半金属化合物的表面层,所述至少一对传感器包括具有电阻性链路的一对两个节点,金属化合物的表面层形成所述对的节点之间的电阻性链路。

25.半金属化合物,也称为金属间化合物,是金属材料和半导体材料通过化学键的缔合,例如金属硅化物,通常是铜或钨的硅化物。

26.根据一个实施方式,半导体结构包括半导体衬底中的第一类型的第一掺杂区和半导体衬底中的与第一掺杂区相对的第二类型的第二掺杂区,所述至少一对传感器包括具有

pn结链路的一对两个节点,第一掺杂区和第二掺杂区之间的交界面形成所述对的节点之间的pn结链路。

27.根据一种实现方式,半导体结构包括在半导体衬底和载体衬底之间的掩埋氧化物区域,所述至少一对传感器包括具有电容性链路的一对两个节点,半导体衬底、掩埋氧化物区域和载体衬底的重叠在所述对的节点之间形成电容性链路。

28.这对应于绝缘体上硅(soi)类型的衬底,其中载体衬底(称为“背栅极”)与半导体衬底之间的电容性接口用作一对传感器的节点之间的电容性链路。

29.根据另一方面,提出了一种用于检测静电放电的方法,该方法包括如上定义的集成电路的制造,以及测量步骤,该测量步骤包括所述至少一对节点之间的链路的表征,以及判定步骤,该判定步骤包括所测量的表征与对应的电阻、电容或pn结链路的标称特性之间的比较。

30.根据一个实施例,金属层的制造包括将天线网络暴露于带电等离子体环境。

31.根据一个实施例,该静电放电传感器的制造与该集成电路的其他元件的制造同时进行,并且其中该判定步骤包括,在所测量的表征与对应链路的标称特性之间存在偏差的情况下,基于该偏差以及耦合到该对应对的节点的天线的尺寸不对称性和/或形状不对称性来评估在该集成电路的其他元件中引起的损伤。

附图说明

32.本发明的其他优点和特征将在检查具体实施方式和实施例的详细描述(绝非限制性的)以及附图时显现,在附图中:

33.图1和图2示出了静电放电传感器的示例;

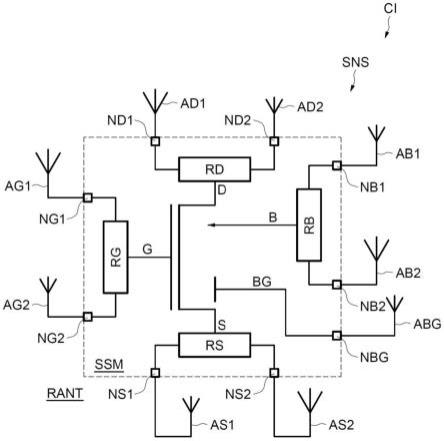

34.图3是可以示意性地示出如图1和2中的传感器的电路的表示;

35.图4至图7示出了静电放电检测器的“单独”对的两个节点之间的链路的示例,以及各个链路的电特性;以及

36.图8示出了用于检测静电放电的方法。

具体实施方式

37.图1和图2示出了属于集成电路c1的静电放电传感器sns的示例。

38.图1对应于在半导体衬底的前表面fa处的传感器sns的俯视图,该传感器sns属于集成电路ci的半导体部件,该集成电路ci被称为并且被标记为前端制程feol。此外,传感器sns的天线网络rant位于与前表面fa的平面平行的平面中,其也在顶视图中示意性地被示出。

39.图2对应于传感器sns的截面图,示出了半导体部件feol和集成电路ci的互连部件,其被称为并且标记为后端制程beol。

40.传感器sns是无源类型的传感器,也就是说,当集成电路被供电和操作时它不旨在起作用,而是旨在经受可能的静电放电,该静电放电可以修改传感器sns的结构。然后观察结构修改以便推导和表征发生在集成电路c1中的静电放电。

41.静电放电传感器sns包括在集成电路的半导体部件feol中制成的半导体结构ssm,以及在互连部件beol的一层或多层金属m1中制成的金属天线rant的网络。

42.半导体结构ssm旨在进行结构修改以检测静电放电,而天线网络rant旨在收集电荷或影响节点的放电动态,以在半导体结构ssm中产生静电放电。

43.在这方面,传感器包括至少一对两个节点nd1,ns1,ng1,nb1,nd2,ns2,ng2,nb2,在半导体结构ssm中具有电阻性链路或电容性链路或pn结链路,天线网络rant的天线ad1,as1,ag1,ab1,ad2,as2,ag2,ab2连接到半导体结构ssm的每个节点。

44.天线网络rant的天线经由传统的接触柱cnt连接到各个节点,穿过位于半导体部件feol和互连部件beol之间的预金属电介质pmd层。半导体衬底的前表面fa被定义为预金属介电层pmd所在的面,也就是说,半导体部件feol的元件所在的面。

45.传感器sns的天线网络rant可以形成在单个金属层级中,例如第一金属层级m1,或者被形成在若干金属层中。

46.金属层m1,m2,m3被金属间电介质层imd1,imd2,imd3垂直隔开。各层金属m2,m3的金属轨可通过垂直穿过金属间介电层imd2,imd3的通孔v23,v34电连接。

47.此外,集成电路ci可以有利地包括如在此描述的多个静电放电传感器sns,并且使得每个传感器的天线网络rant位于对应的金属层级中。这允许利用关于相对于每个金属水平的静电放电的信息,并且因此能够标识静电放电发生的位置。

48.此外,分别连接到每对的所述节点nd1,ns1,ng1,nb1,nd2,ns2,ng2,nb2的天线对ad1,as1,ag1,ab1,ad2,as2,ag2,ab2在它们之间具有形状不对称性和/或尺寸不对称性。

49.形状不对称性和尺寸不对称性允许在产生静电放电的现象中产生不平衡,并且因此放大它们在传感器sns中的结果,以便能够以更高的灵敏度检测它们。

50.例如,对于给定的一对节点,例如节点ng1和ng2,连接到这些节点的天线ag1,ag2在尺寸上具有不对称性,因为它们的表面积的比率大于或等于10。

51.根据另一示例,对于诸如节点nd1和nd2的给定节点对,连接到这些节点的天线ad1,ad2在形状上具有不对称性,其中一个天线ad1具有包括适于穿过金属m1的对应层中的若干表面单元的分支的耙的形状,而另一个天线ad2具有仅覆盖金属m1的对应层中的一个表面单元的板的形状。

52.因此,由板ad2所占据的表面限定的术语“表面单元”具有相对含义,并且不对应于给定或设定的绝对尺寸。

53.一方面,天线的形状不对称性和尺寸不对称性允许在对应对的两个节点的每个节点上累积的电荷量不平衡,并且因此放大由累积导致的这些节点之间的电位差。

54.回想到,电荷的积累尤其可以由在制造互连部件beol的金属m1-m3层级的金属轨期间使用的等离子体环境中的蚀刻步骤引起。

55.另一方面,天线的形状不对称性和尺寸不对称性允许在给定电压下的极化之后使对应对的节点的放电动力学失衡,并且因此放大在所述节点的放电期间产生的电位差。

56.回想到,可以在测试和表征集成电路的阶段期间,特别是根据cdm充电器件模型,提供给定电压下电路节点的极化。

57.如此放大的所述节点之间的这些电位差产生静电放电,其损伤在形成所述节点之间的对应链路的材料中也被放大。

58.因此,传感器sns具有增加的灵敏度,并且特别地能够检测静电放电,该静电放电通常(也就是说没有放大)会导致链路特性的偏差而没有可观察到的恶化。

59.此外,在半导体区域feol中,传感器sns的不同对的节点之间的不同类型的链路允许利用多个测量,这可以表示产生静电放电的不同现象。

60.图1和图2所示的半导体结构ssm是mos(金属氧化物半导体)型结构的有利示例,其允许连接到各个天线的节点的多种组合,在它们之间具有电阻性链路、电容性链路或pn结链路,其特性可以根据所选择的对而变化。

61.实际上,在该示例中,半导体结构ssm相当于mos晶体管,并且包括位于半导体衬底b的前表面fa上的多晶硅g的导电条,以及半导体衬底b中的两个植入区s、d。

62.介电层ox还位于多晶硅条g和半导体衬底b之间,例如像mos晶体管的栅极区和栅极氧化物。

63.半导体衬底b形成第一类型(例如p型)的第一掺杂区,其通常在类似的mos晶体管中称为主体或接地,并且植入区s,d形成与第一类型相对的第二类型(例如n型)的第二掺杂区,其类似于mos晶体管的源极s及漏极d区。

64.此外,在所示的示例中,衬底是绝缘体上硅(soi)类型的,也就是说,其中和其上制造半导体部件feol的元件(例如mos晶体管或传感器sns的半导体结构ssm)的衬底b是相对精细(薄)的半导体层(硅),通过掩埋氧化物区域box与载体衬底sp分离。

65.soi衬底的这个例子特别地允许利用通过在一对的两个节点之间重叠半导体衬底b,掩埋氧化物区box和载体衬底sp而形成的电容性链路。

66.也就是说,传统的衬底,即通常不包括掩埋氧化物区box的晶体硅的体积或块体,完全适合于传感器sns。

67.半导体结构ssm例如可以包括在上述每个区域中形成的两个节点。每个节点例如由将半导体部件feol的所述区域电连接到互连部件beol的第一金属层m1的接触柱cnt实现。

68.因此,传感器sns的半导体结构ssm包括两个节点ng1,ng2,其将被称为“栅极节点”,接触多晶硅g的条。栅极节点ng1,ng2可以有利地布置在条g的对跖(antipodal)位置处,即在使节点ng1,ng2之间的距离最大化的位置处。

69.由于它是导电的,多晶硅条g在两个栅极节点ng1,ng2之间建立电阻性链接。

70.例如,多晶硅g的“条”可以具有从顶部看不是严格的条(即在字面意义上为矩形轮廓)、而是例如具有两个平行分支和垂直分支的h形状的组合物的形状,栅极节点ng1,ng2中的一个节点连接到每个分支。任何其它形状也是可能的。

71.此外,将被称为源极区s和漏极区d的第二掺杂区s,d包括半金属化合物sms,smd的表面层,其通常被称为“硅化”,意味着“自对准硅化物”,通常是诸如铜或钨的金属的硅化物。

72.传感器sns的半导体结构ssm包括与漏极区d接触的两个节点nd1,nd2,这两个节点将被称为“漏极节点”,其可以设置为与彼此相距依据漏极区d中的设计规则所允许的距离的尽量远的位置处。

73.漏极区d的金属化合物smd的表面层在两个漏极节点nd1,nd2之间建立电阻性链接。

74.传感器sns的半导体结构ssm包括与源极区域s接触的两个节点ns1,ns2,这将被称为“源极节点”。

75.在该特定示例中,源节点ns1,ns2不连接到非对称天线,而是连接到称为源天线的同一天线as。因此,在这里描述的传感器sns的体系结构的意义上,该特定示例的源节点ns1,ns2不形成一对节点。也就是说,在这里描述的传感器sns的结构的意义上,一起考虑的源节点ns1,ns2可以形成一对节点中的两个节点中的结合连接到天线的与源天线as具有形状不对称性和/或尺寸不对称性的天线的另一节点的一个节点。

76.例如,源节点ns1,ns2的集合可以与漏节点nd1,nd2之一形成具有pn结链路的节点对的第一节点,源天线as具有形状不对称性和/或尺寸不对称性,天线连接到该对的漏节点ad1,ad2。

77.或者,源节点ns1,ns2可以连接到非对称天线,从而形成具有电阻性链路的一对两个节点。源区s的半金属化合物sms的表面层建立了两个源节点ns1,ns2之间的电阻链接。

78.此外,多晶硅条g、电介质层ox和半导体衬底b的重叠在栅极节点ng1,ng2之一与源极节点ns1,ns2之一或漏极节点nd1,nd2之一之间建立了电容性链路。

79.然而,空间上最接近的栅极节点-源极节点或漏极节点对可能是优选的,以避免将电阻性组件引入到链路中。

80.例如,对ng1-ns1和ng2-nd2对于它们的电容性链路可以是优选的。

81.传感器sns的半导体结构ssm包括与半导体衬底b接触的两个节点nb1,nb2,这将被称为“衬底节点”。

82.多晶硅条g、电介质层ox和半导体衬底b的重叠在栅极节点ng1,ng2中的一个和衬底节点nb1,nb2中的一个之间建立电容性链路。

83.这里同样,可以优选空间上最接近的栅极节点-衬底节点对,即ng1-nb1和ng2-nb2对。

84.尽管未示出这种可能性,但是衬底b的金属化合物表面层可以在两个衬底节点nb1,nb2之间建立电阻性链路。

85.最后,第一掺杂区b(衬底)和第二掺杂区s,d(源极和漏极区)之间的交界面在衬底节点nb1,nb2之一与源极节点ns1,ns2或漏极节点nd1,nd2之一之间建立pn结链路。

86.这里再次优选空间上最接近的节点对,特别是nb1-ns1,nb1-nd1,nb2-ns2,nb2-nd2对。

87.因此,源极节点ns1,ns2和漏极节点nd1,nd2之间具有pn结链路,更确切地说是npn双结。

88.因此,mos型半导体结构ssm的这个例子具有这样的优点,即在它们之间具有电阻性链路或电容性链路或pn结链路的两个节点对的许多可能组合。

89.定义节点对的组合可以根据各种可能性来建立,特别是为了参数化它们之间的电阻、电容和pn结链路的特性。

90.例如,给定节点可以属于在它们之间具有特定链路的单对两个节点;或者,给定节点可属于其间具有第一链路(例如电阻性)的第一对两个节点,并且属于其间具有第二链路(例如电容性)的第二对两个节点,并且甚至进一步属于其间具有第三链路(例如pn结)的第三对两个节点。

91.此外,传感器sns的半导体结构ssm的尺寸可以以参数化所述链路的方式来选择。例如,多晶硅条g的长度lg和宽度wg可以在这方面进行调整,就像两个源极节点ns1,ns2之

间以及两个漏极节点nd1,nd2之间的距离ds一样。

92.例如,在本领域技术人员公知的28nm全耗尽绝缘体上硅(fd-soi)技术中,可以存在28nm和200nm之间的宽度wg,100nm和5μm之间的长度lg,以及100nm和2μm之间的距离ds。

93.图3是电路的表示,其示意性地示出了如上关于图1和图2所述的传感器sns。

94.实际上,静电放电传感器sns包括半导体结构ssm和金属天线网络rant。半导体结构ssm包括通过电介质层与半导体衬底b绝缘的导电栅极区g,以及与衬底b的掺杂类型相对类型的两个掺杂区s,d,其在由导电栅极区g覆盖的部分的任一侧上植入到衬底b中。所述栅极区g和所述衬底b的所述掺杂区s,d中的每个区包括至少两个节点ns1,ns2,nd1,nd2,ng1,ng2,nb1,nb2,在它们之间在对应的区s,d,g,b中具有电阻性链路rs,rd,rg,rb。天线网络rant的天线as1,as2,ad1,ad2,ag1,ag2,ab1,ab2耦合到所述节点,天线ad1,ag2分别耦合到具有形状不对称和/或尺寸不对称的电阻性链路rg的至少一对两个所述节点ng1-ng2,天线ag1,ab1分别耦合到具有形状不对称和/或尺寸不对称的电容性链路的至少一对两个所述节点ng1-nb1,天线ad2,as2分别耦合到具有形状和/或尺寸不对称的pn结链路的至少一对两个所述节点nd2-ns2。

95.在衬底b-box-sp(图2)是soi绝缘体上硅类型的情况下,传感器还可以在所述节点中包括连接到载体衬底sp(图2)的至少一个背栅节点nbg。

96.图4至7示出了静电放电检测器的“单独”对的两个节点之间的链路的示例,以及各个链路的电特性。

97.图4至图6的曲线图400,500,600示出了对应链路对施加到其上的电应力的反应。特别地,曲线400,500和600示出了作为对增加的电压斜坡的反应的流过链路的电流强度。

98.图4示出了在两个节点ns/d1,ns/d2之间由半导体衬底b中形成的掺杂区s/d的表面上的半金属化合物的表面层形成的电阻性链路lrsa1。

99.曲线图400示出了电流(a)相对于链路lrsa1的电压(v)的特性。对于小电压(v)值,电流/电压比基本上是线性的,直到击穿电压,例如略低于2v。

100.超过击穿电压,链路lrsa1的行为不再是线性的并且不遵循简单的电定律,而是可以对应于链路材料的退化现象。特别地,硅化物的迁移导致电阻值的增加,直到基本上6v,其中退化使得连接断开。

101.图5示出了在两个节点ng1,ng2之间由形成在半导体衬底b上的多晶硅导电条g制成的电阻性链路lrpoly。

102.曲线图500表示电流(a)相对于链路lrpoly的电压(v)的特性。

103.这里,电流/电压比对于小电压(v)值基本上是线性的,直到击穿电压,例如基本上为3v。超过击穿电压,链路lrpoly的行为不再是线性的并且不遵循简单的电定律,而是可以对应于链路材料的退化现象。

104.图6示出了通过在衬底b上重叠多晶硅g的导电条和介电层而在两个节点ng,nb之间形成的电容性链路lc。

105.曲线图600示出了电流(a)相对于链路lc的电压(v)的特性。电流强度(a)为零,直到被称为阈值电压的电压,基本上为6v,然后电流泄漏以基本上指数速率通过电介质层,直到击穿电压稍微大于8v。超过击穿电压,氧化物被破坏,并且由于材料的退化现象,电流再次变为零。

106.图7示出了在分别连接到在半导体衬底b中形成的具有相对掺杂的区域的两个节点ns/d,nb之间形成的pn结链路lpn。其中一个区域例如是p型掺杂衬底b,而n型掺杂区域是衬底b中的植入区域s/d。

107.pn结链路lpn对电压斜坡类型(未示出)的电应力的反应将对应于二极管特性,也就是说,在直接极化的情况下,从阈值电压开始指数变化,例如阈值电压基本上位于0.6v。除了击穿电压之外,例如位于1v和1.8v之间,链路lpn的行为不遵循简单的电定律,而是可以对应于链路材料的退化现象。

108.并且,在反向极化的情况下,该特性将对应于零电流响应,或可忽略的泄漏电流,直到称为雪崩的击穿电压通过雪崩效应产生电流,这也可以引起链路lpn的材料中的退化。

109.链路lpn的降级可以导致短路效应,其中泄漏电流大数个数量级(例如相对于在非恶化操作期间大约1na的预期泄漏电流,大约1μa的泄漏电流),或者可选地根据测量的可选电流限制,导致开路效应,即零电流。

110.图8示出了使用上述传感器sns检测静电放电800的方法。

111.在集成电路c1的制造801之后执行检测,包括制造用于集成电路操作的其它元件,以及制造静电放电传感器sns。

112.有利地,静电放电传感器sns的制造801可以与集成电路c1的其他元件的制造801同时进行。

113.特别地,制造801金属层beol可以包括将天线网络rant暴露于带电等离子体环境。暴露于等离子体环境确实能够引起集成电路中由电路节点之间的静电放电引起的损伤。

114.在方法800中,测量步骤802包括对所述至少一对传感器sns的节点之间的链路的表征,判定步骤803,包括测量的表征与对应的电阻,电容或pn结链路的标称特性之间的比较。

115.例如,链路可以例如对应于该对节点之间的电压值的施加,以及该对节点之间流动的电流的测量。

116.例如,通过集成电路ci外部的诸如欧姆表的测量设备来执行表征。

117.例如,在低于击穿电压的电压间隔中,对应链路的标称特性可以由对应于该链路的曲线图400,500,600所表示的行为来定义。

118.例如,如果电阻性链路lrsal的电流-电压测量点不在0v和2v之间的曲线400的线性部分上,则检测到链路lrsal在制造方法期间经历了大于其击穿电压的电位差。

119.例如,如果电阻性链路lrpoly的电流-电压测量点不在0v和v之间的曲线500的线性部分上,则检测到链路lrpoly在制造方法期间经历了大于其击穿电压的静电放电。

120.例如,如果电容性链路lc的电流-电压测量点不在6v的阈值电压和8v的击穿电压之间的曲线600的指数部分上,则检测到链路lc在制造方法期间经历了大于其击穿电压的静电放电。

121.例如,如果pn结链路lpn的电流-电压测量点在正向时具有比阈值电压低几个数量级的泄漏电流(例如在非恶化操作期间相对于大约1na的预期泄漏电流大约为1μa的泄漏电流),而在反向时具有比雪崩电压低的泄漏电流,则检测到链路lpn在制造方法期间已经经历了大于其击穿电压的静电放电。

122.最后,在所测量的特征(802)与对应链路的标称特性之间存在偏差的情况下,该方

法的判定步骤803可以有利地包括对在集成电路ci的其他元件中引起的损伤的评估。

123.实际上,可以基于耦合到对应对的节点的天线的尺寸和集成电路的其它结构的实现来建立模型,这可以评估在集成电路的其它结构中评估在集成电路的其它结构中引起的损伤。

124.实际上,可以量化发生在传感器中的静电放电现象,并从该量化中推导出,同时考虑由各个天线对的尺寸和/或形状的不对称性获得的放大,量化发生在集成电路的其它结构中的静电放电现象。

125.此外,以上关于图4至7描述的每个链路lrsal,lrpoly,lpn,lc可以各自形成静电放电传感器sns的半导体结构ssm。

126.实际上,尽管以上关于图1至3描述的示例具有受益于两个节点对和对应链路对的多种组合的优点,但是仅包括在它们之间具有单个特定链路的一对两个节点的半导体结构ssm完全是可能的。

127.传感器sns的半导体结构ssm也可以由关于图4到7描述的链路lrsal,lrpoly,lpn,lc的任何类型的组合产生,甚至由诸如soi绝缘体上硅类型的衬底中的背栅电容性链路的其它链路产生,而不必导致关于图1到3描述的“完整”示例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1