半导体结构及其制备方法与流程

1.本技术涉及半导体制造技术领域,特别是涉及一种半导体结构及其制备方法。

背景技术:

2.随着半导体存储器件(例如动态随机存取存储器dynamic random access memory,简称dram)变得高度集成,单位单元在半导体衬底上的面积会相应地逐渐缩小,包含在金属氧化物半导体(mos)晶体管中的沟道长度也会逐渐减小,沟道长度的减小易造成短沟道效应的产生。

3.为了维持半导体存储器件的高度集成,当前主流的dram工艺中,存储单元晶体管采用埋入式字线(buried wordline,简称bw)mos可以在一定程度上降低短沟道效应从而减少器件漏电现象。

4.然而,随着存储单元尺寸缩小,bw沟槽尺寸也会随之缩小,进而填入bw沟槽的金属截面积也会减小;这就会导致字线(wordline,简称wl)电阻增高,造成更多功耗,加剧由电阻(r)寄生电容(c)充放电过程引起的信号延迟(简称rc延迟)。

技术实现要素:

5.基于此,有必要针对现有技术中的不足之处,提供一种半导体结构及其制备方法。

6.一方面,本技术提供了一种半导体结构的制备方法,包括:

7.提供衬底;

8.对所述衬底进行第一离子注入工艺,以于所述衬底内形成第一离子注入区域;所述第一离子注入区域从所述衬底的上表面向所述衬底内部延伸;

9.刻蚀所述衬底以形成字线沟槽;所述字线沟槽贯穿所述第一离子注入区域,并延伸至所述第一离子注入区域的下方;所述字线沟槽包括第一部分及与所述第一部分一体连接的第二部分,所述第一部分位于所述第一离子注入区域内,且所述第二部分位于所述第一离子注入区域的下方;

10.在刻蚀所述衬底形成字线沟槽的过程中,对所述第二部分的刻蚀速率大于对所述第一部分的刻蚀速率,以使得所述第二部分的宽度大于所述第一部分的宽度。

11.在其中一个实施例中,在形成所述第一离子注入区域之前,所述半导体结构的制备方法还包括:

12.对所述衬底进行第二离子注入工艺,以于所述衬底内形成第二离子注入区域;所述第二离子注入区域位于所述第一离子注入区域的下方;

13.所述第二离子注入区域与所述第一离子注入区域均为p型,且所述第二离子注入区域的离子浓度小于所述第一离子注入区域的离子浓度。

14.在其中一个实施例中,所述第一离子注入区域内的注入离子及所述第二离子注入区域内的注入离子均包括硼离子。

15.在其中一个实施例中,所述第一离子注入区域为p型;

16.在形成所述第一离子注入区域之前,所述半导体结构的制备方法还包括:

17.对所述衬底进行第二离子注入工艺,以于所述衬底内形成第二离子注入区域;所述第二离子注入区域位于所述第一离子注入区域的下方;

18.所述第二离子注入区域为n型。

19.在其中一个实施例中,所述第一离子注入区域内的注入离子包括硼离子;所述第二离子注入区域内的注入离子包括磷离子。

20.在其中一个实施例中,采用干法刻蚀于所述衬底内形成所述字线沟槽。

21.在其中一个实施例中,在形成所述字线沟槽之后,所述半导体结构的制备方法还包括:

22.对所述衬底进行第三离子注入工艺,以消除所述第一离子注入区域,并于所述衬底内形成第一导电类型的第一掺杂区域;所述第一掺杂区域从所述衬底的上表面向所述衬底内部延伸;对所述衬底进行第四离子注入工艺,以消除所述第二离子注入区域,并于所述衬底内形成第二导电类型的第二掺杂区域;所述第二掺杂区域从所述第一掺杂区域的下表面向下于所述衬底内延伸;所述字线沟槽贯穿所述第一掺杂区域,并延伸至所述第二掺杂区域内;

23.于所述字线沟槽的侧壁及底部形成栅氧化层;

24.于所述栅氧化层的表面形成字线导电层;所述字线导电层的顶部低于所述字线沟槽的顶部。

25.在其中一个实施例中,所述第一导电类型为n型;所述第二导电类型为p型。

26.在其中一个实施例中,于所述栅氧化层的表面形成字线导电层之后,所述半导体结构的制备方法还包括:

27.于所述字线沟槽内形成填充介质层;所述填充介质层位于所述字线导电层的顶部,且至少填充满所述字线沟槽。

28.另一方面,本技术还提供了一种半导体结构,其特征在于,包括:

29.衬底;所述衬底内设有第一离子注入区域;所述第一离子注入区域从所述衬底的上表面向所述衬底内部延伸;

30.字线沟槽;所述字线沟槽贯穿所述第一离子注入区域,并延伸至所述第一离子注入区域的下方;所述字线沟槽包括第一部分及与所述第一部分一体连接的第二部分,所述第一部分位于所述第一离子注入区域内,所述第二部分位于所述第一离子注入区域的下方,且所述第二部分的宽度大于所述第一部分的宽度。

31.在其中一个实施例中,所述衬底内还设有第二离子注入区域,位于所述第一离子注入区域的下方;

32.所述第二离子注入区域与所述第一离子注入区域均为p型,且所述第二离子注入区域的离子浓度小于所述第一离子注入区域的离子浓度。

33.在其中一个实施例中,所述第一离子注入区域内的注入离子及所述第二离子注入区域内的注入离子均包括硼离子。

34.在其中一个实施例中,所述第一离子注入区域为p型;

35.所述衬底内还设有第二离子注入区域,位于所述第一离子注入区域的下方;

36.所述第二离子注入区域为n型。

37.在其中一个实施例中,所述第一离子注入区域内的注入离子包括硼离子;所述第二离子注入区域内的注入离子包括磷离子。

38.在其中一个实施例中,所述第一离子注入区域的深度为100nm~150nm;

39.所述第一离子注入区域的离子浓度为1

×

10

19

cm3~1

×

10

21

cm3。

40.本技术的半导体结构及其制备方法至少具有如下有益效果:

41.本技术提供的半导体结构的制备方法,通过在衬底内形成第一离子注入区,能够在刻蚀衬底形成字线沟槽的过程中,使第二部分的刻蚀速率大于对第一部分的刻蚀速率,从而形成第二部分宽度大于第一部分宽度的字线沟槽;如此,所形成的字线沟槽底部较宽,这样能够增大字线沟槽底部截面积,减小在后续制程中所形成的字线的电阻,避免器件功耗的增加和rc延迟的恶化。

42.本技术提供的半导体结构,具有底部截面积较大的字线沟槽,这样能够减小在后续制程中所形成的字线的电阻,避免器件功耗的增加和rc延迟的恶化。

附图说明

43.为了更清楚地说明本技术实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

44.图1为一种埋入式字线工艺中,通过干法刻蚀形成埋入式字线山形沟槽后所得结构的截面结构示意图;

45.图2为一种埋入式字线工艺中,形成字线结构后所得结构的截面结构示意图;

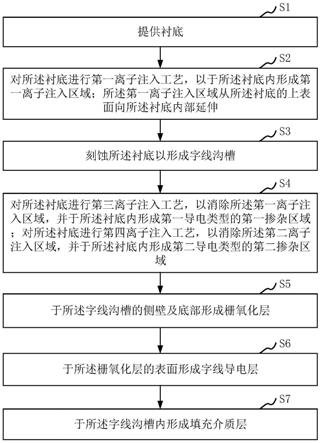

46.图3为本技术其中一个实施例提供的半导体结构的制备方法的流程图;

47.图4为本技术其中一个实施例提供的半导体结构的制备方法中,步骤s1所得结构的截面结构示意图;

48.图5为本技术其中一个实施例提供的半导体结构的制备方法中,步骤s2所得结构的截面结构示意图;

49.图6为本技术其中一个实施例提供的半导体结构的制备方法中,步骤s3所得结构的截面结构示意图;图6亦为本技术其中一个实施例提供的半导体结构的截面结构示意图;

50.图7为本技术其中一个实施例提供的半导体结构的制备方法中,步骤s4所得结构的截面结构示意图;

51.图8为本技术其中一个实施例提供的半导体结构的制备方法中,步骤s5所得结构的截面结构示意图;

52.图9为本技术其中一个实施例提供的半导体结构的制备方法中,步骤s6所得结构的截面结构示意图。

53.附图标记说明:

54.1'、衬底;132'、栅氧化层;133'、金属;134'、填充介质层;1、衬底;13、字线沟槽;132、栅氧化层;133、字线导电层;134、填充介质层;135、第一部分;136、第二部分;141、第一离子注入区域;142、第二离子注入区域;143、第一掺杂区域;144、第二掺杂区域。

具体实施方式

55.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的首选实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本技术的公开内容更加透彻全面。

56.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

57.应当明白,当元件或层被称为“位于

…

上方”其它元件或层时,其可以直接地在其它元件或层上,或者可以存在居间的元件或层。应当明白,尽管可使用术语第一、第二等描述各种元件、部件、区、层、掺杂类型和/或部分,这些元件、部件、区、层、掺杂类型和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层、掺杂类型或部分与另一个元件、部件、区、层、掺杂类型或部分。因此,在不脱离本技术教导之下,下面讨论的第一元件、部件、区、层、掺杂类型或部分可表示为第二元件、部件、区、层或部分;举例来说,可以将第一掺杂区域称为第二掺杂区域,且类似地,可以将第二掺杂区域称为第一掺杂区域;第一掺杂区域与第二掺杂区域为不同的掺杂区域,譬如,第一掺杂区域可以为第一导电类型的掺杂区域且第二掺杂区域可以为第二掺杂区域为第二导电类型的掺杂区域;或第一掺杂区域可以为第二掺杂区域为第二导电类型的掺杂区域且第二掺杂区域可以为第一导电类型的掺杂区域。

58.空间关系术语例如“位于

…

下方”、“位于

…

上方”,在这里可以用于描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,描述为“位于其它元件下方”将取向为在其它元件或特征“上”。因此,示例性术语“位于

…

上方”可包括上和下两个取向。此外,器件也可以包括另外地取向(譬如,旋转90度或其它取向),并且在此使用的空间描述语相应地被解释。

59.在此使用时,单数形式的“一”、“一个”和“所述/该”也可以包括复数形式,除非上下文清楚指出另外的方式。还应明白,当术语“组成”和/或“包括”在该说明书中使用时,可以确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。同时,在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

60.这里参考作为本技术的理想实施例(和中间结构)的示意图的横截面图来描述发明的实施例,这样可以预期由于例如制造技术和/或容差导致的所示形状的变化。因此,本技术的实施例不应当局限于在此所示的区的特定形状,而是包括由于例如制造技术导致的形状偏差。因此,图中显示的区实质上是示意性的,它们的形状并不表示器件的区的实际形状,且并不限定本技术的范围。

61.为了维持半导体存储器件的高度集成,当前主流的dram工艺中,存储单元晶体管采用埋入式字线可以在一定程度上降低短沟道效应从而减少器件漏电现象。

62.在dram埋入式字线工艺中,如图1所示,通常先使用干法刻蚀在衬底1'内形成岛状结构;然后再通过干法刻蚀形成埋入式字线山形沟槽;之后进行热氧化工艺形成栅氧化层132',再由下至上依次沉积金属133'及填充介质层134',以形成字线结构,如图2所示。

63.然而,随着存储单元尺寸缩小,埋入式字线沟槽尺寸也会随之缩小,进而填入埋入式字线沟槽的金属截面积也会减小;这就会导致字线电阻增高,造成更多功耗,加剧rc延迟。

64.针对现有技术中的不足之处,本技术根据一些实施例,提供一种半导体结构的制备方法。

65.请根据图3,在其中一个实施例中,该制备方法可以包括如下步骤:

66.s1:提供衬底。

67.s2:对衬底进行第一离子注入工艺,以于衬底内形成第一离子注入区域;第一离子注入区域从衬底的上表面向衬底内部延伸。

68.s3:刻蚀衬底以形成字线沟槽。

69.其中,步骤s3中形成的字线沟槽应当贯穿第一离子注入区域,并延伸至第一离子注入区域的下方。具体的,字线沟槽可以包括第一部分及与第一部分一体连接的第二部分;第一部分位于第一离子注入区域内,且第二部分位于第一离子注入区域的下方。在刻蚀衬底形成字线沟槽的过程中,对第二部分的刻蚀速率大于对第一部分的刻蚀速率,以使得第二部分的宽度大于第一部分的宽度。

70.上述实施例中的半导体结构的制备方法,通过在衬底内形成第一离子注入区,能够在刻蚀衬底形成字线沟槽的过程中,使第二部分的刻蚀速率大于对第一部分的刻蚀速率,从而形成第二部分宽度大于第一部分宽度的字线沟槽;如此,所形成的字线沟槽底部较宽,这样能够增大字线沟槽底部截面积,减小在后续制程中所形成的字线电阻,因此可以降低器件功耗和减小rc延迟。

71.下面结合图4至图9对本技术涉及的半导体结构的制备方法进行更详细的说明。

72.对于步骤s1,如图4所示,提供衬底1。

73.本技术提供的半导体结构的制备方法,对于衬底1的材质并不做具体限定。作为示例,衬底1可以包括但不限于硅衬底、蓝宝石衬底、玻璃衬底、碳化硅衬底、氮化镓衬底或砷化镓衬底等等中的任意一种或几种;也就是说,衬底1的材质可以包括但不限于硅、蓝宝石、玻璃、碳化硅、氮化镓或砷化镓等等中的任意一种或几种。

74.在一些可能的实施例中,在步骤s1之前,该制备方法还可以包括对初始衬底进行刻蚀,以形成如图4所示的岛状结构的步骤。本技术对于刻蚀初始衬底的方式并不做具体限定;作为示例,可以采用但不仅限于干法刻蚀的方式对初始衬底进行刻蚀。

75.对于步骤s2,请参阅图5,对衬底1进行第一离子注入工艺,以于衬底1内形成第一离子注入区域141。

76.具体的,第一离子注入区域141从衬底1的上表面向衬底1内部延伸。

77.本技术提供的半导体结构的制备方法,对于第一离子注入区域141的深度并不做限定。作为示例,第一离子注入区域141的深度可以为100nm~150nm;譬如,第一离子注入区域141的深度可以为100nm、110nm、120nm、130nm、140nm或150nm等等。

78.在其中一个实施例中,步骤s2形成的第一离子注入区域141深度为130nm。

79.本技术提供的半导体结构的制备方法,对于第一离子注入区域141的离子浓度亦不做限定。作为示例,第一离子注入区域141的离子浓度可以为1

×

10

19

cm3~1

×

10

21

cm3;譬如,第一离子注入区域141的离子浓度可以为1

×

10

19

cm3、1

×

10

20

cm3或1

×

10

21

cm3等等。

80.该制备方法可以在形成第一离子注入区域之前,还形成第二离子注入区域。请继续参阅图5,在其中一个实施例中,形成第二离子注入区域的步骤具体可以包括:对衬底1进行第二离子注入工艺,以于衬底1内形成第二离子注入区域142。

81.具体的,第二离子注入区域142应当位于第一离子注入区域141的下方。

82.作为示例,第一离子注入区域141的下方可以具有本征区域。请继续参阅图5,即图5中的第二离子注入区域142可以替换为本征区域。

83.作为示例,在本技术提供的制备方法中,第一离子注入区域141和第二离子注入区域142还可以均为p型;在此基础上,第二离子注入区域142的离子浓度应当小于第一离子注入区域141的离子浓度。

84.在刻蚀的过程中,空穴会捕获电子,因此对刻蚀产生抑制作用。上述实施例中的半导体结构的制备方法,利用不同空穴浓度区域具有不同刻蚀速率的特性,来形成底部较宽阔的字线沟槽。由于第二离子注入区域142的离子浓度小于第一离子注入区域141的离子浓度,第一离子注入区域141相较于第二离子注入区域142具有更多的空穴,会捕获刻蚀反应过程中产生的电子,对刻蚀产生抑制作用,降低了刻蚀速率;如此,使得第二离子注入区域142的刻蚀速率大于第一离子注入区域141的刻蚀速率,从而在第二离子注入区域142能够形成更宽阔的字线沟槽。

85.在上述实施例中的半导体结构的制备方法中,对于第二离子注入区域142的离子浓度并没有具体限定。第二离子注入区域142的离子浓度可以根据实际需求进行选择,只要第二离子注入区域142的离子浓度小于第一离子注入区域141的离子浓度即可。

86.在上述实施例的基础上,作为示例,在本技术提供的制备方法中,第一离子注入区域141内的注入离子可以包括但不仅限于硼(b)离子。作为示例,第二离子注入区域142内的注入离子可以包括但不仅限于硼离子。

87.作为示例,对衬底1进行第一离子注入工艺以于衬底1内形成第一离子注入区域141的步骤可以采用如下方式进行,比如:使用三氟化硼(bf3)离化产生的硼离子(b+)作为离子源,通过多次不同能量的离子注入工艺,在衬底1内距衬底1上表面100nm~150nm的区域掺入浓度较高的硼元素,形成p型的第一离子注入区域141。

88.作为示例,在本技术提供的制备方法中,第二离子注入区域142还可以为n型;此时,第一离子注入区域141应当为p型。

89.在上述实施例中,由于第二离子注入区域142为n型,是电子浓度远大于空穴浓度的区域,故相较于p型的第一离子注入区域141可以具有更大的刻蚀速率;如此,使得第二离子注入区域142的刻蚀速率大于第一离子注入区域141的刻蚀速率,从而在第二离子注入区域142能够形成更宽阔的字线沟槽。

90.在上述实施例的基础上,作为示例,在本技术提供的制备方法中,第一离子注入区域141内的注入离子可以包括但不仅限于硼离子,第二离子注入区域142内的注入离子可以包括但不仅限于磷(p)离子。

91.对于步骤s3,请参阅图6,刻蚀衬底1以形成字线沟槽13。

92.本技术对于步骤s3中刻蚀衬底1形成字线沟槽13的方式并不做具体限定。作为示例,可以采用但不仅限于干法刻蚀的方式在衬底1内形成字线沟槽13。

93.作为示例,在硅衬底内形成字线沟槽13的步骤可以采用如下方式进行,比如:使用

四氟化碳(cf4)作为刻蚀气体对硅衬底进行干法刻蚀,四氟化碳在电容耦合等离子体(ccp)或电感耦合等离子体(icp)中解离成三氟甲基(cf3)和氟(f)中性基团。这些氟中性基团因电子不饱和而具有较高的反应活性,进而非常容易地与硅衬底发生反应,形成具有挥发特性的四氟化硅(sif4),最终形成字线沟槽13。

94.请结合图7至图9继续参阅图3,在其中一个实施例中,在形成字线沟槽13之后,半导体结构的制备方法还可以包括如下步骤:

95.s4:对衬底1进行第三离子注入工艺,以消除第一离子注入区域141,并于衬底1内形成第一导电类型的第一掺杂区域143;对衬底1进行第四离子注入工艺,以消除第二离子注入区域142,并于衬底1内形成第二导电类型的第二掺杂区域144。

96.如图7所示,第一掺杂区域143从衬底1的上表面向衬底1内部延伸;第二掺杂区域144从第一掺杂区域143的下表面向下于衬底1内延伸。在此基础上,字线沟槽13应当贯穿第一掺杂区域143,并延伸至第二掺杂区域144内。

97.s5:如图8所示,于字线沟槽13的侧壁及底部形成栅氧化层132。

98.s6:如图9所示,于栅氧化层132的表面形成字线导电层133。

99.具体的,字线导电层133的顶部应当低于字线沟槽13的顶部。

100.本技术对于形成栅氧化层132的方式并不做具体限定。作为示例,可以采用但不限于自由基氧化工艺、化学气相沉积工艺(physical vapor deposition,pvd),化学气相沉积工艺(chemical vapor deposition,cvd)、流体化学气相沉积(flowable chemical vapor deposition,fcvd)工艺、高密度等离子沉积(high density plasma,hdp)工艺、等离子体增强沉积工艺或原子层沉积工艺等等中的任意一种方式于字线沟槽13的侧壁及底部形成栅氧化层132。

101.同时,本技术对于栅氧化层132的材质亦不做具体限定。作为示例,栅氧化层132可以包括但不限于二氧化硅层、高k电介质材料层或其他电介质材料层等等中的任意一种或几种;也就是说,栅氧化层132的材质可以包括但不限于二氧化硅、高k电介质材料或其他电介质材料等等中的任意一种或几种。

102.作为示例,可以利用850℃~1050℃的自由基氧化工艺形成栅氧化层132;譬如,可以利用850℃、900℃、950℃、1000℃或1050℃等等自由基氧化工艺形成栅氧化层132。氧中性自由基团(o*)或氢氧中性自由基团(oh*)是氢气(h2)和氧气(o2)反应生成水过程中的中间产物,由于核外电子不饱和因而具有更强的化学活性,自由基可以将较弱的化学键打断,然后形成更强的化学键,因此能够获得更高质量的栅氧化层132。

103.作为示例,在采用自由基氧化工艺形成栅氧化层132的过程中,可以将反应压力控制在20torr以内;譬如,在采用自由基氧化工艺形成栅氧化层132的过程中,可以将反应压力控制为18torr、16torr、14torr、12torr或10torr等等,低压可使气体分子的平均自由程更长。如此,能够获得较长的自由基寿命。

104.本技术对于形成字线导电层133的方式并不做具体限定。作为示例,可以采用但不仅限于化学气相沉积工艺、化学气相沉积工艺、流体化学气相沉积工艺、高密度等离子沉积工艺、等离子体增强沉积工艺或原子层沉积工艺等等中的任意一种或几种于栅氧化层132的表面形成字线导电层133。

105.作为示例,于栅氧化层132的表面形成字线导电层133的步骤,可以采用如下方式

进行,比如:于栅氧化层132的表面形成字线导电材料层;回刻部分字线导电材料层,以形成字线导电层133。

106.同时,本技术对于字线导电层133的材质亦不做具体限定。作为示例,字线导电层133可以包括但不限于氮化钛(tin)层、钛(ti)层、硅化钨(si2w)层或钨(w)层等等中的任意一种或几种;也就是说,字线导电层133的材质可以包括但不限于氮化钛、钛、硅化钨或钨等等中的任意一种或几种。

107.作为示例,于栅氧化层132的表面形成字线导电层133的步骤,还可以采用如下方式进行,比如:使用台阶覆盖较好的化学气相沉积工艺沉积钨金属以字线导电材料层,此过程中反应气体可以包括但不限于硅烷(sih4)和六氟化钨(wf6);然后使用干法刻蚀的方法回刻字线导电材料层,此过程中刻蚀气体可以使用但不仅限于六氟化硫。

108.本技术对于第一掺杂区域143内的离子浓度大小,以及第二掺杂区域144内的离子浓度大小均不做具体限定。作为示例,第一掺杂区域143内的离子浓度大小可以为1

×

10

16

cm3~1

×

10

20

cm3;譬如,第一掺杂区域143内的离子浓度大小可以为1

×

10

16

cm3、1

×

10

17

cm3、1

×

10

18

cm3、1

×

10

19

cm3或1

×

10

20

cm3等等。作为示例,第二掺杂区域144内的离子浓度大小可以为1

×

10

15

cm3~1

×

10

19

cm3;譬如,第二掺杂区域144内的离子浓度大小可以为1

×

10

15

cm3、1

×

10

16

cm3、1

×

10

17

cm3、1

×

10

18

cm3或1

×

10

19

cm3等等。

109.在本技术中,第一导电类型可以为n型;此时第二导电类型应当为p型。

110.作为示例,形成n型的第一掺杂区域143的步骤,可以采用如下方式进行,比如:使用三氟化硼离化产生的硼离子作为离子源,通过离子注入工艺形成掺杂硼离子的n型的第一掺杂区域143。

111.作为示例,形成p型的第二掺杂区域144的步骤,可以采用如下方式进行,比如:使用磷蒸汽离化产生的磷离子(p+)为离子源,通过离子注入工艺在n型的第一掺杂区域143的上方形成掺杂磷离子的p型的第二掺杂区域144。

112.请结合图9继续参阅图3,在其中一个实施例中,在栅氧化层132表面形成字线导电层133之后,半导体结构的制备方法还可以包括如下步骤:

113.s7:于字线沟槽13内形成填充介质层134。

114.具体的,填充介质层134位于字线导电层133的顶部,且至少应当填充满字线沟槽13。

115.本技术对于形成填充介质层134的形式并不做具体限定。作为示例,可以通过但不限于化学气相沉积工艺或化学气相沉积工艺中的任意一种于字线沟槽13内形成填充介质层134。

116.本技术对于填充介质层134的材质亦不做具体限定。作为示例,填充介质层134可以包括但不仅限于二氧化硅层、氮化硅(si3n4)层或氮氧化硅(sion)层等等中的一种或几种;也就是说,填充介质层134的材质可以包括但不仅限于二氧化硅、氮化硅或氮氧化硅等等中的一种或几种。

117.作为示例,于字线沟槽13内形成填充介质层134的步骤可以采用如下方式进行,比如:使用化学气相沉积的方法,利用六氯乙硅烷(si2cl6,简称hcd)或二氯硅烷(sih2cl2,简称dcs)与氨气(nh3)反应,以形成氮化硅作为填充介质材料层;再经过化学机械平坦化(chemical mechanical polishing,简称cmp)形成填充介质层134。

118.应该理解的是,虽然图3的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,图3中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

119.另一方面,本技术还根据一些实施例,提供一种半导体结构。

120.请继续参阅图6,在其中一个实施例中,半导体结构可以包括衬底1及字线沟槽13。

121.其中,衬底1内设有第一离子注入区域141,第一离子注入区域141应当从衬底1的上表面向衬底1内部延伸。字线沟槽13贯穿第一离子注入区域141,并延伸至第一离子注入区域141的下方。

122.具体的,字线沟槽13可以包括第一部分135及与第一部分135一体连接的第二部分136。其中,第一部分135位于第一离子注入区域141内,第二部分136位于第一离子注入区域141的下方,且第二部分136的宽度大于第一部分135的宽度。

123.上述实施例中的半导体结构,具有底部截面积较大的字线沟槽13,这样能够减小在后续制程中所形成的字线的电阻,避免器件功耗的增加和rc延迟的恶化。

124.本技术提供的半导体结构,对于衬底1的材质并不做具体限定。作为示例,衬底1可以包括但不限于硅衬底、蓝宝石衬底、玻璃衬底、碳化硅衬底、氮化镓衬底或砷化镓衬底等等中的任意一种或几种;也就是说,衬底1的材质可以包括但不限于硅、蓝宝石、玻璃、碳化硅、氮化镓或砷化镓等等中的任意一种或几种。

125.本技术提供的半导体结构,对于第一离子注入区域141的深度并不做限定。作为示例,第一离子注入区域141的深度可以为100nm~150nm;譬如,第一离子注入区域141的深度可以为100nm、110nm、120nm、130nm、140nm或150nm等等。

126.在其中一个实施例中,第一离子注入区域141的深度为130nm。

127.本技术提供的半导体结构,对于第一离子注入区域141的离子浓度亦不做限定。作为示例,第一离子注入区域141的离子浓度可以为1

×

10

19

cm3~1

×

10

21

cm3;譬如,第一离子注入区域141的离子浓度可以为1

×

10

19

cm3、1

×

10

20

cm3或1

×

10

21

cm3等等。

128.在其中一个实施例中,衬底1内还可以设有第二离子注入区域142。请继续参阅图6,第二离子注入区域142位于第一离子注入区域141的下方。

129.作为示例,在本技术提供的半导体结构中,第一离子注入区域141和第二离子注入区域142可以均为p型;在此基础上,第二离子注入区域142的离子浓度应当小于第一离子注入区域141的离子浓度。

130.上述实施例中的半导体结构,对于第二离子注入区域142的离子浓度并没有具体限定。第二离子注入区域142的离子浓度可以根据实际需求进行选择,只要第二离子注入区域142的离子浓度小于第一离子注入区域141的离子浓度即可。

131.上述实施例中的半导体结构,能够在后续制程中利用不同空穴浓度区域具有不同刻蚀速率的特性,来形成底部较宽阔的字线沟槽。由于第二离子注入区域142的离子浓度小于第一离子注入区域141的离子浓度,第一离子注入区域141相较于第二离子注入区域142具有更多的空穴,会捕获刻蚀反应过程中产生的电子,对刻蚀产生抑制作用,降低了刻蚀速

率;如此,使得第二离子注入区域142的刻蚀速率大于第一离子注入区域141的刻蚀速率,从而在后续制程中,第二离子注入区域142能够形成更宽阔的字线沟槽。

132.在上述实施例的基础上,作为示例,在本技术提供的半导体结构中,第一离子注入区域141内的注入离子可以包括但不仅限于硼离子。作为示例,在本技术提供的半导体结构中,第二离子注入区域142内的注入离子可以包括但不仅限于硼离子。

133.作为示例,在本技术提供的半导体结构中,第二离子注入区域142还可以为n型;此时,第一离子注入区域141应当为p型。

134.在上述实施例的基础上,作为示例,在本技术提供的半导体结构中,第一离子注入区域141内的注入离子可以包括但不仅限于硼离子,第二离子注入区域142内的注入离子可以包括但不仅限于磷离子。

135.需要注意的是,本技术实施例中的半导体结构的制备方法均可用于制备对应的半导体结构,故而方法实施例与结构实施例之间的技术特征,在不产生冲突的前提下可以相互替换及补充,以使得本领域技术人员能够获悉本技术的技术内容。

136.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

137.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1