一种超高密度连接系统三维扇出型封装结构及其制备方法与流程

1.本发明属于半导体封装技术领域,特别是涉及一种超高密度连接系统三维扇出型封装结构及其制备方法。

背景技术:

2.传统基板如电路板(printed circuit board,pcb)用于电子元器件的支撑体,是电子元器件电气连接的载体。批量应用的多为1-12层,芯片i/o越多基板层数就越多,价格也就高。工艺制程也有一定极限,目前线宽线距只能到20um,正常普遍都是50um以上,当前道芯片制造功能集成越高,未来基板技术将无法满足前道需求,则需要更先进的封装技术将不同种类的高密度芯片集成封装在一起,以构成一个功能强大且体积功耗较小的系统,这已成为半导体芯片先进封装领域的一大挑战。

3.扇出型晶圆级封装(fowlp)由于其输入/输出端口(i/o)较多、集成灵活性较好,已成为目前较为先进的扇出型封装方法之一。目前扇出型晶圆级封装的rdl-first结构是将芯片的表面凸块和金属布线层的表面凸块通过焊料(solder)一一对应焊接固定。但是这种固定方式要求凸块和凸块之间的间距大于15um,甚至大于20um,一旦间距太小则会导致焊料和焊料连接形成焊料桥,引起芯片电性连接错误。

4.因此,提供一种新的超高密度连接系统三维扇出型封装结构及其制备方法是本领域技术人员需要解决的课题。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种超高密度连接系统三维扇出型封装结构及其制备方法,用于解决现有技术中三维扇出型封装结构的芯片连接间距大,密度低等问题。

6.为实现上述目的及其他相关目的,本发明提供一种超高密度连接系统三维扇出型封装结构的制备方法,所述制备方法至少包括:

7.1)提供支撑基底,于所述支撑基底上形成第一绝缘层及位于所述第一绝缘层中的第一金属焊垫;

8.2)于所述第一金属焊垫上形成金属柱;

9.3)提供至少一个第一半导体芯片,所述第一半导体芯片表面形成有第二绝缘层及位于所述第二绝缘层中的第二金属焊垫,并通过混合键合的方式将所述第一金属焊垫和所述第二金属焊垫对应键合、所述第一绝缘层和所述第二绝缘层对应键合;

10.4)形成第一模塑层,所述第一模塑层包覆所述第一半导体芯片和所述金属柱并裸露出所述第一半导体芯片和所述金属柱的表面;

11.5)在所述第一模塑层表面形成第一重新布线层,所述第一重新布线层包括第一介质层及位于所述第一介质层中且与所述金属柱电连的第一布线金属层;

12.6)去除所述支撑基底,裸露出所述第一绝缘层和所述第一金属焊垫表面,于所述

第一绝缘层表面形成第二重新布线层,所述第二重新布线层包括第二介质层及位于所述第二介质层中且与所述第一金属焊垫电连的第二布线金属层,并在所述第二布线金属层表面植球以形成焊球;

13.7)于所述第一重新布线层表面贴装至少一个第二半导体芯片,并形成包覆所述第二半导体芯片的第二模塑层。

14.可选地,所述支撑基底包括玻璃基底、金属基底、半导体基底、聚合物基底及陶瓷基底中的一种。

15.可选地,所述支撑基底和所述第一绝缘层之间还形成有释放层,所述释放层包括胶带层或聚合物层中的一种,通过旋涂工艺将所述分离层涂覆于所述支撑基底表面,然后使用激光固化或紫外光固化或热固化工艺使所述释放层固化成型。

16.可选地,所述第一金属焊垫之间的间距小于10um,所述第二金属焊垫之间的间距小于10um。

17.可选地,所述第一金属焊垫之间的间距小于5um,所述第二金属焊垫之间的间距小于5um。

18.可选地,所述金属柱包括铜柱或者钛柱中的一种,形成所述金属柱的方法包括pvd、cvd、溅射、电镀及化学镀中的一种。

19.可选地,所述第一金属焊垫和所述第二金属焊垫包括铜焊垫。

20.可选地,所述第一模塑层包括环氧基树脂、液态热固性环氧树脂、塑料模塑化合物,形成所述第一模塑层的方法包括压缩成型、转移成型、液封灌封成型、真空层压及旋涂中的一种;所述第二模塑层包括环氧基树脂、液态热固性环氧树脂、塑料模塑化合物,形成所述第二模塑层的方法包括压缩成型、转移成型、液封灌封成型、真空层压及旋涂中的一种。

21.可选地,所述第一布线金属层的材质包括铜、铝、钛金属中的一种,形成所述第一布线金属层的方法包括pvd、cvd、溅射、电镀及化学镀中的一种,所述第一布线金属层包括单层或者多层结构;所述第二布线金属层的材质包括铜、铝、钛金属中的一种,形成所述第二布线金属层的方法包括pvd、cvd、溅射、电镀及化学镀中的一种,所述第二布线金属层包括单层或者多层结构。

22.本发明还提供一种超高密度连接系统三维扇出型封装结构,所述封装结构至少包括:

23.第一绝缘层和第一金属焊垫,所述第一金属焊垫位于所述第一绝缘层中;

24.金属柱,形成于所述第一金属焊垫上;

25.至少一个第一半导体芯片;

26.第二绝缘层和第二金属焊垫,形成于所述第一半导体芯片表面,所述第二金属焊垫位于所述第二绝缘层中,所述第二金属焊垫和所述第一金属焊垫对应键合、所述第二绝缘层和所述第一绝缘层对应键合;

27.第一模塑层,包覆所述第一半导体芯片和所述金属柱并裸露出所述第一半导体芯片和所述金属柱的表面;

28.第一重新布线层,形成于所述第一模塑层表面,所述第一重新布线层包括第一介质层及位于所述第一介质层中且与所述金属柱电连的第一布线金属层;

29.第二半导体芯片,贴装于所述第一重新布线层表面;

30.第二模塑层,包覆所述第二半导体芯片;

31.第二重新布线层,位于所述第一绝缘层远离所述第一半导体芯片的表面,所述第二重新布线层包括第二介质层及位于所述第二介质层中且与所述第一金属焊垫电连的第二布线金属层;

32.焊球,形成于所述第二布线金属层表面。

33.可选地,所述第一金属焊垫之间的间距小于10um,所述第二金属焊垫之间的间距小于10um。

34.可选地,所述第一金属焊垫之间的间距小于5um,所述第二金属焊垫之间的间距小于5um。

35.如上所述,本发明的超高密度连接系统三维扇出型封装结构及其制备方法,具有以下有益效果:本发明的超高密度连接系统三维扇出型封装结构使用rdlfirst(芯片后装)制程,第一金属焊垫和第二金属焊垫之间为非焊接界面,可以实现10um甚至5um以下的间距键合,远小于传统焊接间距(大于20um),从而增加i/o封装数量,完成高密度高集成度的器件封装。另外,本发明的超高密度连接系统三维扇出型封装结构可以同时整合毫米波天线/电容/电感/电晶体/gpu/pmu/ddr/闪存/滤波器等各种电子芯片和元器件,实现高性能系统级封装,灵活性更高且具有广泛的相容性。

附图说明

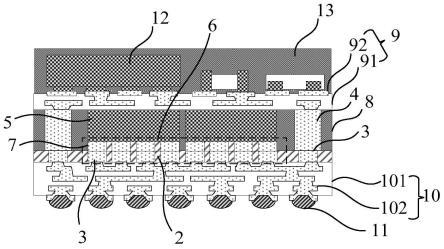

36.图1~图9为本发明超高密度连接系统三维扇出型封装结构的制备方法各个步骤呈现的示意图。其中,图9为本发明超高密度连接系统三维扇出型封装结构示意图。

37.元件标号说明

38.1支撑基底

39.2绝缘层

40.3第一金属焊垫

41.4金属柱

42.5第一半导体芯片

43.6第二绝缘层

44.7第二金属焊垫

45.8第一模塑层

46.9第一重新布线层

47.91第一介质层

48.92第一布线金属层

49.10第二重新布线层

50.101第二介质层

51.102第二布线金属层

52.11焊球

53.12第二半导体芯片

54.13第二模塑层

具体实施方式

55.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

56.请参阅附图。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

57.如图1~图9所示,本发明提供一种超高密度连接系统三维扇出型封装结构的制备方法,所述制备方法至少包括以下步骤:

58.如图1所示,提供支撑基底1,于所述支撑基底1上形成第一绝缘层2及位于所述第一绝缘层2中的第一金属焊垫3。

59.作为示例,所述支撑基底1包括玻璃基底、金属基底、半导体基底、聚合物基底及陶瓷基底中的一种。本实施例中,所述支撑基底1选择半导体基底,如硅晶圆。所述支撑基底1的形状可以为圆形、方形或其他任意所需形状,本实施例通过所述支撑基底1来防止后续制备过程中半导体芯片发生破裂、翘曲、断裂等问题。

60.进一步地,所述支撑基底1和所述第一绝缘层2之间还形成有释放层(未予以图示),所述释放层用于后续分离支撑基底1和封装结构。所述释放层包括胶带层或聚合物层中的一种,通过旋涂工艺将所述释放层涂覆于所述支撑基底1表面,然后使用激光固化或紫外光固化或热固化工艺使所述释放层固化成型。

61.作为示例,所述第一金属焊垫3之间的间距小于10um。进一步地,所述第一金属焊垫3之间的间距小于5um。在一实施例中,所述第一金属焊垫3之间的间距为3um。在另一实施例中,所述第一金属焊垫3之间的间距为4um。

62.作为示例,所述第一金属焊垫3包括但不限于铜焊垫。所述第一金属焊垫3和所述第一绝缘层2的表面齐平,利于后续第一半导体芯片5混合键合工艺的实施。

63.如图2所示,于所述第一金属焊垫3上形成金属柱4。

64.具体地,本实施例中,是两侧的所述第一金属焊垫3上形成金属柱4。

65.作为示例,所述金属柱4包括但不限于铜柱或者钛柱中的一种,形成所述金属柱4的方法包括但不限于pvd、cvd、溅射、电镀及化学镀中的一种。在一实施例中,可以先采用pvd工艺形成金属铜层,再在金属铜层上形成光刻胶,图案化所述光刻胶并进行金属铜层的刻蚀,最后在两侧的所述第一金属焊垫3上形成金属柱4,去除光刻胶。

66.如图3所示,提供至少一个第一半导体芯片5,所述第一半导体芯片5表面形成有第二绝缘层6及位于所述第二绝缘层6中的第二金属焊垫7,并通过混合键合(hybrid bonding)的方式将所述第一金属焊垫3和所述第二金属焊垫7对应键合、所述第一绝缘层2和所述第二绝缘层6对应键合。

67.具体地,如图3所示虚线部分,是中间的所述第一金属焊垫3和所述第二金属焊垫7对应键合。

68.作为示例,所述第一半导体芯片5可以为主晶片,包括但不限于射频芯片等。

69.作为示例,所述第二金属焊垫7之间的间距小于10um。进一步地,所述第二金属焊垫7之间的间距小于5um。在一实施例中,所述第二金属焊垫7之间的间距为3um。在另一实施例中,所述第二金属焊垫7之间的间距为4um。

70.作为示例,所述第二金属焊垫7包括但不限于铜焊垫。

71.如图3所示虚线部分,本发明通过混合键合的方式将所述第一金属焊垫3和所述第二金属焊垫7对应键合、所述第一绝缘层2和所述第二绝缘层6对应键合。所述混合键合是晶圆键合界面既有金属又有绝缘物质的一种键合方式,晶圆间能够不使用粘接媒介物(如焊料),依靠原子键结合在一起,极大改善芯片性能,节省面积,降低成本,实现小间距金属焊垫间的键合固定,避免传统焊接工艺容易出现相邻金属焊垫间焊料桥连导致短接的问题,提高半导体芯片的集成密度。

72.如图4和图5所示,形成第一模塑层8,所述第一模塑层8包覆所述第一半导体芯片5和所述金属柱4并裸露出所述第一半导体芯片5和所述金属柱4的表面。

73.作为示例,所述第一模塑层8包括环氧基树脂、液态热固性环氧树脂、塑料模塑化合物,形成所述第一模塑层8的方法包括压缩成型、转移成型、液封灌封成型、真空层压及旋涂中的一种。形成的所述第一模塑层8如图4所示,之后采用包括但不限于研磨法进行平坦化处理,以使所述所述第一半导体芯片5和所述金属柱4的表面与第一模塑层8的表面相平齐,得到如图5所示的结构。

74.如图6所示,在所述第一模塑层8表面形成第一重新布线层9,所述第一重新布线层9包括第一介质层91及位于所述第一介质层91中且与所述金属柱4电连的第一布线金属层92。

75.作为示例,所述第一介质层91的材料包括环氧树脂、硅胶、pi、pbo、bcb、氧化硅、磷硅玻璃及含氟玻璃中的一种。

76.作为示例,所述第一布线金属层92的材质包括铜、铝、钛金属中的一种,形成所述第一布线金属层92的方法包括pvd、cvd、溅射、电镀及化学镀中的一种,所述第一布线金属层92包括单层或者多层结构。

77.如图7所示,去除所述支撑基底1,裸露出所述第一绝缘层2和所述第一金属焊垫3表面,如图8所示,于所述第一绝缘层2表面形成第二重新布线层10,所述第二重新布线层10包括第二介质层101及位于所述第二介质层101中且与所述第一金属焊垫3电连的第二布线金属层102,并在所述第二布线金属层102表面植球以形成焊球11。

78.作为示例,去除所述支撑基底1的步骤包括但不限于通过对所述支撑基底1表面释放层进行曝光或者加热来实现分离。

79.需要说明的是,去除所述支撑基底1后,将获得的结构倒置,以使裸露的所述第一绝缘层2和所述第一金属焊垫3表面朝上,便于后续工艺的实施。

80.作为示例,所述第二介质层101的材料包括环氧树脂、硅胶、pi、pbo、bcb、氧化硅、磷硅玻璃及含氟玻璃中的一种。

81.作为示例,所述第二布线金属层102的材质包括铜、铝、钛金属中的一种,形成所述第二布线金属层102的方法包括pvd、cvd、溅射、电镀及化学镀中的一种,所述第二布线金属层102包括单层或者多层结构。

82.所述焊球11的材质包括但不限于铜或者镍。所述第二布线金属层102表面可以仅

仅形成有焊球11,也可以先形成金属支柱(未予以图示),再形成焊球11,在此不限。

83.如图9所示,于所述第一重新布线层9表面贴装至少一个第二半导体芯片12,并形成包覆所述第二半导体芯片12的第二模塑层13。

84.需要说明的是,此步骤可以先将上一步骤获得的结构进行翻转,以使所述第一重新布线层9朝上,利于进行所述第二半导体芯片12的贴装工艺。

85.作为示例,所述第二半导体芯片12可以是ddr(双倍速率同步动态随机存储器)及闪存,也可以采用gpu(图形处理器)、pmu(电源管理单元)、毫米波天线、电晶体及滤波器等各种器件。另外,第二半导体芯片12还可以包括电容、电阻和电感等被动元件。

86.作为示例,所述第二模塑层13包括环氧基树脂、液态热固性环氧树脂、塑料模塑化合物,形成所述第二模塑层13的方法包括压缩成型、转移成型、液封灌封成型、真空层压及旋涂中的一种。

87.本发明还提供一种超高密度连接系统三维扇出型封装结构,可以由上述制备方法制备获得,关于所述超高密度连接系统三维扇出型封装结构制备方法、材质、及有益效果等,此处不再赘述。

88.如图9所示,所述封装结构至少包括:

89.第一绝缘层2和第一金属焊垫3,所述第一金属焊垫3位于所述第一绝缘层2中;

90.金属柱4,形成于所述第一金属焊垫3上;

91.至少一个第一半导体芯片5;

92.第二绝缘层6和第二金属焊垫7,形成于所述第一半导体芯片5表面,所述第二金属焊垫7位于所述第二绝缘层6中,所述第二金属焊垫7和所述第一金属焊垫3对应键合、所述第二绝缘层6和所述第一绝缘层2对应键合;

93.第一模塑层8,包覆所述第一半导体芯片5和所述金属柱4并裸露出所述第一半导体芯片5和所述金属柱4的表面;

94.第一重新布线层9,形成于所述第一模塑层8表面,所述第一重新布线层9包括第一介质层91及位于所述第一介质层91中且与所述金属柱4电连的第一布线金属层92;

95.第二半导体芯片12,贴装于所述第一重新布线层9表面;

96.第二模塑层13,包覆所述第二半导体芯片12;

97.第二重新布线层10,位于所述第一绝缘层2远离所述第一半导体芯片5的表面,所述第二重新布线层10包括第二介质层101及位于所述第二介质层101中且与所述第一金属焊垫3电连的第二布线金属层102;

98.焊球11,形成于所述第二布线金属层102表面。

99.作为示例,所述第一金属焊垫3之间的间距小于10um,所述第二金属焊垫7之间的间距小于10um。

100.进一步地,所述第一金属焊垫3之间的间距小于5um,所述第二金属焊垫7之间的间距小于5um。

101.综上所述,本发明提供一种超高密度连接系统三维扇出型封装结构及其制备方法,所述超高密度连接系统三维扇出型封装结构使用rdl first制程,第一金属焊垫和第二金属焊垫之间为非焊接界面,可以实现10um甚至5um以下的间距键合,远小于传统焊接间距(大于20um),从而增加i/o封装数量,完成高密度高集成度的器件封装。另外,本发明的超高

密度连接系统三维扇出型封装结构可以同时整合毫米波天线/电容/电感/电晶体/gpu/pmu/ddr/闪存/滤波器等各种电子芯片和元器件,实现高性能系统级封装,灵活性更高且具有广泛的相容性。

102.所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

103.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1