制备金属-半导体范德华接触的方法、电子器件、电极阵列

本发明涉及半导体器件制备领域,尤其是通用热解制备晶圆级金属-半导体范德华接触。

背景技术:

1、以过渡金属硫族化合物(tmd)为代表的二维(2d)半导体,作为一种具有原子薄厚度和表面无悬挂键的夹层结构,在晶体管的电子学应用中引起了广泛关注。迄今为止,许多2d半导体丰富而有趣的物理特性已被验证。与传统体材料相比,2d半导体的载流子可以限制在单层沟道空间内,有效降低表面电荷散射,同时仍保持较高的载流子迁移率。此外,在器件沟道不断微缩条件下,2d场效应晶体管(fet)对短沟道效应具有很强的免疫力,显著降低了器件静态功耗,弥补了硅基器件的不足。因此,2d半导体为最终体厚度缩放提供了巨大的潜力,这对于进一步扩展摩尔定律至关重要。然而,在2d半导体的超薄和精细的晶格结构上实现高质量金属接触仍然是一项关键挑战。传统硅微电子的金属化过程(例如,热/电子束蒸镀、磁控溅射、化学气相沉积和电子束光刻)通常是基于金属前驱体蒸发的“高能量”制造工艺集成的。这些侵略性方法不一定与2d半导体兼容,因为它们通常涉及热金属原子或团簇轰击接触区域,通过金属原子和2d半导体之间的动能转移或结构缺陷引起的间隙状态而导致实质性损坏。因此,通常在金属-2d接触界面上观测到很强的费米能级钉扎效,这种效应具有很强的捕获电子或空穴的能力,导致具有不可控制的肖特基势垒高度(sbh)和较大的接触电阻(rc),这对2d半导体(异质结)的新物理研究构成了重要的技术挑战。

2、为了避免2d半导体在金属化过程中的遭到损坏并保留其接触区域的固有特性,研究者们已经投入了大量精力来开发“低能量”范德华(vdw)集成方法。在这种方法中,金属电极和2d半导体的接触区域是通过最弱的vdw力相互作用,因此可以保持界面的完整性而不产生共价键或离子键的化学无序结构。例如,通过在mos2表面直接蒸发熔点只有157℃的铟(in)金属,这种低熔点的金属通过“低能量”与2d半导体接触而不会破坏表面,并很好地保留单层mos2的本征特性。在mos2和3d金属之间形成原子级干净的vdw接触,并有0.24nm间距的vdw间隙。因此,高性能的单层mos2晶体管表现出约3kωμm的低接触电阻。用同样的方法,将熔化温度为271℃的半金属铋(bi)直接蒸发到单层mos2可以实现费米能级钉扎效应最小化,实现接触势垒可忽略不计,最低接触电阻为0.12kωμm,这超低电阻数值接近国际器件和系统路线图(irds)。然而,这些“低能量”蒸发接触过程仅适用于特定金属(如in或bi),由于熔化温度低,它们的热稳定性可能需要进一步评估。

3、此外,还可以通过转移预制金属电极实现“低能量”vdw接触。通过在2d半导体表面机械层压平坦的金属薄膜,可以避免传统的“高能量”光刻和金属化工艺。因此,可以很好地保留2d半导体的固有物理特性,从而产生接近肖特基-莫特极限的理想金属-2d界面和高度可调的肖特基势垒。然而,这种方法依赖于从预沉积衬底上机械剥离金属,目前只有少数弱粘附力金属(例如,ag、au、pd、pt)可以成功剥离并转移到2d半导体上。对于工业生产线中使用的常见金属(例如,al、w、ni、co、mo、ti、ta),它们对预沉积衬底表现出高粘附力,不能转移到2d半导体形成vdw接触。因此,不同功函数的3d金属和2d半导体之间通用的vdw集成技术尚未成功开发,这对vdw接触和高性能2d晶体管的实际应用构成了严重限制。

技术实现思路

1、本发明所要解决的技术问题是克服当下vdw接触技术存在的限制,提供一种通用的热解制备金属-半导体范德华接触以及采用该方法制备的电子器件与电极阵列。

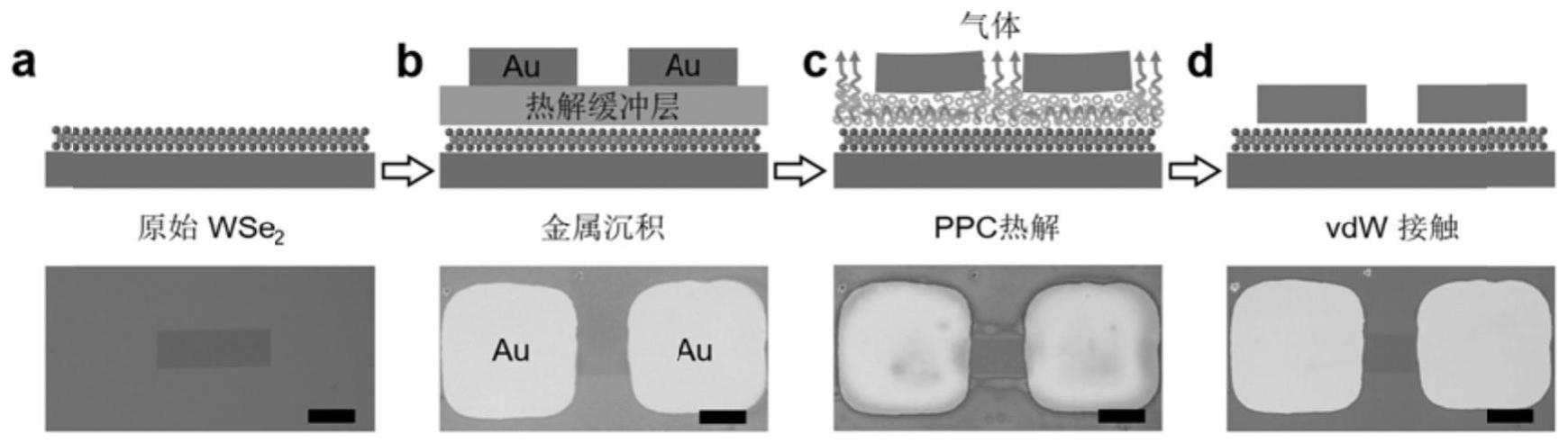

2、本发明所采用的技术方案如下:一种热解制备金属-半导体范德华接触的方法,包括以下步骤:

3、1)配置热解有机缓冲层前驱体溶液;

4、2)将所述热解有机缓冲层前驱体溶液旋涂于半导体表面并烘干形成热解有机缓冲层薄膜;

5、3)在所述热解有机缓冲层薄膜上蒸镀金属形成电极;

6、4)加热退火分解所述热解缓冲层薄膜。

7、进一步,所述金属熔点要高于所述热解有机缓冲层薄膜的分解温度。

8、进一步,所述热解有缓冲层为聚碳酸乙烯酯pec,或聚碳酸丙烯酯ppc,或超支化聚合物hb560中的一种。

9、进一步,所述聚碳酸乙烯酯pec分解温度为250℃,所述聚碳酸丙烯酯ppc分解温度为300℃,超支化聚合物hb560分解温度为600℃。

10、进一步,所述烘干温度为:80-120℃,烘干时间为:1-3分钟,所述蒸镀速率0.02-0.03nm/s。

11、进一步,所述加热退火过程为:由室温逐渐升温到所述热解有机缓冲层薄膜的分解温度,升温速率要小于60℃/min;若温度过快,则会造成电极移动影响电极与半导体层的接触区域;加热退火以去除热解有机缓冲层薄膜,电极就会以弱的相互作用力层压到半导体上,从而实现干净而平整的金属-半导体vdw接触。

12、进一步,所述金属为ag,al,ti,cr,ni,cu,co,au或pd等。

13、进一步,所述半导体为mos2、ws2、mote2、si、ge、gaas、igzo、钙钛矿等。

14、另一方面,本发明还包括一种电子器件,采用所述制备金属-半导体范德华接触的方法所制备的电子器件。

15、另一方面,本发明还包括一种电极阵列,采用所述制备金属-半导体范德华接触的方法所制备的电极阵列。

16、本发明所使用的热解有机缓冲层由于其独特的性能对实现vdw接触至关重要。它可以在热解的温度下分解成气体而不涉及任何溶液或残留物。因此其已广泛成熟应用于工业领域,包括包装、机械、建筑、能源、医疗和微电子应用。

17、本发明的有益效果如下:

18、(1)本发明是通过旋涂热解聚合物薄膜作为缓冲层,通过旋涂在半导体材料上可以有效地保护了在热/电子束蒸镀金属化过程“高能量”的原子或团簇对材料的破坏。这种工业兼容的聚合物缓冲层可以通过简单的退火过程能快速干净除去,上层的金属薄膜就紧密地层压在半导体上形成干净而原子级平整的界面。

19、(2)本发明在加热条件下把缓冲层完全分解成气体流走而不留下任何溶液或残留物。因此可以蒸镀不同功函数的金属,其中包括ag、al、ti、cr、ni、cu、co、au、pd等多种工业兼容金属,这些金属都实现了与半导体形成干净和原子级平整的vdw接触。由于使用了相同的沟道材料,vdw接触器件展现出更好的电学性能归因于vdw接触可以优化接触面质量,可以减小费米能级钉扎效应和降低接触电阻。

20、(3)本发明通过旋涂有机聚合物溶液烘干形成缓冲层,可以避免对半导体层的影响,比如层状半导体mos2材料有丰富的s空位,如果采用某些无机材料沉积在其上时,容易形成合金,从而影响材料的本征特性,而且后续蒸发过程无机材料与金属电极容易形成合金,影响电极的导电效果。

21、(4)有机聚合物干分解后不会与半导体材料或者电极发生反应,半导体材料可以保持固有属性。同时电极表现出干净平整,不会褶皱和产生气泡,尤其是在晶圆级衬底上制备。

22、(5)本发明展示的vdw集成技术不仅局限于2d半导体(例如wse2、mos2、ws2、mote2),而且可以很好地扩展到块状半导体(例如,si、ge、gaas、igzo、钙钛矿),这些半导体以前受到高能金属化过程和不明确的金属-半导体接触(如钙钛矿、氧化物半导体)的困扰。因此vdw集成技术为实现超高效自旋注入、高性能磁隧道器件、超导隧道器件、或各种量子干涉器件等提供一条有效方法。

23、(6)本发明展示vdw接触的晶体管的电学性能明显有很大的提高,展示了高度可调的肖特基势垒。例如,与传统的直接蒸镀接触相比,vdw接触晶体管的阈值电压(vth)随接触金属的功函数可调,以及au电极vdw接触的wse2晶体管的载流子迁移率达到31.4cm2v-1s-1,而直接蒸镀接触的器件迁移率只有10.5cm2v-1s-1。

- 还没有人留言评论。精彩留言会获得点赞!