半导体结构的制作方法及半导体结构与流程

本公开涉及半导体,尤其涉及一种半导体结构的制作方法及半导体结构。

背景技术:

1、随着技术的进步,dram(动态随机存取存储器,dynamic random access memory)向高速度,高集成密度,低功耗方向发展,dram器件结构尺寸越来越小,尤其是在线宽较低的半导体器件制造过程中,栅极结构的材质、形貌、尺寸以及电性能等各方面有了更高的要求。

2、目前的制造流程通常需要多次的湿法清洗来获得所需的栅极结构,而在清洗过程中栅极结构易发生剥离,从而影响栅极结构的电性能。

技术实现思路

1、以下是对本公开详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开提供一种半导体结构的制作方法及半导体结构。

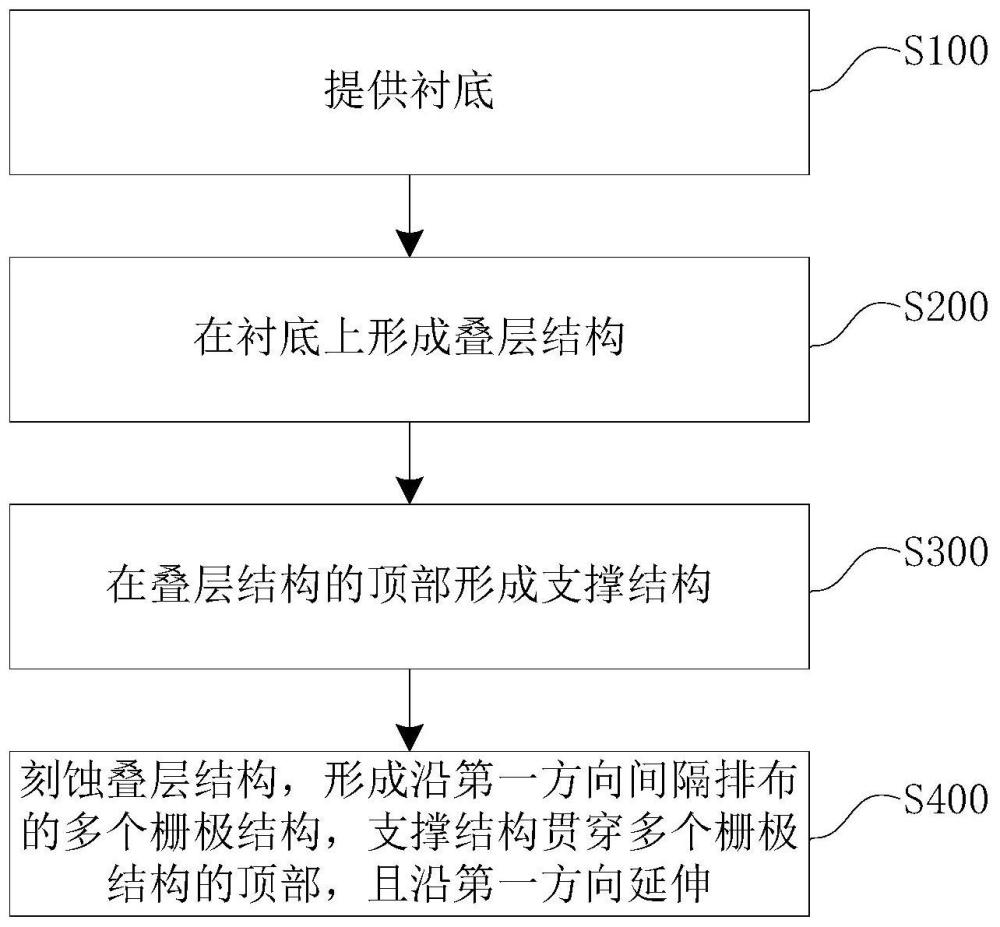

3、本公开的第一方面,提供一种半导体结构的制作方法,所述半导体结构的制作方法包括:

4、提供衬底;

5、在所述衬底上形成叠层结构;

6、在所述叠层结构的顶部形成支撑结构;

7、刻蚀所述叠层结构,形成沿第一方向间隔排布的多个栅极结构,所述支撑结构贯穿所述多个栅极结构的顶部,且沿所述第一方向延伸。

8、在一些实施例中,在所述衬底上形成所述叠层结构,包括:

9、形成栅介电材料层覆盖所述衬底的顶面;

10、形成栅导电材料层覆盖所述栅介电材料层的顶面;

11、形成绝缘材料盖层覆盖所述栅导电材料层的顶面;

12、所述栅介电材料层、所述栅导电材料层和所述绝缘材料盖层共同构成所述叠层结构。

13、在一些实施例中,形成所述栅导电材料层覆盖所述栅介电材料层的顶面,包括:

14、形成第一导电材料层覆盖所述栅介电材料层的顶面;

15、形成阻挡材料层覆盖所述第一导电材料层的顶面;

16、形成第二导电材料层覆盖所述阻挡材料层;

17、所述第一导电材料层、所述阻挡材料层和所述第二导电材料层共同构成所述栅导电材料层。

18、在一些实施例中,在所述叠层结构的顶部形成所述支撑结构,包括:

19、在所述绝缘材料盖层上形成支撑材料层;

20、在所述支撑材料层上形成第一掩膜层;

21、在所述第一掩膜层上形成图形化的第一光刻胶层,所述第一光刻胶层包括沿所述第一方向延伸的第一预设图案;

22、基于所述第一光刻胶层,图案化所述第一掩膜层以将所述第一预设图案转移至所述第一掩膜层中;

23、以图案化后的所述第一掩膜层为掩膜,刻蚀所述支撑材料层,得到所述支撑结构。

24、在一些实施例中,在所述叠层结构的顶部形成所述支撑结构,包括:

25、在所述叠层结构上形成第二掩膜层;

26、在所述第二掩膜层上形成图形化的第二光刻胶层,所述第二光刻胶层包括沿所述第一方向延伸的第二预设图案;

27、基于所述第二光刻胶层,图案化所述第二掩膜层以将所述第二预设图案转移至所述第二掩膜层中;

28、以图案化后的所述第二掩膜层为掩膜,刻蚀所述绝缘材料盖层,得到第一沟槽;

29、在所述第一沟槽中填充支撑材料层,以形成所述支撑结构。

30、在一些实施例中,在形成所述支撑结构之后,且在刻蚀所述叠层结构之前,还包括:

31、在所述叠层结构上形成补充材料层;

32、其中,所述补充材料层与所述支撑结构邻接,所述补充材料层的顶面与所述支撑结构的顶面平齐;或,所述补充材料层包覆所述支撑结构。

33、在一些实施例中,刻蚀所述叠层结构,形成沿所述第一方向间隔排布的多个所述栅极结构,所述支撑结构贯穿所述多个栅极结构的顶部,且沿所述第一方向延伸,包括:

34、在所述支撑结构上和所述叠层结构上形成第三掩膜层;

35、在所述第三掩膜层上形成图形化的第三光刻胶层,所述第三光刻胶层包括沿所述第一方向间隔排布的第三预设图案;

36、基于所述第三光刻胶层,图案化所述第三掩膜层以将所述第三预设图案转移至所述第三掩膜层中;

37、以图案化后的所述第三掩膜层为掩膜,刻蚀所述叠层结构,得到沿所述第一方向间隔排布的多个所述栅极结构,且保留所述支撑结构于所述栅极结构的顶部。

38、在一些实施例中,在以图案化后的所述第三掩膜层为掩膜,刻蚀所述叠层结构的步骤中,

39、所述支撑结构与所述叠层结构的刻蚀选择比小于1:10。

40、本公开的第二方面,提供一种半导体结构,所述半导体结构包括:

41、衬底;

42、多个栅极结构,位于所述衬底上,且沿第一方向间隔排布;

43、支撑结构,贯穿所述多个栅极结构的顶部,且沿所述第一方向延伸。

44、在一些实施例中,所述栅极结构包括:

45、栅介电层,位于所述衬底上;

46、栅导电层,位于所述栅介电层上;

47、以及,绝缘盖层,位于所述栅导电层上。

48、在一些实施例中,所述栅导电层包括:

49、第一导电层,位于所述栅介电层上;

50、阻挡层,位于所述第一导电层上;

51、第二导电层,位于所述阻挡层上。

52、在一些实施例中,所述支撑结构贯穿所述绝缘盖层的顶部。

53、在一些实施例中,所述栅极结构还包括:补充层,位于所述绝缘盖层上;

54、所述支撑结构贯穿所述补充层;

55、所述补充层的顶面与所述支撑结构的顶面平齐。

56、在一些实施例中,在第二方向上的宽度为2nm-10nm;

57、其中,所述第二方向垂直于所述第一方向,且平行于所述衬底。

58、在一些实施例中,所述支撑结构的材料包括氮化碳硅。

59、在一些实施例中,所述多个栅极结构形成至少一个栅极组,每个所述栅极组包括两个所述栅极结构,两个所述栅极结构形成环形结构。

60、在一些实施例中,所述支撑结构贯穿2-6个所述栅极组的顶部。

61、本公开实施例所提供的半导体结构的制作方法及半导体结构中,首先在叠层结构上形成支撑结构,然后通过刻蚀叠层结构得到沿第一方向排布的多个栅极结构,并使得支撑结构沿第一方向延伸并贯穿多个栅极结构的顶部,通过设置支撑结构,能够有效提高栅极结构的深宽比,进而提高半导体结构的电性能,通过支撑结构将多个栅极结构形成可靠支撑和连接,能够有效避免栅极结构在清洗等过程中剥离,保证产品良率。

62、在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:

1.一种半导体结构的制作方法,其特征在于,所述半导体结构的制作方法包括:

2.根据权利要求1所述的半导体结构的制作方法,其特征在于,在所述衬底上形成所述叠层结构,包括:

3.根据权利要求2所述的半导体结构的制作方法,其特征在于,形成所述栅导电材料层覆盖所述栅介电材料层的顶面,包括:

4.根据权利要求2所述的半导体结构的制作方法,其特征在于,在所述叠层结构的顶部形成所述支撑结构,包括:

5.根据权利要求2所述的半导体结构的制作方法,其特征在于,在所述叠层结构的顶部形成所述支撑结构,包括:

6.根据权利要求4所述的半导体结构的制作方法,其特征在于,在形成所述支撑结构之后,且在刻蚀所述叠层结构之前,还包括:

7.根据权利要求5或6所述的半导体结构的制作方法,其特征在于,刻蚀所述叠层结构,形成沿所述第一方向间隔排布的多个所述栅极结构,所述支撑结构贯穿所述多个栅极结构的顶部,且沿所述第一方向延伸,包括:

8.根据权利要求7所述的半导体结构的制作方法,其特征在于,在以图案化后的所述第三掩膜层为掩膜,刻蚀所述叠层结构的步骤中,

9.一种半导体结构,其特征在于,所述半导体结构包括:

10.根据权利要求9所述的半导体结构,其特征在于,所述栅极结构包括:

11.根据权利要求10所述的半导体结构,其特征在于,所述栅导电层包括:

12.根据权利要求10所述的半导体结构,其特征在于,所述支撑结构贯穿所述绝缘盖层的顶部。

13.根据权利要求10所述的半导体结构,其特征在于,所述栅极结构还包括:补充层,位于所述绝缘盖层上;

14.根据权利要求9所述的半导体结构,其特征在于,在第二方向上的宽度为2nm-10nm;

15.根据权利要求9所述的半导体结构,其特征在于,所述支撑结构的材料包括氮化碳硅。

16.根据权利要求9所述的半导体结构,其特征在于,所述多个栅极结构形成至少一个栅极组,每个所述栅极组包括两个所述栅极结构,两个所述栅极结构形成环形结构。

17.根据权利要求16所述的半导体结构,其特征在于,所述支撑结构贯穿2-6个所述栅极组的顶部。

技术总结

本公开提供一种半导体结构的制作方法及半导体结构,半导体结构的制作方法包括:提供衬底;在衬底上形成叠层结构;在叠层结构的顶部形成支撑结构;刻蚀叠层结构,形成沿第一方向间隔排布的多个栅极结构,支撑结构贯穿多个栅极结构的顶部,且沿第一方向延伸。首先在叠层结构上形成支撑结构,然后通过刻蚀叠层结构得到沿第一方向排布的多个栅极结构,并使得支撑结构沿第一方向延伸并贯穿多个栅极结构的顶部,通过设置支撑结构,能够有效提高栅极结构的深宽比,进而提高半导体结构的电性能,通过支撑结构将多个栅极结构形成可靠支撑和连接,能够有效避免栅极结构在清洗等过程中剥离,保证产品良率。

技术研发人员:崔兆培,宋影

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/5

- 还没有人留言评论。精彩留言会获得点赞!