一种低暗电流图像传感器像素结构的制作方法

1.本发明涉及一种cmos图像传感器,尤其涉及一种低暗电流图像传感器像素结构。

背景技术:

2.cmos图像传感器大量应用于便携式数码相机、手机、智能汽车、安防以及医疗领域。在这些应用中多数需要宽动态范围、高速和高灵敏度等先进性能。

3.如图1所示,图像传感器像素由半导体基体中的光电二极管(pd)、传输晶体管(tx)、浮动扩散节点(fd)、复位晶体管(reset)、源跟随器晶体管(sf)、行选通晶体管(select)、电源(vdd)以及pixel输出(vout)组成。多个光电二极管,以及各个晶体管之间需要采用sti(shallow trench isolation)隔离结构或反向pn结隔离结构,达到降低各个器件电路之间的漏电流和串扰(cross talk)。

4.使用sti(shallow trench isolation)隔离结构隔离邻近的光电二极管时,在sti沟槽蚀刻过程中,会对硅造成损伤,形成的缺陷会产生较高的暗电流,降低图像传感器的动态范围。

5.使用部分sti(partial shallow trench isolation),邻近的光电二极管间使用反向pn结隔离结构,可以减少sti沟槽蚀刻的区域。但部分sti隔离结构会在光电二极管和其他晶体管之间形成高应力区域。

6.如图5所示,当高应力区域中存在例如离子注入或是硅本身的mismatch所带来晶格缺陷,会形成位错缺陷,而连续的高应力区域会形成更多的位错缺陷,产生较高的暗电流,降低图像传感器的动态范围。

7.有鉴于此,特提出本发明。

技术实现要素:

8.本发明的目的是提供了一种低暗电流图像传感器像素结构,以解决现有技术中存在的上述技术问题。

9.本发明的目的是通过以下技术方案实现的:

10.本发明的低暗电流图像传感器像素结构,包括置于半导体基体中的光电二极管101、传输晶体管102、浮动扩散节点103、复位晶体管104、源跟随器晶体管106、行选通晶体管107、电源105以及pixel输出108;

11.所述光电二极管有多个,在邻近的光电二极管之间采用反向pn结隔离301,并且在光电二极管之间加入梯形浅槽隔离205,使应力集中在光电二极管四个角落形成钝角结构中。

12.与现有技术相比,本发明所提供的低暗电流图像传感器像素结构,通过降低sti蚀刻所产生的应力,降低光电二极管周围应力,减少光电二极管的位错缺陷。

附图说明

13.图1为cmos图像传感器4管有源像素(4t-aps)电路图

14.101:光电二极管(pd)

15.102:传输栅晶体管(tx)

16.103:浮置扩散节点(fd)

17.104:复位晶体管(reset)

18.105:电源(vdd)

19.106:源跟随器晶体管(sf)

20.107:行选通晶体管(sel)

21.108:pixel输出(vout)

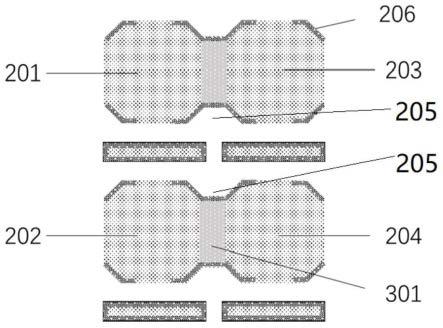

22.图2为浅槽隔离光电二极管应力分布图

23.201:光电二极管1(pd1)

24.202:光电二极管2(pd2)

25.203:光电二极管3(pd3)

26.204:光电二极管4(pd4)

27.205:浅槽隔离(sti)

28.206:高应力区域

29.图3为反向pn结隔离光电二极管应力分布图

30.201:光电二极管1(pd1)

31.202:光电二极管2(pd2)

32.203:光电二极管3(pd3)

33.204:光电二极管4(pd4)

34.206:高应力区域

35.301:反向pn结隔离

36.图4为本实施例光电二极管应力分布图

37.201:光电二极管1(pd1)

38.202:光电二极管2(pd2)

39.203:光电二极管3(pd3)

40.204:光电二极管4(pd4)

41.206:高应力区域

42.301:反向pn结隔离

43.图5为位错缺陷示意图;(a)连续高应力区域,(b)非连续高应力区域;

44.206:高应力区域

45.501:硅衬底

46.502:晶格缺陷

47.503:低应力区域

48.504:位错缺陷(dislocation defect)

49.图6为浅槽隔离蚀刻遮蔽层示意图;(a)传统工艺浅槽隔离蚀刻遮蔽层,(b)本实施例工艺浅槽隔离蚀刻遮蔽层;

50.501硅衬底

51.601.缓冲氧化层(oxide)

52.602高应力硬掩模层(high stress hard mask)

53.603缓冲多晶硅层(poly silicon)

54.604低应力硬掩模层(low stress hard mask);

55.图7为浅槽隔离蚀刻剖面示意图;(a)传统工艺浅槽隔离蚀刻剖面图,(b)本实施例浅槽隔离蚀刻剖面图;

56.205浅槽隔离(sti);

57.501硅衬底

58.601.缓冲氧化层(oxide)

59.602高应力硬掩模层(high stress hard mask)

60.603缓冲多晶硅层(poly silicon)

61.604低应力硬掩模层(low stress hard mask)

具体实施方式

62.下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述;显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例,这并不构成对本发明的限制。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明的保护范围。

63.首先对本文中可能使用的术语进行如下说明:

64.术语“和/或”是表示两者任一或两者同时均可实现,例如,x和/或y表示既包括“x”或“y”的情况也包括“x和y”的三种情况。

65.术语“包括”、“包含”、“含有”、“具有”或其它类似语义的描述,应被解释为非排它性的包括。例如:包括某技术特征要素(如原料、组分、成分、载体、剂型、材料、尺寸、零件、部件、机构、装置、步骤、工序、方法、反应条件、加工条件、参数、算法、信号、数据、产品或制品等),应被解释为不仅包括明确列出的某技术特征要素,还可以包括未明确列出的本领域公知的其它技术特征要素。

66.术语“由

……

组成”表示排除任何未明确列出的技术特征要素。若将该术语用于权利要求中,则该术语将使权利要求成为封闭式,使其不包含除明确列出的技术特征要素以外的技术特征要素,但与其相关的常规杂质除外。如果该术语只是出现在权利要求的某子句中,那么其仅限定在该子句中明确列出的要素,其他子句中所记载的要素并不被排除在整体权利要求之外。

67.除另有明确的规定或限定外,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如:可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本文中的具体含义。

68.术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”、“顺时针”、“逆时针”等指示的方位或位

置关系为基于附图所示的方位或位置关系,仅是为了便于描述和简化描述,而不是明示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本文的限制。

69.本发明实施例中未作详细描述的内容属于本领域专业技术人员公知的现有技术。本发明实施例中未注明具体条件者,按照本领域常规条件或制造商建议的条件进行。本发明实施例中所用试剂或仪器未注明生产厂商者,均为可以通过市售购买获得的常规产品。

70.本发明的低暗电流图像传感器像素结构,包括置于半导体基体中的光电二极管101、传输晶体管102、浮动扩散节点103、复位晶体管104、源跟随器晶体管106、行选通晶体管107、电源105以及pixel输出108;

71.所述光电二极管有多个,在邻近的光电二极管之间采用反向pn结隔离301,并且在光电二极管之间加入梯形浅槽隔离205,使应力集中在光电二极管四个角落形成钝角结构中。

72.在邻近的光电二极管之间的隔离结构中,中部采用反向pn结隔离301,两端采用梯形浅槽隔离205,两端的梯形浅槽隔离205使光电二极管的四个角落形成钝角结构。

73.在浅槽隔离蚀刻的过程中使用硬掩膜层工艺,硬掩膜层为化学气相沉积的氮化硅薄膜,包括依次覆盖在硅衬底501上的缓冲氧化层601、缓冲多晶硅层603和低应力硬掩模层604。

74.所述低应力硬掩模层604沉积过程中,通过调整反应气体的比例使dsc和nh3的比例为5比1,得到低应力氮化硅薄膜,其应力为200mpa。

75.所述缓冲氧化层601的厚度为11nm,所述缓冲多晶硅层603的厚度为50nm,所述低应力硬掩模层604的厚度为75nm。

76.综上可见,本发明实施例的低暗电流图像传感器像素结构,通过降低sti蚀刻所产生的应力,降低光电二极管周围应力,减少光电二极管的位错缺陷。

77.为了更加清晰地展现出本发明所提供的技术方案及所产生的技术效果,下面以具体实施例对本发明实施例所提供的进行详细描述。

78.实施例1

79.本发明的低暗电流的像素结构设计及其制备方法,如图1所示:

80.所述像素结构至少包括置于半导体基体中的光电二极管(pd)、传输晶体管(tx)、浮动扩散节点(fd)、复位晶体管(reset)、源跟随器晶体管(sf)、行选通晶体管(select)、电源(vdd)以及pixel输出(vout)。本实施例通过优化像素版图设计,并在像素工艺制程中,使用低应力氮化硅(sin)薄膜替代高应力氮化硅薄膜以及减小氮化硅薄膜厚度的方法降低光电二极管(pd)受到的应力。减少由于光电二极管的有源区(active area)受到高应力所带来的位错缺陷(dislocation defect),从而降低像素所产生的暗电流,提高图像传感器的性能。

81.如图2所示,使用浅槽隔离邻近的光电二极管仅会在四个角落形成高应力区域,但光电二极管中间的浅槽隔离会在蚀刻过程中受到损伤,形成缺陷导致像素电路产生较高的暗电流。

82.如图3所示,使用反向pn结隔离邻近的光电二极管虽然避免了在浅槽隔离蚀刻过程中所带来的损伤,但在光电二极管周围形成了连续的高应力区域,在经过离子注入和高

温退火的过后,更易形成位错缺陷,致像素电路产生较高的暗电流。

83.如图4所示,本实施例在邻近的光电二极管中间依旧才用反向pn结隔离,避免浅槽隔离蚀刻过程中所带来的损伤。并且在光电二极管中间加入梯形浅槽隔离,使应力集中在光电二极管四个角落形成钝角结构中,避免连续的高应力区域形成,减少位错缺陷的形成,降低像素电路产生的暗电流。

84.如图6、图7所示,在浅槽隔离蚀刻的过程中会使用硬掩膜层工艺。硬掩膜层为化学气相沉积的氮化硅薄膜,在传统工艺中,生成氮化硅薄膜的反应气体dsc(二氯硅烷)和nh3的比例为1比4,其应力约为1200mpa。在本实施例中,通过调整反应气体的比例将dsc(二氯硅烷)和nh3的比例改为5比1,得到低应力氮化硅薄膜,其应力约为200mpa。

85.由于氮化硅(sin)与硅衬底晶格差异较大,会在氮化硅和硅表面形成较大的应力。通常在氮化硅和硅衬底间生长11nm的缓冲氧化层,以减小硅衬底受到的应力。但缓冲氧化层不足以抵消硬掩模层所带来的应力,并且应力随着硬掩模层厚度的增加而增加。在本实施例中,将氮化硅的厚度减小为75nm,以减小应力的产生。但为了避免浅槽隔离在填充氧化物之后的高度发生改变导致各个晶体管电学特性发生变化。本实施例在11nm的缓冲氧化层上,先生长50nm多晶硅,再沉积75nm低应力氮化硅。在不改变整体掩膜层厚度的情况下,降低硬掩膜层的厚度,减小光电二极管受到的应力,减少位错缺陷,降低像素电路产生的暗电流。

86.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求书的保护范围为准。本文背景技术部分公开的信息仅仅旨在加深对本发明的总体背景技术的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域技术人员所公知的现有技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1