数字信号输出的CMUT单元、芯片和超声设备的制作方法

数字信号输出的cmut单元、芯片和超声设备

技术领域

1.本发明涉及高密度单片集成的半导体传感器技术领域,具体涉及三维cmut架构与cmos辅助电路集成的结构及加工技术。

背景技术:

2.超声技术与产品近年来发展迅猛。手机超声指纹,触摸屏等应用,对供应链设备、技术与产能的提升产生革命性的推动,不断要求提升超声芯片的集成度,往小型化方向发展。传统的超声产品与应用主要在医学成像领域,例如胎儿b-超,人体脏体扫描,内窥成像等,在超声应用快速发展的潮流下,超声医学产品也在往小型化、便携式、掌上型方向推进。

3.超声产品小型化的关键是将原本多个分立封装的集成电路,尽可能集成到较少的封装ic中,当然最佳结果是单片集成,即一片ic封装,包含超声换能器及所有辅助电路。换言之,就是不断提出新架构、新技术,实现更高集成度,并同时解决小型化过程中遇到的挑战,如保持足够灵敏度。

4.超声设备的超声探头,除了需要超声换能传感器外,还需要多个cmos辅助电路协助工作,如图1所示,以cmut为例,超声换能器系统结构包括cmut超声探头(作超声发射器器,同时也作超声接收器),超声发射所需的高压cmos辅助电路,超声接收所需的低噪声放大器,a/d转换器等。现有技术下,这些cmos辅助电路需要采用分立封装的cmos电路实现。

5.在超声发射模式,高压源电路、脉冲产生电路、脉冲调制与控制电路是必须的。这些高压电路的电压范围:cmut通常为30—100伏。目前的超声系统中,所需高压均通过外部cmos电路产生,通过pcb印刷电路板输入到超声换能器探头的高压端口。早期的设计中,高压电路采用分立晶体管、高压电阻/电容实现,pcb上的元器件,封装ic数量则更多,体积更大。如果能够用高压ic电路取代分立器件,则可以减少封装元器件的数量,对提升集成度有益。最近,国际最前端的mems-on-cmos架构,将超声换能器做到cmos高压电路上面,在集成度的提升上跨进了一大步。

6.在超声接收模式,超声探头探测到反射的超声波后,产生微小模拟电压信号(通常在毫伏级别,甚至更低),由于这个电压幅度很小,需要一个低噪声放大器cmos电路将信号增强,甚至需要通过可变增益控制器进一步放大,才能满足系统模拟/数字转换器(a/dconverter)输入电压幅度的要求。经过a/d转换器转化成数字信号后,通过微处理器(mcu或fpga算法)形成超声图像。

7.超声探头检测到的模拟信号幅度通常在毫伏级别,甚至低于1毫伏。这个信号经过芯片内部金属互连线、压焊块,尤其经过印刷电路板上不同封装电路之间的较大尺寸的焊点、引线后,信噪比不断衰减,甚至信号有可能已经淹没在噪声中(信噪比小于1)。当进入超高频,高阵列密度超声应用时,超声单元的面积不断缩小,而封装引线及pcb的寄生效应并不会等比例缩小,信噪比的问题变得更加突出。

8.理论上讲,如果能够将超声换能器与接收模式下的cmos辅助电路以及adc都做到同一个芯片上,可以极大程度降低金属布线、封装引线及pcb的寄生效应,从而有利于提高

信噪比。然而,现有工艺架构下,这一需求难以实现。首先,cmos低噪声放大器、可变增益控制器,尤其是模拟/数字转换器,需要用到高端小尺寸cmos工艺,例如90到28纳米。在此同时,高压cmos电路(cmut电压范围为30—100伏),通常采用0.18/0.13微米(180/130纳米)或更大的设计规则。主要原因是高压cmos器件,高压隔离,都需要较深的p/n结,较厚的晶体管栅氧化层,以及较宽的p/n结扩散区,否则达不到高压要求。换言之,cmos低噪声放大器、可变增益控制器、模拟/数字转换器等小尺寸、高密度集成电路与高压cmos电路的工艺兼容性差,很难做到单片集成。其次,即使现有最先进的mems-on-cmos架构,只能做一层cmos晶圆,没有足够的芯片面积将所需cmos辅助电路全部集成到单一芯片中。第三,单片集成如此复杂的高低压电路,将显著增加所需光罩层数,工艺复杂度,降低良率,增加工艺成本。第四,同一硅衬底材料上,同时有高低压器件,容易产生电学参数相互干挠,尤其是小信号高灵敏度放大器,对衬底干挠十分敏感,等等。正是由于这些限制,目前的超声系统中,低压cmos辅助电路(低噪声放大器,可变增益控制器,尤其是模拟/数字转换器),均采用分离cmos电路,通过pcb印刷电路板与超声换能器探头连接。

9.目前所有超声换能器均为模拟信号输出。

技术实现要素:

10.本发明的目的是通过将cmut及其cmos辅助电路单片集成,实现cmut单元及其阵列芯片的数字信号输出,提高芯片集成度、降低芯片面积的同时,解决现有cmut超声换能器信噪比低的技术问题。

11.为实现本发明目的,本发明实施例提供一种数字信号输出的cmut单元,其特征在于,由第一晶圆与第二晶圆键合形成,所述第一晶圆的硅衬底层中预制有所述cmut单元的高压cmos辅助电路及高压cmos辅助电路金属互连层,所述第二晶圆的硅衬底层中预制有所述cmut单元的低压cmos辅助电路及低压cmos辅助电路金属互连层;所述第一晶圆和所述第二晶圆中至少一晶圆的衬底材料层中布置空腔体;所述第二晶圆的硅衬底层背面减薄形成单晶硅薄层,所述单晶硅薄层作为cmut单元的机械层;所述第一晶圆的衬底材料层中布置第一金属布线层,所述第二晶圆的衬底材料层中布置第二金属布线层;所述空腔体下方布置所述cmut单元的下层金属层,所述空腔体上方布置所述cmut单元的上层金属层;所述高压cmos辅助电路、低压cmos辅助电路与所述cmut单元通过所述上层金属层、所述下层金属层、所述第一金属布线层、第二金属布线层、高压cmos辅助电路金属互连层、低压cmos辅助电路金属互连层之间的垂直互连实现电学连接;所述低压cmos辅助电路包括低噪声放大器、a/d转换器,所述低噪声放大器连接至所述a/d转换器,在超声接收模式下,所述cmut单元探测到反射超声波时产生的微小模拟电压信号经所述低噪声放大器输入所述a/d转换器转换为数字信号,作为所述cmut单元的输出信号。

12.本发明实施例还提供一种数字信号输出的cmut芯片,由若干cmut单元排列组成,具有多个纵列,其特征在于,所述cmut单元由第一晶圆与第二晶圆键合形成,所述第一晶圆的硅衬底层中预制有所述cmut单元的高压cmos辅助电路及高压cmos辅助电路金属互连层,所述第二晶圆的硅衬底层中预制有所述cmut单元的低压cmos辅助电路及低压cmos辅助电路金属互连层,所述低压cmos辅助电路包括低噪声放大器;所述第一晶圆和所述第二晶圆中至少一晶圆的衬底材料层中布置空腔体;所述第二晶圆的硅衬底层背面减薄形成单晶硅

薄层,所述单晶硅薄层作为cmut单元的机械层;所述第一晶圆的衬底材料层中布置第一金属布线层,所述第二晶圆的衬底材料层中布置第二金属布线层;所述空腔体下方布置所述cmut单元的下层金属层,所述空腔体上方布置所述cmut单元的上层金属层;所述高压cmos辅助电路、低压cmos辅助电路与所述cmut单元通过所述上层金属层、所述下层金属层、所述第一金属布线层、第二金属布线层、高压cmos辅助电路金属互连层、低压cmos辅助电路金属互连层之间的垂直互连实现电学连接;所述cmut芯片包括多个a/d转换器与所述多个纵列一一对应,每个纵列的每个cmut单元的低噪声放大器分别连接至所述每个纵列对应的a/d转换器,在超声接收模式下,所述每个纵列的每个cmut单元探测到反射超声波时产生的微小模拟电压信号经各自的低噪声放大器输入所述每个纵列对应的a/d转换器转换为数字信号,作为所述cmut芯片的输出信号。

13.本发明实施例还提供一种数字信号输出的cmut芯片,由若干cmut单元排列组成,其特征在于,所述cmut单元由第一晶圆与第二晶圆键合形成,所述第一晶圆的硅衬底层中预制有所述cmut单元的高压cmos辅助电路及高压cmos辅助电路金属互连层,所述第二晶圆的硅衬底层中预制有所述cmut单元的低压cmos辅助电路及低压cmos辅助电路金属互连层,所述低压cmos辅助电路包括低噪声放大器;所述第一晶圆和所述第二晶圆中至少一晶圆的衬底材料层中布置空腔体;所述第二晶圆的硅衬底层背面减薄形成单晶硅薄层,所述单晶硅薄层作为cmut单元的机械层;所述第一晶圆的衬底材料层中布置第一金属布线层,所述第二晶圆的衬底材料层中布置第二金属布线层;所述空腔体下方布置所述cmut单元的下层金属层,所述空腔体上方布置所述cmut单元的上层金属层;所述高压cmos辅助电路、低压cmos辅助电路与所述cmut单元通过所述上层金属层、所述下层金属层、所述第一金属布线层、第二金属布线层、高压cmos辅助电路金属互连层、低压cmos辅助电路金属互连层之间的垂直互连实现电学连接;所述cmut芯片包括一a/d转换器,所述cmut芯片的每个cmut单元的低噪声放大器分别连接至所述a/d转换器,在超声接收模式下,所述每个cmut单元探测到反射超声波时产生的微小模拟电压信号经各自的低噪声放大器输入所述a/d转换器转换为数字信号,作为所述cmut芯片的输出信号。

14.以及,本发明实施例还提供一种超声设备,包括超声扫描探头,其特征在于所述超声扫描探头包括所述的数字信号输出的cmut单元。

15.以及,本发明实施例还提供一种超声设备,包括超声扫描探头,其特征在于所述超声扫描探头包括所述的数字信号输出的cmut芯片。

16.本发明有益效果:本发明基于有源晶圆键合的三维立体集成技术,采用两片cmos晶圆,一片晶圆预制较大设计规则的高压cmos辅助电路,另一片晶圆预制较小设计规则的低压cmos辅助电路,避免了单片集成高/低压cmos所面临的技术、良率及成本等问题。同时,本发明实现了cmut-on-cmos-on-cmos架构,该架构提供了两层cmos,比现有mems-on-cmos多一层硅衬底,也可以多一层cmos电路,整体cmos器件集成度提高了100%,在同一芯片上能容纳更多的cmos设计。本发明将低噪声放大器集成到cmut中,并根据不同产品需求进一步集成增益控制器、a/d转换器,超声探测的模拟小信号直接输入到低噪声放大器,不再需要经过金属互连,压焊块,以及外部印刷电路板,从根本上解决了信噪比问题。而超声小信号通过低噪声放大器,增益控制器后,直接输入a/d转换器实现数字化,在不增加cmut单元面积,不增加芯

片面积前提下,实现了数字信号输出的cmut超声换能器。

附图说明

17.图1是超声换能器系统结构框图;图2是实施例一的cmut单元的结构图;图3是实施例一的低噪声放大器植入cmut单元的结构框图;图4是实施例一的低噪声放大器电路结构图;图5是实施例一-三的数字化层次结构示意图;图6是实施例六的高压cmos辅助电路工艺路线图;图7是实施例六的低压cmos辅助电路工艺流程图。

具体实施方式

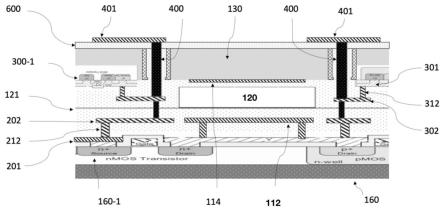

18.实施例一如图2所示,本实施例提供一种数字信号输出的cmut单元,由第一晶圆与第二晶圆通过衬底材料层低温融熔键合形成,图中121为键合界面。第一晶圆的硅衬底层160中预制有cmut单元的高压cmos辅助电路160-1及高压cmos辅助电路金属互连层201。第二晶圆的硅衬底层130中预制有cmut单元的低压cmos辅助电路300-1及低压cmos辅助电路金属互连层301。第二晶圆的硅衬底层130背面减薄形成单晶硅薄层,该单晶硅薄层作为cmut单元的机械层。cmut单元的空腔体120可以布置在第一晶圆的衬底材料层中,也可以布置在第二晶圆的衬底材料层中。为了满足特定产品应用需求,例如获得更大的垂直方向位移、增加超声输出功率等,还可以在两片晶圆布置相互连通的同心空腔体来实现。本实施例仅重点描述单一空腔体,且空腔体120布置在第二晶圆中。单晶硅薄层的厚度整体为2-6微米,根据具体应用场景需要,可以通过附加光罩局部减薄cmut单元空腔体120上方单晶硅薄层厚度,例如减至小于1微米,实现cmut单元性能适配。

19.第一晶圆的衬底材料层中布置第一金属布线层202,第二晶圆的衬底材料层中布置第二金属布线层302。空腔体120下方布置cmut单元的下层金属层112,空腔体120上方布置cmut单元的上层金属层114。高压cmos辅助电路160-1、低压cmos辅助电路300-1与cmut单元通过上层金属层114、下层金属层112、第一金属布线层202、第二金属布线层302、高压cmos辅助电路金属互连层201、低压cmos辅助电路金属互连层301之间的垂直互连实现电学连接。

20.cmut单元的机械层上方布置有氧化物层600,氧化物层600上方布置有附加金属互连层401,附加金属互连层401通过氧化硅穿孔400(tov,through oxide via)垂直连接到第一晶圆和/或第二晶圆的金属层。本实施例中,附加金属互连层401通过氧化硅穿孔400连接到第二晶圆中的第二金属布线层302。附加金属互连层401通过tov增加连接效率,便于电路连接的灵活设计,可以用于实现阵列布线要求的cmut单元之间的金属互连,以及所需要的电源线,接地线等。

21.高压cmos辅助电路160-1包括cmut在超声发射模式下工作所需的高压源电路、高压脉冲产生电路、高压脉冲调制与控制电路、高压/低压开关转换电路等。低压cmos辅助电路300-1包括cmut在超声接收模式下工作所需的低噪声放大器、a/d转换器(简称adc),低噪

声放大器连接至a/d转换器,在超声接收模式下,cmut单元探测到反射超声波时产生的微小模拟电压信号经低噪声放大器输入a/d转换器转换为数字信号,该数字信号作为所述cmut单元的输出信号。

22.本实施例首先在每一个cmut单元中植入一个小信号低噪声放大器,植入方法采用现有工艺路径容易实现。如图3、图4所示给出一种低噪声放大器电路示例。低噪放大器可以同时带二级放大,以提高增益。本实施例的低噪声放大器所占芯片面积很小。以130纳米设计规则估算,layout所占面积在千分之一平方毫米。如果采用180纳米规则,layout所占面积在千分之三平方毫米。

23.在植入低噪放大器的同时,植入a/d转换器。本实施例中每个cmut单元有自己的一个a/d转换器,实现单元层次上的数字信号输出。如图5中cmut level adc所示,即cmut单元本身可以直接输出数字信号。当cmut单元较小,且adc的精度要求较高时,如采用10-16 bit,可能需要更小设计规则的cmos工艺来制造a/d转换器,才能满足每个cmut单元植入一个a/d转换器的面积需求。

24.各cmut单元中低噪声放大器输出的信号需要在特定时钟顺序进入a/d转换器。每一个cmut单元的信号有自己的数字化处理,不参与其他单元的信号数字化。因此本实施例的cmut单元中布置了时钟控制电路,用于控制低噪声放大器的输出信号输入a/d转换器的时序。时钟控制电路属于低压设计,布置于低压晶圆即第二晶圆中,优选布置于低压cmos辅助电路中。对于时钟控制电路的具体布置和时序分配方式,本领域技术人员有能力根据应用场景进行设计。

25.对高灵敏度产品,cmut响应信号很低时,需要增益控制器进一步放大从低噪放大器的输出信号。增益控制器可植入到低噪放大器后端,作为二级放大或多级放大,增益控制器也可以与a/d转换器组合在一起。只有极高灵敏度的cmut,才需要每一个cmut单元分别布置一个增益控制器。

26.本实施例通过垂直互连的三维立体架构,将cmut超声发射模式所需高压辅助电路、超声接收模式所需的低压辅助电路分别集成到构成三维cmut架构的两片晶圆中,实现了cmut与高压辅助电路、低压辅助电路的单片soc系统集成,可以减少封装元器件的数量,极大提高集成度,有效降低了信噪比,在业内实现数字信号输出的cmut单元。

27.第一晶圆和第二晶圆之间的垂直互连结构可以通过氧化硅穿孔400(如图2中附加金属互连层401和第二金属布线层302之间的黑色连接结构tov结构,以及第二金属布线层302与第一金属布线层202之间的黑色连接结构tov结构)、金属连接孔(如图2中312、212所示连接结构)、金属引线孔等实现。第一晶圆和第二晶圆之间的垂直互连结构有多种连接组合方式,本领域技术人员能够根据电路布局灵活设计。本实施例示例了其中一种可能的连接组合方式。

28.如图2所示,附加金属互连层401通过tov结构与第二晶圆中的第二金属布线层302垂直互连,第二金属布线层302通过tov结构与第一晶圆中的第一金属布线层202垂直互连。第二层金属布线层302再分别通过tov结构与第一金属布线层202垂直互连。第一金属布线层202、下层金属层112分别通过第一晶圆中的金属连接孔212与高压cmos辅助电路金属互连层201垂直互连。低压cmos辅助电路金属互连层301通过第二晶圆中的金属连接孔312与第二金属布线层302垂直互连。

29.根据cmos电路设计需要,第一、第二金属布线层102、302可以包括不止一层金属布线,各层金属布线可以通过金属连接孔、金属引线孔垂直互连。为了方便描述,本实施例仅给出金属布线层具有一层金属布线的示例。

30.为了满足多个cmut单元互连布线的要求,cmut上方可能需要额外金属布线层(用金或铝铜线),用于实现多个cmut单元之间的金属互连,以及所需要的电源线,接地线等,因此本实施例在上层金属层114上方进一步布置氧化物隔离层403,金属接触孔402以及第三金属布线层401,以实现与cmut的电学连接。

31.当键合完成,第二晶圆实施减薄之后,通过制造tov实现第一晶圆与第二晶圆之间的电学连接,其中包括必须的电源线,地线,信号线连接等。首先腐蚀穿透第二晶圆,进行硅侧面氧化,进而腐蚀穿透二氧化硅,腐蚀至第二金属布线层302、第一金属布线层202。根据电路连接设计要求,tov的连接主要有电源线,地线,信号线,控制线等。

32.当上述垂直互连结构完成,形成cmut-on-cmos-on-cmos多层堆叠架构,再通过硅正反面穿孔(tsv,through silicon via)162将第一金属布线层201互连到硅片背面接到印刷电路板。图中162-2表示tsv pad,162-3表示tsv焊球。

33.关于本发明中各金属层之间的垂直连接,本实施例仅示例出实现垂直连接的部分方式,根据本实施例的教导,本领域技术人员可以灵活布置,实现的方式并不限于本实施例。

34.实施例二本实施例提供一种数字信号输出的cmut芯片,由若干cmut单元排列组成,具有多个纵列,其中,cmut单元由第一晶圆与第二晶圆键合形成,第一晶圆的硅衬底层160中预制有cmut单元的高压cmos辅助电路160-1及高压cmos辅助电路金属互连层201。第二晶圆的硅衬底层130中预制有cmut单元的低压cmos辅助电路300-1及低压cmos辅助电路金属互连层301。第二晶圆的硅衬底层130背面减薄形成单晶硅薄层,该单晶硅薄层作为cmut单元的机械层130。第一晶圆的衬底材料层中布置第一金属布线层202,第二晶圆的衬底材料层中布置第二金属布线层302。空腔体120下方布置cmut单元的下层金属层112,空腔体120上方布置cmut单元的上层金属层114。高压cmos辅助电路160-1、低压cmos辅助电路300-1与cmut单元通过所述上层金属层114、所述下层金属层112、第一金属布线层202、第二金属布线层302、高压cmos辅助电路金属互连层201、低压cmos辅助电路金属互连层301之间的垂直互连实现电学连接。

35.高压cmos辅助电路160-1包括cmut在超声发射模式下工作所需的高压源电路、高压脉冲产生电路、高压脉冲调制与控制电路、高压/低压开关转换电路等。

36.本实施例中的cmut单元的垂直互连架构与实施例一中的cmut单元基本一致,包括空腔体的布置、金属布线层的布置、垂直互连结构的布置等,以下着重描述不同的部分,与实施例一一致的部分不再赘述。

37.根据产品规格需求不同,本实施例在实现cmut超声换能器的数字信号输出上,采用的方案与实施例一不同。本实施例在每一个cmut单元的低压cmos辅助电路中仅植入低噪放大器,并在cmut阵列每个纵列末端布置一个a/d转换器,每个纵列的多个cmut单元共用一个a/d转换器,a/d转换器与纵列一一对应,实现纵列层次上的数字信号输出,如图5中column level adc所示,即cmut阵列每个纵列的数字信号输出。这一层次的数字信号输出,

更利于高频工作,但芯片面积会有所增加。

38.各cmut单元输出的信号需要在其特定时钟顺序进入a/d转换器,彼此不叠加。各单元信号顺序进入,依序输出。每一cmut单元的信号有自己的数字化处理,不参与其他单元的信号数字化。因此本实施例在cmut芯片中布置时钟控制电路,用于控制各cmut单元的输出信号输入a/d转换器的时序。时钟控制电路是全局分享、分频的,根据需要可以二分频,四分频等等。时钟控制电路属于低压设计,布置于低压晶圆即第二晶圆中,优选布置于低压cmos辅助电路中。对于时钟控制电路的具体布置和时序分配方式,本领域技术人员有能力根据应用场景进行设计。

39.在植入低噪声放大器和a/d转换器的基础上,也可植入可变增益控制器以提到增益,尤其是对高灵敏度产品,cmut响应信号很低时,需要增益控制器进一步放大信号。增益控制器一般一对一布置在a/d转换器的前级。增益控制器可单独布置在纵列末端,或者与a/d转换器组合在一起。

40.本实施例cmut芯片的每个纵列的每个cmut单元的低噪声放大器分别连接至纵列末端对应的a/d转换器,在超声接收模式下,每个纵列的每个cmut单元探测到反射超声波时产生的微小模拟电压信号经各自的低噪声放大器输入对应的a/d转换器转换为数字信号,作为cmut芯片的输出信号。本实施例利用三维垂直互连结构实现了cmut与高压辅助电路、低压辅助电路的单片soc系统集成,实现了数字信号输出的cmut芯片。

41.实施例三本实施例提供一种数字信号输出的cmut芯片,由若干cmut单元排列组成,具有多个纵列,其中,cmut单元由第一晶圆与第二晶圆键合形成,第一晶圆的硅衬底层160中预制有cmut单元的高压cmos辅助电路160-1及高压cmos辅助电路金属互连层201。第二晶圆的硅衬底层130中预制有cmut单元的低压cmos辅助电路300-1及低压cmos辅助电路金属互连层301。第二晶圆的硅衬底层130背面减薄形成单晶硅薄层,该单晶硅薄层作为cmut单元的机械层130。第一晶圆的衬底材料层中布置第一金属布线层202,第二晶圆的衬底材料层中布置第二金属布线层302。空腔体120下方布置cmut单元的下层金属层112,空腔体120上方布置cmut单元的上层金属层114。高压cmos辅助电路160-1、低压cmos辅助电路300-1与cmut单元通过所述上层金属层114、所述下层金属层112、第一金属布线层202、第二金属布线层302、高压cmos辅助电路金属互连层201、低压cmos辅助电路金属互连层301之间的垂直互连实现电学连接。

42.高压cmos辅助电路160-1包括cmut在超声发射模式下工作所需的高压源电路、高压脉冲产生电路、高压脉冲调制与控制电路、高压/低压开关转换电路等。

43.本实施例中的cmut单元的垂直互连架构与实施例一的cmut单元基本一致,包括空腔体的布置、金属布线层的布置、垂直互连结构的布置等,以下着重描述不同的部分,与实施例一一致的部分不再赘述。

44.根据产品规格需求不同,本实施例在实现cmut超声换能器的数字信号输出上,采用的方案与实施例一和实施例2都不同。本实施例在每一个cmut单元的低压cmos辅助电路中仅植入低噪放大器,并在cmut芯片的信号输出端布置一个a/d转换器,每个cmut芯片的所有cmut单元共用一个a/d转换器,a/d转换器与芯片一一对应,实现芯片层次上的数字信号输出,如图5中chip level adc所示,即cmut芯片的数字信号输出。对于集成度较低的换能

器阵列,例如线性阵列或很小的面阵列,安排a/d转换器在芯片输出级完成,这是综合芯片工作速度与芯片面积后,最经济合理的选择。

45.各cmut单元输出的信号需要在其特定时钟顺序进入a/d转换器,彼此不叠加。各单元信号顺序进入,依序输出。每一cmut单元的信号有自己的数字化处理,不参与其他单元的信号数字化。因此本实施例在cmut芯片中布置时钟控制电路,用于控制各cmut单元的输出信号输入a/d转换器的时序。时钟控制电路是全局分享、分频的,根据需要可以二分频,四分频等等。时钟控制电路属于低压设计,布置于低压晶圆即第二晶圆中,优选布置于低压cmos辅助电路中。对于时钟控制电路的具体布置和时序分配方式,本领域技术人员有能力根据应用场景进行设计。

46.在植入低噪声放大器和a/d转换器的基础上,也可植入可变增益控制器以提到增益,尤其是对高灵敏度产品,cmut响应信号很低时,需要增益控制器进一步放大信号。增益控制器一般一对一布置在a/d转换器的前级。增益控制器可单独布置芯片输出级,或者与a/d转换器组合在一起。

47.本实施例cmut芯片的每个cmut单元的低噪声放大器分别连接至芯片信号输出端布置的a/d转换器,在超声接收模式下,每个cmut单元探测到反射超声波时产生的微小模拟电压信号经各自的低噪声放大器输入a/d转换器转换为数字信号,作为cmut芯片的输出信号。本实施例利用三维垂直互连结构实现了cmut与高压辅助电路、低压辅助电路的单片soc系统集成,实现了数字信号输出的cmut芯片。

48.上述实施例一-三中,a/d转换器的布置形式根据产品规格需求而变化,实现了如图4所示cmut产品三个层次的信号数字化。数字化第一层次是chip level adc,即整个芯片在信号输出端用一个adc。对于集成度较低的换能器阵列,例如线性阵列或很小的面阵列,安排adc在芯片输出级完成,这是综合芯片工作速度与芯片面积后,最经济合理的选择。数字化第二层次是column level adc,即超声换能器阵列的每一纵列共用一个adc。换能器的信号数字化在阵列的每一纵列实现,这一做法更利于高频工作,但芯片面积有所增加。数字化第三层次是cmut level adc,每个cmut单元有自己的adc,即cmut单元本身是数字信号输出。当cmut单元较小,且adc的精度要求较高时,如采用10-16bit,可能需要更小设计规则的cmos工艺来制造adc,才能满足每个cmut单元有自己adc的面积要求。数字化不同层次的选择,主要是权衡cmut单元与adc面积、芯片整体速度与功耗以及芯片良率、成本。对于采样频率与时序设计方面,三个层次adc类似,不同之处在于cmut level adc的时钟分配针对单个cmut单元,column level adc的时钟分配针对同一列的cmut单元,而chip level adc的时钟分配针对整个阵列的cmut单元。

49.实施例四本实施例提供一种超声设备,包括超声扫描探头,所述超声扫描探头包括实施例一所述的数字信号输出的cmut单元,cmut单元探测到反射超声波时,直接输出数字信号到微处理器,通过微处理器处理形成超声图像,信号的传输不再需要经过金属互连,压焊块,以及外部印刷电路板,从根本上解决了信噪比问题。

50.实施例五本实施例一种超声设备,包括超声扫描探头,所述超声扫描探头包括实施例2或实施例3所述的数字信号输出的cmut芯片,cmut芯片中的cmut单元探测到反射超声波时,cmut

芯片直接输出数字信号到微处理器,通过微处理器对数字信号进行处理形成超声图像,信号的传输不再需要经过金属互连,压焊块,以及外部印刷电路板,从根本上解决了信噪比问题。

51.实施例六本实施例提供实施例一所述数字信号输出的cmut单元的制造方法,主要工艺路线包括:

·

第一晶圆制造cmut高压cmos辅助电路,第二晶圆制造低压cmos辅助电路;

·

第一、第二晶圆面对面低温融熔键合;

·

键合后的第二晶圆进行背面特殊减薄,形成cmut阵列所需机械层;

·

第一晶圆与第二晶圆之间垂直互连,实现cmut-on-cmos-on-cmos架构。

52.具体包括如下步骤:步骤1、准备第一晶圆、第二晶圆,分别在表面生长100纳米左右的二氧化硅形成硅衬底层,在第一晶圆硅衬底层制造高压cmos辅助电路及高压cmos辅助电路金属互连层,在第二晶圆硅衬底层制造低压cmos辅助电路及低压cmos辅助电路金属互连层。

53.制造cmos辅助电路采用业界标准流程实现,其工艺流程分别如图6、7所示。

54.高压cmos辅助电路,高压达到30—100伏,包括cmos高压源电路,高压脉冲产生电路,高压脉冲调制与控制电路,高压/低压开关转换电路等。考虑到设计规则的选择、所需光罩总数和cmos工艺制程的优化,应尽量把制程较复杂的高压辅助电路安排在同一片晶圆上。在非soc设计作为选项时,部分电路例如高压源电路,可以采用外灌方式,以降低电路整体功耗。

55.低压cmos辅助电路,主要安排低噪声放大器电路、增益控制器电路、a/d转换器电路、时钟控制电路等。这些电路工作电压低(1.0—3.3伏),设计规则尺寸小(130—65纳米),模拟参数要求精确(10-16bit的adc),adc采样频率范围10—500mhz。

56.步骤2、在第一晶圆、第二晶圆的硅衬底层上淀积衬底材料层,制造第一金属布线层、第二金属布线层、上层金属层、下层金属层以及第一晶圆内部、第二晶圆内部的垂直互连结构。

57.根据cmos电路设计需要,第一、第二金属布线层可以包括不止一层金属布线,各层金属布线可以通过金属引线孔垂直互连。

58.步骤3、在第二晶圆衬底材料层制造空腔体。具体方法是:先光刻形成空腔cavity图形,再通过氧化硅腐蚀形成空腔。

59.由于实施例一的空腔体布置在第二晶圆上,因此本实施例空腔体的制造流程位于第二晶圆制备流程尾程。如果空腔体布置在第一晶圆上,则该空腔体的制造流程可以相应置于第一晶圆制备流程尾程。空腔体也可分别布置在两片晶圆上。

60.步骤4、第一晶圆和第二晶圆低温融熔键合,形成键合界面。

61.步骤5、对第二晶圆硅衬底层背面进行厚度减薄形成单晶硅薄层,作为cmut的机械层。

62.步骤6、第一晶圆和第二晶圆垂直互连tov工艺。tov在连接两片晶圆时有多种连接组合方式,本实施例按实施例一的连接方式进行工艺处理。制造tov时,在tov设计部位光刻腐蚀硅,氧气等离子处理后,继续二氧化硅连接孔腐蚀,腐蚀完成后,淀积金属(常用金属

钨)实现电学连接。tov在连接两片晶圆的同时,也预留接触部位给cmut阵列以及所需电源及接地线。

63.步骤7、tov之后,淀积氧化物层600,淀积、光刻、腐蚀附加金属互连层401。附加金属互连层401通过tov 400增加单元内部包括与晶圆的连接效率,同时,附加金属互连层401可以实现阵列布线要求的cmut单元之间的金属互连,以及阵列所需要的电源线,接地线等。对于实施例2和实施例3,即当a/d转换器布置在纵列末端或芯片信号输出端时,cmut单元的基本制造流程同上,不同在于布置a/d转换器和增益控制器的位置不同,并且需要完成各cmut单元之间的电学连接,以及各单元的低噪声放大器与a/d变换器之间的电学连接。由于采用cmut-on-cmos-on-cmos三层电路架构,在布局上不用担心重叠的问题,仅仅需要考虑布线的对称性和实现最小的芯片面积。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1