一种半导体封装结构的制作方法

1.本发明涉及半导体技术领域,特别涉及一种半导体封装结构。

背景技术:

2.半导体封装结构包括基板、外壳以及至少一个芯片或半导体器件,其中至少一个芯片或半导体器件设置于基板上,基板与外壳胶连或者机械连接,其中,外壳例如为一体设置,或者包括多个分体设置的部分。外壳需要开设槽/洞/孔,以供引脚通过,但是开设的槽/洞/孔导致所述外壳的气密性较差;外壳与基板连接处或者分体设置的外壳的连接处的气密性也较差。

3.半导体封装结构内部的键合线等用于电气连接的导电结构通常采用金属材质(例如,铜、银等),在腐蚀性环境中腐蚀性气体(例如硫化氢、盐酸)容易通过外壳的孔洞或者外壳与基板的连接处等位置进入半导体封装结构内部,腐蚀金属材料产生腐蚀层或晶枝,影响材料的电阻率,若晶枝过长则将导致电路耐压部位漏电甚至击穿。

技术实现要素:

4.鉴于上述问题,本发明的目的在于提供一种半导体封装结构,以提高所述半导体封装结构的密封性,并且防止发生漏电以及击穿。

5.本发明提供一种半导体封装结构,包括:

6.底板,所述底板包括基板以及位于所述基板上的第一导电层;

7.框架,所述框架包括框架主体以及嵌于所述框架主体内部的第一嵌体,所述框架主体和所述第一嵌体均呈环状,所述第一嵌体暴露于所述框架主体的两个端面;以及

8.顶盖,所述顶盖包括顶盖主体以及嵌于所述顶盖主体内部的第二嵌体,所述第二嵌体暴露于所述顶盖主体的第二表面;

9.其中,所述第一嵌体在所述框架的第二端与所述基板上的第一导电层密封连接,所述第一嵌体在所述框架的第一端与所述顶盖的第二嵌体密封连接,所述基板、所述框架以及所述顶盖包围形成一个空腔。

10.优选地,所述基板上还包括:

11.第二导电层,所述第二导电层位于所述基板的第一表面上;以及

12.半导体器件或半导体芯片,位于所述第二导电层上,并且与所述第二导电层电连接。

13.优选地,所述第一导电层位于所述基板的第一表面,所述第一导电层为环状,围绕所述第二导电层,且所述第一导电层的内侧壁与所述第二导电层的外侧壁之间具有间隙。

14.优选地,所述第一导电层的内侧壁与所述第二导电层的外侧壁之间的距离d1满足:

15.d1》u

operation

/e

breakdown-air/filler

16.其中,u

operation

为封装于半导体封装结构内的半导体器件或半导体芯片的工作电

压,e

breakdown-air/filler

为围绕半导体器件或半导体芯片的介质中的击穿电场强度的最小值。

17.优选地,所述第一导电层位于所述基板的第二表面,所述第一导电层为板状,其中,所述基板的第二表面与所述基板的第一表面相对;所述第一导电层的面积大于所述基板的面积,所述第一导电层与所述第一嵌体密封连接后,所述基板位于所述空腔内。

18.优选地,还包括引脚,所述引脚的一端与所述第二导电层电连接,所述引脚的另一端延伸至所述半导体封装结构外部。

19.优选地,所述顶盖还包括第一通孔,所述引脚不与所述第二导电层电连接的一端穿过所述第一通孔延伸至所述半导体封装结构外部。

20.优选地,在所述顶盖的第二表面,所述第一通孔的侧壁向所述空腔内延伸。

21.优选地,所述第一通孔延伸至所述空腔内的侧壁的厚度d2满足:

22.d2》u

operation

/e

breakdown-plastic

23.其中,u

operation

为封装于半导体封装结构内的半导体器件或半导体芯片的工作电压,e

breakdown-plastic

为所述顶盖主体材料的击穿电场强度。

24.优选地,所述引脚与所述第一通孔的侧壁之间填充第三填充层。

25.优选地,所述第一嵌体为一体结构,贯穿所述框架主体的高度方向。

26.优选地,部分所述引脚嵌于所述框架主体内。

27.优选地,所述第一嵌体包括分体设置的两部分,其中一部分所述第一嵌体暴露于所述框架主体的第二端的表面,其中另一部分所述第一嵌体暴露于所述框架主体的第一端的表面。

28.优选地,其中一分部的所述第一嵌体与所述引脚之间的距离d4满足:

29.d4》u

operation

/e

breakdown-plastic

30.其中另一部分的所述第一嵌体与所述引脚之间的距离d5满足:

31.d5》u

operation

/e

breakdown-plastic

32.其中,u

operation

为封装于半导体封装结构内的半导体器件或半导体芯片的工作电压,e

breakdown-plastic

为所述框架主体材料的击穿电场强度。

33.优选地,所述顶盖还包括:

34.第二通孔,位于靠近所述顶盖主体的第二表面的一侧;

35.第三通孔,位于靠近所述顶盖主体的第一表面的一侧;

36.所述第三通孔的孔径大于所述第二通孔的孔径,所述第二通孔和所述第三通孔相互连通贯穿所述顶盖主体;

37.在与所述第三通孔连通的一端,所述第二通孔的外壁外侧嵌有环状的第三嵌体,所述第三嵌体暴露于所述第三通孔的底部,所述第三嵌体围绕所述第二通孔;所述顶盖还包括密封板,所述密封板位于所述第三通孔内,并且与暴露于所述第三通孔的底部的第三嵌体密封连接。

38.优选地,所述顶盖还包括:

39.第二通孔,所述第二通孔贯穿所述顶盖主体;

40.在所述第二通孔的外壁外侧嵌有环状的第三嵌体,所述第三嵌体暴露于所述顶盖主体的第一表面,所述第三嵌体围绕所述第二通孔;

41.所述顶盖还包括:密封板,所述密封板位于所述顶盖主体的第一表面,并且与暴露

于所述顶盖主体的第一表面的所述第三嵌体密封连接。

42.优选地,在所述顶盖主体的第二表面,所述第二通孔的侧壁向所述空腔内延伸。

43.优选地,所述半导体器件或半导体芯片上,以及所述第二导电层上覆盖有第二填充层。

44.优选地,所述顶盖主体的第二表面覆盖第一填充层;在所述顶盖的第二表面,所述第二嵌体围绕所述第一填充层,且与所述第一填充层相互分离。

45.优选地,所述第一填充层和所述第二填充层之间具有间隙。

46.优选地,所述第一填充层为软性材料层,其中软性材料层中含有金属氧化物。

47.优选地,所述第一填充层远离所述顶盖的表面与所述第一通孔伸入空腔内部的端面的距离d3满足:

48.d3≥d

1-d249.其中,d1为所述第一导电层的内侧壁与所述第二导电层的外侧壁之间的距离,d2为所述第一通孔延伸至所述空腔内的侧壁的厚度。

50.本发明提供的半导体封装结构包括底板、框架和顶盖,且所述框架的两端分别与所述底板以及所述顶盖经由焊接密封连接,使得所述底板、框架和顶盖的连接处不存在气体扩散通路,保证了所述半导体封装结构的密封性,有效防止腐蚀性气体(例如硫化氢、盐酸等)由底板、框架和顶盖的连接处扩散进入空腔内,避免所述半导体封装结构内部的半导体器件或半导体芯片受到腐蚀性气体的腐蚀,保证所述半导体器件或半导体芯片的正常工作。

51.进一步地,所述框架和所述顶盖均采用绝缘性主体包覆金属嵌体的结构。一方面,金属嵌体能够实现所述半导体封装结构的焊接密封,绝缘性主体包覆金属嵌体,能够避免金属嵌体在腐蚀性环境中被腐蚀;另一方面,所述绝缘性主体能提高金属嵌体与所述半导体封装结构内部的其他导电结构之间的绝缘性隔离,能够有效阻止晶枝在空腔内生长,进一步防止产生导电通路。

52.在优选地实施例中,所述第一导电层和所述第二导电层共同位于所述基板的第一表面,且所述第一导电层与所述第二导电层之间具有间隙,以降低引入的第一导电层影响产品的耐压特性的风险。

53.在优选的实施例中,所述第一导电层和所述第二导电层位于所述基板相对的两个表面,所述第一导电层一方面用于实现与所述框架的密封连接,另一方面实现对所述基板进行支撑,并且所述第一导电层能够对经过所述第一导电层传导的电磁波进行衰减,具有一定的电磁屏蔽作用。

54.在优选的实施例中,所述第一嵌体为一体结构,贯穿所述框架的高度方向,方便加工。

55.在优选地实施例中,所述第一嵌体包括分体的两部分,分体的两部分第一嵌体之间为绝缘性的框架主体,一方面提升所述框架的绝缘性,另一方面为引脚的设置提供了空间。

56.在优选的实施例中,在所述顶盖的第二表面,所述第一通孔的侧壁向所述空腔内延伸,防止伸入所述空腔内部的所述第一通孔的侧壁发生击穿,且所述第一通孔和所述引脚之间填充有第三填充层,以减小腐蚀性气体分子的扩散速度。

57.在优选的实施例中,在顶盖主体的第二表面覆盖有第一填充层,第一填充层为含有金属氧化物粉末的软性填充材料,对所述空腔内的腐蚀性气体进行吸收,避免半导体器件被腐蚀。

58.在优选的实施例中,所述第二填充层与所述第一填充层之间具有间隙,该间隙为缓冲区,所述缓冲区内的空气用来稀释通过所述第一通孔扩散进入所述空腔内的腐蚀性气体,并且扩大稀释后的腐蚀性气体与第一填充层的接触面积,由于腐蚀性气体在第一填充层中的溶解度比在第二填充层中的溶解度大,进入所述空腔的腐蚀性气体将更易被第一填充层吸收。

59.在优选地实施例中,在顶盖上开设第二通孔,并且在第二通孔上增加密封板,且所述密封板与所述顶盖中的第三嵌体之间通过焊接密封连接,阻挡腐蚀性气体的扩散通路。

附图说明

60.通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

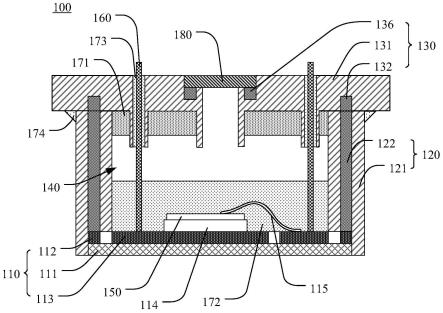

61.图1示出了本发明第一实施例的半导体封装结构的截面图;

62.图2示出了本发明第一实施例的底板的截面图;

63.图3示出了本发明第一实施例的框架的截面图;

64.图4示出了本发明第一实施例的顶盖的截面图;

65.图5示出了本发明第二实施例的半导体封装结构的截面图。

具体实施方式

66.以下将参照附图更详细地描述本发明。在各个附图中,相同的元件采用类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。此外,可能未示出某些公知的部分。

67.本发明可以各种形式呈现,以下将描述其中一些示例。

68.现有技术中,半导体封装结构通常采用金属的封装外壳,以对封装于所述半导体封装结构内部的半导体器件形成电磁屏蔽,且为了提高屏蔽效率,金属的封装外壳通常一体成形。然而,现有的金属封装外壳一般需要预留引脚的位置,需要在封装外壳上开设槽/洞/孔,导致所述封装外壳的气密性较差。另外,在腐蚀性的环境(例如硫化氢、盐酸等环境)中,金属的封装外壳会生长晶枝,使得所述封装外壳与其内部的引线和/或其他导电结构之间的距离减小,所述封装外壳内部的引线/或其他导电结构中任意位置产生导电缺陷将会导致所述封装外壳带电,进一步产生额外的导电、漏电通路,使产品失效。

69.图1示出了本发明第一实施例的半导体封装结构的截面图;如图1所示,所述半导体封装结构100包括底板110、框架120和顶盖130,所述底板110在所述框架120的第二端与所述框架120进行组合,所述顶盖130在所述框架130的第一端与所述框架130进行组合,所述底板110、框架120和顶盖130组合在一起以形成空腔140;其中,所述框架120的第一端与所述框架120的第二端相对。

70.图2示出了本发明第一实施例的底板的截面图,如图1和图2所示,所述底板110包括基板111以及覆盖于所述基板111第一表面的第一导电层112和第二导电层113。其中,所

述第一导电层112呈环状,围绕在所述基板111第一表面的边缘。所述基板111用于对所述第一导电层112以及所述第二导电层113进行支撑,所述第一导电层112用于实现与所述框架120的密封连接,以使得所述底板110在所述框架120的第二端与所述框架120密封连接。本实施例中,所述基板111例如为覆铜陶瓷基板(dbc),所述第一导电层112例如为覆盖于所述基板111第一表面的铜导电层。

71.图3示出了本发明第一实施例的框架的截面图,如图1和图3所示,所述框架120包括框架主体121以及嵌于所述框架主体121内部的第一嵌体122,所述框架主体121和所述第一嵌体122呈环状,以构成环状的所述框架120。在所述框架主体121的高度方向,所述第一嵌体122贯穿所述框架主体121,暴露于所述框架主体121的第一端表面和第二端表面。其中,所述框架主体121采用热塑性材料(例如pbt材料、tpu材料等)模制成型,所述第一嵌体122采用金属材料(例如铜)冲压成型。采用框架主体121包裹第一嵌体122是为了避免金属材料的第一嵌体122在腐蚀性环境中被腐蚀产生枝晶,导致漏电甚至产品失效;框架主体121能提高第一嵌体122与其他导电结构之间的绝缘性能,能够有效阻止晶枝在空腔140内生长产生导电通路。

72.图4示出了本发明第一实施例的顶盖的截面图,如图1和图4所示,所述顶盖130包括顶盖主体131以及嵌于所述顶盖主体131内部的第二嵌体132,所述顶盖主体131呈板状,所述第二嵌体132呈环状,所述顶盖主体131和所述第二嵌体132构成板状的顶盖130。所述第二嵌体132暴露于所述顶盖主体131的第二表面,所述第一表面和所述第二表面相对。所述顶盖主体131采用热塑性材料(例如pbt材料、tpu材料等)模制成型,所述第二嵌体132采用金属材料(例如铜)冲压成型。其中,所述顶盖主体131的厚度大于所述第二嵌体132的厚度,以使得所述第二嵌体132只暴露于所述顶盖主体131的第二表面。

73.本实施例中,所述第一导电层112、所述第一嵌体122以及所述第二嵌体132均为环形,且环形的形状和尺寸相同。在所述框架120的第一端,所述框架120的第一嵌体122与所述顶盖130的第二嵌体132通过焊接形成密封连接;在所述框架120的第二端,所述框架120的第一嵌体122与所述底板110的第一导电层112通过焊接形成密封连接,以使得所述底板110、框架120和顶盖130围成密封的空腔140。其中,所述第一导电层112和所述第一嵌体122以及所述第一嵌体122和所述第二嵌体132之间使用焊锡膏低温回流焊接,焊接温度在200℃以下,以防止所述第一嵌体122和所述框架主体121之间以及所述第二嵌体132和所述顶盖主体131出现分层变形的现象。焊接后,可以确保底板110和框架120的连接处以及框架120和顶盖130的连接处不存在气体扩散通路,杜绝了腐蚀性气体由分体部件的连接处扩散进入空腔140内。

74.进一步地,本实施例中,在所述框架120的第二端,所述框架主体121包覆所述底板110的外侧壁,便于所述底板110的对准安装。

75.进一步地,在所述框架120和所述顶盖130密封连接之后,在所述框架120和所述顶盖130之间使用弹性胶174(例如,玻璃胶等)连接,用于吸收外部的拉应力,缓解第二嵌体132与所述第一嵌体122焊点的应力蠕变老化。

76.半导体器件150(或半导体芯片)被封装于所述空腔140内。优选地,所述半导体器件150(或半导体芯片)为功率半导体器件(或功率半导体芯片),所述半导体封装结构100为功率模块的封装结构。继续参阅图1和图2,所述底板110还包括第二导电层113。所述第二导

电层113位于所述基板111第一表面的中心区域,所述第一导电层112在所述基板111的第一表面围绕所述第二导电层113。所述第二导电层113用于实现半导体器件150的导电连接。本实施例中,所述第二导电层113例如为覆盖于所述基板111第一表面的铜导电层。

77.所述半导体器件150位于所述基板111的第一表面,且经由连接层114和/或键合线115与所述基板111第一表面的第二导电层113导电连接。所述第二导电层113上连接有引脚160,所述半导体器件150经由第二导电层113以及所述引脚160与外界实现电连接。其中,所述连接层114例如为软焊料、银浆等,还可以为绝缘胶;所述键合线115例如为铜线、银线等。

78.进一步地,所述第一导电层112的内壁与所述第二导电层113的外壁之间具有间隙,以使得所述第二导电层113和所述第一导电层112之间相互分离,所述第一导电层112的内壁与所述第二导电层113的外壁之间的间隙使得所述第一导电层112和所述第二导电层113之间绝缘,降低引入的第一导电层112影响产品的耐压特性的风险。在一个具体地实施例中,所述第一导电层112的内壁与所述第二导电层113的外壁之间的距离d1应满足:

79.d1》u

operation

/e

breakdown-air/filler

80.其中,u

operation

为半导体器件150的工作电压,e

breakdown-air/filler

为围绕所述半导体器件150的介质(空气或包覆所述半导体器件150的填充层)中的击穿电场强度的最小值。具体地,d1例如大于1mm。

81.进一步地,所述顶盖130上开设有第一通孔133,所述第一通孔133用于供所述引脚160穿过,以使得所述引脚160的一端延伸至所述半导体封装结构100的外部。具体地,在所述底板110、框架120以及所述顶盖130组合在一起后,所述引脚160的一端与所述第二导电层113电连接,另一端从所述第一通孔133中穿过,经过所述第一通孔133延伸至所述半导体封装结构100的外部。其中,所述第一通孔133的直径大于等于所述引脚160的直径,以使得所述引脚160能够穿过所述第一通孔133。

82.在所述顶盖130的第二表面(即设置第二嵌体132的表面),所述第一通孔133的侧壁从所述顶盖130的第二表面向所述空腔140内延伸。且为了防止伸入所述空腔140内部的所述第一通孔133的侧壁发生击穿,伸入所述空腔140内部的所述第一通孔133的侧壁厚度d2应满足:

83.d2》u

operation

/e

breakdown-plastic

84.其中,u

operation

为半导体器件150的工作电压,e

breakdown-plastic

为所述顶盖主体131材料的击穿电场强度。

85.所述第一通孔133延伸到空腔140内部的长度决定腐蚀性气体通过所述第一通孔133扩散进入所述空腔140中的扩散速度,可根据需求进行设计。

86.所述顶盖主体131的第二表面上覆盖有第一填充层171,在所述顶盖主体131的第二表面,所述第二嵌体132围绕所述第一填充层171,且不与所述第一填充层171接触。所述第一填充层171的形状并没有特别限制。所述第一填充层171例如为含有金属氧化物粉末的软性填充材料,其中,金属氧化物例如为氧化铜、氧化锌、氧化铝等,软性填充材料例如为硅凝胶等。所述第一填充层171被封装于所述空腔140内,对所述空腔140内的腐蚀性气体进行吸收,使空腔140中的空气几乎不存在腐蚀性气体,降低空腔140中的半导体器件150表面的腐蚀性气体的浓度,避免半导体器件150中的敏感金属(例如,铜、银)被腐蚀。

87.所述第一填充层171远离所述顶盖130的表面与所述第一通孔133伸入空腔140内

部的端面的距离d3应满足:

88.d3≥d

1-d289.进一步地,所述顶盖主体131的中心区域开设有第二通孔134和第三通孔135,所述第二通孔134与第三通孔135同心且相互连通,其中,所述第二通孔134位于靠近所述顶盖主体131的第二表面的一侧,所述第三通孔135位于靠近所述顶盖主体131的第一表面的一侧,所述第二通孔134和所述第三通孔135相互连通,并且贯穿所述顶盖主体131。在所述顶盖主体131的第二表面,所述第二通孔134的侧壁向所述空腔140内延伸。优选地,所述第二通孔134向空腔140内延伸的距离大于等于所述第一填充层171的厚度,以形成阻挡墙。

90.本实施例中,所述第一通孔134位于所述顶盖主体131的中心区域,在其他实施例中,可以根据具体地需要开设于所述顶盖主体131的其他位置。并且可以对所述第一通孔134的数量进行任意的设置,且当所述第一通孔134为多个时,通常关于所述顶盖主体131的中心对称设置。

91.所述第二通孔134用于在所述底板110、框架120以及所述顶盖130组合在一起后,向所述空腔140中灌注填充材料。具体地,经由所述第二通孔134向所述空腔140内部填充软性材料,以形成第二填充层172,以保护半导体器件150,其中,所述第二填充层172包覆所述半导体器件150、所述键合线115以及部分的所述引脚160,并覆盖所述第二导电层113的表面。所述第二填充层172的高度大于所述半导体器件150的高度,且所述第二填充层172不与所述第一通孔133以及所述第二通孔134延伸至所述空腔140内部的端面接触。

92.所述第二填充层172为软性填充材料,例如为硅酮胶、硅橡胶等。所述第二填充层172填充有二氧化硅,以降低硅酮胶、硅橡胶等中各类杂质的溶解度与扩散系数。进一步地,所述第一填充层171中也可以掺杂二氧化硅,且第二填充层172中二氧化硅的掺杂量大于所述第一填充层171中二氧化硅的掺杂量。

93.进一步地,所述第二填充层172与所述第一填充层171之间具有间隙,该间隙为缓冲区,所述缓冲区内的空气用来稀释通过所述第一通孔133、第二通孔134以及第三通孔135扩散进入所述空腔140内的腐蚀性气体,并且扩大稀释后的腐蚀性气体与第一填充层171的接触面积,由于所述第一填充层171中二氧化硅的含量低于所述第二填充层172中二氧化硅的含量,腐蚀性气体在第一填充层171中的溶解度比在第二填充层172中的溶解度大(二氧化硅浓度升高,硫化氢的溶解度降低),进入所述空腔140的腐蚀性气体将更易被第一填充层171吸收。

94.另外,在向所述空腔140内填充完第二填充层172之后,向所述第一通孔133的内壁与所述引脚160的外壁之间填充第三填充层173,所述第三填充层173包裹于所述引脚160的周围,以阻挡腐蚀性气体进入空腔140。所述第三填充层173的材料为软性填充材料,例如为硅酮胶、硅橡胶等。

95.所述第三通孔135用于安装密封板180,在经由所述第二通孔134灌注填充材料完成之后,将所述密封板180安装于所述第三通孔135内,以对所述第二通孔134靠近所述第三通孔135的一端的端口进行封堵。具体地,在与所述第三通孔135连通的一端,所述第二通孔134的外壁外侧嵌有环状的第三嵌体136,所述第三嵌体136围绕所述第二通孔134,所述第三嵌体暴露于所述第三通孔135的底部。所述密封板180置于所述第三通孔135内,并且与暴露于所述第三通孔135的底部的第三嵌体136密封连接,以实现对所述第二通孔134的封堵。

所述密封板180例如为金属板(例如,铜、铝、铁等),通过低温回流焊接与所述第三嵌体136密封连接。

96.进一步地,所述第三通孔135的直径大于所述第二通孔134的直径,所述密封板180的直径等于所述第三通孔135的直径,进而所述密封板180的直径大于所述第二通孔134的直径,以使得所述密封板180对所述第二通孔134靠近所述第三通孔135一端的端口进行全面地封堵。优选地,所述第三通孔135的深度等于所述密封板180的厚度,以使所述顶盖主体131的第一表面与所述密封板180的表面齐平。

97.本实施例中设置有第三通孔135,在其他实施例中,还可以不设置第三通孔135,所述第二通孔134贯穿所述顶盖主体131的厚度方向,所述第三嵌体136暴露于所述顶盖主体131的第一表面,所述密封板180位于所述顶盖主体131的第一表面,与暴露于所述顶盖主体131的第一表面的第三嵌体136密封连接。此时,所述密封板180凸出于所述顶盖主体131的第一表面。

98.本实施例中,形成所述半导体封装结构的方法包括:

99.s10:形成具有第一导电层112和第二导电层113的基板111。

100.其中,所述基板111的第一表面具有第一导电层112和第二导电层113,所述第一导电层112围绕所述第二导电层113,且所述第一导电层112的内壁与所述第二导电层113的外壁之间具有间隙,以使得所述第一导电层112和所述第二导电层113相互分离。

101.接着,将半导体器件150固定于所述第二导电层113上。其中,所述半导体器件150分别经由连接层114以及键合线115与所述第二导电层113电连接,所述连接层114的材料为例如为软焊料、银浆等,还可以为绝缘胶;所述键合线115例如为铜线、银线等。即所述半导体器件150分别经由连接层114以及键合线115连接于所述第二导电层113上。

102.s20:形成具有第一嵌体122的框架120,并且在所述框架120的第二端,将所述第一嵌体122与所述第一导电层112焊接在一起。

103.本实施例中,在所述第一嵌体122周围,使用热塑性材料模制成型,以形成包裹所述第一嵌体122的框架本体121。进一步地,所述第一导电层112和所述第一嵌体122之间使用焊锡膏低温回流焊接,焊接温度在200℃以下,以防止所述第一嵌体122和所述框架主体121之间出现分层变形的现象。

104.完成框架安装后,在所述第二导电层113上焊接引脚160。

105.s30:形成具有第二嵌体132以及第三嵌体136的顶盖130,并且在所述框架120的第一端,将所述第一嵌体122与所述第二嵌体132焊接在一起。

106.本实施例中,在所述第二嵌体132以及第三嵌体136周围,使用热塑性材料模制成型,形成包裹所述第二嵌体132的顶盖主体131。

107.所述顶盖130上开设有第一通孔133,所述第一通孔133用于供所述引脚160穿过,以使得所述引脚160的一端延伸至所述半导体封装结构100外部。在所述顶盖130的第二表面(即覆盖所述第一填充层171的表面),所述第一通孔133的外壁从所述顶盖130的第二表面向着远离所述顶盖130第二表面的方向延伸。所述顶盖主体131的中心区域开设有第二通孔134和第三通孔135,所述第二通孔134与第三通孔135同心且相互连通,其中,所述第二通孔134位于靠近所述框架主体131第二表面的一侧,所述第三通孔135位于靠近所述框架主体131第一表面的一端,所述第二通孔134和所述第三通孔135相互连通,并且贯穿所述顶盖

主体131。在所述顶盖130的第二表面,所述第二通孔134的外壁从所述顶盖130的第二表面向着远离所述顶盖130第二表面的方向延伸。在与所述第三通孔135连通的一端,所述第二通孔134的外壁外侧嵌有环状的第三嵌体136,所述第三嵌体暴露于所述第三通孔135的底部。

108.进一步地,在所述顶盖130的第二表面上形成第一填充层171。其中,在所述顶盖主体131的第二表面,所述第二嵌体132围绕所述第一填充层171,且不与所述第一填充层171接触。在形成所述第一填充层171的过程中,所述第一通孔133延伸出所述顶盖130第二表面的部分通孔外壁以及所述第二通孔134延伸出所述顶盖130第二表面的部分通孔外壁对形成所述第一填充层171的材料进行阻挡,以防止形成所述第一填充层171的材料对所述第一通孔133以及第二通孔134进行封堵。

109.进一步地,在所述框架120的第一端,将所述框架120以及所述顶盖130焊接在一起。具体地,所述第二嵌体132和所述第一嵌体122之间使用焊锡膏低温回流焊接,焊接温度在200℃以下,以防止所述第二嵌体132和所述顶盖本体131之间出现分层变形的现象。

110.具体地,在所述底板110、框架120以及所述顶盖130组合在一起后,所述引脚160的一端与所述第二导电层113电连接,另一端从所述第一通孔133穿过,经过所述第一通孔133延伸至所述半导体封装结构100外部。其中,所述第一通孔133的直径大于等于所述引脚160的直径,以使得所述引脚160能够穿过所述第一通孔133。

111.s40:经由所述第二通孔134向所述空腔140内灌注填充材料,以形成第二填充层172。其中,所述第二填充层172包覆所述半导体器件150、所述键合线115以及部分的所述引脚160。所述第二填充层172为软性填充材料,例如为硅酮胶、硅橡胶等。所述第二填充层172的高度大于所述半导体器件150的高度,且所述第二填充层172不与所述第一通孔133以及所述第二通孔134延伸至所述空腔140内部的端面接触。

112.进一步地,所述第二填充层172与所述第一填充层171之间具有间隙,该间隙为缓冲区,所述缓冲区内的空气用来稀释通过所述第一通孔133、第二通孔134以及第三通孔135扩散进入所述空腔140内的腐蚀性气体,并且扩大稀释后的腐蚀性气体与第一填充层171的接触面积,由于腐蚀性气体在第一填充层171中的溶解度比在第二填充层172中的溶解度大,进入所述空腔140的腐蚀性气体将更易被第一填充层171吸收。

113.进一步地,在向所述空腔140内灌注填充材料以形成第二填充层172之后,向所述第一通孔133的内壁与所述引脚160的外壁之间灌注填充材料,以形成第三填充层173,所述第三填充层173包裹于所述引脚160的周围。

114.s50:在所述第三通孔135内安装密封板180,以对所述第二通孔134靠近所述第三通孔135的一端端口进行封堵。具体地,所述密封板180置于所述第三通孔135内,并且与暴露于所述第三通孔135的底部的第三嵌体136密封连接,以实现对所述第二通孔134的封堵。所述密封板180例如为金属板,通过焊接与所述第三嵌体136密封连接。

115.进一步地,在所述框架120和所述顶盖130之间使用弹性胶174(例如,玻璃胶等)连接,用于吸收外部的拉应力,缓解第二嵌体132与所述第一嵌体122焊点的应力蠕变老化。

116.图5示出了本发明第二实施例的半导体封装结构的截面图;如图5所示,所述半导体封装结构200包括底板210、框架220和顶盖230,所述底板210、框架220和顶盖230组合在一起后在所述半导体封装结构200的内部形成空腔240,半导体器件250(或半导体芯片)封

装于底板210、框架220和顶盖230围成的空腔240内。

117.本实施例中,所述底板210包括基板211以及覆盖于所述基板211第二表面的第一导电层212以及覆盖于所述基板211第一表面的第二导电层213,所述第一导电层212呈板状。本实施例的第一导电层212一方面用于实现与所述框架220的密封连接,另一方面对所述基板211进行支撑,并且所述第一导电层212能够对经过所述第一导电层212传导的电磁波进行衰减,具有一定的电磁屏蔽作用。所述第二导电层213用于实现半导体器件250的固定以及导电连接。所述基板211例如为覆铜陶瓷基板(dbc),所述第一导电层212例如为金属导电层,所述第二导电层213为覆盖于所述基板211第一表面的铜导电层。

118.所述半导体器件250位于所述底板210的第一表面,所述半导体器件250经由连接层214和/或键合线215与所述基板211第一表面的第二导电层213电连接。所述第二导电层213上还通过键合线215连接有引脚260,所述半导体器件250经由第二导电层213以及所述引脚260与外界实现电连接。其中,所述连接层214例如为软焊料、银浆等,还可以为绝缘胶;所述键合线215例如铜线、银线等。

119.进一步地,所述第一导电层212的面积大于所述基板211的面积,以使得所述第一导电层212与所述框架220密封连接之后,所述基板211被封装于所述空腔240内部。

120.所述框架220包括框架主体221以及嵌于所述框架主体221内部的第一嵌体。本实施例中,所述第一嵌体包括分体设置的第一嵌体2221和第一嵌体2222,所述第一嵌体2221和第一嵌体2222分别位于所述框架主体221的两端,其中,所述第一嵌体2221暴露于所述框架主体221的第二端的表面,所述第一嵌体2222暴露于所述框架主体221的第一端的表面,所述第一嵌体2221和所述第一嵌体2222之间通过框架主体221进行隔离。其中,所述框架主体221采用热塑性材料(例如pbt材料、tpu材料等)模制成型,所述第一嵌体222采用金属材料(例如铜)冲压成型。

121.所述引脚260嵌于所述框架主体221内部。所述引脚260的一端暴露于所述空腔240内部,并且经由键合线215与所述基板211上的第二导电层213电连接,另一端延伸至所述框架主体221的外部。

122.具体地,本实施例中,所述引脚260呈l型,l型的引脚260的一端在所述框架主体221的内侧壁暴露于所述空腔240内部,l型的引脚260的另一端在所述框架主体221的第一端的表面延伸至所述框架主体221的外部。所述第一嵌体2221与所述引脚260之间具有一定的间隙,且经由框架主体221绝缘隔离,所述第一嵌体2222与所述引脚260之间具有一定的间隙,且经由框架主体221绝缘隔离。

123.进一步地,所述第一嵌体2221与所述引脚260之间的距离d4应满足:

124.d4》u

operation

/e

breakdown-plastic

125.所述第一嵌体2222与所述引脚260之间的距离d5应满足:

126.d5》u

operation

/e

breakdown-plastic

127.其中,u

operation

为半导体器件250的工作电压,e

breakdown-plastic

为框架主体221材料的击穿电场强度。

128.本实施例中,所述第一嵌体2221和所述第一嵌体2222只位于所述框架主体221的两个端面处,所述第一嵌体2221和所述第一嵌体2222之间为绝缘性的框架主体221,一方面提升所述框架220的绝缘性,另一方面为引脚260的设置提供了空间。

129.所述顶盖230包括顶盖主体231以及嵌于所述顶盖主体231内部的第二嵌体232,所述顶盖主体231呈板状,所述第二嵌体232呈环状,所述顶盖主体231和所述第二嵌体232构成板状的顶盖230。所述第二嵌体232暴露于所述顶盖主体231的第二表面。所述顶盖主体231采用热塑性材料(例如pbt材料、tpu材料等)模制成型,所述第二嵌体232采用金属材料(例如铜)冲压成型。其中,所述顶盖主体231的厚度大于所述第二嵌体232的厚度,以使得所述第二嵌体232只暴露于所述顶盖主体231的第二表面。

130.所述第二嵌体232顶端与所述顶盖主体231的第一表面的距离d6应满足:

131.d6》u

operation

/e

breakdown-air-d5132.其中,u

operation

为半导体器件250的工作电压,e

breakdown-air

为空气中的击穿电场强度。

133.所述顶盖主体231的第二表面上覆盖有第一填充层271,在所述顶盖主体231的第二表面,所述第二嵌体232围绕所述第一填充层271,且不与所述第一填充层271接触。所述第一填充层271例如为含有金属氧化物粉末的软性填充材料,其中,金属氧化物例如为氧化铜、氧化锌、氧化铝等,软性填充材料例如为硅凝胶等。所述第一填充层271对腐蚀性气体进行吸收。

134.第二填充层272包覆所述半导体器件250、所述键合线215以及部分的所述引脚260,并覆盖所述第二导电层213的表面,以吸收机械冲击能量并阻挡腐蚀性气体扩散。所述第二填充层272为软性填充材料,例如为硅酮胶、硅橡胶等。所述第二填充层272的高度大于所述半导体器件250的高度。

135.在所述底板210、框架220和顶盖230组合在一起后,所述第二填充层272与所述第一填充层271均位于所述空腔240内,且所述第二填充层272与所述第一填充层271之间具有间隙,该间隙为缓冲区,所述缓冲区内的空气用来稀释扩散进入所述空腔240内的腐蚀性气体,并且扩大稀释后的腐蚀性气体与第一填充层271的接触面积,由于腐蚀性气体在第一填充层271中的溶解度比在第二填充层272中的溶解度大,进入所述空腔240的腐蚀性气体将更易被第一填充层271吸收。

136.本实施例中,所述第一导电层212为板状,所述第一嵌体2221、2222以及所述第二嵌体232均为环状,在所述框架主体221的第二端,所述第一嵌体2221与所述第一导电层212焊接密封连接,在所述框架主体221的第一端,所述第一嵌体2222与所述顶盖230的第二嵌体232焊接密封连接,以使得所述底板210、框架220和顶盖230围成密封的空腔240,确保底板210和框架220的连接处以及框架220和顶盖230的连接处不存在气体扩散通路,杜绝了腐蚀性气体由分体部件的连接处扩散进入空腔240内。

137.其中,所述基板211被封装于所述空腔240内部;且所述基板211的侧壁与所述第一嵌体2221的侧壁之间具有间隙。进一步地,所述基板211的侧壁与所述第一嵌体2221的侧壁经由绝缘的所述第二填充层272和/或所述框架主体221绝缘隔离。

138.进一步地,本实施例中,在所述框架220的第二端,所述框架主体221包覆所述基板211的外侧壁,便于所述底板210的对准安装。

139.所述第一导电层212和所述第一嵌体2221外部还可以通过螺钉或者胶进行固定,所述顶盖主体231还可以通过所述卡扣或者螺钉进行固定,以增加连接强度。

140.本实施例中,形成所述半导体封装结构的方法包括:

141.s100:提供所述基板211,其中,所述基板211的第一表面具有第二导电层213。将半导体器件250固定于所述第二导电层213上。其中,所述半导体器件250分别经由连接层214以及键合线215与所述第二导电层213电连接,所述连接层214的材料为例如为软焊料、银浆等,还可以为绝缘胶;所述第二导电层213为覆盖于所述基板211第一表面的铜导电层,所述键合线215例如铜线、银线等。即所述半导体器件250分别经由连接层214以及键合线215焊接于所述第二导电层213上。

142.s200:完成键合后,将第一导电层212与所述基板211的第二表面焊接在一起,所述第一导电层212的面积大于所述底板210的面积,以使得所述第一导电层212与所述框架220密封连接之后,所述基板211被封装于所述空腔240内部,其中,所述第一导电层212呈板状,例如为金属导电层。

143.s300:形成具有第一嵌体以及引脚260的框架220,并且在所述框架220的第二端,将所述第一嵌体2221与所述第一导电层212焊接在一起,在所述空腔240内,将所述引脚260与所述第二导电层213电连接。

144.本实施例中,在所述第一嵌体以及引脚260的周围,使用热塑性材料模制成型,以形成包裹所述第一嵌体以及引脚260的框架本体221。

145.本实施例中,所述第一嵌体包括分体设置的第一嵌体2221和第一嵌体2222,所述第一嵌体2221和第一嵌体2222分别位于所述框架主体221的两端,其中,所述第一嵌体2221暴露于所述框架主体221的第二端表面,所述第一嵌体2222暴露于所述框架主体221的第一端表面,所述第一嵌体2221和所述第一嵌体2222之间通过框架主体221进行隔离。其中,所述框架主体221采用热塑性材料(例如pbt材料、tpu材料等)模制成型,所述第一嵌体222采用导电材料(例如铜)。

146.所述引脚260的一端暴露于所述空腔240内部,另一端延伸至所述框架主体221的外部。本实施例中,所述引脚260呈l型,l型引脚260的一端在所述框架主体221的内侧壁暴露于所述空腔240内部,l型引脚260的另一端在所述框架主体221的第一端表面延伸至所述框架主体221的外部。所述第一嵌体2221与所述引脚260之间具有一定的间隙,且经由框架主体221绝缘隔离,所述第一嵌体2222与所述引脚260之间具有一定的间隙,且经由框架主体221绝缘隔离。

147.进一步地,所述第一导电层212和所述第一嵌体2221之间使用焊锡膏低温回流焊接,焊接温度在200℃以下,以防止所述第一嵌体2221和所述框架主体221之间出现分层变形的现象。

148.进一步地,将所述引脚260暴露于所述空腔240内的一端经由键合线215与所述基板211上的第二导电层213电连接。

149.进一步地,灌注填充材料以形成第二填充层272。其中,所述第二填充层272包覆所述半导体器件250、所述键合线215以及部分的所述引脚260。所述第二填充层272为软性填充材料,例如为硅酮胶、硅橡胶等。所述第二填充层272的高度大于所述半导体器件250的高度。

150.s400:形成具有第二嵌体232的顶盖230,并且在所述框架220的第一端,将所述第一嵌体2222与所述第二嵌体232焊接在一起。

151.本实施例中,在所述第二嵌体232周围,使用热塑性材料模制成型,形成包裹所述

第二嵌体232的顶盖主体231。

152.进一步地,在所述顶盖230的第二表面上形成第一填充层271。其中,在所述顶盖主体231的第二表面,所述第二嵌体232围绕所述第一填充层271,且不与所述第一填充层271接触。

153.进一步地,在所述框架220的第一端,将所述框架220以及所述顶盖230焊接在一起。具体地,所述第二嵌体232和所述第一嵌体2222之间使用焊锡膏低温回流焊接,焊接温度在200℃以下,以防止所述第二嵌体232和所述顶盖本体231之间出现分层变形的现象。

154.本发明提供的半导体封装结构包括底板、框架和顶盖,且所述框架的两端分别与所述底板以及所述顶盖经由焊接密封连接,使得所述底板、框架和顶盖的连接处不存在气体扩散通路,保证了所述半导体封装结构的密封性,有效防止腐蚀性气体(例如硫化氢、盐酸等)由底板、框架和顶盖的连接处扩散进入空腔内,避免所述半导体封装结构内部的半导体器件或半导体芯片受到腐蚀性气体的腐蚀,保证所述半导体器件或半导体芯片的正常工作。

155.进一步地,所述框架和所述顶盖均采用绝缘性主体包覆金属嵌体的结构。一方面,金属嵌体能够实现所述半导体封装结构的焊接密封,绝缘性主体包覆金属嵌体,能够避免金属嵌体在腐蚀性环境中被腐蚀;另一方面,所述绝缘性主体能提高金属嵌体与所述半导体封装结构内部的其他导电结构之间的绝缘性隔离,能够有效阻止晶枝在空腔内生长,进一步防止产生导电通路。

156.在优选地实施例中,所述第一导电层和所述第二导电层共同位于所述基板的第一表面,且所述第一导电层与所述第二导电层之间具有间隙,以降低引入的第一导电层影响产品的耐压特性的风险。

157.在优选的实施例中,所述第一导电层和所述第二导电层位于所述基板相对的两个表面,所述第一导电层一方面用于实现与所述框架的密封连接,另一方面实现对所述基板进行支撑,并且所述第一导电层能够对经过所述第一导电层传导的电磁波进行衰减,具有一定的电磁屏蔽作用。

158.在优选的实施例中,所述第一嵌体为一体结构,贯穿所述框架的高度方向,方便加工。

159.在优选地实施例中,所述第一嵌体包括分体的两部分,分体的两部分第一嵌体之间为绝缘性的框架主体,一方面提升所述框架的绝缘性,另一方面为引脚的设置提供了空间。

160.在优选的实施例中,在所述顶盖的第二表面,所述第一通孔的侧壁向所述空腔内延伸,防止伸入所述空腔内部的所述第一通孔的侧壁发生击穿,且所述第一通孔和所述引脚之间填充有第三填充层,以减小腐蚀性气体分子的扩散速度。

161.在优选的实施例中,在顶盖主体的第二表面覆盖有第一填充层,第一填充层为含有金属氧化物粉末的软性填充材料,对所述空腔内的腐蚀性气体进行吸收,避免半导体器件被腐蚀。

162.在优选的实施例中,所述第二填充层与所述第一填充层之间具有间隙,该间隙为缓冲区,所述缓冲区内的空气用来稀释通过所述第一通孔扩散进入所述空腔内的腐蚀性气体,并且扩大稀释后的腐蚀性气体与第一填充层的接触面积,由于腐蚀性气体在第一填充

层中的溶解度比在第二填充层中的溶解度大,进入所述空腔的腐蚀性气体将更易被第一填充层吸收。

163.在优选地实施例中,在顶盖上开设第二通孔,并且在第二通孔上增加密封板,且所述密封板与所述顶盖中的第三嵌体之间通过焊接密封连接,阻挡腐蚀性气体的扩散通路。

164.依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1