一种3D芯片的封装方法与流程

一种3d芯片的封装方法

技术领域

1.本发明涉及半导体封装技术领域,用于第二代半导体砷化镓、磷化铟等易碎的半导体芯片,其应用领域为微波射频芯片的3d封装和光纤通信的多芯片模块的立体封装,实现多功能、小型化。

背景技术:

2.芯片制造就是按照芯片布图,在大电阻率硅晶圆上逐层制做材料介质层的过程,为了节省面积,提升封装模块的多功能、小型化封装水平,在多芯片封装时,可以在基板的电路层制作完成之后,继续在其上制做另一层电路层,使之形成两个、甚至多个电路层在大电阻率硅晶圆上的堆叠,这样的堆叠形成被称之为3d芯片的封装。

3.现有的3d芯片在封装时,由于这种封装技术,是以第一个建立在基板上的电路层上的进行堆叠的,因此对半导体基板的强度要求要远比以往的要高,而传统的封装步骤中,并未存在对半导体基板进行加强处理的步骤,因此在加工时需要提前对半导体基板进行加强处理,这样的设置耽误了实际封装进程,为此本技术提出一种新型处理方式,在不耽误封装进程的情况下,完成对半导体基板的加强处理,实现多芯片封装的多功能、小型化及立体功能。

技术实现要素:

4.本发明的目的在于提供一种3d芯片的封装方法,以解决上述背景技术中提出的问题。

5.为实现上述目的,本发明提供如下技术方案:一种3d芯片的封装方法,包括以下步骤:

6.步骤一、设计制造3d芯片模具;

7.步骤二、在3d芯片模具的内部开设凹槽,并在凹槽内放置半导体芯片基板;

8.步骤三、将3d芯片模具连带半导体芯片基板一同移动到光刻机处进行光刻工艺,并在半导体芯片基板上形成装配槽;

9.步骤四、在半导体芯片基板上的装配槽内贴装电路元器件芯片;

10.步骤五、在贴装后的电路元器件上芯片固定大电阻率硅晶圆,并在硅晶圆上继续焊接电路元器件芯片;

11.步骤六、往3d芯片模具的内部填充低温惰性气体,并将其放入到加热炉内升温处理,温度范围100度到300度可调,根据不同种类芯片的物理特性确定温度范围。

12.更进一步地,步骤六中的惰性气体为氩气,氦气或氖气中的一种,且填充的时间为15min~20min。

13.更进一步地,步骤三中光刻机的光源为激光,其波长为175nm~480nm,激光的脉冲能量密度在350mj/

㎝2~520mj/

㎝2,刻蚀时间为3s~6s,激光入射角度为0

°

~45

°

。

14.更进一步地,步骤四中的电路元器件的结构为平躺放置结构,步骤五中的硅晶圆

是叠放固定在电路元器件的顶端。

15.更进一步地,步骤一中的3d芯片模具包括储放座,储放座外部的一端固定连接有转动座,储放座外部的另一端固定连接有卡接座,所述储放座顶部的中心点位置处开设有密封槽,步骤二处的凹槽设置在所述密封槽的内部。

16.更进一步地,所述转动座的外部转动连接有装配块,装配块外部的一端固定连接有铰接座,铰接座的外部转动连接有卡扣,卡扣在转动时和挂置在所述卡接座的外部。

17.更进一步地,所述装配块的底部固定连接有密封罩,密封罩的底端在所述装配块转动时和密封槽的内部相接触。

18.更进一步地,所述装配块的内部开设连通缺口,装配块在连通缺口的内部插接有压合组件,所述装配块和储放座接触时,压合组件的输出端和放置在储放座内的所述半导体芯片基板的顶部相接触。

19.更进一步地,所述储放座顶部一侧的两端分别开设有放置槽,所述装配块内部的两端分别固定连接有注气筒,注气筒和放置槽相适配。

20.更进一步地,所述注气筒末端的一侧固定连接有透气管,所述注气筒的内部和透气管的内部相连通。

21.与现有技术相比,本发明的有益效果是:

22.该3d芯片的封装方法,通过向半导体芯片基板填充惰性气体,使得半导体芯片基板在3d芯片模具内发生反应,消除了半导体芯片基板内部的热应力,有效减少了半导体芯片基板在冷却过程中的热应力,并修复半导体芯片基板在贴装过程中引入的应力缺陷,提高产品的整体强度,提升第二代半导体砷化镓、磷化铟等易碎的半导体芯片的3d封装水平,在微波射频芯片的3d封装和光纤通信的多芯片模块的立体封装领域,实现多功能、小型化及立体功能。

附图说明

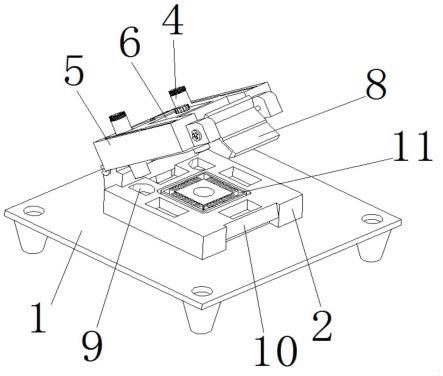

23.图1为本发明3d芯片模具的斜轴测图;

24.图2为本发明3d芯片模具的等轴测图;

25.图3为3d芯片模具上装配块内部结构图;

26.图4为本发明3d芯片模具上压合组件的结构组成图。

27.图中:1、放置台;2、储放座;3、转动座;4、注气筒;5、装配块;6、压合组件;601、连接块;602、挤压板;603、压力弹簧;604、受力凸起;7、铰接座;8、卡扣;9、放置槽;10、卡接座;11、密封槽;12、密封罩;13、透气管。

具体实施方式

28.芯片制造就是按照芯片布图,在大电阻率硅晶圆上逐层制做材料介质层的过程,为了节省面积,提升封装模块的多功能、小型化封装水平,在多芯片封装时,可以在基板的电路层制作完成之后,继续在其上制做另一层电路层,使之形成两个、甚至多个电路层在大电阻率硅晶圆上的堆叠,这样的堆叠形成被称之为3d芯片的封装。

29.现有的3d芯片在封装时,由于这种封装技术,是以第一个建立在基板上的电路层上的进行堆叠的,因此对半导体基板的强度要求要远比以往的要高,而传统的封装步骤中,

并未存在对半导体基板进行加强处理的步骤,因此在加工时需要提前对半导体基板进行加强处理,这样的设置耽误了实际封装进程,为此本技术提出一种新型处理方式,在不耽误封装进程的情况下,完成对半导体基板的加强处理,其中需要补充的是,该处理方式包括以下步骤:

30.步骤一、设计制造3d芯片模具;

31.步骤二、在3d芯片模具的内部开设凹槽,并在凹槽内放置半导体芯片基板;

32.步骤三、将3d芯片模具连带半导体芯片基板一同移动到光刻机处加工光刻,并在半导体芯片基板上形成装配槽;

33.步骤四、在半导体芯片基板上的装配槽内焊接电路元器件;

34.步骤五、在焊接后的电路元器件上固定硅晶圆,并在硅晶圆上继续焊接电路元器件;

35.步骤六、往3d芯片模具的内部填充低温惰性气体,并将其放入到加热炉内升温处理。

36.需要补充的是,在本技术中,步骤六中的惰性气体为氩气,氦气或氖气中的一种,且填充的时间为15min~20min。

37.需要注意的是,本方案中的处理方式是通过采用加热的方式实现对半导体芯片基板的晶相修复,其中在热处理过程中还会通入预设量的惰性气体(如氩气)及微量的还原性气体(如氢气),以避免沟槽表面被氧化,其中需要补充但是,加热过程通常在10min~20min,此外需要强调的是,加热处理可以修复3d芯片模具在贴装过程中引入的应力缺陷,提高产品的整体强度,完成第二代半导体砷化镓、磷化铟等易碎的半导体芯片的3d封装,在微波射频芯片的3d封装和光纤通信的多芯片模块的立体封装领域,实现多功能、小型化及立体功能。

38.需要补充的是,该实施例通过让半导体的加热阶段在具有一定的真空度的封闭环境下进行,使得半导体在无外界压力的情况下加热与冷却,这样半导体主要靠辐射形式进行热传导散热,并且在散热的过程中,能够使得半导体的表面与内部中心之间的温度及半导体的头部与尾部之间的温度更加的均匀,避免出现半导体表面与内部的温度在散热过程中不均匀的现象,从而可以大大减少半导体的内部的热应力。

39.还需要补充的是,在升温处理后还可以将3d芯片模具放置到氮气柜内静置散热过程中,使得半导体的温度稳定在100~300℃,这样的设置消除了半导体芯片基板的内部的热应力,有效消除半导体芯片基板在冷却过程中的热应力现象,加强了半导体芯片基板的整体强度。

40.此外需要注意的是,步骤三中光刻机的光源为激光,其波长为175nm~480nm,激光的脉冲能量密度在350mj/

㎝2~520mj/

㎝2,刻蚀时间为3s~6s,激光入射角度为0

°

~45

°

,需要强调的是,在本技术提供的实施例中,光刻机为现阶段成熟的技术装置,具体型号为湖南艾科威智能装配有限公司生产的离子束刻蚀机,其中补充的是,该机器在本技术中产生的激光还可以是以下参数,其中波长为180nm~500nm,其中激光的脉冲能量密度在380mj/

㎝2~550mj/

㎝2,其中半导体刻蚀机在半导体模具上刻蚀时间为3s~8s,其中半导体刻蚀机的激光入射角度为0

°

~60

°

,其中激光入射角度为入射角度为半导体刻蚀机激光与半导体模具竖直方向上之间形成的夹角度数,此外需要强调的是,在本技术中半导体刻蚀机具体刻

蚀时长也可以根据实际需要进行调整。

41.步骤四中的电路元器件的结构为平躺放置结构,步骤五中的大电阻率硅晶圆是叠放固定在电路元器件的顶端。

42.参考图1-图4可知,步骤一中的3d芯片模具包括储放座2,储放座2外部的一端固定连接有转动座3,储放座2外部的另一端固定连接有卡接座10,储放座2顶部的中心点位置处开设有密封槽11,步骤二处的凹槽设置在密封槽11的内部。

43.需要说明的是,在本技术中储放座2的底部固定连接有放置台1,其中放置台1起到了稳定的作用。

44.此外需要说明的是,在本技术中转动座3的外部转动连接有装配块5,其中装配块5具有以下特征:

45.特征一、装配块5外部的一端固定连接有铰接座7,其中铰接座7的外部转动连接有卡扣8,卡扣8在转动时和挂置在卡接座10的外部,其中需要注意的是,在本技术中卡扣8的整体结构可以参考图1和图2。

46.特征二、装配块5的底部固定连接有密封罩12,密封罩12的底端在装配块5转动时和密封槽11的内部相接触,其中参考图3可知,密封罩12外部的一侧开设有缺口,其中该缺口起到了连通惰性气体的作用。

47.特征三、装配块5的内部开设连通缺口,装配块5在连通缺口的内部插接有压合组件6,装配块5和储放座2接触时,压合组件6的输出端和放置在储放座2内的半导体芯片基板的顶部相接触。

48.其中参考图4可知,在本技术中压合组件6包括连接块601,其中连接块601设置在连通缺口池,连接块601的底端安装有压力弹簧603,压力弹簧603的底部固定有挤压板602,其中挤压板602和半导体芯片基板的背板相接触,此外需要注意的是,在本技术中半导体芯片基板的信号输出端为针脚端,参考图2可知,密封槽11处还设置有针脚槽,通过针脚槽的设置,使得半导体芯片基板能够更稳定的放置在储放座2的内部。

49.此外还需要注意的是,在本技术中储放座2顶部一侧的两端分别开设有放置槽9,装配块5内部的两端分别固定连接有注气筒4,注气筒4和放置槽9相适配,需要补充的是,参考图3可知,注气筒4末端的一侧固定连接有透气管13,注气筒4的内部和透气管13的内部相连通,本装置在实际使用时,通过注气筒4出填充惰性气体,使得惰性气体沿透气管13排放到储放座2的内部,在通过密封罩12上缺口和半导体芯片基板的背板相接触,此外在进行加工处理时,可以通过用手拉动受力凸起604来实现压合组件6和装配块5的分离。

50.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1