具有阻隔区的场效应晶体管器件

本发明属于半导体器件,具体是关于一种具有阻隔区的场效应晶体管器件。

背景技术:

1、随着集成电路技术的发展,场效应晶体管的栅长(对应沟道长度)在不断缩小,目前基于亚微米甚至10纳米以下栅长器件的vlsi芯片已经量产。对于这类小尺寸器件,如何应对其短沟道效应是器件技术的重要挑战。短沟道效应使得小尺寸器件的阈值电压和亚阈值特性全面劣化,具体表现为器件阈值电压不再是常数,而是随沟道长度的减小而降低,并随器件漏端电压的增加而降低;器件转移特性的亚阈值摆幅也同时劣化。

2、目前改善场效应晶体管器件短沟道效应的方法主要包括鳍式场效应晶体管finfet,绝缘层上硅soi、轻掺杂漏(ldd)结构和金属源漏肖特基势垒晶体管(sbmosfet)等。①finfet的沟道区为3d鳍型薄片,栅极是三面围栅结构,两个侧栅增强了栅极对沟道的控制,有效地抑制了短沟道效应,该方案中器件制备工艺较平面型器件复杂得多,目前22nm以下技术节点的芯片较多采用finfet方案。②soi技术,在硅沟道层和背衬底之间引入埋氧化层,在沟道层很薄全耗尽的条件下,可以有效抑制源漏之间的泄漏电流,该方案的难点在于soi硅片的成本非常高,目前基于soi方案的10纳米级技术节点的芯片也已经量产。③轻掺杂漏ldd设置于漏端沟道附近而远离沟道的源漏区域仍然是重掺杂,该轻掺杂区形成的漏端pn结减小了漏端电压对于沟道的影响,是亚微米级短沟道器件的主流技术方案,该方案中器件的开态电流和场效应迁移率受到ldd影响均有一定程度的下降。④肖特基势垒晶体管的工作电流为金属源极与半导体沟道间肖特基势垒的隧穿电流,对短沟道效应不敏感,该方案工艺难度比较大,势垒材料的选择有限而且很难兼顾对于器件关态电流的抑制。

3、另一方面,短沟道器件的输出特性曲线上出现的kink效应也受到很多关注。器件工作于饱和工作状态时,较高的漏极电压使得器件漏端耗尽并形成高电场区,载流子在此容易发生碰撞离化效应,并与mos器件寄生的双极型晶体管耦合放大,使漏极电流随漏极电压增大而迅速增加,形成所谓的kink电流,器件的输出特性曲线大幅度翘曲,严重影响正常的输出特性。

4、常用的改善kink效应的方法主要包括增加器件沟道长度和轻掺杂漏(ldd)结构。增加沟道长度可以减小漏端碰撞离化产生的载流子对于源端的影响,削弱寄生晶体管效应并缓解kink效应。但是沟道长度增加会相应的降低器件的输出电流。ldd结构可以降低漏端耗尽区内的峰值电场强度,减弱载流子碰撞离化效应,从而抑制kink效应,但是ldd结构会引入额外的寄生电阻,降低器件的场效应迁移率和开态电流。

5、公开于该背景技术部分的信息仅仅旨在增加对本技术的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本技术的目的在于提供一种场效应晶体管器件,其用于解决现有技术场效应晶体管短沟道效应的问题。

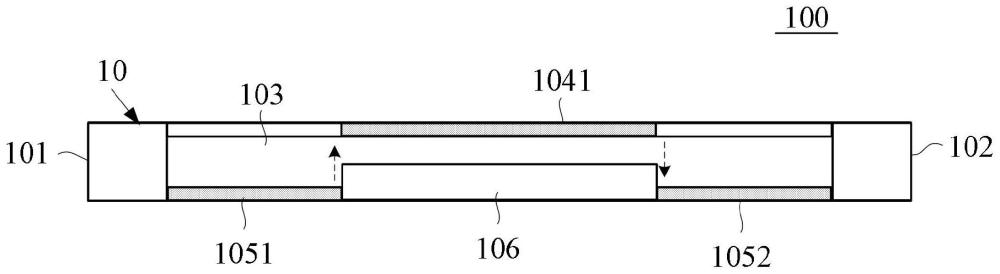

2、为实现上述目的,本技术提供了一种具有阻隔区的场效应晶体管器件,包括有源层,所述有源层包括源极区域、漏极区域以及位于所述源极区域和漏极区域之间的沟道区域;

3、当器件开启时,所述沟道区域内形成有有效沟道、以及至少在所述沟道区域的厚度方向上远离所述有效沟道的等效源区和/或等效漏区,所述场效应晶体管器件通过所述有效沟道、以及等效源区和/或等效漏区连通所述源极区域和漏极区域以贡献工作电流;

4、其中,所述场效应晶体管包括载流子阻隔区,在与所述有效沟道长度方向垂直的平面上,所述等效源区和等效漏区的垂直投影位于所述载流子阻隔区的垂直投影之内。

5、一实施例中,所述沟道区域中形成有不连通所述源极区域和漏极区域的导电区;其中,

6、当所述导电区与所述源极区域连通时,所述导电区构成所述等效源区;和/或,

7、当所述导电区与所述漏极区域连通时,所述导电区构成所述等效漏区。

8、一实施例中,包括设置于所述有源层一侧表面上的第一栅极,所述第一栅极和所述导电区在所述沟道区域上的垂直投影有交叠;其中,所述第一栅极可控制所述沟道区域并于其中形成沟道,所述沟道中与所述导电区在所述沟道区域上垂直投影之间不交叠的部分构成所述有效沟道。

9、一实施例中,当器件开启时,所述导电区的电导大于所述沟道中除有效沟道外其余部分的电导,以使所述导电区和有效沟道的至少其中之一可向其中另一注入载流子。

10、一实施例中,所述导电区的电导至少大于所述沟道中除有效沟道外其余部分电导的三倍。

11、一实施例中,所述场效应晶体管器件为平面结构器件或垂直结构器件。

12、一实施例中,当器件开启时,所述沟道中有效沟道的单位长度电导小于所述沟道中除有效沟道外其余部分的单位长度电导。

13、一实施例中,所述场效应晶体管器件包括设置于所述第一栅极和沟道区域之间的栅绝缘层,其中,所述栅绝缘层中与所述有效沟道对应部分的厚度大于其余部分栅绝缘层的厚度。

14、一实施例中,所述场效应晶体管器件包括设置于所述第一栅极和沟道区域之间的栅绝缘层,其中,所述栅绝缘层中与所述有效沟道对应部分的介电常数大于其余部分栅绝缘层的介电常数。

15、一实施例中,当所述场效应晶体管器件为n型器件时,所述第一栅极中与所述有效沟道对应部分的功函数大于所述第一栅极的其余部分的功函数;

16、当所述场效应晶体管器件为p型器件时,所述第一栅极中与所述有效沟道对应部分的功函数小于所述第一栅极的其余部分的功函数。

17、一实施例中,所述载流子阻隔区与沟道区域的接触界面形成势垒,所述势垒用于阻止载流子进入所述载流子阻隔区。

18、一实施例中,所述载流子阻隔区为绝缘区或半绝缘区;

19、一实施例中,所述载流子阻隔区的介电常数小于所述沟道区域的介电常数。

20、一实施例中,所述载流子阻隔区、以及所述等效源区和/或等效漏区在所述沟道区域上的垂直投影没有交叠。

21、一实施例中,所述载流子阻隔区与所述等效源区远离源极区域的一端接触。

22、一实施例中,所述载流子阻隔区与所述等效漏区远离漏极区域的一端接触。

23、一实施例中,所述载流子阻隔区为在所述沟道区域的开槽中填充的介质材料。

24、一实施例中,所述载流子阻隔区为在所述沟道区域中离子注入或掺杂形成的绝缘区或半绝缘区。

25、一实施例中,所述载流子阻隔区为形成在衬底上的介质材料,所述有源层在形成有所述介质材料的的衬底上制备所得。

26、一实施例中,还包括设置于所述有源层临近导电区一侧表面的第二栅极,所述第二栅极可控制所述沟道区域中形成所述导电区。

27、一实施例中,所述导电区由所述沟道区域在远离所述有效沟道一侧表面掺杂引入的载流子形成。

28、一实施例中,还包括设置于所述有源层远离所述有效沟道一侧表面的绝缘层,所述导电区由所述绝缘层中的注入电荷通过静电感应在所述沟道区域临近绝缘层处生成的载流子构成。

29、一实施例中,还包括设置于所述有源层远离所述有效沟道一侧表面的半导体材料层,所述有源层与所述半导体材料层形成异质结构,所述导电区由分布于所述异质结构中的二维电子气沟道或二维空穴气沟道构成。

30、一实施例中,所述导电区由对所述沟道区域远离所述有效沟道的一侧表面进行表面处理形成的二维电子气沟道或二维空穴气沟道构成。

31、与现有技术相比,本技术的实施方式中,通过将器件设置成在开启时,能够于沟道区域中形成有效沟道、以及沟道区域厚度方向上远离有效沟道的等效源区和等效漏区,从而连通源极区域和漏极区域以贡献工作电流;这样,与漏极(源极)区域连通的等效漏区(源极)在结构上远离有效沟道,可以减小漏端电压对有效沟道的影响;并减小了器件饱和工作时漏端耗尽区内的峰值电场,从而抑制了器件的短沟道效应,并改善了器件的输出特性;同时,通过设置载流子阻隔区,使得在有效沟道长度方向垂直的平面上,等效源区和等效漏区的垂直投影位于载流子阻隔区的垂直投影之内,可以阻断载流子从等效源区直接注入等效漏区,从而减少器件的关态电流。

- 还没有人留言评论。精彩留言会获得点赞!