半导体装置及其制造方法与流程

半导体装置及其制造方法

1.本技术是申请日为2019年08月30日、申请号为201910816918.6、发明名称为“半导体装置”的专利申请的分案申请。

技术领域

2.本揭露是关于一种半导体装置的半导体结构及其制造方法,且特别是一种具两斜度接触开口的半导体结构及其制造方法。

背景技术:

3.在半导体装置,当导电材料是直接或者透过薄绝缘材料电性连接时,半导体装置有时易受电路短路(或短路)。短路倾向于发生在当在导电材料间的电位是大于半导体装置设计的电压时,导致在导电材料间的绝缘材料崩溃。当在制程中测试装置时,或者在终端使用者使用一段时间后,电气短路造成装置失效。

技术实现要素:

4.本发明的一态样是提供一种半导体装置,此装置包含于基材上的栅极结构、于栅极结构和基材上的介电膜堆叠与延伸穿过介电膜堆叠的接触。介电膜堆叠包含于基材和栅极结构上的第一层间介电层、于基材中的源极/漏极元件、于第一层间介电层上的阻障层以及于阻障层上的第二层间介电层。接触电性连接至源极/漏极元件。接触侧壁的上部具有第一斜度。接触侧壁的下部具有不同于第一斜度的第二斜度。自第一斜度至第二斜度的转折是存在于接触的一部分,且接触的部分延伸穿过阻障层。

5.本发明的又一态样是在提供一种制造半导体装置的方法,包含沉积第一介电材料于基材上,且沉积栅极结构于基材上,其中基材具有源极/漏极元件。沉积阻障材料于第一介电材料上。沉积第二介电材料于阻障材料上。创设图案化遮罩层于第二介电材料的顶表面上。蚀刻两斜度(two-slope)接触开口。其中蚀刻两斜度接触开口的操作是通过第一蚀刻制程、第二蚀刻制程以及第三蚀刻制程而形成。第一蚀刻制程利用透过在图案化遮罩层内的第一开口蚀刻第二介电材料,来暴露出阻障材料的顶表面,其中第一蚀刻制程对阻障层材料是具选择性的。第二蚀刻制程利用透过在第二介电材料内的第二开口蚀刻阻障材料,来暴露出第一介电材料的顶表面,其中第二蚀刻制程对阻障层材料的选择性小于第一蚀刻制程。第三蚀刻制程利用透过在阻障材料内的第三开口蚀刻第一介电材料,来暴露出基材的顶表面,其中第三蚀刻制程是高度异向性。以导电材料填充两斜度接触开口,其中导电材料是电性连接至源极/漏极元件。

附图说明

6.当结合随附附图阅读时,自以下详细描述将最佳地理解本揭露的态样。应注意,根据工业中的标准实务,附图中的各特征并非按比例绘制。实际上,可出于论述清晰的目的任意增减所说明的特征的尺寸。

7.图1是根据本揭露的一些实施例的具有栅极结构与邻近接触结构的半导体装置的示意图;

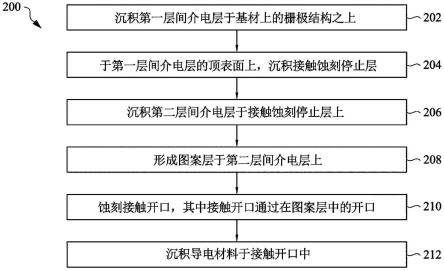

8.图2是根据本揭露的一些实施例的制造半导体装置的方法的流程图;

9.图3a至图3d是根据本揭露的一些实施例的制程期间的半导体装置的示意图。

10.【符号说明】

11.100:半导体装置

12.101/301:基材

13.102/302:栅极结构

14.104/112/304/312:层间介电层

15.105a/05b/105c:源极/漏极元件

16.106/382:接触

17.107a:上部

18.107b/306b:下部

19.108a/108b/108c:侧壁段

20.110:接触蚀刻停止层

21.111a/111b/111c:直径

22.114a/114b/314a/314b:侧壁角

23.116:最近点

24.118:分隔距离

25.120:侧边

26.124/397/329:顶表面

27.126/326:参考线

28.127/128/129/131/298/327/331/342/346/386/396/398:位置

29.130:分隔距离

30.132/134/136:厚度

31.138:高度

32.150a/150b:控制栅

33.152a/152b:浮栅

34.154a/154b:选择栅

35.156:栅极元件

36.155:介电质

37.200:方法

38.202/204/206/208/210/212:操作

39.300/330/360/380:半导体装置

40.305:遮罩层

41.306a:接触开口

42.308b:接触侧壁

43.316:点

44.340:投射线

45.344:距离

46.382:导体接触

47.384:粘着层

48.399:开口

具体实施方式

49.以下揭露提供许多不同实施例或例示,以实施发明的不同特征。以下叙述的组件、数值、操作、成份和排列方式、或其他类似描述的特定例示是为了简化本揭露的一实施例。这些当然仅是作为例示,其目的不在构成限制。其他组件、数值、操作、成份和排列方式、或其他类似描述是可思及的。举例而言,第一特征形成在第二特征之上或上方的描述包含第一特征和第二特征有直接附接的实施例,也包含有其他特征形成在第一特征和第二特征之间,以致第一特征和第二特征无直接附接的实施例。为简化及清楚,各种特征可以不同的尺寸任意绘示。此外,本揭露的一实施例可在各种例示中重复参考标号及/或标记文字。此重复仅是为了简化或清楚,且其本身并非意指本说明所讨论的各种实施例及/或态样之间的关系。

50.于电流流过在集成电路中的导电元件间的绝缘材料时,半导体装置是处在电气短路的风险中。当在接近栅极结构处形成接触(例如:当在有关栅极结构的源极或漏极区域制造电性接触)时,接触的侧边靠近栅极结构的侧边。当栅极结构倾向于具有垂直的侧边,接触倾向于具有斜度的侧边。因此,在栅极结构的顶部与接触的侧壁间的距离是小于栅极结构的底部与接触侧壁间的距离。在接触侧壁和栅极结构间的距离较小的位置,电气短路是更有可能发生,例如当瞬间的高电压造成在接触和栅极结构间的绝缘材料崩溃,而允许电流通过栅极结构和接触之间。

51.当发生电气短路,短路的栅极结构(与集成电路是作为一整体)的馈电电流(supply current,idd)增加。在静态(quiescent state)时的栅极结构(与集成电路)的馈电电流(iddq或idd,q)是尽可能的接近零电流,以有助于减少半导体装置的寄生功耗(parasitic power consumption)。如此,规范接触结构的轮廓有助于降低在栅极结构和接触结构间所产生的电气短路的可能性,此接触结构产生电性连接至有关于栅极结构的源极或漏极。

52.再者,通过完全地填充接触开口,其减少与接触有关的阻抗,规范接触结构的轮廓是有益于半导体装置的。在一些例子中,接触被导电材料填充,导电材料包含多晶硅、纯金属或金属合金。在沉积期间,一些导电材料沉积制程是倾向于孔洞的形成在接触内。相较于针对没有孔洞的半导体装置的设计规格,接触结构中的孔洞相应增加接触的阻抗,且在一些实施例中,降低于半导体装置操作的切换速度或频率。

53.制造如下所述的具有两斜度(two-slope)接触的集成电路或半导体装置可使半导体装置符合在接触与相邻的栅极电极结构之间具有分隔距离的装置设计或规格,而减少晶体管结构所使用的总面积,其中晶体管结构包含源极/漏极、通道、栅极电极与连接至晶体管结构的接触。在一些实施例中,两斜度接触具有下侧壁与上侧壁,其中下侧壁具有范围实质为85

°

至89.5

°

的斜度(例如自基材的顶表面垂直地向上延伸的垂直线的5

°

之内,且此基材内具有源极/漏极结构),且对应于自基材向上延伸的垂直线,上侧壁具有范围实质为45

°

至85

°

的斜度。在一些例子中,上侧壁和下侧壁在上层间介电层(inter-layer dielectric,ild)与下ild之间的阻障层具有一接合,其中在透过阻障层中的开口除去暴露的下ild材料的蚀刻制程期间,阻障层是作为遮罩层。阻障层具有一厚度,且此厚度实质不超过接触开口/接触的总高度的10%。在上ild与下ild间的阻障层能使接触/接触侧壁与栅极结构的分隔距离实质的去耦接(decoupling),且阻障层可使接触顶部区域/接触开口的尺寸实质的去耦接。在一些实施例中,名词“去耦接”是指接触侧壁的斜度与接触顶开口的宽度(或者于接触被导电材料所填充,则称接触顶宽度)之间的线性关系。通过放置阻障层在基材上方的一距离(此距离是大于第一ild厚度),在接触侧壁及栅极结构间的分隔距离分别是由接触顶开口的宽度或接触顶宽度来决定。

54.图1是包含在基材101上的栅极结构102的半导体装置100的剖视示意图。此栅极结构102是被第一ild 104覆盖且邻近接触106。为了清楚说明的目的,在图1中接触106是绘示为接触开口。栅极结构102是具有一对控制栅极150a和150b、一对浮动栅极152a和152b与一对选择栅极154a/154b的分离式栅极快闪记忆体(split gate flash memory cell)。栅极元件156是控制栅极150a和150b与浮动栅极152a和152b的每一者的共通抹除栅极(erase gate)。介电质155是位在栅极结构102的栅极元件156和基材101之间。源极/漏极元件105a、05b和105c是位在基材101中,且通过介电质155和第一ild104,源极/漏极元件105a、05b和105c是电性独立于栅极结构102。第一接触(图1未显示,但请参阅图3d中的接触382)是电性连接至源极/漏极元件105a,且第二接触(图1未显示,但请参阅图3d中的接触382)是电性连接至源极/漏极元件105a。虽栅极结构102是分离式栅极快闪记忆体,本揭露并不限于分离式栅极快闪记忆体,且栅极结构的其他类型亦可包含于本揭露的范围内。接触蚀刻停止层(contact etch stop layer,cesl)110,或阻障层,是在第一ild 104上。在一些实施例中,cesl 110是直接抵靠第一ild 104的顶表面。在一些实施例中,第一ild是单一介电材料。在一些实施例中,阻障层是氮化硅、氮氧化硅或其他介电材料。其他介电材料是以薄层(例如接触的总高度《10%)沉积,且其他介电材料是对被使用以于第一ild及第二ild中形成接触开口的蚀刻化学物质具阻抗的。在一些实施例中,第一ild在个别的顶部包含多种介电材料层。在一些实施例中,第一ild 104包含栅极介电氧化物的层,栅极介电氧化物的层位于基材的顶表面且在基材上形成栅极结构的部分。

55.第二ild 112是在cesl 110上。在一些实施例中,第二ild 112是直接在cesl 110的顶表面上。在一些实施例中,第一ild 104和第二ild 112独立地的包含(但不限于)二氧化硅、多晶硅、氟化二氧化硅〔氟化硅玻璃(fluorinated silicon glass,fsg)〕等的一或多者。cesl 110是与第一ild 104及第二ild 112具有不同蚀刻率的介电材料。在一些实施例中,cesl 110包含二或多层的介电材料,此二或多层的介电材料是共同的在第一ild 104的顶表面之上(或顶表面上)推积成层。根据一些实施例,蚀刻停止材料的多层是用于促进延伸至第一ild 104的接触开口的维度掌握的增进,以助于缓和在形成接触上部时光微影的变异。在一些实施例中,蚀刻制程期间,cesl 110具有低于第一ild 104的蚀刻率的蚀刻率,以形成接触106的下部。根据一些实施例,cesl 110是氮化硅层、氮氧化硅层、碳化硅层或所属领域所熟知的其他蚀刻停止层。在一些实施例中,第二ild是与第一ild相同的材料。在一些实施例中,第二ild是与第一ild不同的介电材料。在一些实施例中,第二ild包含介电材料的多层。

56.接触106具有延伸穿过第二ild 112的上部107a及延伸穿过第一ild 104的下部107b,且接触106是抵靠基材101的顶表面。在一些实施例中,接触106是为了电性连接至晶体管的源极区域。在一些实施例中,接触106是为了电性连接至晶体管的漏极区域。在一些实施例中,接触106是为了电性连接至作为晶体管的源极区域或漏极区域的两个晶体管所分享的区域。上部107a是对应于延伸穿过第二ild 112且于cesl 110上的接触的部分(亦可参照图3d的接触382)。接触106的下部107b是对应于具有cesl 110与第一ild 104的接触高度的部分(例如低于第二ild 112与cesl 110的分界面的接触点)。上部107a具有含第一侧壁角(θ1)(与第一斜度)的上侧壁段108a,且下部107b具有含第二侧壁角(θ2)114b的下侧壁段108b,而第二斜度较第一斜度陡。根据一些实施例,参考线126在接触开口的顶部平行延伸至第二ild的顶表面。第一侧壁角(θ1)(或第一斜度)114a是参考线126与上侧壁段108a间的角度。第二侧壁角(θ2)(或第二斜度)114b是基材101顶表面(此处接触暴露基材的顶表面)与下侧壁段108b间的角度。在一些实施例中,第二侧壁角(θ2)(或第二斜度)114b是紧邻于阻障层被量测。在一些实施例中,第二侧壁角(θ2)(或第二斜度)114b是在邻近于基材101的接触的底部或接触开口被量测。根据一些实施例,第一侧壁角114a的范围实质为45

°

至85

°

。当第一侧壁角114a小于约45

°

,在第二ild的顶表面中接触的周长将足够大而使接触互相侵蚀,或使接触侵蚀延伸至栅极电极的接触。当第一侧壁角114a大于约85

°

,则于减少及/或消除填充的问题上,或者有关在集成电路中小尺寸晶体管的源极/漏极接触上,上区域及下区域间的不同的斜度(或侧壁角)失去效能。第一侧壁角的最小斜度与第一侧壁角的最大斜度的比值为不大于1.88(85

°

/45

°

=1.88)。根据一些实施例,第二侧壁角114b在范围约85

°

至89.5

°

。当第二侧壁角实质小于85

°

,晶体管的底面积将对于集成电路的电路布局过大,而无法符合设计准则和晶体管的布局参数,且无法维持在电路布局所在设计的晶体管区域内。

57.根据一些实施例,通过在第二ild 112与上侧壁段108a和第一ild 104与下侧壁段108b间的cesl 110的暴露部分,中侧壁段108c被定义。在中侧壁段108c,接触106在第一ild 104与cesl 110间的界面具有直径111c。在第二ild 112的顶表面,接触106具有直径111a。在第一ild 104的底部接近101处,接触106具有直径111b。下侧壁段108b(在最近点116)是第一分隔距离(d1)118,第一分隔距离(d1)118是自最接近接触106的第一栅极结构102的侧壁120远离。根据一些实施例,最近点116是接近栅极结构102的顶部。根据一些实施例,最近点116是接近栅极结构102的中部。根据一些实施例,直径111c(在cesl的高度)是小于或等于在接触底部的直径111b的110%。根据一些实施例,在接触顶部的直径111a是直径111c的长度的至少115%,但小于或等于200%。在一些例示中,当接触直径过大,则接触过于接近栅极结构且更有可能装置失效。因在强电场中,接触与栅极结构间的介电材料崩溃,经由电气短路的形成,装置失效有可能发生。

58.第二ild 112具有顶表面124。上侧壁段108a在位置127与顶表面124相会。下侧壁段108b在位置129与基材101相会。位置128是在位置131正上方的顶表面124的点,位置131是对于接触106在栅极结构102上的最接近点。第一分隔距离d1是在接触106上的最近点116与栅极结构102上的位置131间量测。第二分隔距离d2 130是在位置127与位置128间量测。在一些实施例中,位置127是在栅极结构102的正上方,且第二分隔距离d2是在顶表面124上量测。在一些实施例中,位置128是在接触106(图未显示)的顶表面上,且第二分隔距离130

是在接触106的顶表面上量测(图未显示)。第二分隔距离d2是在接触边缘与在栅极结构正上方的介电材料间的距离。第二分隔距离d2是在ic设计所给予的限制内尽可能的大,为了使半导体装置的源极/漏极区域的接触和与栅极结构电性连接的接触(图未显示)间的干扰或短路的可能性降低,以调节电流通过基材101中的通道。当d2为零,或小于零(例如:当接触的边缘是在栅极结构的正上方,或当位置128是在接触的顶表面上)时,通过侧向地延着栅极结构的顶部取代栅极结构,达成在源极/漏极接触和栅极结构接触间的分隔,而远离侵蚀的源极/漏极接触。

59.第一ild 104具有第一厚度132,且第二ild具有第二厚度134。阻障层(cesl 110)具有足以承受制程中形成接触开口的上部的蚀刻制程第三厚度136。根据一些实施例,依据使用于制造两斜度接触的蚀刻制程,第三厚度136各有不同。两斜度接触是具有在上区域与下区域间的分界的侧壁的接触(参阅图1,上侧壁段108a与下侧壁段108b)。当上侧壁段与下侧壁段各别延着段具有接近常数斜度,且接触侧壁的斜度改变发生在段的接面,接触侧壁具有区别性的“两个斜度”轮廓。下侧壁段具有大于栅极结构102的栅极高度138的第一厚度132,因此上侧壁段108a与下侧壁段108b间的接合面是在栅极结构102的顶部上。

60.根据一些实施例,第一厚度132在范围由约80nm至130nm第一ild的第一厚度是大于栅极结构的高度,由于第一ild覆盖栅极结构并由在第一ild和第二ild间的阻障层分隔栅极结构。第一ild的厚度在各种实施例中,是维持在大于栅极结构高度的约10nm至15nm,以使阻障层与栅极结构的顶部保持分隔。第一厚度落在低于10nm至15nm的分隔距离,栅极结构的电性绝缘的优点在于如接触材料位在接近栅极结构而更有可能使介电崩溃的减少。

61.在一些实施例中,第二ild 112具有范围实质为50nm至240nm的第二厚度。在实施例中具有第二厚度(例如范围实质为100nm至240nm),使用第二ild 112的较大厚度,较大的侧壁角(接近90

°

)达成朝向栅极结构位置的接触边缘(参阅图1位置127)的侧向取代。如第二ild的厚度减小至在约50nm至100nm间,侧壁角减小,而在短的垂直敷设中,达成朝向栅极结构位置的接触边缘(参阅图1位置127)的侧向取代。具有厚度小于约50nm的厚度的第二ild膜,是无法达成朝向具减少高度的栅极结构位置的接触边缘的侧向取代。下-侧壁角接触开口是更难以达成,且具有在阻障层开口旁的区域暴露阻障层的风险。在第一ild的蚀刻制程期间,阻障层暴露导致阻障层的侵蚀,使第一ild中的开口的直径与形状较不一致或不可预测。

62.在一些实施例中,阻障层具有厚度范围实质为至在一些实施例中,增加阻障层的厚度有助于维持阻障层开口的几何形状与一致性(遍布于晶圆)。增加阻障层的厚度高于倾向于导致在阻障层开口蚀刻中的不一致,造成被为阻障层开口的蚀刻制程穿透至第一ild,使得每次第一ild蚀刻更难以描绘。阻障层小于关系到不平坦的覆盖,造成在接触蚀刻制程期间,第一ild的穿透和不平坦的蚀刻。相较于当接合面是在栅极结构的顶部之上,当在上侧壁段与下侧壁段间的接合面发生在(或低于)栅极结构的顶部的高度,接触在较大的程度上仍在接触与栅极结构间的介电材料的崩溃的风险中。相较于栅极结构的顶部,当接合面的位置太低,上侧壁的浅斜度实际上增加接触与栅极结构间的介电崩溃的风险。

63.根据一些实施例,图2是制造两斜度接触的方法200的流程图。根据一些实施例,图3a至3c是在制程期间的半导体装置的剖视示意图。在操作202中,第一ild层是沉积在基材上,在基材顶表面上,基材具有栅极结构或晶体管。通过如原子层沉积(atomic layer deposition)及化学气相沉积(chemical vapor deposition,cvd)的制程,沉积ild膜。cvd包含电浆辅助化学气相沉积(plasma enhanced chemical vapor deposition,pe-cvd)、高压化学气相沉积(high-pressure chemical vapor deposition,hp-cvd)、气相磊晶(vapor-phase epitaxy,vpe)等。

64.根据一些实施例,基材具有平坦的顶表面。在一些实施例中,基材包含半导体材料,半导体材料层的区域具有n掺杂及/或p掺杂区域以用为集成电路的源极和漏极区域。根据一些实施例,基材是纹理基材,其中基材已被蚀刻成作为半导体装置中的晶体管的源极、漏极汲通道区域的鳍。根据一些实施例,第一ild层沉积至半导体材料的凹陷区域,以使电性连接至晶体管源极/漏极或栅极结构的邻近的鳍、栅极结构及/或接触彼此隔离。

65.第一ild 304是位在基材301之上且在栅极结构302上。

66.在操作204中,阻障层沉积在第一ild上,以通过多重蚀刻制程使两斜度接触形成,且以使在透过阻障层的开口的接触收缩。阻障层310(接触蚀刻停止层)是在第一ild 304的顶表面上。使用如所属领域通常知识者熟知的原子层沉积、溅镀或化学气相沉积制程,阻障层是沉积至第一ild 304上。对于第一ild及/或第二ild电浆蚀刻条件,依照所欲选择的阻障层,为半导体装置选择阻障层材料。特别是在电浆蚀刻的条件下,阻障层材料对于侧向蚀刻的阻抗的能力。在一些实施例中,阻障层310是单一介电材料(如氮化硅或碳化硅)的单一膜。在一些实施例中,阻障层包含不同于第一ild 304或第二ild 312介电材料的多层。在一些实施例中,第一ild 304是单一介电材料。在一些实施例中,第一ild 304是多个介电材料,此多个介电材料是由接近栅极结构的半导体装置的电性导体元件所沉积,以覆盖并隔绝的栅极结构302。

67.在操作206中,第二ild是沉积在阻障层上,其中两斜度接触的上部被形成。通过如原子层沉积及cvd形成ild膜,其中cvd包含pe-cvd、hp-cvd、及vpe等。第二ild 312是在阻障层310上。在一些实施例中,第二ild 312是直接抵靠阻障层310。根据一些实施例,第二ild 312是与第一ild 304不同的介电材料。在一些实施例中,第二ild 312是与第一ild 304相同的介电材料。根据一些实施例,第二ild 312是单一介电材料。在一些实施例中,第二ild 312是多于一的叠于彼此的顶部的ild材料。

68.在操作208中,形成图案化遮罩层于第二ild层的顶表面。在一些实施例中,通过沉积光阻或有机遮罩层在基材上,暴露光阻或有机遮罩层至光线以修改层的部分的溶解度,形成图案化遮罩层。形成图案化遮罩层的方法还包含溶解遮罩层的修改部分,以暴露第二ild层的顶表面的部分。在一些实施例中,图案化遮罩层是图案化的光阻层。在一些实施例中,图案化遮罩层是适合于电子束图案化的遮罩层。在一些实施例中,图案化遮罩层是自组装遮罩层。

69.在操作210中,进行一系列的蚀刻步骤,以透过ild层和阻障层形成两斜度接触。图3a至图3c是半导体装置300、330与360的剖视示意图,其代表在操作210期间半导体装置的变化。栅极结构302是在基材的顶表面上。在操作210的一些实施例中,至少一蚀刻步骤是电浆蚀刻步骤。电浆蚀刻步骤具有蚀刻化学物质和电浆环境,且蚀刻步骤蚀刻第二ild 312快

于阻障层310。在操作210的一些实施例中,包含多重蚀刻制程。在操作210的一些实施例中,第一蚀刻制程去除第二ild的部分并暴露阻障层。第二蚀刻制程去除被第一蚀刻制程暴露的阻障层的部分并暴露第一ild。第三蚀刻制程去除在阻障层中透过开口暴露的第一ild的部分并暴露在第一ild下的基材。在一些实施例中,第一蚀刻制程去除第二ild的部分并在阻障层被暴露前停止。第二蚀刻制程去除第二ild的剩余部分,且在第二ild剩余的部分被去除后,去除暴露的阻障层的部分而暴露第一ild。第三蚀刻制程去除在阻障层中透过开口暴露的第一ild的部分,且暴露第一ild下的基材。在一些实施例中,第一蚀刻制程对阻障层材料是具选择性的(例如:蚀刻制程蚀刻阻障层材料慢于蚀刻第一ild的材料)。在一些实施例中,第二蚀刻制程对阻障层材料的选择性是小于第一蚀刻制程。在一些实施例中,第三蚀刻制程对阻障层的材料是具选择性的。当第三蚀刻制程对阻障层的材料是具选择性时,第三蚀刻制程去除第一ild快于去除阻障层材料。在一些实施例中,在形成阻障层中的开口后,因第三蚀刻制程是高度异向性,阻障层的材料具有低侧向去除率。在一些实施例中,在第三蚀刻制程期间,因第三蚀刻制程亦可产生覆盖在接触开口的侧壁的聚合材料,第三蚀刻制程于阻障层的材料中具有低侧向去除率。在一些实施例中,相较于阻障材料的去除率,通过减少在蚀刻制程进行的压力及/或增加通过蚀刻制程所产生的离子的加速电压,第一ild去除率是增加的。

70.在图3a中,接触开口306a的上部被蚀刻以暴露阻障层310的上表面。在图案化遮罩层305(例如图案化的光阻材料或其他微影型遮罩)中的开口399设置接触开口306的上部的形状和尺寸。参考线326平行于阻障层310的顶表面和第二ild 312的顶表面延伸。第一侧壁角314a是在参考线326与接触侧壁308a的上部间量测。

71.在图3b中,在蚀刻制程去除阻障层310的暴露部分后,接触开口306a的上部已被延伸,暴露第一ild 304的顶表面397。接触侧壁308a的上部由位置327延伸至位置398。

72.在图3c中,在如上所述的(例如)第三蚀刻制程,形成接触开口的下部306b。接触侧壁308b的下部由位置298延伸至位置386(抵靠基材301的顶表面329)。接触侧壁308b的下部具有不同于第一侧壁角314a的第二侧壁角314b。相较于接触侧壁的上部,接触侧壁308b的下部是更垂直的。

73.在图3c中,投射线340由位置327(于接触开口306a的上部的顶部边缘)延伸至位置396。投射线从位置331在距离(d3)344处有最近点342。位置331是最接近投射线340上的最近点342的在栅极结构302上的位置。根据本揭露的一些实施例,由位置327延伸至位置396的投射线340代表单一斜度接触侧壁的斜率。没有阻障层310,在具有实质沿着投射线340的侧壁轮廓的接触中,蚀刻制程形成接触开口。在投射线340和栅极结构302间的第三分隔距离(d3)344妨碍集成电路的设计原则,因集成电路的设计原则的指示,具有等同于第三分隔距离(d3)344的ild 304是较易受介电崩溃的影响。如此单一蚀刻制程无法塑型具有实质对齐投射线340的轮廓的接触侧壁轮廓的主要部分。第三分隔距离(d3)344是小于在位置331和位置346间的第四分隔距离(d4)〔图未显示,但并不类似于图1中的第一分隔距离(d1)〕。位置346的实际位置是在接近栅极结构302上的位置331的下接触侧壁308b。

74.在图3d中,半导体装置380包含延伸透过介电层且到达基材310的顶表面(图未显示)的导体接触382。在图3d中的元件(类似于图1中所标号的元件)具有视为与图1中所提供相似的标号(较图1的标号增值200)。

75.第一分隔距离318是在接触的侧壁上的最近点316与栅极结构302的位置331间的距离,其中位置331是最接近接触侧壁的最近点316的位置。选择性的粘着层384包含导体接触382的外部。根据一些实施例,粘着层384是在以导电材料填充接触开口前,沉积在接触开口内的钛层。在沉积后,粘着层是材料的薄层,促进接触的填充材料和开口的侧壁间贴附于所填充的接触的增进。粘着层有时使用于介电材料和金属间的晶格不匹配的情形,或者使用于导电金属填充接触。在一些例示中,除了使用阻障层减少导电材料(例如金属)原子扩散至栅极结构周围的介电材料中,还可使用粘着层。在一未限制的实施例中,钛粘着层是直接沉积抵靠于接触开口的侧壁,且氮化钛的阻障层是沉积在接触开口内粘着层的顶部上。在沉积粘着层与阻障层后,接触开口被金属使用溅镀填充。在一未限制的实施例中,溅镀钨到钛粘着层和氮化钛的阻障层的顶部上的接触开口。在一些实施例中,阻障层是直接沉积在接触开口侧壁上,粘着层沉积在阻障层的顶部。在所属领域中通常知识者所熟知的粘着层和阻障层的其他例子中,且亦包含在本揭露的范围内,包含镍、银、钯及/或钴作为粘着层,且还包含氮层作为阻障层。在一些实施例中,阻障层材料包含镍、银、铂、钯及/或钴的氮化物。

76.在操作212中,导电材料是沉积在操作210期间形成的接触开口。在方法200中的一些实施例中,在抵靠第二ild的上侧壁和在第一ild上的下侧壁两者上,衬垫层可选择性地沉积在接触开口的侧壁上。在方法200中的一些实施例中,在抵靠第二ild的上侧壁和在第一ild上的下侧壁两者上,扩散阻障层是选择性的沉积在接触开口的侧壁上。在一些实施例中,通过溅镀制程沉积导电材料。在一些实施例中,通过包含pecvd、lpcvd和所属领域所熟知的其他cvd技术的一或多者的cvd制程沉积导电材料。在一些实施例中,依照与在半导体装置内晶体管的形成接触一致的材料,沉积于接触开口的导电材料是多晶硅、纯金属或金属合金。

77.如本说明书所揭露两斜度接触有关于多个益处。对半导体装置其中一个益处是在接触和最接近接触的栅极结构间,电气短路的较低发生率。根据一些实施例,透过两斜度接触,接触顶部的区域可较单一斜度接触大。单一斜度在接触和最接近接触的栅极结构间具有相同的分隔距离。接触顶部区域的增加使具有重叠的内互连结构(介层窗或沟槽)的失准更为困难。

78.对半导体装置的另一益处是改善粘着层制程窗。粘着层制程窗包含有关沉积钛粘着层和阻障层(例如氮化钛阻障)沉积的操作,以及有关以钨填充接触开口以在集成电路的层间形成接触的操作。具有较大的顶部开口,填充导电材料至接触倾向于制造孔洞,或倾向于在接触侧壁具有脱层。当被沉积在接触开口内的导电材料在接触开口的下侧壁上以低速率集中,且在接触开口的上侧壁或在接触侧壁的顶部边缘以高速率集中,孔洞倾向于发生在接触内。在接触开口的上部(或在接触开口的顶部边缘)的沉积速率的增加,限制接触开口的区域,接触开口的区域中新导电材料进入以填充接触。如开口区域缩小,导电材料的整体沉积速率减少,而于导电材料沉积期间,在上部的沉积速率和接触结构的中部/下部产生及/或加速部平衡。根据一些实施例,在基材的顶表面上增加接触开口的区域,其中导电材料被沉积以促进接触开口的顶部、中部和底部间的沉积速率更为一致。根据一些实施例,调节接触开口侧壁的斜度(至较部垂直)亦影响在接触开口的顶部、中部和底部间的沉积速率的分配。然而,在一些实施例中,增加接触开口区域(例如增加接触开口直径),和减少垂直

接触侧壁而使接触侧壁较接近栅极结构,造成在接触结构和邻近栅极结构间电气短路的较大的可能性。

79.在一些例示中,导电材料是沉积在基材中,或ild和基材的顶表面上的接触开口内,作为在基材顶部上的毯覆层。在一些例示中,当导电材料的毯覆层是沉积在基材上,导电材料层的顶部被去除,以在ild的开口内留下导电材料的部分。在一些实施例中,在ild材料和沉积在接触开口内的导电材料间的接触侧壁上,接触(或介层窗)具有衬垫层及/或扩散阻障。在一些实施例中,衬垫层及/或扩散阻障是在接触侧壁上,以由基材层隔离导电材料,或避免导电材料的原子扩散至ild材料。

80.图案化层是沉积在第二部分及/或第二介电材料的顶表面,且透过在图案化层内的开口,第二介电材料是以第一蚀刻化学物质被蚀刻,直到暴露阻障材料。在一些实施例中,通过以含氟化学物质且与第二介电材料反应的电浆蚀刻,进行第二材料的蚀刻。当阻障材料被暴露,电浆化学物质被改为第二蚀刻化学物质,以与阻障层反应。在一些实施例中,第二蚀刻化学物质对第二介电材料与第一电材料具选择性的。一旦阻障层被蚀刻透过且第一介电材料被暴露,第二蚀刻化学物质被改为第三蚀刻化学物质。在一些例示中,第一蚀刻化学物质与第三蚀刻化学物质为相同的化学物质。在一些例示中,第一蚀刻化学物质与第三蚀刻化学物质为不相同的化学物质。相较于阻障材料被蚀刻,第三蚀刻化学物质对以较快速率蚀刻的第一介电质为具选择性的。如此,当第二介电材料被蚀刻通过以暴露在基材下的第一介电材料,在阻障材料内开口的直径些微改变(或不全然改变)。当第一介电材料被蚀刻时,在第二介电材料中接触开口的直径的增加快于阻障材料的直径的改变,使得接触侧壁的上部的斜率较大〔例如远离“垂直”或“90

°”

(垂直于基材表面)〕。接触开口(透过第一介电材料)的下部斜度维持在垂直的5

°

内或垂直于基材表面。在一些实施例中,接触开口的下部斜度是小于偏离垂直的0.5

°

或垂直。第一介电材料被蚀刻直到基材的顶表面被暴露。接触开口接着以导电材料填充。

81.对于两斜度或双斜度接触,相较于由栅极结构的侧壁到一线的间距,由接触开口侧壁(或接触侧壁)的最近点(此最近点是指最接近于栅极结构的侧壁的一点)到栅极结构的侧壁的间距是较远的,其中前述的线是延伸于两点之间,一点是位于第二介电材料的顶表面上的接触开口上的一位置,且此点是最接近于栅极结构,而另一点是位于基材的顶表面上的接触开口上的一位置,且相对于栅极结构,第一介电材料是抵靠在此另一点上。如此,双斜度接触开口或接触结构提供较多的介电材料于接触和栅极结构之间,而减少接触和栅极结构之间短路或介电崩溃的可能。

82.本揭露的一些态样是关于一种装置,此装置包含于基材上的栅极结构、于栅极结构和基材上的介电膜堆叠与延伸穿过介电膜堆叠的接触。介电膜堆叠包含于基材和栅极结构上的第一层间介电层、于第一层间介电层上的阻障层以及于阻障层上的第二层间介电层。接触侧壁的上部具有第一斜度。接触侧壁的下部具有不同于第一斜度的第二斜度。自第一斜度至第二斜度的转折是存在于接触的一部分,且接触的部分延伸穿过阻障层。在一实施例中,阻障层的厚度实质是小于第一层间介电层、阻障层和第二层间介电层的总厚度的10%。第二斜度是大于第一斜度。在一实施例中,第二斜度的范围至少由85

°

至89.5

°

。在一实施例中,第一斜度的范围至少由45

°

至不大于85

°

。在一实施例中,第二层间介电层具有顶表面,且顶表面实质平行于接触的顶表面。在一实施例中,第一斜度的最小值与最大值的比

值是不大于1.88。在一实施例中,栅极结构是分离栅快闪记忆体。

83.根据一些实施例是关于一半导体装置,半导体装置包含于基材上的栅极结构、于栅极结构和基材上的介电膜堆叠与延伸穿过介电膜堆叠的接触。介电膜堆叠包含于基材和栅极结构上的第一层间介电层、于第一层间介电层上的阻障层以及于阻障层上的第二层间介电层。接触的顶部具有第一直径。接触的底部具有第二直径。延伸穿过阻障层的接触的一部分具有第三直径,其中第一直径是大于第三直径,且第一直径是小于或等于第三直径的两倍。在一实施例中,阻障层是氮化硅层。在一实施例中,第一层间介电层、第二层间介电层和阻障层是不同的介电材料。在一实施例中,抵靠着第一层间介电层的接触侧壁的上部的斜度为大于85

°

。在一实施例中,抵靠着第二层间介电层的下接触侧壁的斜度为小于85

°

。在一实施例中,第三直径是第二直径的至少1.1倍。在一实施例中,第一直径是第三直径的至少1.15倍。在一实施例中,第三直径是第二直径的至少1.1倍,且第一直径是第二直径的至少1.15倍。

84.本揭露的另一些态样是关于一种制造半导体装置的方法,包含沉积第一介电材料于基材上,且沉积栅极结构于基材上。沉积阻障材料于第一介电材料上。沉积第二介电材料于阻障材料上。创设图案化遮罩层于第二介电材料的顶表面上。蚀刻两斜度(two-slope)接触开口。其中蚀刻两斜度接触开口的操作是通过利用透过在图案化遮罩层内的第一开口蚀刻第二介电材料,来暴露出阻障材料的顶表面。利用透过在第二介电材料内的第二开口蚀刻阻障材料,来暴露出第介一电材料的顶表面。利用透过在阻障材料内的第三开口蚀刻第一介电材料,来暴露出基材的顶表面。以导电材料填充两斜度接触开口,其中导电材料是电性连接于基材的顶表面。在此方法的一些例子中,蚀刻两斜度接触开口的操作还包含以蚀刻制程蚀刻第一介电材料,其中第一介电材料移除速率是大于阻障材料移除速率。在此方法的一些例子中,蚀刻第二介电材料的操作还包含使用第一蚀刻制程蚀刻第二介电材料。在阻障材料被第一蚀刻制程暴露前,暂停第一蚀刻制程。使用第二蚀刻步骤,蚀刻第二介电材料的余留物,其中第二介电材料的余留物是在阻障材料之上且在图案化遮罩层的第一开口之下,且第二介电材料移除速率是大于阻障材料移除速率。在此方法的一些例子中,蚀刻第一介电材料的操作还包含以第一蚀刻制程蚀刻第二介电材料,其中第一介电材料移除速率是不大于阻障材料移除速率,且在暴露出第一介电材料的顶表面之前,暂停第一蚀刻制程。

85.前述内容概述若干实施例的特征以使得熟悉此项技术者可较佳地理解本揭露的一实施例的内容态样。熟悉此项技术者应理解,其可容易地使用本揭露的一实施例的内容作为设计或修改其他制程及结构的基础用于进行本文中所介绍的实施例的相同的目的及/或达成相同的优点。熟悉此项技术者应同时意识到,此等等效建构不偏离本揭露的一实施例的内容的精神及范畴,且其可在本文中进行各种变化、替代及修饰而不偏离本揭露的一实施例的内容的精神及范畴。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1