半导体结构、半导体结构的制备方法和半导体存储器与流程

1.本公开涉及存储器技术领域,尤其涉及一种半导体结构、半导体结构的制备方法和半导体存储器。

背景技术:

2.栅诱导漏极泄露电流(gate induced drain leakage,gidl)是金属-氧化物半导体场效应晶体管(metal oxide semiconductor field effect transistor,mosfet,mos管)的主要断态漏电机理,严重影响着mos管器件的可靠性。在mos管栅极关断而漏极接电压时,漏极杂质扩散层与栅极重叠部分靠近界面处的能带发生强烈的弯曲,表面形成反型层,而耗尽层非常窄,导带电子和价带空穴发生带-带隧穿效应(band-to-band tunneling,btbt),从而形成漏极漏电流,随着器件尺寸的不断缩小,器件内横向电场不断增强,热载流子效应引起断态漏电的几率随之变大。

技术实现要素:

3.本公开实施例提供了一种半导体结构、半导体结构的制备方法和半导体存储器:

4.第一方面,本公开实施例提供了一种半导体结构,包括:

5.沟道掺杂区;

6.形成在所述沟道掺杂区两侧的漏极掺杂区和源极掺杂区;

7.绝缘隔离层,包括第一绝缘隔离部分和第二绝缘隔离部分,所述第一绝缘隔离部分形成在所述沟道掺杂区的表面,所述第二绝缘隔离部分形成在所述漏极掺杂区的部分表面;

8.第一金属层,形成在所述第一绝缘隔离部分的表面;

9.第二金属层,形成在所述第二绝缘隔离部分的表面。

10.在一些实施例中,所述第二金属层的功函数小于或者等于所述第一金属层的功函数,且所述第二金属层的功函数大于预设功函数阈值。

11.在一些实施例中,所述预设功函数阈值为4.6电子伏特。

12.在一些实施例中,所述第一金属层的材料包括下述至少之一:铱、镍、铂、钴。

13.在一些实施例中,所述半导体结构还包括第三金属层,所述第三金属层的材料与所述第二金属层的材料相同;其中,

14.所述第三金属层形成在所述第一金属层的表面,且所述第三金属层与所述第二金属层连接。

15.在一些实施例中,所述沟道掺杂区、所述漏极掺杂区以及所述源极掺杂区的掺杂离子类型相同。

16.在一些实施例中,所述沟道掺杂区为轻掺杂区;

17.所述漏极掺杂区和所述源极掺杂区均为重掺杂区;

18.其中,所述重掺杂区的掺杂离子浓度大于所述轻掺杂区的掺杂离子浓度。

19.在一些实施例中,所述漏极掺杂区包括第一子掺杂区和第二子掺杂区,且所述第一子掺杂区位于所述沟道掺杂区与所述第二子掺杂区之间;其中,所述第二绝缘隔离部分形成在所述第一子掺杂区的表面。

20.在一些实施例中,所述绝缘隔离层还包括第三绝缘隔离部分,所述第三绝缘隔离部分形成在所述源极掺杂区的部分表面;

21.所述半导体结构还包括第四金属层,所述第四金属层形成在所述第三绝缘隔离部分的表面。

22.在一些实施例中,所述源极掺杂区包括第三子掺杂区和第四子掺杂区,且所述第三子掺杂区位于所述沟道掺杂区与所述第四子掺杂区之间,所述第三绝缘隔离部分形成在所述第三子掺杂区的表面;其中,

23.所述沟道掺杂区为轻掺杂区;

24.所述第一子掺杂区和所述第三子掺杂区均为中掺杂区;

25.所述第二子掺杂区和所述第四子掺杂区均为重掺杂区;

26.其中,所述中掺杂区的掺杂离子浓度大于所述轻掺杂区的掺杂离子浓度,且所述中掺杂区的掺杂离子浓度小于所述重掺杂区的掺杂离子浓度。

27.在一些实施例中,所述半导体结构还包括第五金属层;其中,

28.所述第五金属层形成在所述第一金属层的表面,且所述第五金属层的两端与所述第二金属层和所述第四金属层分别连接。

29.在一些实施例中,所述半导体结构还包括位线和电容;其中,

30.所述位线与所述源极掺杂区的远离所述沟道掺杂区的一侧连接;

31.所述电容与所述漏极掺杂区的远离所述沟道掺杂区的一侧连接。

32.在一些实施例中,所述半导体结构还包括控制引线;其中,

33.所述第一金属层和所述第二金属层连接;

34.所述控制引线的一端与所述第一金属层和/或所述第二金属层连接,所述控制引线的另一端与控制端连接。

35.在一些实施例中,所述半导体结构还包括金属隔离层、第一控制引线和第二控制引线;其中,

36.所述金属隔离层形成于所述第一金属层和所述第二金属层之间,用于将所述第一金属层和所述第二金属层进行绝缘隔离;

37.所述第一控制引线的一端与所述第一金属层连接,所述第一控制引线的另一端与第一控制端连接;

38.所述第二控制引线的一端与所述第二金属层连接,所述第二控制引线的另一端与第二控制端连接。

39.第二方面,本公开实施例提供了一种半导体结构的制备方法,包括:

40.提供衬底;

41.对所述衬底进行掺杂,于所述衬底中形成沟道掺杂区、漏极掺杂区和源极掺杂区,且所述漏极掺杂区和所述源极掺杂区形成在所述沟道掺杂区的两侧;

42.形成绝缘隔离层,所述绝缘隔离层包括第一绝缘隔离部分和第二绝缘隔离部分,所述第一绝缘隔离部分形成在所述沟道掺杂区的表面,所述第二绝缘隔离部分形成在所述

漏极掺杂区的部分表面;

43.于所述第一绝缘隔离部分的表面形成第一金属层;

44.于所述第二绝缘隔离部分的表面形成第二金属层。

45.在一些实施例中,所述于所述第一绝缘隔离部分的表面形成第一金属层,包括:

46.于所述第二绝缘隔离部分的表面形成掩膜层;

47.以所述掩膜层为掩膜,于所述第一绝缘隔离部分的表面形成第一金属层;

48.去除所述掩膜层。

49.在一些实施例中,在所述于所述第二绝缘隔离部分的表面形成第二金属层时,所述方法还包括:

50.于所述第一金属层的表面形成第三金属层,且所述第三金属层与所述第二金属层连接;其中,所述第三金属层的材料与所述第二金属层的材料相同。

51.在一些实施例中,该方法还包括:

52.形成位线和电容;其中,所述位线与所述漏极掺杂区的远离所述沟道掺杂区的一侧连接;所述电容与所述源极掺杂区的远离所述沟道掺杂区的一侧连接。

53.在一些实施例中,所述第二金属层的功函数小于或者等于所述第一金属层的功函数,且所述第二金属层的功函数大于预设功函数阈值;其中,所述预设功函数阈值为4.6电子伏特。

54.第三方面,本公开实施例提供了一种半导体存储器,包括如第一方面任一项所述的半导体结构。

55.本公开实施例提供了一种半导体结构、半导体结构的制备方法和半导体存储器,该半导体结构包括:沟道掺杂区;形成在沟道掺杂区两侧的漏极掺杂区和源极掺杂区;绝缘隔离层,包括第一绝缘隔离部分和第二绝缘隔离部分,第一绝缘隔离部分形成在沟道掺杂区的表面,第二绝缘隔离部分形成在漏极掺杂区的部分表面;第一金属层,形成在第一绝缘隔离部分的表面;第二金属层,形成在第二绝缘隔离部分的表面。这样,在半导体结构中,第二金属层能够降低漏极掺杂区到沟道掺杂区的杂质分布的浓度梯度,降低漏极掺杂区附近的载流子数量,从而有效降低沟道掺杂区的电场强度,抑制由于带-带隧穿效应导致的栅诱导漏极泄露电流。

附图说明

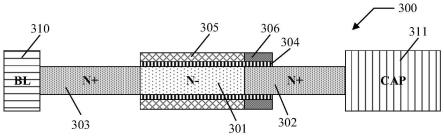

56.图1为一种无结晶体管的组成结构示意图;

57.图2为一种累积模式无结晶体管的组成结构示意图;

58.图3为一种沟道长度与电场强度的关系示意图;

59.图4为一种能带轮廓示意图;

60.图5为本公开实施例提供的一种半导体结构的组成结构示意图一;

61.图6为本公开实施例提供的一种晶体管的立体结构示意图;

62.图7为本公开实施例提供的一种半导体结构的组成结构示意图二;

63.图8为本公开实施例提供的一种半导体结构的组成结构示意图三;

64.图9为本公开实施例提供的一种半导体结构的组成结构示意图四;

65.图10为本公开实施例提供的一种半导体结构的组成结构示意图五;

medium dopant,用n表示),例如,n型中掺杂的离子浓度为:e

19

个每立方厘米(e

19

/cm3)。这时候,由于轻掺杂的扩展,晶体管具有更好的关断状态,但是晶体管的开启电流低。

86.图2为一种累积模式无结晶体管jlamt的组成结构示意图。如图2所示,对于jlamt而言,其可以包括沟道201、位于沟道两侧的漏极202和源极203,形成在沟道201表面的栅介质层204和形成在栅介质层204表面的栅极205,其中,d表示与漏极202连接的器件,s表示与源极203连接的器件。如图2所示,在jlamt中,沟道201的掺杂类型为n型轻掺杂(n type light dopant,用n-表示),例如,n型轻掺杂的离子浓度为:e

18

/cm3,漏极202和源极203的掺杂类型均为n型重掺杂(n type heave dopant,用n+表示),例如,n型重掺杂的离子浓度为:e

20

/cm3。这时候,晶体管的开启电压高,但是由于btbt的影响,电流泄露更严重。

87.图3为一种沟道长度与电场强度的关系示意图,图4为一种能带轮廓示意图。其中,图3和图4均对应图2所示的jlamt。在图3中,横轴为沟道长度(单位为:纳米(nm)),纵轴为电场强度(单位为:毫伏每厘米(mv/cm)),在该jlamt中,电场强度较强,导致晶体管的漏电流大。在图4中,横轴对应jlamt中源极、沟道和漏极所处位置,纵轴为能量(单位为:电子伏特(ev));如图4所示,该能带轮廓是在源漏电压vd=1v,栅源电压vg=0v时获取的。由于电场强度较强,能带的弯曲程度大,漏极的导带(ec)和沟道的价带(ev)的重叠区域大。这些均会导致jlamt中电流泄露严重。

88.基于此,本公开实施例提供了一种半导体结构,包括:沟道掺杂区;形成在沟道掺杂区两侧的漏极掺杂区和源极掺杂区;绝缘隔离层,包括第一绝缘隔离部分和第二绝缘隔离部分,第一绝缘隔离部分形成在沟道掺杂区的表面,第二绝缘隔离部分形成在漏极掺杂区的部分表面;第一金属层,形成在第一绝缘隔离部分的表面;第二金属层,形成在第二绝缘隔离部分的表面。这样,在半导体结构中,在漏极掺杂区的附近形成第二金属层,第二金属层能够降低漏极掺杂区到沟道掺杂区的杂质分布的浓度梯度,降低漏极掺杂区附近的载流子数量,从而有效降低沟道掺杂区的电场强度,抑制由于带-带隧穿效应(btbt)导致的栅诱导漏极泄露电流(gidl)。

89.下面将结合附图对本公开各实施例进行详细说明。

90.本公开的一实施例中,参见图5,其示出了本公开实施例提供的一种半导体结构300的组成结构示意图一。如图5所示,该半导体结构300可以包括:

91.沟道掺杂区301;

92.形成在沟道掺杂区301两侧的漏极掺杂区302和源极掺杂区303;

93.绝缘隔离层304,包括第一绝缘隔离部分和第二绝缘隔离部分,第一绝缘隔离层部分形成在沟道掺杂区301的表面,第二绝缘隔离部分形成在漏极掺杂区302的部分表面;

94.第一金属层305,形成在第一绝缘隔离部分的表面;

95.第二金属层306,形成在第二绝缘隔离部分的表面。

96.需要说明的是,该半导体结构300可以形成在衬底的有源区中,附图中未示出衬底。另外,该半导体结构可以应用于动态随机存取存储器(dynamic random access memory,dram)中,例如三维dram(three dimensional dram,3d dram),在3d dram中形成有多个空间堆叠的半导体结构300。

97.如图5所示,在该半导体结构300中,包括三个掺杂区:沟道掺杂区301、漏极掺杂区302和源极掺杂区303,且漏极掺杂区302和源极掺杂区303分布在沟道掺杂区301的两侧。绝

缘隔离层304形成在沟道掺杂区301的表面和漏极掺杂区302的部分表面,且第二绝缘隔离部分形成在漏极掺杂区302的靠近沟道掺杂区301的一侧,将形成在沟道掺杂区301的表面的绝缘隔离层304记作第一绝缘隔离部分,将形成在漏极掺杂区302的部分表面的绝缘隔离层304记作第二绝缘隔离部分,第一绝缘隔离部分和第二绝缘隔离部分组成完整的绝缘隔离层304。可以理解的是,绝缘隔离层304是一个完整的整体,划分为第一绝缘隔离部分和第二绝缘隔离部分只是为了便于描述。

98.在绝缘隔离层304的表面形成有金属层,金属层具体包括第一金属层305和第二金属层306;其中,第一金属层305形成在第一绝缘隔离部分的表面,第二金属层306形成在第二绝缘隔离部分的表面。

99.需要说明的是,漏极掺杂区302和源极掺杂区303的长度可以是相同的,第二金属层306的长度可以为漏极掺杂区302或者源极掺杂区303的长度的五分之一到二分之一。

100.还需要说明的是,在半导体结构300中,沟道掺杂区301、漏极掺杂区302、源极掺杂区303、绝缘隔离层304、第一金属层305和第二金属层306组成一晶体管(mos管)。其中,沟道掺杂区301形成晶体管的沟道,漏极掺杂区302形成晶体管的漏极,源极掺杂区303形成晶体管的源极,第一金属层305可以形成晶体管的栅极。其中,绝缘隔离层304相当于晶体管的栅介质层,第二金属层306也可以视作栅极的一部分。

101.还需要说明的是,该晶体管可以为无结型晶体管,具体可以是jlamt,即在半导体结构300中,沟道掺杂区301、漏极掺杂区302以及源极掺杂区303的掺杂离子类型相同。例如,沟道掺杂区301、漏极掺杂区302和源极掺杂区303可以均为n型离子的掺杂,从而形成n型金属氧化物半导体场效应管(negative channel metal oxide semiconductor,nmos管),或者,沟道掺杂区301、漏极掺杂区302和源极掺杂区303可以均为p型离子的掺杂,从而形成p型金属氧化物半导体场效应管(positive channel metal oxide semiconductor,pmos管)。在本公开实施例中,以n型离子的掺杂为例进行描述。

102.进一步地,如图5所示,在本公开实施例中,沟道掺杂区301可以为轻掺杂区(n-);漏极掺杂区302和源极掺杂区303可以均为重掺杂区(n+)。即沟道掺杂区301、漏极掺杂区302和源极掺杂区303的掺杂离子类型相同,但是掺杂离子的浓度不同,其中,重掺杂区的掺杂离子浓度大于轻掺杂区的掺杂离子浓度。

103.这样,本公开实施例在无结型晶体管的漏极(漏极掺杂区302)靠近沟道(沟道掺杂区301)的一端形成第二金属层306,第二金属层306能够降低漏极到沟道的杂质分布的浓度梯度,从而能够有效降低沟道的电场强度,减少晶体管在关断状态下产生的漏电流,有效抑制gidl效应,降低了晶体管的关断电流;另外,在栅极开启的时候,栅极电压还会增加载流子量,降低电阻,还可以提高晶体管的开启电流。

104.另外,第二金属层的长度可以为漏极掺杂区或者源极掺杂区的长度的五分之一到二分之一,这样,还能够在抑制gidl效应的同时,保证晶体管的正常工作不会受到影响。

105.还需要说明的是,图5示出的是半导体结构300的剖面示意图,对于半导体结构300中的晶体管,参见图6,其示出了本公开实施例提供的一种晶体管的立体结构示意图。如图6所示,晶体管的栅极可以为环绕栅。也就是说,绝缘隔离层304环绕沟道掺杂区301的表面和漏极掺杂区302的部分表面形成,第一金属层305和第二金属层306环绕绝缘隔离层304的表面形成。

106.在一些实施例中,第二金属层306的功函数小于或者等于第一金属层305的功函数,且第二金属层306的功函数大于预设功函数阈值。

107.需要说明的是,第一金属层305(也可以称作控制栅极、control gate)为控制沟道的开关,第一金属层305的材料可以为功函数较大的金属材料,例如:铱(ir)、镍(ni)、铂(pt)、钴(co)。其中,铱的功函数为5.27ev,镍的功函数为5.15ev,铂的功函数为5.65ev,钴的功函数为5ev。

108.第二金属层306用于调节沟道靠近漏极部分的杂质分布,降低漏极到沟道的杂质分布的浓度梯度,从而能够有效降低沟道电场。第二金属层306的功函数大于预设功函数阈值并小于或者等于第一金属层305的功函数,其中,预设功函数阈值可以为4.6ev,保证第二金属层306能够起到降低沟道电场的效果。

109.其中,功函数(work function,wf)是指把一个电子从固体内部刚刚移到此物体表面所需的最少的能量,功函数的大小大概为金属自由原子电离能的二分之一,功函数的大小标志着电子在金属中束缚的强弱,功函数越大,电子越不容易离开金属。由于第二金属层306的功函数较大(大于4.6ev),则能够有效降低漏极掺杂区302(漏极)的载流子数量,这样,会在沟道掺杂区301(沟道)和漏极掺杂区302(漏极)之间形成浓度缓变结,最终降低电场强度,从而减少晶体管的漏极在关断状态下产生的漏电流,改善btbt效应,抑制gidl效应。另外,在栅极开启的时候,栅极电压会使得载流子量增加,降低电阻,从而提高晶体管的开启电流。

110.进一步地,参见图7,其示出了本公开实施例提供的一种半导体结构300的组成结构示意图二,如图7所示,在一些实施例中,该半导体结构300还可以包括第三金属层307;其中,

111.第三金属层307形成在第一金属层305的表面,且第三金属层307与第二金属层304连接。

112.需要说明的是,如图7所示,在本公开实施例中,半导体结构300还可以包括形成在第一金属层305的表面的第三金属层307,而且第三金属层307和第二金属层306连接,也就是说,第三金属层307还形成在第二金属层306的部分表面,第三金属层307也可视作栅极的一部分。其中,第三金属层307的材料可以与第二金属层306的材料相同。这时候,第三金属层307和第二金属层306共同作用,也能够有效减少晶体管的漏电流,降低由于btbt导致的gidl效应,降低晶体管的关断电流,并提高晶体管的开启电流。

113.进一步地,第一金属层305和第二金属层306的材料可以是相同的。参见图8,其示出了本公开实施例提供的一种半导体结构300的组成结构示意图三,如图8所示,在一些实施例中,漏极掺杂区可以包括第一子掺杂区3021和第二子掺杂区3022,且第一子掺杂区3021位于沟道掺杂区301与第二子掺杂区3022之间;其中,第二绝缘隔离部分形成在第一子掺杂区3021的表面。

114.需要说明的是,如图8所示,漏极掺杂区可以具体分为第一子掺杂区3021和第二子掺杂区3022,第一子掺杂区3021即被第二绝缘隔离部分所覆盖的部分漏极掺杂区,第二子掺杂区3022即未被第二绝缘隔离部分所覆盖的部分漏极掺杂区。其中,沟道掺杂区301为轻掺杂区,第一子掺杂区3021为中掺杂区,第二子掺杂区3022和源极掺杂区303为重掺杂区,中掺杂区的掺杂离子浓度大于轻掺杂区的掺杂离子浓度且小于重掺杂区的掺杂离子浓度。

也就是说,本公开实施例可以将漏极掺杂区分为重掺杂的第二子掺杂区3022和中掺杂的第一子掺杂区3021,且中掺杂的第一子掺杂区3021与低掺杂的沟道掺杂区301连接,从而使得第二掺杂区和沟道掺杂区之间的浓度梯度变得平缓,有利于减少晶体管的漏电流,降低gidl效应。

115.进一步地,图9示出了本公开实施例提供的一种半导体结构300的组成结构示意图四,图10示出了本公开实施例提供的一种半导体结构300的组成结构示意图五,如图9或者图10所示,在一些实施例中,绝缘隔离层304还可以包括第三绝缘隔离部分,第三绝缘隔离部分形成在源极掺杂区的部分表面;半导体结构300还包括第四金属层308,第四金属层308形成在第三绝缘隔离部分的表面。

116.其中,第四金属层308也可视作栅极的一部分。

117.在一些实施例中,源极掺杂区可以包括第三子掺杂区3031和第四子掺杂区3032,且第三子掺杂区3031位于沟道掺杂区301与第四子掺杂区3032之间,第三绝缘隔离部分形成在第三子掺杂区3031的表面;其中,

118.沟道掺杂区301为轻掺杂区;

119.第一子掺杂区3021和第三子掺杂区3031均为中掺杂区;

120.第二子掺杂区3022和第四子掺杂区3032均为重掺杂区;

121.其中,中掺杂区的掺杂离子浓度大于轻掺杂区的掺杂离子浓度,且中掺杂区的掺杂离子浓度小于重掺杂区的掺杂离子浓度。

122.需要说明的是,如图9或者图10所示,绝缘隔离层304还可以形成在源极掺杂区的部分表面,具体是形成在源极掺杂区的靠近与沟道掺杂区301的连接处的部分表面,将形成在源极掺杂区的部分表面的绝缘隔离层304记作第三绝缘隔离部分。可以理解,第一绝缘隔离部分、第二绝缘隔离部分和第三绝缘隔离部分组成完成的绝缘隔离层304,划分为三个部分仅是为了便于描述,绝缘隔离层304是一个完整的整体。另外,对应地,在第三绝缘隔离部分的表面形成有第三金属层308。

123.还需要说明的是,如图9或者图10所示,源极掺杂区可以分为第三子掺杂区3031和第四子掺杂区3032,且第三子掺杂区3031位于沟道掺杂区301和第四子掺杂区3032之间,即第三子掺杂区3031与沟道掺杂区301连接,第三绝缘隔离部分形成在第三子掺杂区3031的表面。

124.其中,沟道掺杂区301可以为轻掺杂区,第一子掺杂区3021和第三子掺杂区3031可以均为中掺杂区,第二子掺杂区3022和第四子掺杂区3032均为重掺杂区。也就是说,本公开实施例还可以将源极掺杂区分为重掺杂的第四子掺杂区3032和中掺杂的第三子掺杂区3031,且中掺杂的第三子掺杂区3031与低掺杂的沟道掺杂区301连接。

125.还需要说明的是,在本公开实施例中,中掺杂区的掺杂离子浓度大于轻掺杂区的掺杂离子浓度,且中掺杂区的掺杂离子浓度小于重掺杂区的掺杂离子浓度。也就是说,对于本公开实施例中涉及到的重掺杂区、中掺杂区和轻掺杂区三种掺杂方式,按照掺杂离子浓度由高至低的顺序进行排序,依次为:重掺杂区的掺杂离子浓度最高,中掺杂区的掺杂离子浓度次之,轻掺杂区的掺杂离子浓度最低。示例性地,重掺杂区的掺杂离子浓度可以为e

20

/cm3,中掺杂区的掺杂离子浓度可以为e

19

/cm3,重掺杂区的掺杂离子浓度可以为e

18

/cm3。

126.这样,不仅使得沟道掺杂区301(沟道)和漏极掺杂区(漏极)之间的浓度梯度呈缓

慢变化,还使得沟道掺杂区301(沟道)和源极掺杂区(源极)之间的浓度梯度呈缓慢变化,从而减小晶体管的漏电流。

127.还需要说明的是,第一金属层305、第二金属层306以及第四金属层308的材料可以为相同材料(如图9所示),或者第二金属层306以及第四金属层308的材料也可以与第一金属层305的材料不同(如图10所示)。由于本公开实施例在源极(源极掺杂区)和漏极(漏极掺杂区)都形成有金属层,从而对源极和漏极都能够起到弱化效果,降低载流子数量,从而降低电场强度,改善btbt效应,抑制gidl效应,减少晶体管在关断状态下的漏电流,对源极的弱化还能够降低在晶体管的预充电过程中的漏电,起到更全面的漏电保护效果。

128.进一步地,在图10所示的半导体结构的基础上,参见图11,其示出了本公开实施例提供的一种半导体结构300的组成结构示意图六,如图11所示,在一些实施例中,半导体结构300还可以包括第五金属层309;其中,

129.第五金属层309形成在第一金属层305的表面,且第五金属层309的两端与第二金属层306和第四金属层308分别连接。

130.需要说明的是,如图11所示,在图10所示结构的基础上,半导体结构300还可以包括第五金属层309,第五金属层309形成在第一金属层305的表面,而且还与第二金属层306和第四金属层308分别连接,也就是说,第五金属层309还形成在第二金属层306和第四金属层308的部分表面。其中,第五金属层309也可视作栅极的一部分。

131.还需要说明的是,如图11所示,第五金属层309的材料可以与第二金属层306和第四金属层308的材料相同。第二金属层306可以对漏极掺杂区(漏极)起到弱化效果,第四金属层308可以对源极掺杂区(源极)起到弱化效果,同时,被弱化的部分可以作为半导体结构中的轻掺杂漏极ldd,即第一子掺杂区3021和第三子掺杂区3031可以作为轻掺杂漏极,从而使得对源极/漏极的弱化效果具有可调节性;源极和漏极的高掺杂能够降低电阻,提供晶体管导通的载流子,减小肖特基势垒宽度。另外,轻掺杂漏极能够减弱晶体管中的漏区电场,从而能够改进热电子退化效应等一系列的短沟道效应。

132.示例性的,参见图12和图13,图12为本公开实施例提供的一种沟道长度与电场强度的关系对比示意图,图13为本公开实施例提供的一种能带轮廓对比示意图。在图12和图13中,jlamt为常规的累积模式无结晶体管的电场强度与沟道长度的关系示意图,用实线表示;wf-jlamt为本公开实施例提供的包含第二金属层的无结型晶体管的电场强度与沟道长度的关系示意图,用虚线表示。如图12所示,与常规的jlamt相比,在本公开实施例提供的半导体结构中,由于在漏极掺杂区302的部分表面形成有绝缘隔离层304的第二绝缘隔离部分,在第二绝缘隔离部分的表面形成有第二金属层306,第二金属层306采用功函数大于4.6ev并小于等于第一金属层305的功函数的材料,相较于只有单独金属栅极的常规jlamt,wf-jlamt的沟道的电场强度明显降低。

133.如图13所示,与常规的jlamt相比,由于在wf-jlamt中,漏极靠近沟道部分的电场降低,使得能带弯曲减小,在第二金属层306的作用下,如图13中的虚线方框所示,wf-jlamt的漏极的能带中多出了一个台阶,这个台阶将漏极和沟道交接的部分能带拉高,从而漏极的导带(ec)与沟道的价带(ev)的重叠(如图13中的虚线椭圆框所示)减小甚至消失;最终能够有效改善btbt效应,减少漏极的漏电流,从而有效减少晶体管的关断电流,抑制gidl效应。

134.进一步地,如前述图4或者图7至11的任一附图所示,在一些实施例中,该半导体结构300还可以包括位线310和电容311;其中,

135.位线310与源极掺杂区303的远离沟道掺杂区301的一侧连接;

136.电容311与漏极掺杂区302的远离沟道掺杂区301的一侧连接。

137.需要说明的是,以图5为例,如图5所示,位线310(图中的bl)与源极掺杂区303连接,电容311(图中的cap)与漏极掺杂区302连接。从而晶体管、位线310和电容311能够实现对数据的存取读出等操作。

138.进一步地,在一些实施例中,半导体结构还可以包括金属隔离层、第一控制引线和第二控制引线;其中,

139.金属隔离层形成于第一金属层和所述第二金属层之间,用于将第一金属层和第二金属层进行绝缘隔离;

140.第一控制引线的一端与第一金属层连接,第一控制引线的另一端与第一控制端连接;

141.第二控制引线的一端与第二金属层连接,第二控制引线的另一端与第二控制端连接。

142.需要说明的是,在本公开实施例中,第一金属层和第二金属层可以分别通过第一控制引线和第二控制引线分别进行控制,这时候,可以在第一金属层和第二金属层之间增加金属隔离层将两者进行绝缘隔离。示例性地,参见图14,其示出了本公开实施例提供的一种金属层单独控制的控制引线连接示意图。其中,(a)为半导体结构300的立体结构示意图,(b)和(c)中未示出位线310、电容311等结构,图14中各序号的含义与前述附图均相同。

143.如图14中的各图所示,第一控制引线313a的一端与第一金属层305连接,另一端与第一控制端(图中未示出)连接,第二控制引线313b的一端与第二金属层306连接,另一端与第二控制端(图中未示出)连接,在第一金属层305和第二金属层306之间设有金属隔离层312将两者进行绝缘隔离。第一控制引线313a和第二控制引线313b可以如图14中的(a)所示,位于晶体管不同侧,也可以如图14中的(b)所示,位于晶体管相同侧。另外,如图14中的(c)所示,半导体结构还可以包括第三控制引线313c,第三控制引线313c的一端与第四金属层308连接,另一端与第三控制端(图中未示出)连接,第四金属层308和第一金属层305之间也存在金属隔离层312进行绝缘隔离,在图14中的(c)中,三个控制引线分布于晶体管的不同侧,另外,三个控制引线也可以位于晶体管的同侧。

144.还需要说明的是,第一控制端、第二控制端和第三控制端可以为同一控制端或者不同的控制端,可以为外部电源、字线、半导体存储器中的其它器件等。

145.进一步地,第一金属层和第二金属层还可以通过同一控制引线进行控制,这时候,第一金属层和第二金属层之间无需进行绝缘隔离。在一些实施例中,半导体结构还可以包括控制引线;其中,

146.第一金属层和第二金属层连接;

147.控制引线的一端与第一金属层和/或第二金属层连接,控制引线的另一端与控制端连接。

148.需要说明的是,图15为本公开实施例提供的一种金属层共同控制的控制引线连接示意图,在图15中,未示出位线310、电容311等结构。如图15中的(a)所示,控制引线313的一

端与第一金属层305连接,另一端与控制端连接,或者,如图15中的(b)所示,控制引线313的一端与第二金属层306连接,另一端与控制端连接,或者控制引线313还可以同时与第一金属层305和第二金属层306连接,用于同时对第一金属层305和第二金属层306进行控制;另外,在图15中的(c)所示,控制引线313可以如图所示与第一金属层305连接,也可以与第二金属层306或者第四金属层308连接。其中,控制端可以为外部电源、字线、半导体存储器中的其它器件等等。

149.也就是说,在本公开实施例中,第一金属层和第二金属层可以分别单独控制也可以共同控制,例如从晶体管的同一侧单独或共同控制,或者从晶体管的两侧相反的方向引出单独控制。这样,本公开实施例可以通过多种方式实现对第一金属层、第二金属层以及第四金属层的灵活控制。

150.简言之,本公开实施例利用不同功函数的金属材料作为栅极,用于控制沟道的掺杂分布,从而达到降低沟道电场,减小关断电流,抑制btbt所产生的gidl效应。采用功函数金属弱化部分漏极的方法,可以在不改变掺杂的前提下,弱化漏极接近沟道的部分,从而在达到降低关断电流,抑制gidl效应的同时,还可以增强开启电流。

151.本公开实施例提供了一种半导体结构,包括:沟道掺杂区;形成在沟道掺杂区两侧的漏极掺杂区和源极掺杂区;绝缘隔离层,包括第一绝缘隔离部分和第二绝缘隔离部分,第一绝缘隔离部分形成在沟道掺杂区的表面,第二绝缘隔离部分形成在漏极掺杂区的部分表面;第一金属层,形成在第一绝缘隔离部分的表面;第二金属层,形成在第二绝缘隔离部分的表面。其中,沟道掺杂区、漏极掺杂区、源极掺杂区、绝缘隔离层、第一金属层和第二金属层可以组成晶体管。这样,在半导体结构中,在漏极掺杂区的附近形成第二金属层,第二金属层能够降低漏极掺杂区到沟道掺杂区的杂质分布的浓度梯度,降低漏极掺杂区附近的载流子数量,从而有效降低沟道掺杂区的电场强度,在晶体管断开的情况下,减小晶体管的漏电流,从而减小晶体管的关断电流,抑制由于btbt导致的gidl效应;另外,在晶体管开启时,栅压会增加载流子量,降低电阻,还能够增加晶体管的开启电流。

152.本公开的另一实施例中,参见图16,其示出了本公开实施例提供的一种半导体结构的制备方法的流程示意图。如图16所示,该方法可以包括:

153.s1001、提供衬底。

154.s1002、对衬底进行掺杂,于衬底中形成沟道掺杂区、漏极掺杂区和源极掺杂区,且漏极掺杂区和源极掺杂区形成在沟道掺杂区的两侧。

155.需要说明的是,首先提供一衬底,且衬底中形成有多个有源区,对于3d半导体结构而言,多个有源区可以呈空间阵列排布。然后对有源区进行掺杂,以形成多个掺杂区。具体地,图17为形成沟道掺杂区301、漏极掺杂区302和源极掺杂区303后所得的结构示意图,在图17中,仅示出了有源区部分。

156.如图17所示,漏极掺杂区302和源极掺杂区303分别位于沟道掺杂区301的两侧。另外,这三个掺杂区可以为无结型晶体管的三个掺杂区,因此,在一些实施例中,沟道掺杂区301、漏极掺杂区302以及源极掺杂区303的掺杂离子类型相同;例如,三个掺杂区的掺杂离子类型可以均为n型离子掺杂或者p型离子掺杂。

157.在一些实施例中,如图17所示,沟道掺杂区301可以为轻掺杂区(n-),漏极掺杂区302和源极掺杂区303为重掺杂区(n+)。另外,漏极掺杂区302和源极掺杂区303还可以如前

述图7至图11所示,漏极掺杂区302包括第一子掺杂区3021和第二子掺杂区3022,和/或,源极掺杂区303包括第三子掺杂区3031和第四子掺杂区3032。这时候,只需要改变掺杂浓度即可。

158.s1003、形成绝缘隔离层。

159.其中,绝缘隔离层包括第一绝缘隔离部分和第二绝缘隔离部分,第一绝缘隔离部分形成在沟道掺杂区的表面,第二绝缘隔离部分形成在漏极掺杂区的部分表面。

160.需要说明的是,图18为形成绝缘隔离层304后所得结构示意图。如图18所示,在沟道掺杂区301的表面以及漏极掺杂区302的部分表面形成绝缘隔离层304,将形成在沟道掺杂区301的表面的绝缘隔离层304记作第一绝缘隔离部分,将形成在漏极掺杂区302的部分表面的绝缘隔离层304记作第二绝缘隔离部分。且第二绝缘隔离部分的长度可以为漏极掺杂区302或者源极掺杂区303的长度的五分之一至二分之一。

161.s1004、于第一绝缘隔离部分的表面形成第一金属层。

162.s1005、于第二绝缘隔离部分的表面形成第二金属层。

163.在第一绝缘隔离部分和第二绝缘隔离部分的表面分别形成第一金属层和第二金属层,从而得到无结型晶体管。

164.在一些实施例中,于第一绝缘隔离部分的表面形成第一金属层,可以包括:

165.于第二绝缘隔离部分的表面形成掩膜层;

166.以掩膜层为掩膜,于第一绝缘隔离部分的表面形成第一金属层;

167.去除掩膜层。

168.需要说明的是,图19为形成掩膜层316后所得的结构示意图。如图19所示,在形成第一金属层时,首先在第二绝缘隔离部分的表面形成掩膜层316。其中,掩膜层316的材料可以为光刻胶等。

169.然后以掩膜层316为掩膜,在第一绝缘隔离部分的表面形成第一金属层305,图20为形成第一金属层305后所得的结构示意图。

170.将掩膜层316去除,得到如图21所示的结构。如图21所示,在第一绝缘隔离部分的表面形成有第一金属层305,第二绝缘隔离部分暴露。在第二绝缘隔离部分的表面形成第二金属层306,得到如图22所示的结构。

171.在一些实施例中,第二金属层的功函数小于或者等于第一金属层的功函数,且第二金属层的功函数大于预设功函数阈值。

172.需要说明的是,第二金属层306用于调节沟道靠近漏极部分的杂质分布,降低漏极到沟道的杂质分布的浓度梯度,能够有效降低沟道电场。第二金属层306的功函数大于预设功函数阈值并小于或者等于第一金属层305的功函数,其中,预设功函数阈值可以为4.6ev,以保证第二金属层306能够起到降低沟道电场的效果。

173.在一些实施例中,在于第二绝缘隔离部分的表面形成第二金属层时,该方法还可以包括:

174.于第一金属层的表面形成第三金属层,且第三金属层与第二金属层连接,第三金属层的材料与第二金属层的材料相同。

175.需要说明的是,图23为形成第三金属层307后所得的结构示意图,这时候,能够形成如前述图7所示的半导体结构,第二金属层305和第三金属层307可以共同作用,实现降低

gidl效应。

176.进一步地,在一些实施例中,该方法还可以包括:

177.形成位线和电容;其中,位线与漏极掺杂区的远离沟道掺杂区的一侧连接;电容与源极掺杂区的远离沟道掺杂区的一侧连接。

178.需要说明的是,形成电容和位线后所得的结构可以参照前述图5或者图7所示。另外,本公开实施例仅以形成图5或者图7所示的半导体结构为例对半导体结构的制备方法进行说明,基于相似的方法,还可以形成前述图8至图11任一项所示的半导体结构,这里不再赘述。

179.对于本公开实施例未披露的细节,可以参照前述实施例的描述而理解。

180.本公开实施例提供了一种半导体结构的制备方法,利用该方法制得的半导体结构中,在漏极掺杂区的附近形成第二金属层,第二金属层能够降低漏极掺杂区到沟道掺杂区的杂质分布的浓度梯度,降低漏极掺杂区附近的载流子数量,从而有效降低沟道掺杂区的电场强度,抑制由于带-带隧穿效应导致的栅诱导漏极泄露电流。

181.本公开的再一实施例中,参见图24,其示出了本公开实施例提供的一种半导体存储器400的组成结构示意图。如图24所示,该半导体存储器400包括前述实施例任一项所述的半导体结构300。

182.其中,该半导体存储器400可以包括3d dram。

183.对于该半导体存储器400而言,由于其包括前述实施例所述的半导体结构300,从而能够有效抑制由于带-带隧穿效应导致的栅诱导漏极泄露电流。

184.以上所述,仅为本公开的较佳实施例,并非用于限定本公开的保护范围。

185.需要说明的是,在本公开中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

186.上述本公开实施例序号仅仅为了描述,不代表实施例的优劣。

187.本公开所提供的几个方法实施例中所揭露的方法,在不冲突的情况下可以任意组合,得到新的方法实施例。

188.本公开所提供的几个产品实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的产品实施例。

189.本公开所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

190.以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1