一种提升抗疲劳特性的并五苯有机场效应晶体管

1.本发明属于微电子技术领域,具体涉及一种提升抗疲劳特性的并五苯有机场效应晶体管。

背景技术:

2.过去二十几年来由于在从射频识别标签到柔性及大面积显示等领域的应用前景,基于有机场效应晶体管的非易失性电子器件获得了人们非常多的关注【1,2】。为了促进有机场效应器件的实际应用,人们在研究诸如p-型沟道材料,n-型沟道材料及聚合物等电荷俘获材料方面花费了大量的精力。作为最有潜力的p-型沟道材料之一,具有5个苯环的平面型分子结构的小分子半导体材料并五苯(pentacene)已经被广泛应用于有机半导体场效应器件的结构研究中。研究表明聚苯乙烯(ps),聚 (2-乙烯基萘)(pvn),聚α-甲基苯乙烯(pαms)等作为电荷俘获介质的存储器件上应用在很高的工作电压下其转移特性曲线显示了很大的存储窗口【3】。在以pαms 为电荷存储介质的并五苯有机场效应晶体管器件中baeg等人使用200v/1μs的脉冲电压对器件开展了编程操作,并使用-100v/1μs的脉冲对器件开展了擦除操作【1】。在以苯乙烯-聚4-乙烯吡啶嵌段共聚物(ps-b-p4vp)为电荷俘获介质的并五苯有机场效应器件中,leong等人使用-30v/1s的脉冲开展了编程操作,并使用100v/30s的脉冲开展了擦除操作【4】。以具有如此高的脉冲幅值或如此长的脉冲宽度的脉冲电压对并五苯有机场效应器件开展编程/擦除操作并不满足现代电子器件应用的工业标准。因此,至今为止以聚合物薄膜作为电荷俘获介质的并五苯有机场效应晶体管器件还没有得到实际应用。

3.针对以聚合物薄膜作为电荷俘获介质的并五苯有机场效应晶体管器件为背景,人们开展了多方面的基础研究。理论和实验研究【5,6】都表明,在并五苯/聚合物界面处的并五苯薄膜中靠近界面的并五苯晶界处存在与外界环境(如氢和氧气等) 有关的带正电的缺陷,所带正电荷的体密度高达4

╳

10

18

cm-3

【7】。该带正电的缺陷层厚度约1.5nm,由于缺陷的形成该薄层已经不具有半导体特性。该薄层所带正电荷形成的电场方向指向p-型半导体并五苯薄膜,对并五苯薄膜中的空穴(hole)往聚合物薄膜中迁移起阻碍作用,此带正电的缺陷层起正电荷势垒的作用,该正电荷势垒的存在导致了以聚合物薄膜作为电荷俘获介质的并五苯有机场效应存储器件的高工作电压。

4.本发明小组中国发明专利申请,cn201911336850.8,一种提升并五苯有机场效应晶体管工作性能的方法及美国发明专利申请,20255cjh,a method for enhancingthe performance of pentacene organic field-effect transistor and thestructure of pentacence organic field-effect transistor,在结构为栅电极/ 绝缘层/聚合物介质薄膜/并五苯/源与漏电极的有机场效应晶体管器件中,聚合物介质和并五苯之间设置一n-型半导体薄膜过渡层;n-型半导体过渡层厚度为1-100nm; n-型半导体薄膜是结晶态薄膜、半晶态薄膜或者非晶态薄膜。通过n-型半导体过渡层中界面处的感生电子降低并五苯与电荷俘获介质界面处的空穴势垒高度,有效降低并五苯有机半导体晶体管的编程/擦除工作

电压;通过n-型半导体过渡层中电离施主所形成的带正电的空间电荷区阻碍聚合物介质薄膜中被俘获的正电荷(空穴)逃逸到并五苯薄膜中,提高并五苯有机半导体晶体管器件的编程/擦除可靠性及数据保持能力,提升并五苯有机场效应晶体管工作性能。

5.本发明小组中国发明专利申请,cn202011153410.1一种n-型半导体插层并五苯有机场效应晶体管及应用,及美国发明专利申请,20256cjh,apentaceneorganicfield-effecttransistorwithn-typesemiconductorinterlayeranditsapplication,提升并五苯有机场效应晶体管存储器件性能的方法,有机场效应晶体管器件的结构为底栅型:从下到上分别是栅电极/绝缘层/聚合物介质薄膜/并五苯/源与漏电极;有机场效应晶体管器件的结构或为顶栅型,从下到上分别是源与漏电极/并五苯/聚合物介质薄膜/绝缘层/栅电极,在聚合物介质薄膜和并五苯之间增加一层n-型半导体薄膜为过渡层;n-型半导体薄膜是n-型无机半导体薄膜,n-型有机半导体薄膜,厚度为1-100nm。并五苯厚度为1-100nm;源漏电极厚度为50-200nm。n-型半导体薄膜是n-型半导体薄膜,具体分为n-型小分子薄膜和n-型聚合物薄膜,如n-n

”‑

二3-正戊烷基-3,4,9,10-苝二酰亚胺(ptcdi-c13)、n-n

”‑

二正十三烷基-3,4,9,10-苝二酰亚胺(ep-pdi)、n-n

”‑

二苯基-1,4,5,8-奈二酰亚胺(ndi);n-型半导体薄膜是结晶态薄膜、半晶态薄膜或者非晶态薄膜;

6.通过n-型半导体插层中界面处的感生电子降低并五苯与聚合物介质界面处的空穴势垒高度,有效降低并五苯有机半导体晶体管的编程/擦除工作电压;通过调节n-型半导体插层中n-型载流子数量调节并五苯与聚合物介质界面处的空穴势垒高度至合理的范围,使并五苯有机场效应晶体管器件具有较低的工作电压,较快的编程/擦除速度,良好的编程/擦除可靠性及数据保持能力,从而提升并五苯有机场效应晶体管的工作性能。

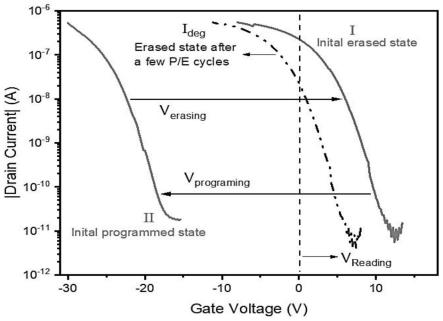

7.在以聚合物驻极体作为电荷俘获介质的并五苯ofet存储器件中,编程操作过程中空穴在负栅压所产生电场驱动下越过界面势垒从并五苯进入聚合物驻极体中,并被其中的浅能级及深能级陷阱捕获,被束缚在聚合物中,此时器件的转移特性曲线如示意图1中的曲线ii所示。在擦除操作过程中对器件施加正的栅压,部分被浅能级俘获的空穴接受正栅压所提供的电场能量后又被驱动到并五苯沟道中,而留在深能级陷阱中的空穴则可能由于激发能量不够高而无法被解除束缚,仍然被束缚在聚合物介质的深陷阱能级中。在器件如此反复的编程/擦除循环动作过程中,又不断地有空穴被空着的深能级陷阱俘获而不能再回到并五苯沟道。上述物理特征在ofet器件的宏观测量数据中就表现为在正的擦除脉冲作用下,器件转移特性曲线不能再回到对器件进行初次擦除操作后的曲线位置(图1中的曲线i所示),而与其相比阈值电压有一定偏移,如示意图1中的i

deg

所示。此时施加同样的源漏电压,并在同样的栅压下读取器件源漏间的电流i

ds

,就会发现器件的i

ds

是下降的,这可能就是并五苯ofet存储器件抗疲劳特性劣化的根本原因。而对应地,在相同的编程脉冲作用下从并五苯沟道中被驱动到聚合物中的空穴则填充剩余空着的缺陷能级,总体上聚合物驻极体中所俘获的电荷数量无太大差异,ofet存储器件的转移特性曲线基本会与器件初次编程操作后的曲线重合,如图1中的曲线ii所示,此时从器件源漏电极间读取的i

ds

不会发生太明显的变化。

8.由于聚合物电荷俘获介质(如聚苯乙烯(ps),聚(2-乙烯基萘)(pvn),聚α-甲基苯乙烯(pαms)等)中存在各种深缺陷能级(这些缺陷可能来源于聚合物中的化学缺陷)。聚合物中这些化学缺陷可能包括侧链缺陷、不饱和化学键、被氧化的基团、添加剂及杂质等)

【8】,大多数以聚合物为电荷俘获介质的并五苯有机场效应晶体管在经历几百次的组合编程/擦除脉冲栅压的操作下,其通过源漏电极的开态与关态的电流比会急剧下降,导致器件的抗疲劳特性(endurancecharacteristics)严重退化,使得器件无法获得实际应用。【9-11】

9.参考文献:

10.1.baeg,k.,-j,noh,y.y.,ghim,j.,kang,s.j.,lee,h.kim,d.y.,organicnon-volatilememorybasedonpentancenefield-effecttransistorsusingapolymericgateelectret.,adv.mater.18,3179-3183(2006).

11.2.dimitrakopoulos,c.d.&malenfant,p.r.adv.mater.14,99-117(2002).

12.3.baeg,k.,j.,nohy.y.,ghimj.,limb.,kimd.y.,polarityeffectsofpolymergateelectretsonnon-volatileorganicfield-effecttransistormemory,adv.funct.mater.18,3678-3685(2008).

13.4.leong,w.l.,mathews,n.,mhaisalkar,s.,lamy.m.,chen,t.,lee,s.,micellarpoly(styrene-b-4-vinypyridine)-nanoparticlehybridsystemfornon-volatileorganictransistormemory,j.mater.chem.19,7354-7361(2009).

14.5.knipp,d,street,r.a.,volkel,a.andho,j.,pentacenethinfilmtransistorsoninorganicdielectrics:morphology,structuralproperties,andelectronictransport,j.appl.phys.93,347-355(2003).

15.6.northrupj.e.,chabinycm.l.,gapstatesinorganicsemiconductors:hydrogen-andoxygen-inducedstatesinpentacene,phys.rev.b68,041202(r):1-4(2003).

16.7.kalb,w.l.,mattenberger,k.andbatlogg,b.,oxygen-relatedtrapsinpentacenethinfilms:energeticpositionandimplicationsfortransistorperformance,phys.rev.b,78,035334:1-11(2008).

17.8.g.teyssedre,f.h.zheng,l.boudou,andc.laurent,chargetrapspectroscopyinpolymerdielectrics:acriticalreview,j.phys.d:appl.phys.54,263001(2021).

18.9.hsu,j.-c.,lee,w.-y.,wu,h.-c.,sugiyama,k.,hiraoa.,&chen,w.-c.nonvolatilememorybasedonpentaceneorganicfield-effecttransistorswithpolystyrenepara-substitutedoligofluorenependentmoietiesaspolymerelectrets.j.mater.chem.22,5820(2012).

19.10.li,w.,guo,f.n.,ling,h.f.,zhang,p.,yi,m.d.,wang,l.y.,wu,d.q.,xie,l.h.&huang,w.high-performancenonvolatileorganicfield-effecttransistormemorybasedonorganicsemiconductorheterostructuresofpentacene/p13/pentaceneasbothchargetransportandtrappinglayers.advsci.4,1700007(2017)。

20.11.yu,y.,bian,l.y.,chen,j.g.,ma,q.h.,li,y.x.,ling,h.f.,feng,q.y.,xie,l.h.,yi,m.d.&huang,w.4,5-diazafluorene-baseddonor

–

acceptorsmallmoleculesaschargetrappingelementsfortunablenonvolatileorganic

transistor memory.adv.sci.5,1800747(2018).

技术实现要素:

21.本发明的目的在于,针对上述问题,本发明提出一种提升抗疲劳特性的并五苯有机场效应晶体管,促进其实际应用。在cn201911336850.8的中国发明专利及 20255cjh的美国发明专利申请,本发明团队提出了一种在并五苯/聚合物界面引入 n-型半导体过渡层来提升并五苯有机场效应晶体管存储器件性能的方法。在 cn202011153410.1的中国发明专利及20256cjh的美国发明专利申请,提出了一种在聚合物/绝缘层界面引入n-型半导体插层来提升并五苯有机场效应晶体管存储器件性能的方法。在其基础之上,我们再提出一种使用具有浅能级陷阱的电荷俘获介质取代原先并五苯有机场效应晶体管中的聚合物介质,在保持器件其他优异性能的同时,进一步提高其抗疲劳特性,促进其实际应用。

22.本发明的技术方案是,一种提升并五苯有机场效应晶体管抗疲劳特性的晶体管,并五苯有机场效应晶体管器件中的电荷俘获介质层具有大量的浅能级空穴陷阱,且器件具有如图2所示的底栅型结构:栅电极/栅绝缘层/n-型半导体薄膜/具有浅能级陷阱的电荷俘获介质层/隧穿层/并五苯/源(漏)电极;栅电极1为导体,电阻率在 0.1-0.001ω

·

㎝

之间;栅绝缘层介质薄膜2为绝缘体,厚度范围为5-150nm;n-型半导体薄膜层3的厚度为1-200nm;具有浅能级空穴陷阱的电荷俘获介质层4,厚度为 1-100nm;隧穿层5为绝缘体,厚度范围为1-20nm;并五苯6厚度范围为1-100nm;源漏电极7和8为导体,电阻率在0.1-0.001ω

·

㎝

之间,厚度范围为50-200nm;另一种是顶栅型,从下到上分别是源(漏)电极/并五苯/隧穿层/具有浅能级空穴陷阱电荷俘获介质层/n-型半导体薄膜/栅绝缘层/栅电极,也是包括在内的;两种从本质上并无差别,所以这两种结构都属于本发明的范围。

23.栅电极可以是金属、导电氮化物或导电氧化物材料;底栅型场效应晶体管的栅电极还可以是n-型重掺高导硅或者p-型重掺高导硅等半导体材料;底栅型场效应晶体管的栅电极还可以是柔性的带导电涂层的基板。

24.栅绝缘层介质薄膜可以是二氧化硅、氧化铝等绝缘体,其作用是阻挡被n-型半导体薄膜俘获的电荷逃逸到栅电极;栅绝缘层介质薄膜还可以是聚合物绝缘体,如 pmma、p(vdf-trfe)等。

25.n-型半导体薄膜提供可以移动的n-型载流子(电子),且具有一定的载流子浓度;基于静电感应效应,通过n-型半导体中靠近绝缘层界面处的感生电子降低并五苯与绝缘层界面处的空穴势垒高度,有效降低并五苯有机半导体晶体管的编程/擦除工作电压。

26.n-型半导体薄膜为n-型无机半导体薄膜,包括硒化锌(znse

1-x

)、或硫化锌 (zns

1-x

)、或氧化锌(zno

1-x

),x在0.001-0.5之间;或铟镓锌氧化物(igzo),或缺氧的氧化物薄膜,或缺氧的复合氧化物薄膜,如zrhfo

2-δ

等;或金属氮氧化物,如 tio

x

ny等;但n-型半导体薄膜不限于上述几种有机薄膜;制备方法包括磁控溅射法,热蒸发方法,或电子束蒸发方法,其厚度范围为1-200nm,是结晶态薄膜或非晶态薄膜。

27.n-型半导体薄膜还可以是n-型有机小分子半导体薄膜,如n-n

”‑

二3-正戊烷基-3,4,9,10-苝二酰亚胺(ptcdi-c13)、n-n

”‑

二正十三烷基-3,4,9,10-苝二酰亚胺(ep-pdi)等,但不限于上述几种有机薄膜;n-型半导体薄膜是结晶态薄膜、半晶态薄膜或者非晶态薄膜。n-型有机半导体薄膜制备方法包括溶液方法,如甩胶法 (spin-coating),溶胶-凝胶法

(sol-gel),或喷涂法(spray),或丝网印刷法 (silk-screen printing),喷墨打印法(ink-jetting)等,或热蒸发方法,或其他类似的物理及化学薄膜制备方法;其厚度范围为1-100nm。

28.n-型半导体薄膜还可以为两种n-型半导体复合结构薄膜;可以是在n-型有机半导体薄膜表面再制备一层n-型无机半导体薄膜,或在n-型有机半导体薄膜表面再制备一层n-型无机半导体薄膜;复合结构薄膜中n-型有机半导体薄膜的厚度范围为0.5-60nm,n-型无机半导体薄膜的厚度范围为0.5-60nm,但是复合结构薄膜的厚度范围为1-100nm;n-型半导体薄膜还可以为多层无机半导体薄膜与有机半导体薄膜之间的组合。

29.具有浅能级陷阱的电荷俘获介质层在有机场效应晶体管结构中起空穴俘获作用,可以是具有浅能级陷阱的聚合物介质薄膜;或是具有浅缺能级陷阱的有机小分子介质薄膜;或是具有浅能级陷阱的无机介质膜。

30.所述具有浅能级陷阱的电荷俘获介质薄膜,存储于其中的电荷(空穴)可以在正的脉冲栅压下完全被解除束缚(de-trap),或绝大部分存储于其中的电荷(空穴) 可以在正的脉冲栅压下被解除束缚(de-trap);或者说在上述电荷俘获介质层薄膜中电荷(空穴)陷阱基本为浅能级陷阱,深能级陷阱密度极低。

31.理论上,n-型半导体是理想的空穴俘获介质。

32.具有浅能级陷阱的电荷俘获层介质可以是n-型无机半导体薄膜,包括硒化锌 (znse

1-x

)、或硫化锌(zns

1-x

)、或氧化锌(zno

1-x

),x在0.001-0.5之间;或铟镓锌氧化物(igzo),或缺氧的氧化物薄膜,或缺氧的复合氧化物薄膜,如zrhfo

2-δ

等;或金属氮氧化物,如tio

x

ny等;但n-型半导体薄膜不限于上述几种有机薄膜;制备方法包括磁控溅射法,热蒸发方法,或电子束蒸发方法,是结晶态薄膜或非晶态薄膜。

33.具有浅能级陷阱的电荷俘获介质层还可以是n-型有机小分子半导体薄膜,如 n-n

”‑

二3-正戊烷基-3,4,9,10-苝二酰亚胺(ptcdi-c13)、n-n

”‑

二正十三烷基

ꢀ‑

3,4,9,10-苝二酰亚胺(ep-pdi)等,但不限于上述几种有机薄膜;n-型有机小分子半导体薄膜是结晶态薄膜、半晶态薄膜或者非晶态薄膜。

34.具有浅能级陷阱的电荷俘获介质层还可以是n-型有机聚合物半导体薄膜,如poly-{[n,n'-bis(2-octyldodecyl)naphthalene-1,4,5,8-bis(dicarboximide)-2, 6-diyl]-alt-5,5'-(2,2'-bithiophene)}(n2200)等,但不限于上述几种有机薄膜; n-型有机聚合物半导体薄膜是结晶态薄膜、半晶态薄膜或者非晶态薄膜。

[0035]

n-型有机小分子半导体薄膜及n-型有机聚合物半导体薄膜的制备方法包括溶液方法,如甩胶法(spin-coating),溶胶-凝胶法(sol-gel),或喷涂法(spray),或丝网印刷法(silk-screen printing),喷墨打印法(ink-jetting)等,或热蒸发方法,或其他类似的物理及化学薄膜制备方法;其厚度范围为1-100nm。

[0036]

具有浅能级陷阱的电荷俘获介质层还可以为两种n-型半导体复合结构薄膜;可以是在n-型有机半导体薄膜表面再制备一层n-型无机半导体薄膜,或在n-型有机半导体薄膜表面再制备一层n-型无机半导体薄膜;复合结构薄膜中n-型有机半导体薄膜的厚度范围为0.5-60nm,n-型无机半导体薄膜的厚度范围为0.5-60nm,但是复合结构薄膜的厚度范围为1-100nm;n-型半导体薄膜还可以为多层无机半导体薄膜与有机半导体薄膜之间的组合;但不限于上述几种薄膜组合方式;

[0037]

并五苯薄膜的制备方法包括溶液方法,如甩胶法(spin-coating),溶胶-凝胶法(sol-gel),或喷涂法(spray),或丝网印刷法(silk-screen printing),喷墨打印法(ink-jetting)等,或热蒸发方法,或其他类似的物理及化学薄膜制备方法;其厚度范围为1-50nm。

[0038]

并五苯薄膜与具有浅能级陷阱的电荷俘获介质层薄膜之间的设有的隧穿层薄膜可以是二氧化硅、氧化铝等绝缘体,其作用是在电场驱动空穴从并五苯到电荷俘获介质层薄膜后,当外电压撤除后阻挡空穴载流子返回或逃逸到并五苯薄膜中;并五苯与具有浅能级陷阱的电荷俘获介质层薄膜之间的隧穿层薄膜还可以是聚合物绝缘体,如pmma、p(vdf-trfe)等,厚度在1nm-20nm之间。

[0039]

所述方法得到的并五苯有机场效应晶体管存储器件,有机场效应晶体管器件的结构为底栅型:从下到上分别是栅电极/栅绝缘层/n-型半导体薄膜/具有浅能级陷阱的电荷俘获介质层/隧穿层/并五苯/源(漏)电极;有机场效应晶体管器件的结构或为顶栅型,从下到上分别是源(漏)电极/并五苯/隧穿层/具有浅能级陷阱的电荷俘获介质层/n-型半导体薄膜/栅绝缘层/栅电极。

[0040]

n-型半导体薄膜中由于并五苯靠近隧穿层界面处带正电界面层的静电作用产生感应电荷(电子),n-型半导体薄膜中电子被吸引到靠近电荷俘获层薄膜界面处,从而积累高密度的电子;而在n-型半导体薄膜内部离化的施主形成带正电的空间电荷区。由于电荷俘获层/n-型半导体界面处高浓度电子的积累,使得并五苯/隧穿层界面处总体的正电荷电场强度大幅减小,从而使得并五苯与隧穿层界面处空穴势垒的高度大幅降低;并五苯与隧穿层界面处空穴势垒高度的大幅降低使得驱动空穴载流子从并五苯进入电荷俘获介质层,或驱动空穴载流子从电荷俘获介质层返回并五苯薄膜所需的工作电压有效降低,即有机半导体场效应晶体管器件的编程/擦除电压有效降低;

[0041]

并五苯与电荷俘获介质层之间的隧穿层薄膜的设置目的在于,在外部脉冲栅压撤销后,隧穿层薄膜起到阻挡原来积聚(或俘获)在电荷俘获介质层中的空穴会返回到并五苯薄膜中,提升并五苯有机半导体场效应晶体管存储器件的保持特性。

[0042]

使用具有浅缺陷能级的电荷俘获介质层的目的是,在擦除(erasing)操作中,俘获在具有浅缺陷能级的电荷俘获介质中的空穴可以在较低的正脉冲栅压下被解除束缚,并返回到并五苯沟道中。在多次的编程/擦除操作后其擦除操作的转移特性曲线与初始的擦除操作曲线相比,其阈值电压不发生,或仅发生较少的偏移,使得用电学方法读出的开态/关态电流比不发生,或仅发生较少的衰减,从而提升并五苯场效应晶体管的抗疲劳特性。

[0043]

有益效果:在结构为栅电极/栅绝缘层/n-型半导体薄膜/具有浅能级陷阱的电荷俘获介质层/隧穿层/并五苯/源(漏)电极的有机场效应晶体管器件中,使用不存在如聚合物介质中的深能级陷阱,或者深能级陷阱密度极低的介质薄膜作为空穴俘获介质,可以有效防止并五苯有机半导体晶体管存储器件在反复的编程/擦除操作过程中空穴被电荷俘获介质中的深能级陷阱俘获,导致在多次编程/擦除循环动作后器件转移特性曲线的阈值电压发生偏移,劣化器件的抗疲劳特性。

附图说明

[0044]

图1.现有器件并五苯ofet器件转移特性显示的其抗疲劳特性退化示意图;

[0045]

图2:本发明以具有浅能级陷阱介质作为电荷俘获层的并五苯有机场效应晶体管结构示意图,其中1为栅电极,2为栅绝缘层介质,3为n-型半导体薄膜,4为具有浅能级陷阱的电荷俘获介质,5为隧穿层薄膜,6为并五苯,7和8分别为源、漏电极。

[0046]

图3.本发明以pvn为电荷俘获介质的并五苯ofet器件结构示意图。

[0047]

图4.以pvn为电荷俘获介质的并五苯ofet器件的转移特性曲线。

[0048]

图5a,图5b是以pvn为电荷俘获介质的并五苯ofet器件的抗疲劳特性曲线(图 5a),以及抗疲劳测试前后的转移特性曲线(图5b)。

[0049]

图6a,图6b及图6c是以pvn为电荷俘获介质的并五苯ofet器件在黑暗条件下进行200次的抗疲劳测试,及分别进行后续的在635nm(图6a),532nm(图6b)及 375nm(图6c)单色光照射下的抗疲劳测试测试结果图。

[0050]

图7a,图7b,图7c是以pvn为电荷俘获介质的ofet器件在黑暗条件下及分别在635nm,532nm及375nm光照条件下(30分钟后)的转移特性曲线,结果分别如图 7a,图7b,图7c所示。

[0051]

图8.pvn中陷阱能级及其密度分布示意图。

[0052]

图9.以n2200作为电荷俘获介质的ofet器件的转移特性曲线。

[0053]

图10a、图10b分别以n2200作为电荷俘获介质的ofet器件在黑暗条件(图10a) 和在635nm,532nm及375nm单色光(图10b)照射下器件经历16000次连续编程/擦除循环操作过程中擦除态源漏电流的变化图。

[0054]

图11为以缺氧氧化锌薄膜为电荷俘获介质的并五苯ofet器件的转移特性曲线。

[0055]

图12为以缺氧氧化锌薄膜为电荷俘获介质的并五苯ofet器件的编程/擦除(抗疲劳特性)特性曲线。

[0056]

图13为以缺氧氧化锌薄膜为电荷俘获介质及以三氧化二铝为隧穿层的并五苯 ofet器件的编程/擦除(抗疲劳特性)特性曲线。

[0057]

图14为器件的编程/擦除(抗疲劳特性)特性曲线。

具体实施方式

[0058]

实施例1

[0059]

为进行对比实验,首先制备以pvn为电荷俘获介质的并五苯ofet器件,其结构示意图如图3所示。以《100》-晶向的重掺p-si作为栅电极,电阻率小于0.005ω

·

㎝

;以厚度为90nm的热氧化二氧化硅为栅绝缘层;以厚度为20nm的缺氧的氧化锌(zno) 作为n-型半导体层;以pvn作为电荷俘获介质,厚度为10nm;隧穿层绝缘介质为聚甲基丙烯酸乙酯(pmma),厚度为4nm;并五苯厚度为40nm;以铜膜作为源漏电极,厚度为80nm;

[0060]

具体制备工艺步骤如下:

[0061]

将90nm热氧化sio2覆盖的p-si衬底先后用丙酮、乙醇和去离子水超声清洗10 分钟,并用氮气枪吹干备用。使用磁控溅射法,在上述p-si衬底上生长20nm的氧化锌(zno)。为了尽可能多地增加zno中的氧空位,以增加载流子浓度及缺陷能级的密度,在制备时溅射气体使用纯的氩气。由于氧空位的存在,zno薄膜呈n-型半导体特征。利用甩胶方法将浓度为2mg/ml的pvn甲苯溶液旋涂到上述zno薄膜上,转速为4000rpm,时间为60秒,然后在手套箱中80℃干燥30分钟。然后,利用热蒸发方法借助于掩模版制备40nm厚度的并五苯薄膜,生长

速度为最后,同样使用热蒸发工艺借助于另一套掩模版制备80nm厚度的cu膜作为源漏电极,生长速度为

[0062]

接着使用旋涂法,在生长了zno的衬底上生长4nm的pmma作为隧穿层。称取 10mg的pmma粉末,再用量筒量取10ml的甲苯作为溶剂,在50℃的恒温下搅拌8小时,配成1mg/ml的pmma溶液。以3000rpm的转速高速旋转60s旋涂pmma溶液,并在80℃的恒温条件下退火30min。

[0063]

接着使用真空热蒸镀法,在生长完pmma的上述衬底上生长40nm的并五苯。

[0064]

在生长完并五苯的样品上采用真空热蒸镀法生长边长为300μm,厚度为80nm 的铜(cu)电极。

[0065]

将上述器件的一角用金刚刀划衬底,直至漏出p-si,作为栅电极;

[0066]

使用keithley 4200(4200-scs)半导体分析系统对制备的器件进行电学性能测试,通过测试电流与外加电压的响应关系,来分析器件的输出特性、转移特性、擦写速度、抗疲劳性能以及保持性能等性能参数;

[0067]

器件实现开关的过程如下:工作时,在器件的两个相邻的cu电极即源漏电极之间施加一定电压,如果没有栅电压或者栅电压很小,源漏电极之间的并五苯中电流通常很小,电流特性与绝缘体类似,器件处于关状态;当在栅电极上施加足够高的电压,则在并五苯中靠近绝缘层的界面处产生一个导电沟道,源漏电极之间的电流迅速增大,使器件导通,成为开状态;这样器件就实现了开关过程。

[0068]

图4是以pvn为电荷俘获介质的并五苯ofet器件的转移特性图,在较低的工作电压下,器件的编程及擦除曲线的阈值电压显示出较大的偏移,即器件具有较大的存储窗口。

[0069]

图5a是器件的抗疲劳特性曲线。在

±

30v/1s的脉冲栅压下,经过200次的擦除/编程操作循环后,由于擦除态转移特性曲线的阈值电压的偏移,导致器件擦除态的源漏电流从9.6*10-7

a衰减到7.2*10-9

a。图5b是器件抗疲劳测试前后的转移特性曲线,从图5b可以看到,器件抗疲劳测试前后其擦除态的转移特性曲线间其阈值电压有1.3v的偏移。运用公式:

[0070][0071]

(其中ci是栅介质单位面积的电容,e是基本的电荷单位),可以估算出在抗疲劳测试开始前被pvn介质俘获的电荷(空穴)中有9.3%无法在正的栅压下被解除束缚。

[0072]

我们用光激发辅助的手段测试了pvn薄膜中空穴陷阱及其密度的分布,方法如下。理论上,陷阱深度为-e0的深能级陷阱中被束缚的空穴可以被单光子能量大于等于e0的物理光线激发,并在合适的正的栅压下被转移到并五苯沟道中,此为光激发辅助下的擦除操作。我们对上述并五苯ofet器件在黑暗条件下进行200次的抗疲劳测试后再分别进行后续的在635nm,532nm及375nm单色光照射下的抗疲劳测试,结果如图6a,6b及6c所示。

[0073]

从图6a中可以看出,在635nm的单色光(对应于1.95ev能量的光子)照射下,器件源漏间的电流经过反复的编程/擦除操作后继续下降,意味着在陷阱深度小于 1.95ev的陷阱中被激发的空穴又被pvn中更深能级的陷阱捕获。此外,还可以看到,在第四个200-编程/擦除循环操作中,器件源漏间的电流经过反复的编程/擦除操作后继续下降,且电流最低点也继续下降,意味着有更多的在陷阱深度小于1.95ev的陷阱中被激发的空穴又继续被pvn中更深能级的陷阱捕获。

[0074]

从图6b中可以看出,在532nm的单色光(对应于2.33ev能量的光子)照射下,器件源漏间的电流经过反复的编程/擦除操作中显示与图5a的趋势一致,意味着在陷阱深度小于2.33ev的陷阱中被激发的空穴又被pvn中更深能级的陷阱捕获,即pvn 中还有很多更深的陷阱存在。

[0075]

从图6c中可以看出,在375nm的单色光(对应于3.31ev能量的光子)照射下,器件源漏间的电流经过反复的编程/擦除操作中在其达到最高值后,其峰值几乎保持不变,仅有极小的下降,意味着pvn中仍然具有比3.31ev更深的陷阱存在,但密度极低。

[0076]

我们测试了另外新鲜的ofet器件在黑暗条件下及分别在635nm,532nm及375nm 光照条件下(30分钟后)的转移特性曲线,结果如图7a,7b,7c所示。从图7a,7b, 7c可以得到,光照后器件的存储窗口分别为15.9v,18v及21.8v。根据公式(1), pvn中对应于635nm,532nm及375nm光照条件下的空穴陷阱的面密度分别为2.13

×ꢀ

10

12

cm-2

,2.41

×

10

12

cm-2

and 2.92

×

10

12

cm-2

,因此我们可以获得pvn中空穴陷阱的分布图如图8所示。从图8我们可以清楚地看到在对应于激发光波长532-375nm范围(2.33-3.71ev)内pvn中存在最高密度的空穴陷阱,而该类陷阱中被俘获的空穴在我们器件所使用的工作电压下是无法被解除束缚的,即无法被擦除。这就是其抗疲劳特性退化的直接原因。

[0077]

为了提升并五苯ofet器件的抗疲劳特性,我们使用具有潜能级空穴陷阱的n

‑ꢀ

型聚合物半导体poly-{[n,n'-bis(2-octyldodecyl)naphthalene-1,4,5,8-[0078]

bis(dicarboximide)-2,6-diyl]-alt-5,5'-(2,2'-bithiophene)} (p(ndi2od-2t);n2200)作为电荷俘获介质,器件结构示意图如图3所示,其中每个介质层的厚度与pvn作为电荷俘获介质的ofet器件一致,仅使用n2200代替pvn作为电荷俘获介质。

[0079]

图9显示以n2200作为电荷俘获介质的ofet器件的转移特性曲线。在

±

15v 的工作电压下器件显示出8.5v的存储窗口,据此计算得到的器件的开关电流比为 1.25

×

105,场效应迁移率为0.16cm

2 v-1 s-1

。

[0080]

图9显示以n2200作为电荷俘获介质ofet器件的抗疲劳特性曲线。器件经过 4000次的编程/擦除操作循环后,器件擦除态的源漏电流仅从3*10-8

a变化到1.4*10-8 a。与pvn作为电荷存储介质的ofet器件相比,其稳定型获得了质的提升。

[0081]

图10是器件在黑暗条件和在635nm,532nm及375nm单色光照射下器件经历 16000次连续编程/擦除循环操作过程中擦除态源漏电流的变化图。我们可以发现,在黑暗条件和在635nm及532nm单色光照射条件下,擦除态源漏电流都没有特别急剧的下降。特别是在375nm单色光照射下,在达到峰值后擦除态源漏电流几乎保持不变。这意味着尽管n2200中依然存在深能级陷阱,但其密度极低。

[0082]

实施例2

[0083]

实施例2与实施例1的区别在于,在实施例2中使用同样具有浅能级空穴陷阱材料zno取代了实施例1中的n2200。

[0084]

zno使用磁控溅射法在纯ar中生长。由于氧空位的存在,zno薄膜呈n-型半导体特征。

[0085]

图11是以缺氧氧化锌薄膜为电荷俘获介质的并五苯ofet器件的转移特性曲线。在编程/擦除扫描电压v

gs

=

±

15v时,约有7.8v的窗口,i

on

/i

off

=1

×

105。

[0086]

图12是以缺氧氧化锌薄膜为电荷俘获介质的并五苯ofet器件的编程/擦除(抗疲

劳特性)特性曲线。在擦除脉冲栅压ve=15v/s,读取栅压vr=0v及编程脉冲栅压 v

p

=-15v/s,读取栅压vr=3v下,器件经过10000次编程/擦除循环后器件的开态及关态的电流密度仍保持极高的稳定性。

[0087]

实施例3

[0088]

本实施例与实施例2的区别在于,隧穿层介质为al2o3,制备方法为原子层沉积方法(ald)。图13是器件的转移特性曲线,在编程/擦除扫描电压v

gs

=

±

15v时,器件的存储窗口约为4.6v。器件的编程/擦除(抗疲劳特性)特性曲线如图14所示。器件在经历1000次的编程/擦除动作循环后,依然保持了极高的开态与关态的电流比。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1