具有热稳定硅化物栅极功函数金属的CMOS架构的制作方法

本公开涉及集成电路,并且更特别地,涉及晶体管。

背景技术:

1、集成电路继续缩小到更小的特征尺寸和更高的晶体管密度。关于增加晶体管密度的更近的发展通常被称为三维(3d)集成,其通过利用z维度(在x维度和y维度中向上而不是横向向外构建)来扩展晶体管密度。一些这样的3d集成电路是利用被称为层转移(layertransfer)的技术形成的。这种层转移可以包括例如接合和基于氢或基于氢/氦的分裂技术。通过在两个不同的晶圆(有时称为寄主晶圆(host wafer)和施主晶圆(donor wafer)或衬底)上分别形成晶体管,并且然后经由氧化物接合层将这两个晶圆接合到一起,随后进行化学机械抛光(cmp)操作以去除多余的晶圆,来形成其他3d集成电路。通过在相同鳍状物结构的上部区域和下部区域上形成晶体管来实现另外的3d集成电路。在任何这样的情况下,这样的3d集成方案提供了堆叠的晶体管架构,并且引起了许多不可忽视的问题。

技术实现思路

技术特征:

1.一种集成电路结构,包括:

2.根据权利要求1所述的集成电路结构,其中,所述化合物的所述一种或多种金属是一种或多种第一金属,并且所述第一栅极电极还包括一种或多种第二金属,其中,所述一种或多种第二金属的至少一部分在所述化合物的第一部分与第二部分之间。

3.根据权利要求2所述的集成电路结构,其中,所述一种或多种第一金属包括钛或钽,并且所述一种或多种第二金属包括钴或钨。

4.根据权利要求2所述的集成电路结构,其中,所述化合物是双金属硅化物,使得所述一种或多种第二金属的至少一部分在所述双金属硅化物的第一部分与第二部分之间。

5.根据权利要求1至4中任一项所述的集成电路结构,其中,所述化合物的所述一种或多种金属是一种或多种第一金属,并且所述第一栅极电极还包括一种或多种第二金属,并且其中,包括所述一种或多种第二金属的顶表面与硅化物功函数层的顶表面共面。

6.根据权利要求1至4中任一项所述的集成电路结构,其中,所述化合物的所述一种或多种金属是一种或多种第一金属,并且所述第一栅极电极还包括一种或多种第二金属,并且其中,硅化物功函数层的顶表面低于包括所述一种或多种第二金属的顶表面,使得包括所述一种或多种第二金属的所述顶表面不与所述硅化物功函数层的所述顶表面共面。

7.根据权利要求1至4中任一项所述的集成电路结构,其中,所述第一高k栅极电介质和所述第二高k栅极电介质中的每一者的厚度在5埃至25埃的范围内,并且其中,包括所述化合物的所述层的厚度在20埃至100埃的范围内。

8.根据权利要求1至4中任一项所述的集成电路结构,其中,包括所述化合物的所述层是第一层,所述第一栅极电极还包括具有第一非邻接部分和第二非邻接部分的第二层,所述第一非邻接部分在所述栅极电极与所述高k栅极电介质的第一部分之间,并且所述第二非邻接部分在所述栅极电极与所述高k栅极电介质的第二部分之间,并且其中,所述第二层不在所述栅极电极与所述高k栅极电介质的第三部分之间。

9.根据权利要求8所述的集成电路结构,其中,所述第二层的厚度在2埃到10埃的范围内。

10.根据权利要求9所述的集成电路结构,其中,所述第二层包括钛和氮。

11.根据权利要求1至4中任一项所述的集成电路结构,其中,所述第一栅极电极是n型金属氧化物半导体(nmos)栅极电极,并且所述第二栅极电极是p型金属氧化物半导体(pmos)栅极电极。

12.根据权利要求1至4中任一项所述的集成电路结构,其中,所述第一半导体主体包括第一纳米带,并且所述第一栅极结构环绕所述第一纳米带,并且其中,所述第二半导体主体包括第二纳米带,并且所述第二栅极结构环绕所述第二纳米带。

13.根据权利要求1至4中任一项所述的集成电路结构,包括:

14.根据权利要求1至4中任一项所述的集成电路结构,其中,所述第一栅极电极的所述化合物是硅化物,并且所述第二栅极电极不含硅化物。

15.一种集成电路结构,包括:

16.根据权利要求15所述的集成电路结构,其中,所述一种或多种第一金属包括钛或钽,并且所述一种或多种第二金属包括钴或钨。

17.根据权利要求15或16所述的集成电路结构,其中,所述化合物是包括一种金属的单金属硅化物,或者是包括第一金属和第二金属的双金属硅化物。

18.根据权利要求17所述的集成电路结构,其中,所述化合物包括多个接合配置和/或相。

19.根据权利要求17所述的集成电路结构,其中,所述化合物包括包含硅和所述第一金属的第一相、以及包含硅和所述第二金属但不包括所述第一金属的第二相。

20.根据权利要求17所述的集成电路结构,其中,所述化合物包括包含第一化学计量或接合配置的第一相、以及包含第二化学计量或接合配置的第二相。

21.根据权利要求15或16所述的集成电路结构,包括:

22.一种集成电路,包括:

23.根据权利要求22所述的集成电路结构,其中,所述第一栅极电极是n型金属氧化物半导体(nmos)栅极电极,并且所述第二栅极电极是p型金属氧化物半导体(pmos)栅极电极。

24.根据权利要求22所述的集成电路结构,其中,所述电介质主体连同所述第一半导体主体和所述第二半导体主体以及所述第一栅极结构和所述第二栅极结构是叉板式晶体管结构的一部分。

25.根据权利要求22至24中任一项所述的集成电路结构,其中,所述化合物的所述一种或多种金属是一种或多种第一金属,并且所述第一栅极电极还包括一种或多种第二金属,其中,所述一种或多种第二金属的至少一部分在所述化合物的第一部分与第二部分之间。

技术总结

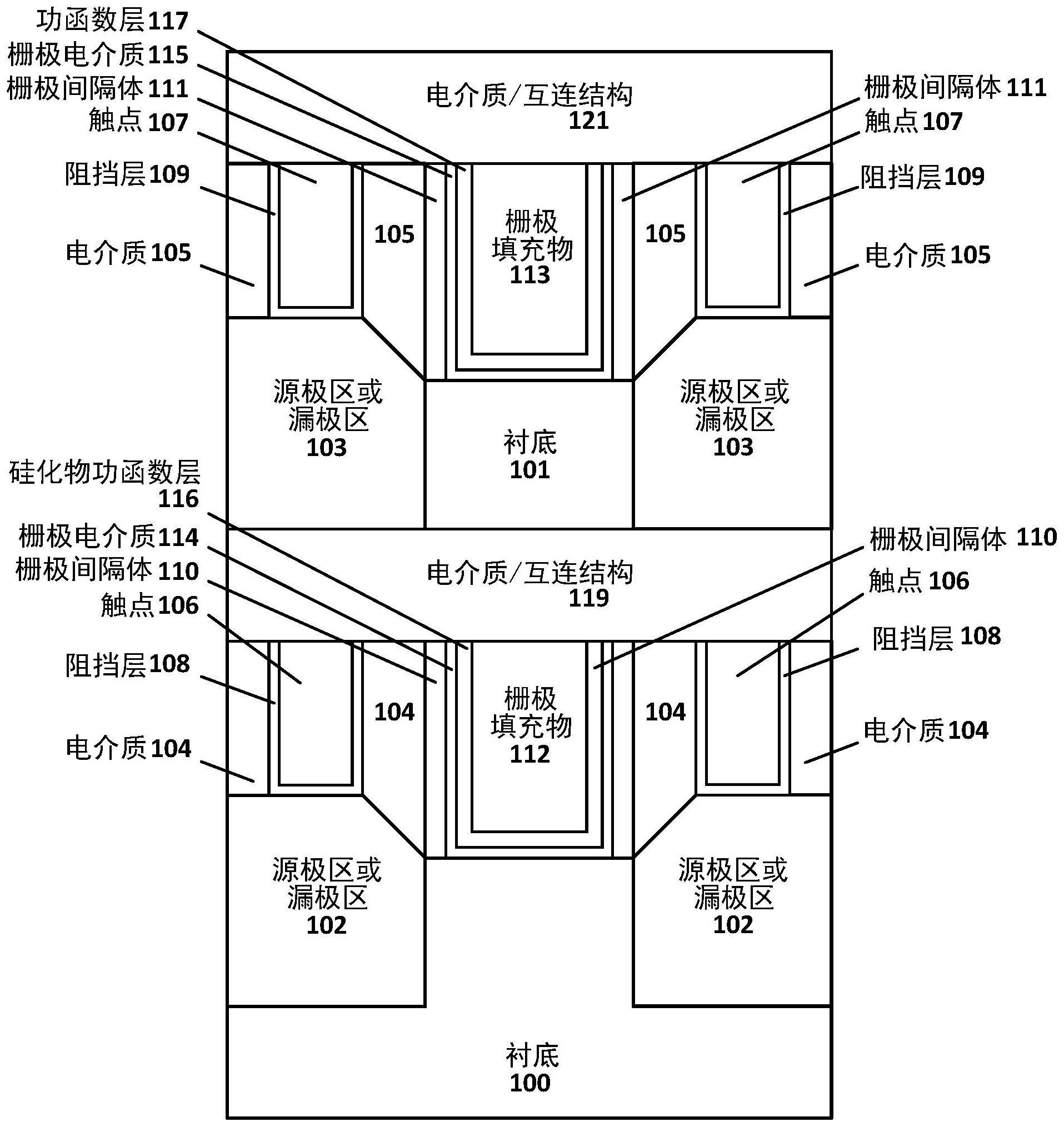

一种具有晶体管架构的集成电路,包括第一半导体主体和第二半导体主体。第一半导体主体和第二半导体主体相对于彼此垂直(例如,堆叠配置)或水平(叉板式配置)布置,并且通过绝缘体材料彼此分离,并且每个半导体主体都可以配置用于平面或非平面晶体管拓扑。第一栅极结构在第一半导体主体上,并且包括第一栅极电极和第一高k栅极电介质。第二栅极结构在第二半导体主体上,并且包括第二栅极电极和第二高k栅极电介质。在示例中,第一栅极电极包括包含硅和一种或多种金属的化合物的层;第二栅极结构可以包括或不包括硅化物功函数层。在一个示例中,第一栅极电极为n型,并且第二栅极电极为p型。

技术研发人员:A·D·利拉克,O·阿克顿,C-Y·黄,G·杜威,E·曼内巴赫,A·潘,W·拉赫马迪,J·T·卡瓦列罗斯

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!