电子封装件及其制法的制作方法

本发明有关一种半导体装置,尤指一种具电子组件堆叠结构的电子封装件及其制法。

背景技术:

1、随着电子产业的蓬勃发展,电子产品也逐渐迈向多功能、高性能的趋势。同时,目前应用于芯片封装领域的技术,包含有例如芯片尺寸构装(chip scale package,简称csp)、芯片直接贴附封装(direct chip attached,简称dca)或多芯片模块封装(multi-chip module,简称mcm)等覆晶型态的封装模块等。

2、图1为现有半导体封装件1的剖面示意图。如图1所示,该半导体封装件1于一封装层11中嵌埋多个半导体芯片1a,1b与多个导电柱13,且于该封装层11上侧形成电性连接该多个导电柱13的第一布线结构10,并于该封装层11下侧形成电性连接该多个半导体芯片1a,1b与多个导电柱13的第二布线结构12。

3、但是,现有半导体封装件1中,将多个半导体芯片1a,1b整合于单一堆叠组件的方式采用并排(side by side)方式,致使两个半导体芯片1a,1b之间的横向(如图1所示的箭头方向x)电性信号的传输距离过长,导致电性表现不佳,因而无法符合终端产品的效能需求。

4、因此,如何克服上述现有技术的问题,实已成为目前业界亟待克服的难题。

技术实现思路

1、鉴于上述现有技术的种种缺陷,本发明提供一种电子封装件及其制法,以至少部分地解决现有技术中的问题。

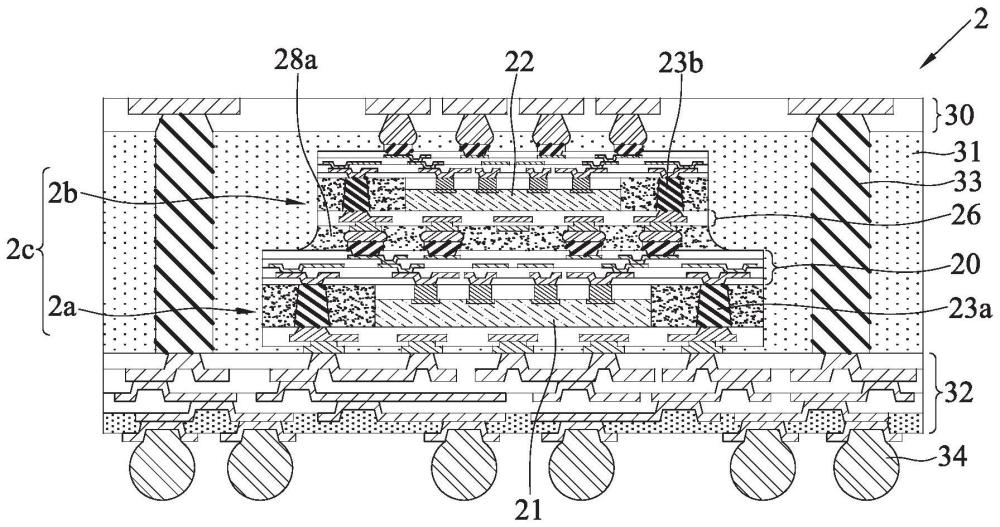

2、本发明的电子封装件,包括:封装层;一堆叠组件,其嵌埋于该封装层中,且该堆叠组件包含第一电子模块与堆叠于该第一电子模块上的第二电子模块,其中,该第一电子模块包含一第一包覆层、至少一嵌埋于该第一包覆层中的第一电子组件、多个嵌埋于该第一包覆层中的第一导电通孔、及至少一设于该第一包覆层上以电性连接该第一电子组件与该多个第一导电通孔的第一线路结构,且该第二电子模块包含一第二包覆层、至少一嵌埋于该第二包覆层中的第二电子组件、多个嵌埋于该第二包覆层中的第二导电通孔、及至少一设于该第二包覆层上以电性连接该第二电子组件与该多个第二导电通孔的第二线路结构,以令该多个第一导电通孔与该多个第二导电通孔电性导通;多个导电柱,其嵌埋于该封装层中;以及布线结构,其形成于该封装层上且电性连接该多个导电柱与该堆叠组件。

3、本发明还提供一种电子封装件的制法,包括:提供第一电子模块与第二电子模块,其中,该第一电子模块包含一第一包覆层、至少一嵌埋于该第一包覆层中的第一电子组件、多个嵌埋于该第一包覆层中的第一导电通孔、及至少一设于该第一包覆层上以电性连接该第一电子组件与该多个第一导电通孔的第一线路结构,且该第二电子模块包含一第二包覆层、至少一嵌埋于该第二包覆层中的第二电子组件、多个嵌埋于该第二包覆层中的第二导电通孔、及至少一设于该第二包覆层上以电性连接该第二电子组件与该多个第二导电通孔的第二线路结构;将该第一电子模块与该第二电子模块相互堆叠,以形成堆叠组件,并使该多个第一导电通孔与该多个第二导电通孔电性导通;将该堆叠组件设于一承载板上,且该承载板上形成有多个导电柱,其中,该堆叠组件以该第一电子模块及/或第二电子模块接置于该承载板上;形成封装层于该承载板上,以令该封装层包覆该多个导电柱与该堆叠组件;形成布线结构于该封装层上,以令该布线结构电性连接该多个导电柱与该堆叠组件;以及移除该承载板。

4、前述的制法中,还包括于该承载板上形成另一布线结构,以令该堆叠组件接置于该另一布线结构上。

5、前述的制法中,该承载板与该多个导电柱构成为一体成形的金属件。

6、前述的电子封装件及其制法中,该第一电子模块的构造与该第二电子模块的构造为相同。

7、前述的电子封装件及其制法中,该封装层、该第一包覆层与该第二包覆层的至少两者的材料为相同。

8、前述的电子封装件及其制法中,该封装层、该第一包覆层与该第二包覆层的至少两者的材料为相异。

9、前述的电子封装件及其制法中,该至少一第一线路结构为多个第一线路结构,以分别设于该第一包覆层的相对两侧上,且该至少一第二线路结构为多个第二线路结构,以分别设于该第二包覆层的相对两侧上。例如,该多个第一线路结构的其中一者具有多个第一电性接触垫,而另一者具有多个第一导电凸块,且该多个第二线路结构的其中一者具有多个第二导电凸块,而另一者具有多个第二电性接触垫,以令该第二电子模块以该多个第二导电凸块通过焊锡材料接置于该第一电子模块的该多个第一电性接触垫上。进一步,可以结合材包覆该多个第二导电凸块、焊锡材料与第一电性接触垫。或者,以封装材包覆该多个第二导电凸块、焊锡材料、第一电性接触垫与该第二电子模块。甚至于,先以结合材包覆该多个第二导电凸块、焊锡材料与第一电性接触垫,再以封装材包覆该结合材与该第二电子模块。

10、前述的电子封装件及其制法中,该第一线路结构或第二线路结构具有多个电性连接该布线结构的导电凸块。

11、前述的电子封装件及其制法中,该第一线路结构或第二线路结构具有多个电性连接该布线结构的电性接触垫。

12、由上可知,本发明的电子封装件及其制法中,主要通过将该第一电子模块与第二电子模块相互堆叠,并以该第一导电通孔与第二导电通孔作为该第一电子模块与第二电子模块之间的电性连接路径,以缩短该第一电子组件与第二电子组件之间的电性信号的传输距离,故相比于现有技术,本发明的电子封装件通过快速、低损耗的垂直电路导通路径,以提升电性表现,因而能符合终端产品的效能需求。

13、再者,该封装层可依据该堆叠组件的翘曲程度进行材料选用,使该封装层的翘曲型态能配合该堆叠组件而相互消弭,以提高后续将该电子封装件接置于电子装置上的良率。

技术特征:

1.一种电子封装件,包括:

2.如权利要求1所述的电子封装件,其中,该第一电子模块的构造与该第二电子模块的构造为相同。

3.如权利要求1所述的电子封装件,其中,该封装层、该第一包覆层与该第二包覆层的至少两者的材料为相同。

4.如权利要求1所述的电子封装件,其中,该封装层、该第一包覆层与该第二包覆层的至少两者的材料为相异。

5.如权利要求1所述的电子封装件,其中,该至少一第一线路结构为多个第一线路结构,以分别设于该第一包覆层的相对两侧上,且该至少一第二线路结构为多个第二线路结构,以分别设于该第二包覆层的相对两侧上。

6.如权利要求5所述的电子封装件,其中,该多个第一线路结构的其中一者具有多个第一电性接触垫,而另一者具有多个第一导电凸块,且该多个第二线路结构的其中一者具有多个第二导电凸块,而另一者具有多个第二电性接触垫,以令该第二电子模块以该多个第二导电凸块通过焊锡材料接置于该第一电子模块的该多个第一电性接触垫上。

7.如权利要求6所述的电子封装件,其中,该堆叠组件还包含包覆该多个第二导电凸块、焊锡材料与第一电性接触垫的结合材。

8.如权利要求6所述的电子封装件,其中,该堆叠组件还包含包覆该多个第二导电凸块、焊锡材料、第一电性接触垫与该第二电子模块的封装材。

9.如权利要求6所述的电子封装件,其中,该堆叠组件还包含包覆该多个第二导电凸块、焊锡材料与第一电性接触垫的结合材及包覆该结合材与该第二电子模块的封装材。

10.如权利要求1所述的电子封装件,其中,该第一线路结构或第二线路结构具有多个电性连接该布线结构的导电凸块。

11.如权利要求1所述的电子封装件,其中,该第一线路结构或第二线路结构具有多个电性连接该布线结构的电性接触垫。

12.一种电子封装件的制法,包括:

13.如权利要求12所述的电子封装件的制法,其中,该第一电子模块的构造与该第二电子模块的构造为相同。

14.如权利要求12所述的电子封装件的制法,其中,该封装层、该第一包覆层与该第二包覆层的至少两者的材料为相同。

15.如权利要求12所述的电子封装件的制法,其中,该封装层、该第一包覆层与该第二包覆层的至少两者的材料为相异。

16.如权利要求12所述的电子封装件的制法,其中,该至少一第一线路结构为多个第一线路结构,以分别设于该第一包覆层的相对两侧上,且该至少一第二线路结构为多个第二线路结构,以分别设于该第二包覆层的相对两侧上。

17.如权利要求16所述的电子封装件的制法,其中,该多个第一线路结构的其中一者具有多个第一电性接触垫,而另一者具有多个第一导电凸块,且该多个第二线路结构的其中一者具有多个第二导电凸块,而另一者具有多个第二电性接触垫,以令该第二电子模块以该多个第二导电凸块通过焊锡材料接置于该第一电子模块的该多个第一电性接触垫上。

18.如权利要求17所述的电子封装件的制法,其中,该制法还包括以结合材包覆该多个第二导电凸块、焊锡材料与第一电性接触垫。

19.如权利要求17所述的电子封装件的制法,其中,该制法还包括以封装材包覆该多个第二导电凸块、焊锡材料、第一电性接触垫与该第二电子模块。

20.如权利要求17所述的电子封装件的制法,其中,该制法还包括先以结合材包覆该多个第二导电凸块、焊锡材料与第一电性接触垫,再以封装材包覆该结合材与该第二电子模块。

21.如权利要求12所述的电子封装件的制法,其中,该第一线路结构或第二线路结构具有多个电性连接该布线结构的导电凸块。

22.如权利要求12所述的电子封装件的制法,其中,该第一线路结构或第二线路结构具有多个电性连接该布线结构的电性接触垫。

23.如权利要求12所述的电子封装件的制法,其中,该制法还包括于该承载板上形成另一布线结构,以令该堆叠组件接置于该另一布线结构上。

24.如权利要求12所述的电子封装件的制法,其中,该承载板与该多个导电柱构成为一体成形的金属件。

技术总结

一种电子封装件及其制法,包括于封装层中嵌埋堆叠组件与多个导电柱,且于该封装层上形成布线结构,通过将第一电子模块与第二电子模块相互堆叠而形成该堆叠组件,并以第一导电通孔与第二导电通孔作为该第一电子模块与第二电子模块之间的电性连接路径,以缩短该第一电子模块与第二电子模块中的第一电子组件与第二电子组件之间的电性信号的传输距离。

技术研发人员:林欣柔,王隆源,高灃,陈秋铃,王泓凯

受保护的技术使用者:矽品精密工业股份有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!