半导体结构及其形成方法与流程

本公开涉及集成电路领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、动态随机存储器(dynamic random access memory,dram)是计算机等电子设备中常用的半导体装置,其由多个存储单元构成,每个存储单元通常包括晶体管和电容器。所述晶体管的栅电极与字线电连接、源电极与位线电连接、漏电极与电容器电连接,字线上的字线电压能够控制晶体管的开启和关闭,从而通过位线能够读取存储在电容器中的数据信息,或者将数据信息写入到电容器中。

2、随着dram尺寸的微缩,为了改善晶体管的漏电和提升器件的可靠性,hkmg(high-kmetal gate)技术被引入到dram的制程中。hkmg技术包括先栅(first gate)技术与后栅(last gate)技术。对于先栅(first gate)技术而言,在厚氧器件中,因为较厚的栅介电材料的存在会影响高k介质层的偶极子的扩散,导致功函数金属不能起到很好的阈值电压调节作用,造成厚氧器件栅极的阈值电压过高,引起厚氧器件性能的退化。

技术实现思路

1、本公开所要解决的技术问题是,提供一种半导体结构及其形成方法,其能够提高半导体器件的稳定性。

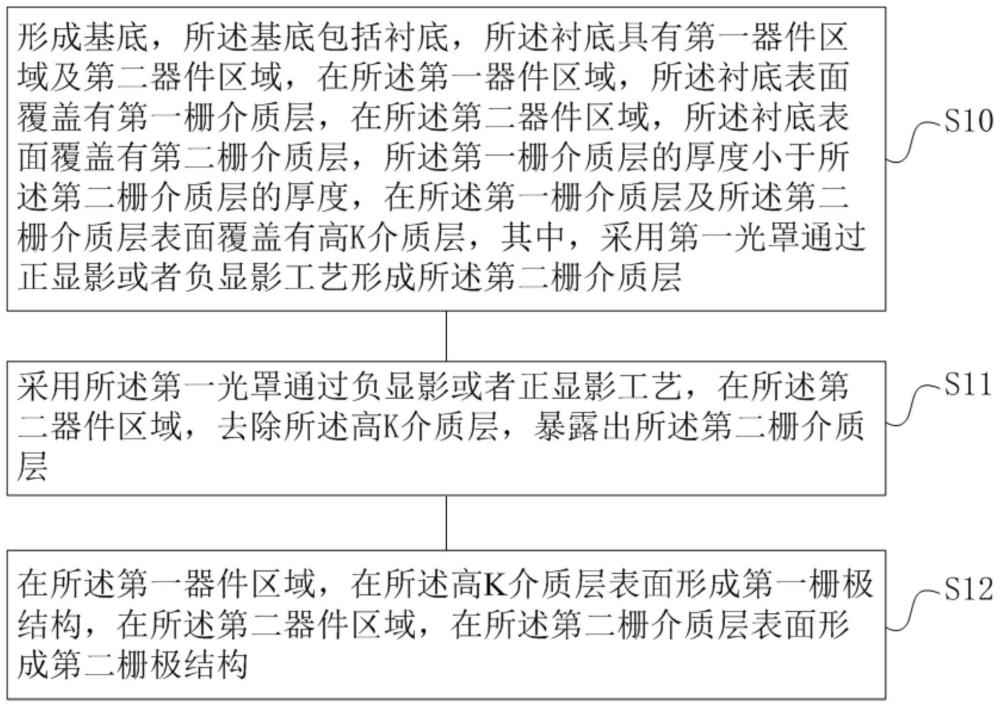

2、为了解决上述问题,本公开实施例提供了一种半导体结构的形成方法,包括:形成基底,所述基底包括衬底,所述衬底具有第一器件区域及第二器件区域,在所述第一器件区域,所述衬底表面覆盖有第一栅介质层,在所述第二器件区域,所述衬底表面覆盖有第二栅介质层,所述第一栅介质层的厚度小于所述第二栅介质层的厚度,在所述第一栅介质层及所述第二栅介质层表面覆盖有高k介质层,其中,采用第一光罩通过正显影或者负显影工艺形成所述第二栅介质层;采用所述第一光罩通过负显影或者正显影工艺,在所述第二器件区域,去除所述高k介质层,暴露出所述第二栅介质层;在所述第一器件区域,在所述高k介质层表面形成第一栅极结构,在所述第二器件区域,在所述第二栅介质层表面形成第二栅极结构。

3、在一实施例中,形成基底的步骤包括:提供所述衬底;在所述第二器件区域,在所述衬底表面形成第二栅介质层;在所述第一器件区域,在所述衬底表面形成第一栅介质层;形成高k介质层,所述高k介质层覆盖所述第一栅介质层及所述第二栅介质层。

4、在一实施例中,在所述第二器件区域,在所述衬底表面形成第二栅介质层的步骤包括:在所述衬底上形成第二栅介质材料层;采用所述第一光罩通过正显影或者负显影工艺,在所述第二器件区域,在所述第二栅介质材料层上形成第一掩膜层;以所述第一掩膜层作为遮挡,在所述第一器件区域,去除所述第二栅介质材料层,在所述第二器件区域,所述第二栅介质材料层作为所述第二栅介质层;去除所述第一掩膜层。

5、在一实施例中,在所述第一器件区域,在所述衬底表面形成第一栅介质层的步骤包括:形成第一栅介质材料层,在所述第一器件区域,所述第一栅介质材料层覆盖所述衬底表面,所述第一栅介质材料层作为所述第一栅介质层。

6、在一实施例中,在所述第二器件区域,所述第一栅介质材料层还覆盖所述第二栅介质材料层的表面,所述第一栅介质材料层与所述第二栅介质材料层共同作为所述第二栅介质层。

7、在一实施例中,在所述第二器件区域,去除所述高k介质层,暴露出所述第二栅介质层的步骤包括:采用所述第一光罩通过负显影或者正显影工艺,在所述第一器件区域,在所述高k介质层表面形成第二掩膜层;以所述第二掩膜层作为遮挡,在所述第二器件区域,去除所述高k介质层,暴露出所述第二栅介质层;去除所述第二掩膜层。

8、在一实施例中,在去除所述高k介质层的步骤之前还包括:在所述高k介质层表面形成保护层;在去除所述高k介质层的步骤中,在所述第一器件区域,所述保护层用于保护所述高k介质层;在形成所述第一栅极结构的步骤之前,去除所述保护层。

9、在一实施例中,所述第一器件区域包括第一n阱区及第一p阱区,所述第二器件区域包括第二n阱区及第二p阱区,形成所述基底的步骤还包括:在所述第一n阱区,在所述衬底表面形成硅锗层,所述第一栅介质层覆盖所述硅锗层。

10、在一实施例中,所述第一栅极结构包括第一nmos晶体管栅极结构及第一pmos晶体管栅极结构,所述第二栅极结构包括第二nmos晶体管栅极结构及第二pmos晶体管栅极结构,形成所述第一栅极结构及所述第二栅极结构的步骤包括:在所述第一p阱区形成第一nmos晶体管栅极结构,在所述第一n阱区形成第一pmos晶体管栅极结构,在所述第二p阱区形成第二nmos晶体管栅极结构,在所述第二n阱区形成第二pmos晶体管栅极结构。

11、在一实施例中,形成所述第一栅极结构及所述第二栅极结构的步骤包括:在所述第一p阱区及所述第二p阱区形成nmos晶体管金属栅极层;在所述第一n阱区及所述第二n阱区形成pmos晶体管金属栅极层;形成栅极复合材料层,所述栅极复合材料层覆盖所述nmos晶体管金属栅极层及pmos晶体管金属栅极层;图案化所述栅极复合材料层、所述nmos晶体管金属栅极层及pmos晶体管金属栅极层,形成所述第一nmos晶体管栅极结构、所述第一pmos晶体管栅极结构、所述第二nmos晶体管栅极结构及所述第二pmos晶体管栅极结构。

12、本公开实施例还提供一种半导体结构,其包括:衬底,所述衬底具有第一器件区域及第二器件区域;在所述第一器件区域,第一栅介质层覆盖所述衬底表面;在所述第二器件区域,第二栅介质层覆盖所述衬底表面,且所述第一栅介质层的厚度小于所述第二栅介质层的厚度;高k介质层,覆盖所述第一栅介质层表面;第一栅极结构,位于所述高k介质层表面;第二栅极结构,位于所述第二栅介质层表面。

13、在一实施例中,所述第一器件区域包括第一n阱区及第一p阱区,所述第一栅极结构包括第一nmos晶体管栅极结构及第一pmos晶体管栅极结构,所述第一nmos晶体管栅极结构设置在所述第一p阱区上,所述第一pmos晶体管栅极结构设置在所述第一n阱区上;所述第二器件区域包括第二n阱区及第二p阱区,所述第二栅极结构包括第二nmos晶体管栅极结构及第二pmos晶体管栅极结构,所述第二nmos晶体管栅极结构设置在所述第二p阱区上,所述第二pmos晶体管栅极结构设置在所述第二n阱区上。

14、在一实施例中,在所述第一n阱区,所述半导体结构还包括硅锗层,所述硅锗层设置在所述第一栅介质层与所述衬底之间。

15、在一实施例中,所述第一nmos晶体管栅极结构与所述第二nmos晶体管栅极结构具有相同结构,所述第一pmos晶体管栅极结构与所述第二pmos晶体管栅极结构具有相同结构。

16、在一实施例中,所述第一nmos晶体管栅极结构与所述第二nmos晶体管栅极结构均包括nmos晶体管金属栅极层及覆盖所述nmos晶体管金属栅极层的第一栅极复合层;所述第一pmos晶体管栅极结构与所述第二pmos晶体管栅极结构均包括pmos晶体管金属栅极层及覆盖所述pmos晶体管金属栅极层的第二栅极复合层。

17、本公开实施例提供的半导体结构的形成方法,在形成所述高k介质层后,去除厚度较大的第二栅介质层所在的第二器件区域的高k介质层,仅保留第二栅介质层作为后续形成的第二栅极结构与衬底之间的隔离层,即在第二器件区域不存在高k介质层,而不会存在因为较厚的第二栅介质层的存在而影响高k介质层的偶极子的扩散的问题,使得第二栅极结构能够起到良好的阈值电压调节作用,避免第二器件区域的阈值电压过高,提高了第二器件区域的半导体器件的稳定性。同时,本公开实施例提供的形成方法,不会因所述第二器件区域的高k介质层的去除而影响第一器件区域的高k介质层,在具有较薄的第一栅介质层的所述第一器件区域依然形成有所述高k介质层,也进一步保证了第一器件区域的半导体结构的稳定性。并且,本公开实施例提供的形成方法采用第一光罩通过正显影或者负显影工艺形成所述第二栅介质层,采用所述第一光罩通过负显影或者正显影工艺,在所述第二器件区域,去除所述高k介质层,即采用同一光罩形成所述第二栅介质层及去除所述高k介质层,成本较低、制备工艺简单,无需复杂工艺即可避免第二器件区域的第二栅极结构无法较好地调节阈值电压的缺陷,大大提高了半导体工艺的实用性。

18、本公开实施例提供的半导体结构在第一器件区域(薄氧器件区域)在第一栅极结构与衬底之间设置高k介质层,以降低第一栅极结构泄露电流,并且,在第二器件区域(厚氧器件区域)在第二栅极结构与衬底之间仅采用厚度较大的第二栅介质层作为隔离层,而并无高k介质层,在降低第二栅极结构泄露电流的同时也避免因第二栅介质层厚度太厚而引起高k介质层的偶极子的扩散的问题,使得第二栅极结构能够起到良好的阈值电压调节作用,避免第二器件区域的阈值电压过高,提高了第二器件区域的半导体器件的稳定性。

- 还没有人留言评论。精彩留言会获得点赞!