一种半导体器件及其制作方法与流程

一种半导体器件及其制作方法

1.本技术是针对申请日为2019年09月03日,申请号为201910826314.x,发明名称为一种三维存储器件及其制作方法的专利申请提出的分案申请。

技术领域

2.本发明属于半导体集成电路领域,涉及一种半导体器件及其制作方法。

背景技术:

3.在三维逻辑与非闪存(3d nand)技术中,互补金属氧化物半导体页面缓冲电路(cmos page buffer circuit)中高压金属氧化物半导体(hv mos)上层的金属走线,除了高压金属线(hv metal line)hv和低压金属线(lv metal line),其他都是很长的浮置虚设走线(floating dummy),而这些浮置虚设走线受高压金属线的耦合效应(coupling effect)影响,易造成高压/虚设走线(hv/dummy)两根金属线之间,或者是虚设走线/低压(dummy/lv)两根金属线之间的线对线击穿电压(vbd)降低,从而带来时间依赖性电介质击穿(tddb)的问题。

4.当前的解决方案主要是增大走线之间的间距,但随着3d nand技术层数越来越多,器件后段走线数量大幅度增加,增大间距已不再可能。

5.因此,如何设计一种新的三维存储器件及其制作方法,以改善上述问题,成为本领域技术人员亟待解决的一个重要技术问题。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种三维存储器件及其制作方法,用于解决现有技术中浮置虚设走线因受高压金属线的耦合效应影响导致线对线击穿电压(vbd)降低,从而带来时间依赖性电介质击穿(tddb)的问题。

7.为实现上述目的及其他相关目的,本发明提供一种三维存储器件,包括:

8.第一电压走线,所述第一电压走线沿第一方向延伸;

9.第二电压走线,与所述第一电压走线位于同一直线上,且所述第二电压走线的电压低于所述第一电压走线的电压;

10.多条虚设走线,分布于所述第一电压走线与所述第二电压走线的两侧,其中,任意一条与所述第一电压走线及所述第二电压走线相邻的所述虚设走线仅与所述第一电压走线及所述第二电压走线其中之一在第二方向上有相对部分,或与所述第一电压走线及所述第二电压走线在第二方向上均没有相对部分,所述第二方向与所述第一方向垂直。

11.可选地,多条所述虚设走线包括与所述第一电压走线及所述第二电压走线相邻的第一虚设走线、第二虚设走线、第三虚设走线及第四虚设走线,所述第一虚设走线与所述第二虚设走线位于同一直线上,所述第三虚设走线与所述第四虚设走线位于同一直线上,所述第一虚设走线与所述第三虚设走线分别位于所述第一电压走线的相对两侧并与所述第一电压走线在所述第二方向上有相对部分,所述第二虚设走线与所述第四虚设走线分别位

于所述第二电压走线的相对两侧并与所述第二电压走线在所述第二方向上有相对部分。

12.可选地,所述三维存储器件还包括至少一中心虚设走线,所述中心虚设走线与所述第一电压走线及所述第二电压走线位于同一直线上,并位于所述第一电压走线与所述第二电压走线之间。

13.可选地,所述第一虚设走线、所述第二虚设走线、所述第三虚设走线及所述第四虚设走线均与所述中心虚设走线在所述第二方向上有相对部分。

14.可选地,多条所述虚设走线还包括第五虚设走线,所述第五虚设走线与所述第三虚设走线及所述第四虚设走线位于同一直线上,且所述第五虚设走线位于所述第三虚设走线与所述第四虚设走线之间。

15.可选地,所述第一虚设走线及所述第四虚设走线均与所述中心虚设走线在所述第二方向上没有相对部分,所述第二虚设走线及所述第三虚设走线均与所述中心虚设走线在所述第二方向上有相对部分。

16.可选地,多条所述虚设走线还包括第五虚设走线,所述第五虚设走线与所述第三虚设走线及所述第四虚设走线位于同一直线上,且所述第五虚设走线位于所述第三虚设走线与所述第四虚设走线之间。

17.可选地,所述三维存储器件中设有页面缓冲高压nmos晶体管,所述晶体管的漏极通过第一接触部连接于所述第一电压走线下方,所述晶体管的源极通过第二接触部连接于所述第二电压走线下方。

18.可选地,所述第一电压走线的电压大于或等于20v,所述第二电压走线的电压小于或等于10v。

19.可选地,所述三维存储器件还包括第三电压走线,所述第三电压走线的电压等于所述第二电压走线的电压,所述第三电压走线与所述第二电压走线平行,且所述第三电压走线与所述第二电压走线之间通过至少一所述虚设走线间隔。

20.可选地,所述第三电压走线与所述第二电压走线通过至少一所述虚设走线及至少两个连接部连接,且至少一所述连接部的两侧分别与所述第二电压走线及一所述虚设走线连接,至少一所述连接部的两侧分别与一所述虚设走线及所述第三电压走线连接。

21.本发明还提供一种三维存储器件的制作方法,包括以下步骤:

22.提供一衬底;

23.形成走线层于所述衬底上方,所述走线层包括第一电压走线、第二电压走线及多条虚设走线,其中,所述第二电压走线与所述第一电压走线位于同一直线上,且所述第二电压走线的电压低于所述第一电压走线的电压,多条所述虚设走线分布于所述第一电压走线与所述第二电压走线的两侧,且任意一条与所述第一电压走线及所述第二电压走线相邻的所述虚设走线仅与所述第一电压走线及所述第二电压走线其中之一在第二方向上有相对部分,或与所述第一电压走线及所述第二电压走线在第二方向上均没有相对部分,所述第二方向与所述第一方向垂直。

24.可选地,通过形成导电层于所述衬底上方,并将所述导电层图形化,得到所述走线层。

25.可选地,通过形成具有开口图形的掩膜层于所述衬底上方,并形成导电材料于所述开口图形中,得到所述走线层。

26.可选地,多条所述虚设走线包括与所述第一电压走线及所述第二电压走线相邻的第一虚设走线、第二虚设走线、第三虚设走线及第四虚设走线,所述第一虚设走线与所述第二虚设走线位于同一直线上,所述第三虚设走线与所述第四虚设走线位于同一直线上,所述第一虚设走线与所述第三虚设走线分别位于所述第一电压走线的相对两侧并与所述第一电压走线在所述第二方向上有相对部分,所述第二虚设走线与所述第四虚设走线分别位于所述第二电压走线的相对两侧并与所述第二电压走线在所述第二方向上有相对部分。

27.可选地,所述三维存储器件还包括至少一中心虚设走线,所述中心虚设走线与所述第一电压走线及所述第二电压走线位于同一直线上,并位于所述第一电压走线与所述第二电压走线之间。

28.可选地,所述第一虚设走线、所述第二虚设走线、所述第三虚设走线及所述第四虚设走线均与所述中心虚设走线在所述第二方向上有相对部分。

29.可选地,多条所述虚设走线还包括第五虚设走线,所述第五虚设走线与所述第三虚设走线及所述第四虚设走线位于同一直线上,且所述第五虚设走线位于所述第三虚设走线与所述第四虚设走线之间。

30.可选地,所述第一虚设走线及所述第四虚设走线均与所述中心虚设走线在所述第二方向上没有相对部分,所述第二虚设走线及所述第三虚设走线均与所述中心虚设走线在所述第二方向上有相对部分。

31.可选地,多条所述虚设走线还包括第五虚设走线,所述第五虚设走线与所述第三虚设走线及所述第四虚设走线位于同一直线上,且所述第五虚设走线位于所述第三虚设走线与所述第四虚设走线之间。

32.可选地,所述衬底中设有页面缓冲高压nmos晶体管,所述第一电压走线通过第一接触部连接于所述晶体管的漏极上方,所述第二电压走线通过第二接触部连接于所述晶体管的源极上方。

33.如上所述,本发明的三维存储器件及其制作方法通过改进走线的布局,使得紧邻高压走线或低压走线的虚设走线不同时面对高压走线与低压走线,从而可以在不增加走线之间间距的情况下有效提高高压走线与虚设走线之间、或者虚设走线与低压走线之间的线对线击穿电压(vbd),不仅可以有效控制芯片面积,且不会影响原本的高压走线与低压走线。

附图说明

34.图1显示为一种示例三维存储器件的走线平面布局图。

35.图2显示为图1所示三维存储器件的仿真结果示意图。

36.图3显示为本发明的三维存储器件于实施例一中的走线平面布局图。

37.图4显示为本发明的三维存储器件于实施例二中的走线平面布局图。

38.图5显示为本发明的三维存储器件于实施例三中的走线平面布局图。

39.图6显示为图5所示三维存储器件的仿真结果示意图。

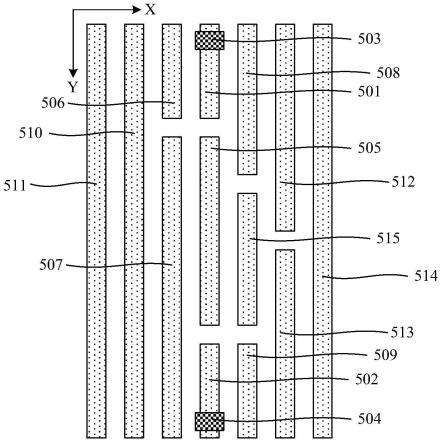

40.图7显示为本发明的三维存储器件于实施例四中的走线平面布局图。

41.元件标号说明

42.101

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电压走线

43.102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电压走线

44.103

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一接触部

45.104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二接触部

46.105、106、107、108、109、110、111

ꢀꢀꢀꢀꢀꢀꢀ

虚设走线

47.112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三电压走线

48.113、114、115

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

连接部

49.w

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

走线宽度

50.d

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

走线间距

51.201

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电压走线

52.202

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电压走线

53.203

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一接触部

54.204

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二接触部

55.205

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一虚设走线

56.206

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二虚设走线

57.207

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三虚设走线

58.208

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四虚设走线

59.209、210、211、212

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

虚设走线

60.213

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三电压走线

61.301

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电压走线

62.302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电压走线

63.303

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一接触部

64.304

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二接触部

65.305

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

中间虚设走线

66.306

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一虚设走线

67.307

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二虚设走线

68.308

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三虚设走线

69.309

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四虚设走线

70.310、311、312、313

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

虚设走线

71.314

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三电压走线

72.401

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电压走线

73.402

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电压走线

74.403

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一接触部

75.404

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二接触部

76.405

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

中间虚设走线

77.406

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一虚设走线

78.407

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二虚设走线

79.408

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三虚设走线

80.409

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四虚设走线

81.410、411、412、413

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

虚设走线

82.414

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三电压走线

83.415

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第五虚设走线

84.416、417、418

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

连接部

85.501

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电压走线

86.502

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电压走线

87.503

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一接触部

88.504

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二接触部

89.505

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

中间虚设走线

90.506

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一虚设走线

91.507

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二虚设走线

92.508

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三虚设走线

93.509

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四虚设走线

94.510、511、512、513

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

虚设走线

95.514

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三电压走线

96.515

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第五虚设走线

97.x

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二方向

98.y

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一方向

具体实施方式

99.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

100.请参阅图1至图7。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局。

101.如图1所示,显示为一种示例三维存储器件的走线平面布局图,该三维存储器件包括位于同一直线上的第一电压走线101与第二电压线走线102,其中,所述第一电压走线101作为高压走线,所述第二电压走线102作为低压走线,所述第一电压走线101与所述第二电压走线102分别通过其下方的第一接触部103与第二接触部104为其下方的半导体元件提供高压和低压。

102.作为示例,图1中示出了走线宽度w及走线间距d。

103.作为示例,所述三维存储器件还包括分布于所述第一电压走线101与所述第二电压线走线102相对两侧的多条虚设走线,其中,虚设走线105与所述第一电压走线101及所述第二电压线走线102的左侧相邻且同时面对所述第一电压走线101及所述第二电压线走线102,虚设走线106及所述虚设走线107与所述第一电压走线101及所述第二电压线走线102的右侧相邻,且所述虚设走线107同时面对所述第一电压走线101及所述第二电压线走线102,虚设走线108、虚设走线109、虚设走线111及虚设走线111均与所述第一电压走线101或

所述第二电压线走线102之间间隔有其它走线。

104.作为示例,所述三维存储器件还包括分布于所述第一电压走线101与所述第二电压线走线102右侧的第三电压走线112,所述第三电压走线112也作为低压走线,且所述第三电压走线11与所述第一电压走线101或所述第二电压线走线102之间间隔有其它走线。

105.如图2所示,显示为图1所示三维存储器件的仿真结果示意图。其中,所述第一电压走线101上施加高压hv=22v,所述第二电压走线102上施加低压lv=0v,所述第二电压走线102与所述第三电压走线112之间通过连接部113、所述虚设走线107、连接部114、所述虚设走线111及连接部115连接,仿真结果显示,由于耦合效应,所述虚设走线105的电压为6.5v,所述虚设走线106的电压为11.27v,所述虚设走线110的电压为4.7v。

106.由于金属tddb击穿位置(电场最强处)在电压压差最大的两根走线之间,在图2的仿真结果中,两根走线之间最大压差δv=(22-6.5)v=15.5v,因此器件容易在所述第一电压走线101与所述虚设走线105之间发生击穿。所述虚设走线105的特点是紧邻所述第一电压走线101,且长度较长,同时与所述第一电压走线101与所述第二电压线走线102相对。

107.本发明通过对上述器件仿真以及对仿真结果分析,认为受耦合效应影响最大的是紧邻高压走线及低压走线两侧的虚设走线,因此,本发明采用切断法来清除掉同时面对高压走线与低压走线的紧邻虚设走线。下面通过更为具体的实施例来说明本发明的技术方案。

108.实施例一

109.本实施例中提供一种三维存储器件,请参阅图3,显示为该三维存储器件的走线平面布局图,该三维存储器件包括第一电压走线201、第二电压走线202及多条虚设走线,其中,所述第一电压走线201沿第一方向y延伸,所述第二电压走线202与所述第一电压走线201位于同一直线上,多条所述虚设走线分布于所述第一电压走线201与所述第二电压走线202的两侧。

110.具体的,所述第二电压走线的电压低于所述第一电压走线的电压,所述第一电压走线201作为高压走线,所述第二电压走线202作为低压走线。

111.作为示例,所述三维存储器件中设有页面缓冲高压nmos晶体管,所述晶体管的漏极通过第一接触部203连接于所述第一电压走线201下方,所述晶体管的源极通过第二接触部204连接于所述第二电压走线202下方。

112.作为示例,所述第一电压走线的电压大于或等于20v,所述第二电压走线的电压小于或等于10v。

113.具体的,任意一条与所述第一电压走线201及所述第二电压走线202相邻的所述虚设走线仅与所述第一电压走线及所述第二电压走线其中之一在第二方向x上有相对部分,或与所述第一电压走线及所述第二电压走线在第二方向上均没有相对部分,所述第二方向x与所述第一方向y垂直。

114.本实施例中,多条所述虚设走线包括与所述第一电压走线及所述第二电压走线相邻的第一虚设走线205、第二虚设走线206、第三虚设走线207及第四虚设走线208,其中,所述第一虚设走线205与所述第二虚设走线206位于同一直线上,所述第三虚设走线207与所述第四虚设走线208位于同一直线上,所述第一虚设走线205与所述第三虚设走线207分别位于所述第一电压走线201的相对两侧并与所述第一电压走线201在所述第二方向x上有相

对部分,所述第二虚设走线206与所述第四虚设走线208分别位于所述第二电压走线202的相对两侧并与所述第二电压走线202在所述第二方向x上有相对部分。

115.作为示例,多条所述虚设走线还包括与所述第一电压走线201或所述第二电压走线202非直接相邻的虚设走线209、虚设走线210、虚设走线211、虚设走线212。

116.作为示例,所述三维存储器件还包括第三电压走线213,所述第三电压走线213作为低压走线,所述第三电压走线的电压等于所述第二电压走线的电压。所述第三电压走线213与所述第二电压走线202平行,且所述第三电压走线213与所述第二电压走线202之间通过至少一所述虚设走线间隔。

117.当然,与位于同一直线上的高压走线与低压走线非紧邻的虚设走线也可以采用其它布局,与高压走线不位于同一直线上的低压走线也可以采用其它布局,此处不应过分限制本发明的保护范围。

118.本实施例的三维存储器件中,紧邻高压走线或低压走线的虚设走线均不同时面对高压走线与低压走线,从而可以在不增加走线之间间距的情况下有效提高高压走线与虚设走线之间、或者虚设走线与低压走线之间的线对线击穿电压(vbd),有利于有效控制芯片面积,且新的走线布局仅相当于在某些走线中设置小小的切断点,不会影响原本的高压走线与低压走线。

119.实施例二

120.本实施例与实施例一采用基本相同的技术方案,不同之处在于,实施例一中位于同一直线上的高压走线与低压走线之间无虚设走线间隔,而本实施例中,位于同一直线上的高压走线与低压走线之间设有虚设走线,换句话说,相当于在原来的低压走线中设置了切断点。

121.请参阅图4,显示为本实施例中三维存储器件的走线平面布局图,该三维存储器件包括第一电压走线301、第二电压走线302、至少一中心虚设走线305及多条虚设走线,其中,所述第一电压走线201沿第一方向y延伸,所述第一电压走线301、所述第二电压走线302及所述中心虚设走线305位于同一直线上,且所述中心虚设走线305位于所述第一电压走线301与所述第二电压走线302之间,多条所述虚设走线分布于所述第一电压走线301与所述第二电压走线302的两侧。

122.具体的,所述第二电压走线的电压低于所述第一电压走线的电压,所述第一电压走线301作为高压走线,所述第二电压走线302作为低压走线。

123.作为示例,所述三维存储器件中设有页面缓冲高压nmos晶体管,所述晶体管的漏极通过第一接触部303连接于所述第一电压走线301下方,所述晶体管的源极通过第二接触部304连接于所述第二电压走线302下方。

124.作为示例,所述第一电压走线的电压大于或等于20v,所述第二电压走线的电压小于或等于10v。

125.具体的,任意一条与所述第一电压走线及所述第二电压走线相邻的所述虚设走线仅与所述第一电压走线及所述第二电压走线其中之一在第二方向x上有相对部分,或与所述第一电压走线及所述第二电压走线在第二方向x上均没有相对部分,所述第二方向x与所述第一方向y垂直。

126.本实施例中,多条所述虚设走线包括第一虚设走线306、第二虚设走线307、第三虚

设走线308及第四虚设走线309,其中,所述第一虚设走线306与所述第二虚设走线307位于同一直线上,所述第三虚设走线308与所述第四虚设走线309位于同一直线上,所述第一虚设走线306与所述第三虚设走线308分别位于所述第一电压走线301的相对两侧,所述第二虚设走线307与所述第四虚设走线309分别位于所述第二电压走线302的相对两侧。

127.进一步的,所述第一虚设走线306、所述第二虚设走线307、所述第三虚设走线308及所述第四虚设走线309均与所述中心虚设走线305在所述第二方向x上有相对部分。

128.作为示例,多条所述虚设走线还包括与所述第一电压走线301或所述第二电压走线302非直接相邻的虚设走线310、虚设走线311、虚设走线312、虚设走线313。

129.作为示例,所述三维存储器件还包括第三电压走线314,所述第三电压走线314作为低压走线,所述第三电压走线的电压等于所述第二电压走线的电压。所述第三电压走线314与所述第二电压走线302平行,且所述第三电压走线314与所述第二电压走线302之间通过至少一所述虚设走线间隔。

130.当然,与位于同一直线上的高压走线与低压走线非紧邻的虚设走线也可以采用其它布局,与高压走线不位于同一直线上的低压走线也可以采用其它布局,此处不应过分限制本发明的保护范围。

131.本实施例的三维存储器件的走线平面布局相对于图1所示的走线平面布局,相当于切断了虚设走线105及第二电压走线102,其中,切断虚设走线105可以破坏原有虚设走线105同面对高压走线与低压走线的关系,切断第二电压走线102相当于将原有的低压走线的一部分变为虚设走线,可以破坏原有虚设走线106同时面对高压走线与低压走线的关系,从而可以在不增加走线之间间距的情况下有效提高高压走线与虚设走线之间、或者虚设走线与低压走线之间的线对线击穿电压(vbd),有利于有效控制芯片面积,且新的走线布局仅相当于在某些走线中设置小小的切断点,不会影响原本的高压走线与低压走线。

132.实施例三

133.本实施例与实施例二采用基本相同的技术方案,不同之处在于,实施例二中与低压走线直接相邻的第四虚设走线较长,而本实施例中,多条所述虚设走线还包括第五虚设走线,所述第五虚设走线与所述第三虚设走线及所述第四虚设走线位于同一直线上,且所述第五虚设走线位于所述第三虚设走线与所述第四虚设走线之间,相当于在原有的第四虚设走线中设置断点,将较长的第四虚设走线分隔为两段虚设走线。

134.请参阅图5,显示为本实施例中三维存储器件的走线平面布局图,该三维存储器件包括第一电压走线401、第二电压走线402、至少一中心虚设走线405及多条虚设走线,其中,所述第一电压走线201沿第一方向y延伸,所述第一电压走线401、所述第二电压走线402及所述中心虚设走线405位于同一直线上,且所述中心虚设走线405位于所述第一电压走线401与所述第二电压走线402之间,多条所述虚设走线分布于所述第一电压走线401与所述第二电压走线402的两侧。

135.具体的,所述第二电压走线的电压低于所述第一电压走线的电压,所述第一电压走线401作为高压走线,所述第二电压走线402作为低压走线。

136.作为示例,所述三维存储器件中设有页面缓冲高压nmos晶体管,所述晶体管的漏极通过第一接触部403连接于所述第一电压走线401下方,所述晶体管的源极通过第二接触部404连接于所述第二电压走线402下方。

137.作为示例,所述第一电压走线的电压大于或等于20v,所述第二电压走线的电压小于或等于10v。

138.具体的,任意一条与所述第一电压走线及所述第二电压走线相邻的所述虚设走线仅与所述第一电压走线及所述第二电压走线其中之一在第二方向x上有相对部分,或与所述第一电压走线及所述第二电压走线在第二方向x上均没有相对部分,所述第二方向x与所述第一方向y垂直。

139.本实施例中,多条所述虚设走线包括第一虚设走线406、第二虚设走线407、第三虚设走线408、第四虚设走线409及第五虚设走线415,其中,所述第一虚设走线406与所述第二虚设走线407位于同一直线上,所述第三虚设走线408、所述第四虚设走线409及所述第五虚设走线415位于同一直线上,且所述第五虚设走线415位于所述第三虚设走线408与所述第四虚设走线409之间。所述第一虚设走线406与所述第三虚设走线408分别位于所述第一电压走线401的相对两侧,所述第二虚设走线407与所述第四虚设走线409分别位于所述第二电压走线402的相对两侧。

140.进一步的,所述第一虚设走线406与所述第三虚设走线408均与所述第一电压走线401及所述中心虚设走线405在所述第二方向x上有相对部分,所述第二虚设走线407与所述第四虚设走线409均与所述第二电压走线402及所述中心虚设走线405在所述第二方向x上有相对部分。所述虚设走线515与所述第一电压走线及所述第二电压走线在第二方向x上均没有相对部分。

141.作为示例,多条所述虚设走线还包括与所述第一电压走线401或所述第二电压走线402非直接相邻的虚设走线410、虚设走线411、虚设走线412、虚设走线413。

142.作为示例,所述三维存储器件还包括第三电压走线414,所述第三电压走线414作为低压走线,所述第三电压走线的电压等于所述第二电压走线的电压。所述第三电压走线414与所述第二电压走线402平行,且所述第三电压走线414与所述第二电压走线402之间通过至少一所述虚设走线间隔。

143.当然,与位于同一直线上的高压走线与低压走线非紧邻的虚设走线也可以采用其它布局,与高压走线不位于同一直线上的低压走线也可以采用其它布局,此处不应过分限制本发明的保护范围。

144.请参阅图6,显示为图5所示三维存储器件的仿真结果示意图。其中,所述第一电压走线401上施加高压hv=22v,所述第二电压走线402上施加低压lv=0v,所述第二电压走线402与所述第三电压走线414之间通过连接部416、所述虚设走线107、连接部114、所述虚设走线111及连接部115连接,仿真结果显示,由于耦合效应,所述第一虚设走线406的电压为13.14v,所述第二虚设走线407的电压为5.8v,所述中心虚设走线405的电压为7.8v,所述第三虚设走线408的电压为13.08v,所述虚设走线412的电压为5.9。可见,最大压差产生于所述第一电压走线401与所述第三虚设走线408之间,最大压差δv=(22-13.08)v=8.92v。相对于图1所示的走线布局的最大压差15.5v,本实施例的走线布局大大降低了走线之间的电压差,从而有效抑制tddb效应。

145.本实施例的三维存储器件的走线平面布局相对于图1所示的走线平面布局,相当于切断了虚设走线105、第二电压走线102及虚设走线107,其中,切断虚设走线105可以破坏原有虚设走线105同面对高压走线与低压走线的关系,切断第二电压走线102相当于将原有

的低压走线的一部分变为虚设走线,可以破坏原有虚设走线106同时面对高压走线与低压走线的关系,切断虚设走线107可以减少虚设走线107的长度,进一步优化耦合电压的分配,从而可以在不增加走线之间间距的情况下有效提高高压走线与虚设走线之间、或者虚设走线与低压走线之间的线对线击穿电压(vbd),有利于有效控制芯片面积,且新的走线布局仅相当于在某些走线中设置小小的切断点,不会影响原本的高压走线与低压走线。

146.实施例四

147.本实施例与实施例三采用基本相同的技术方案,不同之处在于,实施例三中所述第一虚设走线同时与所述第一电压走线及所述中心虚设走线在所述第二方向x上有相对部分,所述第四虚设走线同时与所述第二电压走线及所述中心虚设走线在所述第二方向x上有相对部分,而本实施例中,所述第一虚设走线与所述第一电压走线在所述第二方向x上有相对部分但与所述中心虚设走线在所述第二方向x上没有相对部分,所述第四虚设走线与所述第二电压走线在所述第二方向x上有相对部分但与所述中心虚设走线在所述第二方向x上没有相对部分。

148.请参阅图7,显示为本实施例中三维存储器件的走线平面布局图,该三维存储器件包括第一电压走线501、第二电压走线502、至少一中心虚设走线505及多条虚设走线,其中,所述第一电压走线201沿第一方向y延伸,所述第一电压走线501、所述第二电压走线502及所述中心虚设走线505位于同一直线上,且所述中心虚设走线505位于所述第一电压走线501与所述第二电压走线502之间,多条所述虚设走线分布于所述第一电压走线501与所述第二电压走线502的两侧。

149.具体的,所述第二电压走线的电压低于所述第一电压走线的电压,所述第一电压走线501作为高压走线,所述第二电压走线502作为低压走线。

150.作为示例,所述三维存储器件中设有页面缓冲高压nmos晶体管,所述晶体管的漏极通过第一接触部503连接于所述第一电压走线501下方,所述晶体管的源极通过第二接触部504连接于所述第二电压走线502下方。

151.作为示例,所述第一电压走线的电压大于或等于20v,所述第二电压走线的电压小于或等于10v。

152.具体的,任意一条与所述第一电压走线及所述第二电压走线相邻的所述虚设走线仅与所述第一电压走线及所述第二电压走线其中之一在第二方向x上有相对部分,或与所述第一电压走线及所述第二电压走线在第二方向x上均没有相对部分,所述第二方向x与所述第一方向y垂直。

153.本实施例中,多条所述虚设走线包括第一虚设走线506、第二虚设走线507、第三虚设走线508、第四虚设走线509及第五虚设走线515,其中,所述第一虚设走线506与所述第二虚设走线507位于同一直线上,所述第三虚设走线508、所述第四虚设走线509及所述第五虚设走线515位于同一直线上,且所述第五虚设走线515位于所述第三虚设走线508与所述第四虚设走线509之间,所述第一虚设走线506与所述第三虚设走线508分别位于所述第一电压走线501的相对两侧,所述第二虚设走线507与所述第四虚设走线509分别位于所述第二电压走线502的相对两侧。

154.进一步的,所述第一虚设走线506与所述第一电压走线501在所述第二方向x上有相对部分但与所述中心虚设走线505及所述第二电压走线502在所述第二方向x上没有相对

部分邻,所述第二虚设走线507与所述中心虚设走线505及所述第二电压走线502在所述第二方向x上均有相对部分,所述第三虚设走线508与所述第一电压走线501及所述中心虚设走线505在所述第二方向x上均有相对部分但与所述第二电压走线502在所述第二方向x上没有相对部分,所述第四虚设走线509与所述第二电压走线502在所述第二方向x上有相对部分但与所述中心虚设走线505在所述第二方向x上没有相对部分。所述虚设走线515与所述第一电压走线及所述第二电压走线在第二方向x上均没有相对部分。

155.作为示例,多条所述虚设走线还包括与所述第一电压走线501或所述第二电压走线502非直接相邻的虚设走线510、虚设走线511、虚设走线512、虚设走线513。

156.作为示例,所述三维存储器件还包括第三电压走线514,所述第三电压走线514作为低压走线,所述第三电压走线的电压等于所述第二电压走线的电压。所述第三电压走线514与所述第二电压走线502平行,且所述第三电压走线514与所述第二电压走线502之间通过至少一所述虚设走线间隔。

157.当然,与位于同一直线上的高压走线与低压走线非紧邻的虚设走线也可以采用其它布局,与高压走线不位于同一直线上的低压走线也可以采用其它布局,此处不应过分限制本发明的保护范围。

158.本实施例的三维存储器件的走线平面布局相对于实施例三的三维存储器件的走线平面布局优化了断点的位置,进一步切断了第一虚设走线与中心虚设走线之间的耦合路径,并进一步切断了中心虚设走线与第四虚设走线之间的耦合路径,可以在不增加走线之间间距的情况下更有效提高高压走线与虚设走线之间、或者虚设走线与低压走线之间的线对线击穿电压(vbd),有利于有效控制芯片面积,且新的走线布局仅相当于在某些走线中设置小小的切断点,不会影响原本的高压走线与低压走线。

159.实施例五

160.本实施例中提供一种三维存储器件的制作方法,用于制作实施例一至实施例四中任意一项所述的三维存储器件,包括以下步骤:

161.s1:提供一衬底;

162.s2:形成走线层于所述衬底上方,所述走线层包括第一电压走线、第二电压走线及多条虚设走线,其中,所述第二电压走线与所述第一电压走线位于同一直线上,且所述第二电压走线的电压低于所述第一电压走线的电压,多条所述虚设走线分布于所述第一电压走线与所述第二电压走线的两侧,且所有与所述第一电压走线直接相邻的所述虚设走线均不与所述第二电压走线直接相邻,所有与所述第二电压走线直接相邻的所述虚设走线均不与所述第一电压走线直接相邻。

163.作为示例,可以通过形成导电层于所述衬底上方,并将所述导电层图形化,得到所述走线层。

164.作为示例,也可以通过形成具有开口图形的掩膜层于所述衬底上方,并形成导电材料于所述开口图形中,得到所述走线层。

165.作为示例,多条所述虚设走线包括与所述第一电压走线及所述第二电压走线相邻的第一虚设走线、第二虚设走线、第三虚设走线及第四虚设走线,所述第一虚设走线与所述第二虚设走线位于同一直线上,所述第三虚设走线与所述第四虚设走线位于同一直线上,所述第一虚设走线与所述第三虚设走线分别位于所述第一电压走线的相对两侧并与所述

第一电压走线在所述第二方向x上有相对部分,所述第二虚设走线与所述第四虚设走线分别位于所述第二电压走线的相对两侧并与所述第二电压走线在所述第二方向x上有相对部分。

166.作为示例,所述三维存储器件还包括至少一中心虚设走线,所述中心虚设走线与所述第一电压走线及所述第二电压走线位于同一直线上,并位于所述第一电压走线与所述第二电压走线之间。

167.作为示例,所述第一虚设走线、所述第二虚设走线、所述第三虚设走线及所述第四虚设走线均与所述中心虚设走线在所述第二方向x上有相对部分。或者所述第一虚设走线及所述第四虚设走线均与所述中心虚设走线在所述第二方向x上没有相对部分,所述第二虚设走线及所述第三虚设走线均与所述中心虚设走线在所述第二方向x上有相对部分。

168.作为示例,多条所述虚设走线还包括第五虚设走线,所述第五虚设走线与所述第三虚设走线及所述第四虚设走线位于同一直线上,且所述第五虚设走线位于所述第三虚设走线与所述第四虚设走线之间。

169.作为示例,所述三维存储器件中设有页面缓冲高压nmos晶体管,所述晶体管的漏极通过第一接触部连接于所述第一电压走线下方,所述晶体管的源极通过第二接触部连接于所述第二电压走线下方。

170.作为示例,所述第一电压走线的电压大于或等于20v,所述第二电压走线的电压小于或等于10v。

171.作为示例,所述走线层还包括第三电压走线,所述第三电压走线的电压等于所述第二电压走线的电压,所述第三电压走线与所述第二电压走线平行,且所述第三电压走线与所述第二电压走线之间通过至少一所述虚设走线间隔。

172.作为示例,所述第三电压走线与所述第二电压走线通过至少一所述虚设走线及至少两个连接部连接,且至少一所述连接部的两侧分别与所述第二电压走线及一所述虚设走线连接,至少一所述连接部的两侧分别与一所述虚设走线及所述第三电压走线连接。

173.本实施例中件的制作方法可以用于制作实施例一至实施例四中任意一项所述的三维存储器件,通过简单改变光刻图形即可实现不同的走线层设计,具有工艺简单,不会增加制作成本的优点。

174.综上所述,本发明的三维存储器件及其制作方法通过改进走线的布局,使得紧邻高压走线或低压走线的虚设走线不同时面对高压走线与低压走线,从而可以在不增加走线之间间距的情况下有效提高高压走线与虚设走线之间、或者虚设走线与低压走线之间的线对线击穿电压(vbd),不仅可以有效控制芯片面积,且不会影响原本的高压走线与低压走线。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

175.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1