沟槽栅超结器件及其制造方法与流程

本发明涉及半导体集成电路制造领域,特别是涉及一种沟槽栅超结(superjunction)器件。本发明还涉及一种沟槽栅超结器件的制造方法。

背景技术:

1、超结结构就是交替排列的n型柱和p型柱的结构。如果用超结结构来取代垂直双扩散mos晶体管(vertical double-diffused metal-oxide-semiconductor,vdmos)器件中的n型漂移区,在导通状态下提供导通通路(只有n型柱提供通路,p型柱不提供),在截止状态下承受反偏电压(pn立柱共同承受),就形成了超结金属-氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)。超结mosfet能在反向击穿电压与传统的vdmos器件一致的情况下,通过使用低电阻率的外延层,而使器件的导通电阻大幅降低。

2、一般的超结器件,都包含电荷流动区,过渡区和终端区域。电荷流动区由交替排列的p型柱和n型柱形成,或者为了在导通时得到更低的电阻值,都需要采用更高浓度的p-n柱结合更小的步进,p-n柱表示交替排列的p型柱和n型柱。但是在沟槽填充的p-n柱中,更小的步进就需要减小沟槽的宽度,过渡区比邻电荷流动区即电流流动区并将电荷流动区围绕,过渡区中包括一个宽度较大的p型区域,至少p型区域之上可以有一定厚度的介质膜,介质膜上可以有多晶硅和多晶硅上面的接触孔和金属,这个多晶硅和金属分别作为多晶硅场板和金属场板与正面金属层组成的栅极衬垫(gate pad)相连,并和电荷流动区的多晶硅栅相连,实现栅极上的电位控制;这个与多晶硅栅通过接触孔相连的金属即栅极的金属和电荷流动区以及部分过渡区(p型环的一个部分相连)上的金属即源极的金属在物理上有一定间隔,例如2微米~10微米;过渡区之外有一个终端区,终端区域有交替排列的p型柱和n型柱,可以有介质膜,介质膜上可以有浮空的多晶硅场板和金属场板,并在终端靠近划片槽的区域可以有n+截止环,其上可以有浮空或者连接到n+的金属场板,终端区域用于承受芯片反向偏置的电压,并给芯片进行了一定的物理保护。

3、在现有技术上,n型外延是淀积在高浓度的n型半导体衬底上的,例如对于高于600v的超结器件,n型衬底的杂质浓度高于1e19cm-3,而n型外延的浓度都是在1e15cm-3~1e16cm-3,为了降低比导通电阻,芯片的n型外延杂质浓度不断提高,p-n柱的横向尺寸不断缩小即步进减小,同时采用沟槽栅的优势越来越高,因为采用沟槽栅一是可以增加沟道密度,降低比导通电阻,同时消除了平面栅的jfet区域,jfet区域在步进不断减小的情况下,平面栅在多晶栅之下的p型阱之间的n区域越来越小,jfet效应越来越严重,沟槽栅消除了jfet效应后有利于进一步降低比导通电阻。

4、随着深沟槽即超结结构的沟槽也即超结沟槽的步进的缩小,由于达到同样击穿电压的超结沟槽的深度基本一样,例如击穿电压600v的器件,p型柱沟槽的深度基本要40μm或者更深一些,这样p型柱的深宽比加大,超结沟槽的填充难度加大超结沟槽填充中,至少一个很大的难点是在填充封口的附近即超结沟槽的顶部开口附近,由于开口很小,填充的过程中在接近封口的区域,由于沟槽的形貌,填充工艺过程中的不均匀性,有些区域会在位置较低的区域没有完全填充好的情况下,上部出现了封口,这样就在这个位置上出现了小的空洞,或者填充质量低,主要是填充的p型硅的密度不够,小的空洞,如果在器件应用过程中没有处于0电位,例如在反向偏压时这个区域进入了耗尽区域,那么这些空洞就会产品大量的电子空穴对,导致器件的漏电很大,影响器件的性能也影响器件的可靠性。如果是填充质量不足够好,那么在发生耗尽时也会出现漏电的增高,但更可能是影响器件的寿命。这个空洞一般可以通过sem,tem进行观察到,填充质量不够好,但是没有明显空洞的,一般在制样过程中通过较长的腐蚀时间处理,也能看到该位置与填充质量好的区域的对比度的差异。但是为了提高产品的可生产性,特别是考虑p型外延(epi)工艺的填充速率,需要器件能容忍一定的小缺陷。

5、另外,采用沟槽栅带来一个cgd大,特别是cgd的变化比较大的问题,cgd表示栅漏电容,因此沟槽栅的沟槽刻蚀工艺,控制难度很大,深度的变化会比较大,例如:深度4微米的沟槽,深度的变化可能达到+0.4微米~-0.4微米的范围,cgd会正比与栅极和n型柱的接触面积,沟槽栅的沟槽即栅极沟槽的这个变化使得器件的cgd的变化很大,影响器件开关特性的一致性。

6、如图1所示,是现有超结器件俯视图;一般的超结器件结构,都包含电流流动区、横向承受反向偏置电压的终端区和处于电流流动区和终端区之间的过渡区,终端区环绕于所述电流流动区的外周,图1中1区表示电流流动区,2区表示过渡区,3区表示终端区。

7、1区包括由交替排列的p型柱22和n型柱23组成的超结结构,图1中的p型柱22和n型柱23都呈条形结构。n型柱23于在超结器件导通时提供导通通路,p型柱22和n型柱23在超结器件反偏时互相耗尽共同承受反向偏压。

8、2区和3区位于超结器件的终端,共同作为表示超结器件的终端保护结构。在器件导通时所述2区和3区不提供电流,在反偏状态用于承担从1区外周单元的表面到器件最外端表面衬底的电压该电压为横向电压和从1区外周单元表面到衬底的电压该电压为纵向电压。

9、2区中有至少一个p型环25,图1中为一个p型环25,该p型环25一般与1区的p型背栅即p型阱连接在一起;现有技术中,2区中一般有具有一定倾斜角的场板介质膜,在2区中还具有用于减缓表面电场急剧变化的场板24,场板24为多晶场板片或金属场板,以及p型柱22;2区中也可以不设置所述金属场板。

10、3区包括由交替排列的p型柱22和n型柱23组成的超结结构,图1中3区的p型柱22和n型柱23分别由1区中的p型柱22和n型柱23延伸扩展而成,交替排列方向相同。在其它结构中,3区的p型柱22和n型柱23也能首尾相连的环型结构。

11、3区中有金属场板,3区中也可以不设置所述金属场板;3区中可以有p型环25也可以没有,有p型环25时该处的p型环是不与电流流动区的p型背栅连接相连的(悬浮的);在3区的最外端有终端截止环21,所述终端截止环21由n+注入区或n+注入区再加形成于其上的介质或介质加上金属构成。

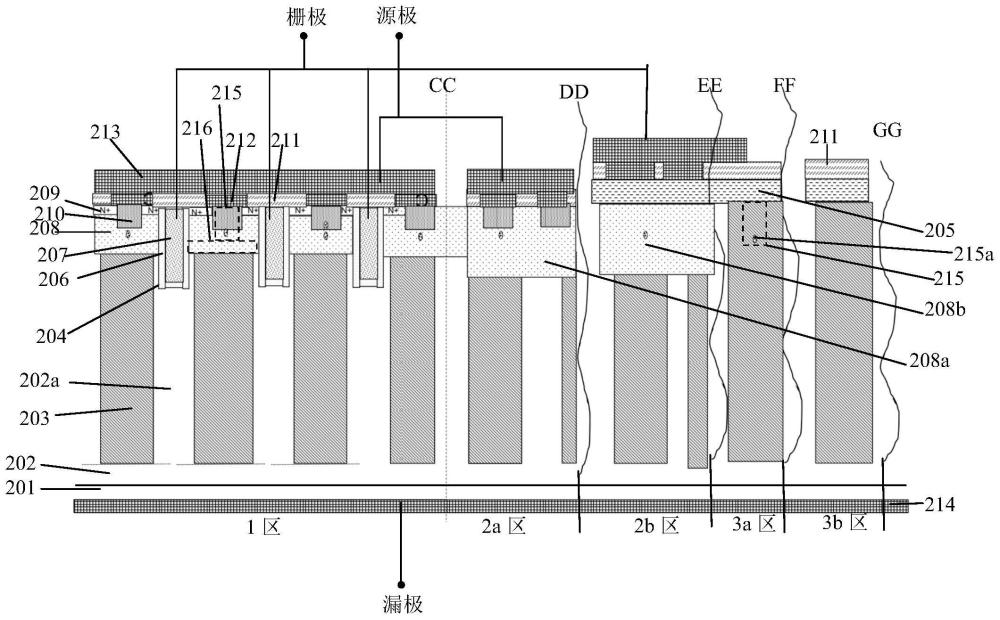

12、如图2a所示,是现有沟槽栅超结器件的剖面示意图;如图2b所示,是现有沟槽栅超结器件的俯视图的局部放大图;现有沟槽栅超结器件的中间区域为电流流动区,终端区环绕于所述电流流动区的外周,过渡区位于所述电流流动区和所述终端区之间。图2a中,所述电流流动区为1区,所述过渡区为2区,所述终端区为3区,俯视面结构如图1所示。

13、在半导体衬底101上形成有外延层102,在外延层102中形成有由n型柱102a和p型柱103交替排列形成的超结结构。n型柱102a对应于图1中的n型柱23,p型柱103对应于图1中的p型柱22。如图2b所示,随着超结结构的步进减小,所述p型柱22的顶部容易形成缺陷114,缺陷114为小空洞或者质量较差材料。

14、在1区、2区和3区中都形成有所述超结结构,在所述电流流动区的所述超结结构的顶部形成有多个呈并联结构的超结器件的器件单元结构。

15、各所述器件单元结构的沟槽栅由形成于栅极沟槽中栅介质层104和多晶硅栅105叠加而成。

16、所述栅极沟槽全部或部分位于所述n型柱102a中,所述栅介质层104形成于所述栅极沟槽的侧面,所述多晶硅栅105所述栅极沟槽完全填充。

17、各所述器件单元结构的沟道区由形成于所述超结结构表面p型阱区106组成,所述多晶硅栅105在纵向上穿过所述沟道区,被位于所述n型柱102a中的所述多晶硅栅105的侧面覆盖的所述沟道区表面用于形成导电沟道,所述导电沟道下方被所述多晶硅栅105侧面覆盖的所述n型柱102a的表面用于形成积累区。

18、当所述栅极沟槽全部位于所述n型柱102a中,所述多晶硅栅105的两个侧面都会覆盖对应的所述沟道区并形成所述导电沟道。

19、当所述栅极沟槽部分位于所述n型柱102a中时,所述栅极沟槽的一个侧面会位于所述n型柱102a中,另一个侧面则会位于p型柱103中,这样所述多晶硅栅105仅有一个侧面即位于所述n型柱102a中的侧面会覆盖对应的所述沟道区并形成所述导电沟道。

20、在所述沟道区的表面形成有由n型重掺杂区组成的源区107。

21、在所述过渡区中形成有p型环106a。p型环106a对应于图1中的p型环25。

22、在所述终端区即3区还形成有保护环介质层109;保护环介质层109的材料通常采用氧化层,保护环介质层109的内侧面通常会延伸到所述过渡区中。

23、在所述过渡区的所述保护环介质层109的顶部还形成有多晶硅场板105a,多晶硅场板105a通常和多晶硅栅105同时形成,即对多晶硅进行图形化刻蚀同时形成。

24、所述超结器件还包括由正面金属层112图形化形成的源极和栅极,所述栅极包括栅衬垫(gate pad)、栅总线(gate bus)和栅手指(gate finger)。通常,所述正面金属层112包括多层,图2a中仅显示了一层。

25、所述沟道区和所述源区107通过顶部对应的接触孔112连接到所述源极。所述接触孔112穿过所述层间膜110。

26、所述p型环106a通过顶部对应的接触孔112连接到所述源极。在所述源区107和所述p型环106a对应的接触孔112的底部形成有p型重掺杂的接触区108,通过所述接触区108实现接触孔112和底部对应的所述沟道区和所述p型环106a的欧姆接触。

27、所述多晶硅场板105a通过顶部对应的接触孔112连接到所述栅极。图2a对应的剖面中没有显示所述多晶硅栅105顶部的接触孔112,在其他剖面中,所述多晶硅栅105会通过顶部的接触孔112连接对应的所述栅总线或所述栅手指,最后通过所述栅总线或所述栅手指连接到所述栅衬垫。

28、在所述终端区的最外侧还形成有n+区组成的截止环107a,截止环107a对应于图1中的截止环21。

29、所述超结器件还包括如下背面结构:

30、由背面减薄后的所述半导体衬底101组成的漏区,所述半导体衬底101采用n型重掺杂时不需要进行背面注入或增加n+背面离子注入;如果所述半导体衬底101不采用n型重掺杂时,则需要增加n+背面离子注入来使所述漏区的掺杂满足要求。

31、在漏区的背面形成有由背面金属层113组成的漏极。

32、图2a中,1区位于线aa的左侧,2区位于线aa和线bb之间,3区位于线bb的右侧。由于图2a中仅显示了所述沟槽栅超结器件部分区域的剖面结构且有一定的省略,如1区和2区之间的虚线aa处有一定的省略。为了便于理解在图2a中增加了和源极、漏极以及栅极相关的电路连线,这些电路连线仅表示各金属层的电连接关系,并不具体限定各金属层具体的连接结构。例如,图2a的剖面中,所述电流流动区的所述源区107顶部的所述正面金属层112和所述过渡区的所述p型环106a顶部的所述正面金属层112虽然没有显示二者直接接触在一起,但是实际二者,通常二者能直接接触在一起的并呈一整体结构,也即,不需要额外在设置接触孔和另外的金属层就能使所述电流流动区的所述源区107顶部的所述正面金属层112和所述过渡区的所述p型环106a顶部的所述正面金属层112接触在一起。

33、同样,图2a中,所述多晶硅场板105a顶部的所述正面金属层112是作为栅总线的金属,所述栅总线和所述电流流动区的所述栅极沟槽的所述多晶硅栅105无法直接形成接触,二者之间需要通过多晶硅和接触孔112实现电连接,图2a中和栅极相关的电路连线则显示了所述电流流动区的所述多晶硅栅105和所述多晶硅场板105a顶部的所述正面金属层112是电连接在一起的。

技术实现思路

1、本发明所要解决的技术问题是提供一种沟槽栅超结器件,能消除超结结构的第二导电类型柱填充超结沟槽时在超结沟槽的顶部开口区域形成的封口缺陷区对器件性能的不利影响,特别有利于提高小步进的超结结构的沟槽外延填充的工艺窗口和效率。为此,本发明还提供一种沟槽栅超结器件的制造方法。

2、为解决上述技术问题,本发明提供的沟槽栅超结器件的中间区域为电流流动区,终端区环绕于所述电流流动区的外周,过渡区位于所述电流流动区和所述终端区之间。

3、在半导体衬底的顶部表面上形成有第一导电类型的第一外延层,在所述第一外延层中形成有由第一导电类型柱和第二导电类型柱交替排列形成的超结结构;所述第二导电类型柱由填充于超结沟槽中的第二导电类型的第二外延层组成。

4、所述超结沟槽形成于所述第一外延层中且各所述超结沟槽的底部表面和所述半导体衬底的顶部表面具有间隔。

5、所述第二导电类型柱的顶部具有封口缺陷区,所述封口缺陷区由所述第二外延层填充所述超结沟槽时形成于所述超结沟槽的顶部开口区域。

6、在所述电流流动区形成有所述超结结构,且在所述电流流动区的所述超结结构的顶部形成有多个呈并联结构的超结器件的器件单元结构。

7、各所述器件单元结构包括沟槽栅,所述沟槽栅包括形成于栅极沟槽中的栅介质层和栅极导电材料层;所述栅极沟槽全部或者部分位于所述第一导电类型柱中。

8、各所述器件单元结构的沟道区由形成于所述超结结构表面第二导电类型阱区组成,所述栅极导电材料层在纵向上穿过所述沟道区,被位于所述第一导电类型柱中的所述栅极导电材料层的侧面覆盖的所述沟道区表面用于形成导电沟道。

9、所述沟道区底部的所述第一外延层组成漂移区,在所述超结器件反偏时,所述漂移区会对所述沟道区产生纵向耗尽并形成阱耗尽区,所述第二导电类型阱区的深度大于等于所述阱耗尽区的深度和所述封口缺陷区的深度和,使所述超结器件反偏时使所述阱耗尽区完全位于所述封口缺陷区的下方从而防止所述阱耗尽区进入到所述封口缺陷区中。

10、在所述沟道区的表面形成有由第一导电类型重掺杂区组成的源区。

11、在所述过渡区中形成有第二导电类型环。

12、进一步的改进是,保护环介质层覆盖至少部分所述终端区并延伸到所述过渡区中,所述保护环介质层的内侧面位于所述过渡区的上,且所述保护环介质层的内侧面将所述过渡区分为第一过渡区和第二过渡区,所述第一过渡区位于所述保护环介质层的内侧表面的内侧,所述第二过渡区位于所述保护环介质层的内侧表面的外侧。

13、进一步的改进是,所述保护环介质层也形成在栅极手指的形成区域和栅极衬垫的形成区域中。

14、进一步的改进是,所述保护环介质层为氧化层。

15、进一步的改进是,所述保护环介质层的氧化层为热氧化层或者为热氧化层和cvd沉积氧化层的叠加层。

16、进一步的改进是,所述栅极导电材料层为多晶硅栅。

17、所述多晶硅栅通过对第一多晶硅层进行全面回刻形成或者进行图形化刻蚀形成。

18、进一步的改进是,所述超结器件还包括由正面金属层图形化形成的源极和栅极,所述栅极包括栅极衬垫、栅极总线和栅极手指。

19、所述沟道区和所述源区通过顶部对应的接触孔连接到所述源极。

20、所述第二导电类型环通过顶部且位于所述第一过渡区中的接触孔连接到所述源极。

21、进一步的改进是,所述第二导电类型阱区的深度大于2微米或者达3微米以上。

22、进一步的改进是,所述栅极沟槽的深度大于等于4微米。

23、为解决上述技术问题,本发明提供的沟槽栅超结器件的制造方法中,超结器件分为电流流动区、过渡区和终端区,中间区域为所述电流流动区,所述终端区环绕于所述电流流动区的外周,所述过渡区位于所述电流流动区和所述终端区之间;包括如下步骤:

24、步骤一、提供半导体衬底,在所述半导体衬底的顶部表面上形成有第一导电类型的第一外延层,进行第二导电类型环离子注入在所述过渡区中形成第二导电类型环。

25、步骤二、形成保护环介质层,所述保护环介质层覆盖至少部分所述终端区并延伸到所述过渡区中,所述保护环介质层的内侧面位于所述过渡区的上,且所述保护环介质层的内侧面将所述过渡区分为第一过渡区和第二过渡区,所述第一过渡区位于所述保护环介质层的内侧表面的内侧,所述第二过渡区位于所述保护环介质层的内侧表面的外侧。

26、步骤二、在所述第一外延层中形成由第一导电类型柱和第二导电类型柱交替排列形成的超结结构;所述电流流动区中具有所述超结结构;包括如下分步骤:

27、采用光刻定义加刻蚀工艺在所述第一外延层中形成超结沟槽;各所述超结沟槽的底部表面和所述半导体衬底的顶部表面具有间隔。

28、进行外延生长工艺在所述超结沟槽中填充第二导电类型的第二外延层;由填充于超结沟槽中的第二导电类型的第二外延层组成所述第二导电类型柱,由所述第二导电类型柱之间的所述第一外延层组成所述第一导电类型柱;所述第二导电类型柱的顶部具有封口缺陷区,所述封口缺陷区由所述第二外延层填充所述超结沟槽时形成于所述超结沟槽的顶部开口区域。

29、步骤三、形成保护环介质层,所述保护环介质层覆盖至少部分所述终端区并延伸到所述过渡区中,所述保护环介质层的内侧面位于所述过渡区的上,且所述保护环介质层的内侧面将所述过渡区分为第一过渡区和第二过渡区,所述第一过渡区位于所述保护环介质层的内侧表面的内侧,所述第二过渡区位于所述保护环介质层的内侧表面的外侧。

30、步骤四、形成所述超结器件的各器件单元结构的沟槽栅,各所述器件单元结构形成于所述电流流动区的所述超结结构的顶部并呈并联结构,所述沟槽栅包括形成于栅极沟槽中的栅介质层和栅极导电材料层;所述栅极沟槽全部或者部分位于所述第一导电类型柱中。

31、步骤五、进行第二导电类型阱注入在所述超结结构表面形成第二导电类型阱区,各所述器件单元结构的沟道区由形成于所述超结结构表面第二导电类型阱区组成,所述栅极导电材料层在纵向上穿过所述沟道区,被位于所述第一导电类型柱中的所述栅极导电材料层的侧面覆盖的所述沟道区表面用于形成导电沟道。

32、所述沟道区底部的所述第一外延层组成漂移区,在所述超结器件反偏时,所述漂移区会对所述沟道区产生纵向耗尽并形成阱耗尽区,所述第二导电类型阱区的深度大于等于所述阱耗尽区的深度和所述封口缺陷区的深度和,使所述超结器件反偏时使所述阱耗尽区完全位于所述封口缺陷区的下方从而防止所述阱耗尽区进入到所述封口缺陷区中。

33、步骤六、进行第一导电类型重掺杂离子注入在所述沟道区的表面形成源区。

34、进一步的改进是,所述保护环介质层也形成在栅极手指的形成区域和栅极衬垫的形成区域中。

35、进一步的改进是,步骤三中,所述保护环介质层为氧化层,所述保护环介质层的氧化层形成之后,采用光刻加刻蚀工艺对所述保护环介质层的氧化层进行图形化形成所述保护环介质层。

36、进一步的改进是,所述保护环介质层的氧化层为采用热氧化工艺形成的热氧化层组成;或者所述保护环介质层的氧化层为热氧化层和采用cvd沉积工艺形成的cvd沉积氧化层的叠加层。

37、进一步的改进是,所述栅极导电材料层为多晶硅栅。

38、所述多晶硅栅通过对第一多晶硅层进行全面回刻形成或者进行图形化刻蚀形成。

39、进一步的改进是,步骤六之后,还包括:形成层间膜,接触孔和正面金属层,对所述正面金属层进行图形化形成源极和栅极,所述栅极包括栅极衬垫、栅极总线和栅极手指。

40、所述沟道区和所述源区通过顶部对应的所述接触孔连接到所述源极。

41、所述第二导电类型环通过顶部且位于所述第一过渡区中的接触孔连接到所述源极。

42、进一步的改进是,所述第二导电类型阱区的深度大于2微米或者达3微米以上。

43、进一步的改进是,所述栅极沟槽的深度大于等于4微米。

44、本发明通过结合超结结构的外延填充形成的封口缺陷区和阱耗尽区的深度来设置第二导电类型阱区的深度,能消除超结结构的封口缺陷区对器件性能的不利影响,例如能消除阱耗尽区到达封口缺陷区时所产生的漏电和可靠性问题,从而本发明能在超结结构具有封口缺陷区的条件下使器件的可靠性满足要求以及使漏电特性稳定。

45、本发明在超结结构具有封口缺陷区的条件下,能降低超结结构的外延填充难度并从而提升外延填充效率,特别有利于提高小步进的超结结构的沟槽外延填充的工艺窗口和效率。

- 还没有人留言评论。精彩留言会获得点赞!