半导体结构与半导体结构的形成方法与流程

本公开涉及半导体,具体而言,涉及一种半导体结构与半导体结构的形成方法。

背景技术:

1、随着半导体的发展,摩尔定律走向极限,2.5d和3d集成技术渐成为延续摩尔定律、提高电子系统性能和功能密度的有效手段,2.5d和3d集成技术中大量用到tsv(throughsilicon via,硅通孔)导电通孔。tsv工艺通过在晶圆中形成金属立柱,并配以金属凸点,可以实现晶圆(芯片)之间或芯片与基板间直接的三维互连,这样可以弥补传统半导体芯片二维布线的局限性。这种互连方式与传统的堆叠技术如键合技术相比具有三维方向堆叠密度大、封装后外形尺寸小等优点,从而大大提高芯片的速度并降低功耗。因此,tsv技术已经被广泛认为是继键合、载带焊和倒装芯片之后的第四代封装技术,将逐渐成为高密度封装领域的主流技术。

2、然而,现有工艺中tsv正面端部互连工艺具有以下缺点:在当前tsv的各向同性的干法刻蚀工艺中,tsv孔边缘处会出现凸起部分,当制作绝缘层、种子层和金属填充时,会形成一个多层结构的“应力集中”区,使此处的绝缘层与基底之间产生容易分层或裂纹,严重影响tsv质量和可靠性,而当前的工艺和结构无法消除应力集中区的影响。

3、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本公开的目的在于提供一种半导体结构与半导体结构的形成方法,半导体结构提高了释放应力能力,改善了半导体结构中应力集中的问题。

2、本公开的其他特性和优点将通过下面的详细描述变得显然,或部分地通过本公开的实践而习得。

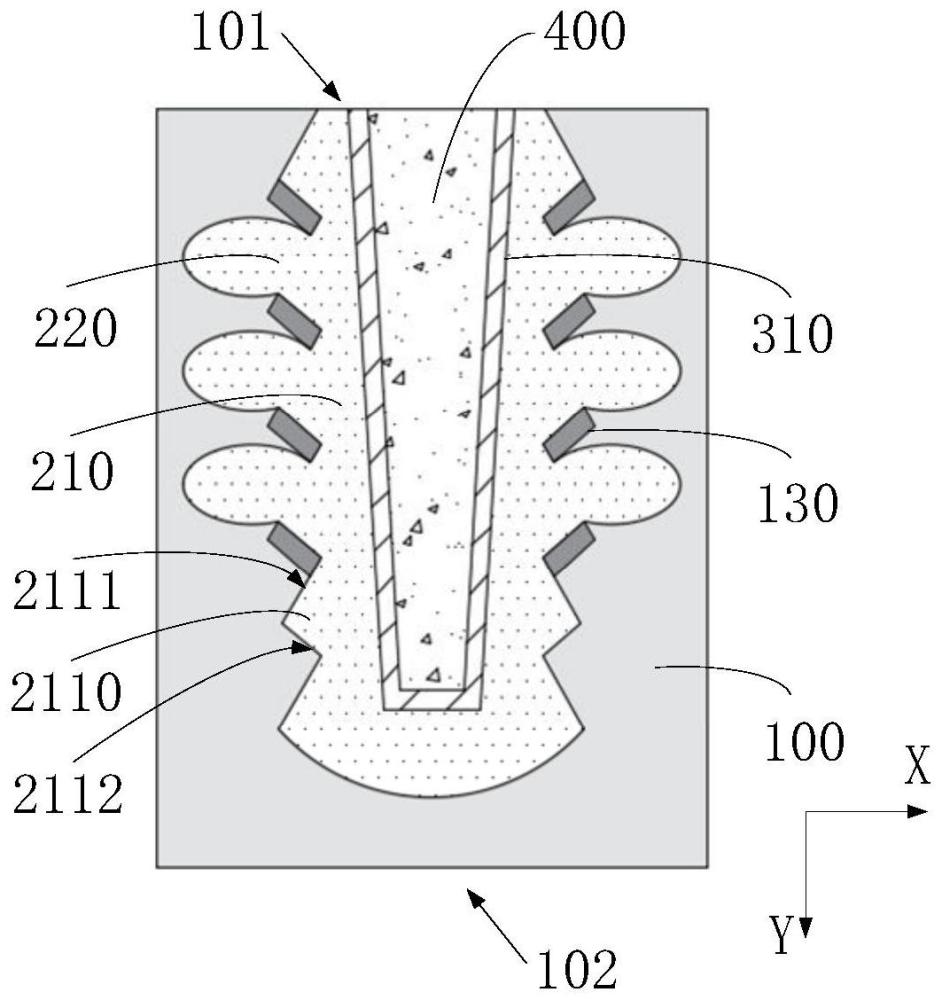

3、根据本公开实施例的一个方面,提供了一种半导体结构,该半导体结构包括:

4、衬底,包括相背的第一面和第二面;

5、第一缓冲结构,位于所述衬底中,且沿第一方向延伸,所述第一方向为由所述第一面指向所述第二面的方向;

6、第二缓冲结构,位于所述第一缓冲结构的部分侧壁上,且沿第二方向延伸,所述第二方向与所述第一方向相交;以及

7、导电结构,位于所述第一缓冲结构中,且沿所述第一方向延伸。

8、在本公开的一种示例性实施例中,所述第二缓冲结构位于所述第一缓冲结构上靠近所述第一面的一端。

9、在本公开的一种示例性实施例中,所述第二缓冲结构在所述第一缓冲结构的周向上呈环形凸起。

10、在本公开的一种示例性实施例中,所述半导体结构包括多个第二缓冲结构,所述多个第二缓冲结构在所述第一方向上均匀分布。

11、在本公开的一种示例性实施例中,所述第二缓冲结构在所述第一方向上的宽度,沿所述第二方向先逐渐增大,后逐渐减小。

12、在本公开的一种示例性实施例中,所述第一缓冲结构与所述第二缓冲结构为一体式结构。

13、在本公开的一种示例性实施例中,所述第一缓冲结构与所述第二缓冲结构的材料不同。

14、在本公开的一种示例性实施例中,所述第一缓冲结构的侧壁上具有凸起部,所述凸起部具有第一表面和第二表面,所述第一表面和所述第二表面相交,所述第二缓冲结构在所述第一表面上沿所述第二方向延伸。

15、在本公开的一种示例性实施例中,所述半导体结构还包括:

16、阻挡结构,位于所述凸起部的所述第一表面上。

17、在本公开的一种示例性实施例中,所述阻挡结构位于所述第二缓冲结构的两侧。

18、在本公开的一种示例性实施例中,所述阻挡结构在所述第一缓冲结构的周向上呈环状。

19、在本公开的一种示例性实施例中,所述导电结构两端分别从所述第一面和所述第二面露出。

20、根据本公开实施例的另一个方面,提供了一种半导体结构的形成方法,该形成方法包括:

21、提供衬底,所述衬底包括相背的第一面和第二面;

22、在所述衬底的所述第一面上沿第一方向形成第一凹陷部,所述第一方向为由所述第一面指向所述第二面的方向;

23、在所述第一凹陷部的侧壁上沿第二方向形成第二凹陷部,所述第二方向与所述第一方向相交;

24、在所述第二凹陷部中形成第二缓冲结构,在所述第一凹陷部中形成第一缓冲结构;

25、在所述第一缓冲结构中形成导电结构,所述导电结构在所述第一方向上延伸。

26、在本公开的一种示例性实施例中,在所述第一凹陷部的侧壁上沿第二方向形成第二凹陷部,包括:

27、在所述第一凹陷部的部分侧壁上形成阻挡结构;

28、以所述阻挡结构为掩膜对所述第一凹陷部的部分侧壁进行刻蚀,形成第二凹陷部。

29、在本公开的一种示例性实施例中,在所述第一凹陷部的部分侧壁上形成阻挡结构,包括:

30、在所述第一凹陷部的部分侧壁进行离子掺杂,所述离子掺杂区域形成阻挡结构。

31、在本公开的一种示例性实施例中,在所述第一凹陷部的部分侧壁上形成多个阻挡结构,对相邻两个所述阻挡结构之间的所述第一凹陷部侧壁沿所述第二方向进行侧向刻蚀,形成所述第二凹陷部。

32、在本公开的一种示例性实施例中,在所述第二凹陷部中填充第二缓冲材料形成第二缓冲结构;在所述第一凹陷部中填充第一缓冲材料形成所述第一缓冲结构。

33、在本公开的一种示例性实施例中,对所述第一缓冲结构沿所述第一方向进行刻蚀,形成具有第一沟槽的第一缓冲结构,在所述第一沟槽中形成所述导电结构。

34、在本公开的一种示例性实施例中,在形成所述第一缓冲结构之后,形成所述导电结构之前,所述形成方法还包括:

35、在所述第一沟槽中填充阻挡材料形成阻挡初始层;

36、对所述阻挡初始层沿所述第一方向进行刻蚀,形成具有第二沟槽的阻挡层;在所述第二沟槽中形成所述导电结构。

37、在本公开的一种示例性实施例中,所述第一缓冲结构与所述第二缓冲结构的材料相同;通过同一次填充工艺,在所述第一凹陷部中形成第一缓冲结构,在所述第二凹陷部中形成第二缓冲结构。

38、在本公开的一种示例性实施例中,在所述第一缓冲结构中形成导电结构;

39、在所述第一缓冲结构中形成导电初始结构;

40、从所述第二面进行化学机械抛光,形成两端分别从所述第一面和所述第二面露出的导电结构。

41、本公开提供的半导体结构,接触结构中的第一缓冲结构覆盖导电结构的侧壁,能够作为应力缓冲层对tsv的应力集中区进行释放;第二缓冲结构位于第一缓冲结构的外侧,能够对tsv的应力进一步地进行释放,减轻半导体结构中tsv中应力集中的问题。

42、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述第二缓冲结构位于所述第一缓冲结构上靠近所述第一面的一端。

3.根据权利要求1所述的半导体结构,其特征在于,所述第二缓冲结构在所述第一缓冲结构的周向上呈环形凸起。

4.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构包括多个第二缓冲结构,所述多个第二缓冲结构在所述第一方向上均匀分布。

5.根据权利要求1所述的半导体结构,其特征在于,所述第二缓冲结构在所述第一方向上的宽度,沿所述第二方向先逐渐增大,后逐渐减小。

6.根据权利要求1所述的半导体结构,其特征在于,所述第一缓冲结构与所述第二缓冲结构为一体式结构。

7.根据权利要求1所述的半导体结构,其特征在于,所述第一缓冲结构与所述第二缓冲结构的材料不同。

8.根据权利要求1所述的半导体结构,其特征在于,所述第一缓冲结构的侧壁上具有凸起部,所述凸起部具有第一表面和第二表面,所述第一表面和所述第二表面相交,所述第二缓冲结构在所述第一表面上沿所述第二方向延伸。

9.根据权利要求8所述的半导体结构,其特征在于,所述半导体结构还包括:

10.根据权利要求9所述的半导体结构,其特征在于,所述阻挡结构位于所述第二缓冲结构的两侧。

11.根据权利要求9所述的半导体结构,其特征在于,所述阻挡结构在所述第一缓冲结构的周向上呈环状。

12.根据权利要求1所述的半导体结构,其特征在于,所述导电结构两端分别从所述第一面和所述第二面露出。

13.一种半导体结构的形成方法,其特征在于,包括:

14.根据权利要求13所述的形成方法,其特征在于,在所述第一凹陷部的侧壁上沿第二方向形成第二凹陷部,包括:

15.根据权利要求14所述的形成方法,其特征在于,在所述第一凹陷部的部分侧壁上形成阻挡结构,包括:

16.根据权利要求14所述的形成方法,其特征在于,在所述第一凹陷部的部分侧壁上形成多个阻挡结构,对相邻两个所述阻挡结构之间的所述第一凹陷部侧壁沿所述第二方向进行侧向刻蚀,形成所述第二凹陷部。

17.根据权利要求13所述的形成方法,其特征在于,在所述第二凹陷部中填充第二缓冲材料形成第二缓冲结构;在所述第一凹陷部中填充第一缓冲材料形成所述第一缓冲结构。

18.根据权利要求17所述的形成方法,其特征在于,对所述第一缓冲结构沿所述第一方向进行刻蚀,形成具有第一沟槽的第一缓冲结构,在所述第一沟槽中形成所述导电结构。

19.根据权利要求18所述的形成方法,其特征在于,在形成所述第一缓冲结构之后,形成所述导电结构之前,所述形成方法还包括:

20.根据权利要求13所述的方法,其特征在于,所述第一缓冲结构与所述第二缓冲结构的材料相同;通过同一次填充工艺,在所述第一凹陷部中形成第一缓冲结构,在所述第二凹陷部中形成第二缓冲结构。

21.根据权利要求13所述的方法,其特征在于,在所述第一缓冲结构中形成导电结构;

技术总结

一种半导体结构及其制造方法,该半导体结构包括:衬底、第一缓冲结构、第二缓冲结构和导电结构,衬底包括相背的第一面和第二面;第一缓冲结构位于所述衬底中,且沿第一方向延伸,所述第一方向为由所述第一面指向所述第二面的方向;第二缓冲结构位于所述第一缓冲结构的部分侧壁上,且沿第二方向延伸,所述第二方向与所述第一方向相交;导电结构位于所述第一缓冲结构中,且沿所述第一方向延伸。本公开提供的半导体结构提高了应力释放能力,改善了半导体结构中应力集中的问题。

技术研发人员:张永会

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!