一种数据处理结构、半导体结构和存储器的制作方法

本公开涉及半导体,尤其涉及一种数据处理结构、半导体结构和 存储器。

背景技术:

1、目前,随着电路集成度的不断提高,集成电路的器件尺寸以及器件距离进 一步压缩,对器件功能提出了更高的要求。存储器中存在对数据进行逻辑处理 的功能模块,在工作速度较高的情况,数据处理结构的不同部分之间存在干扰, 降低了存储器的性能。

技术实现思路

1、本公开提供了一种数据处理结构、半导体结构和存储器,能够降低噪声干 扰问题,提高数据处理结构的工作性能。

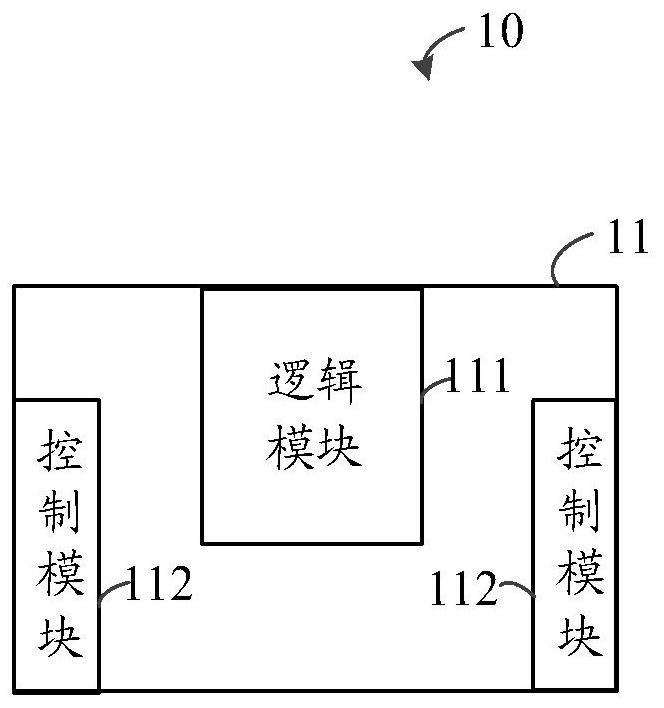

2、第一方面,本公开实施例提供了一种数据处理结构,所述数据处理结构包 括数据采样模块,且所述数据采样模块包括逻辑模块和控制模块,所述控制模 块位于所述逻辑模块的外围;所述逻辑模块包括第一阱区,所述控制模块包括 第二阱区,所述第一阱区与所述第二阱区之间存在间隔,以使得所述控制模块 和所述逻辑模块分离设置;其中,

3、所述控制模块,用于产生使能控制信号;

4、所述逻辑模块,用于接收第一数据信号、时钟信号和所述使能控制信号; 在所述使能控制信号有效的情况下,利用所述时钟信号对第一数据信号进行采 样处理,输出第二数据信号。

5、在一些实施例中,所述第一阱区与第一电源连接,所述第二阱区与第二电 源连接,且所述第一电源的电位高于所述第二电源的电位。

6、在一些实施例中,所述数据处理结构还包括数据缓冲模块,所述数据缓冲 模块用于输出所述第一数据信号,或者接收所述第二数据信号;

7、所述数据缓冲模块和所述数据采样模块相邻,且所述数据采样模块和所述 数据缓冲模块沿第一方向排列。

8、在一些实施例中,在第一方向上,所述控制模块的投影与所述逻辑模块的 投影具有重叠部分。

9、在一些实施例中,在所述第一方向上,所述控制模块和所述逻辑模块均位 于所述数据缓冲模块同一侧,且所述控制模块与所述数据缓冲模块相接触,所 述逻辑模块和所述数据缓冲模块之间的距离为第一值;在第二方向上,所述控 制模块与所述逻辑模块之间的距离为第二值,以使得所述控制模块、所述逻辑 模块和所述数据缓冲模块之间存在一连续区域;其中,所述第二方向和所述第 一方向垂直。

10、在一些实施例中,所述数据处理结构还包括多个电容模块;其中,

11、多个所述电容模块位于所述控制模块、所述逻辑模块和所述数据缓冲模块 之间的连续区域中;其中,所述数据采样模块和所述数据缓冲模块共用多个所 述电容模块实现电源去噪功能。

12、在一些实施例中,所述电容模块的电源端通过金属层和接触结构连接到电 源信号端,所述电容模块的接地端通过金属层和接触结构连接到地信号端;

13、其中,所述电源信号端为所述数据采样模块和所述数据缓冲模块供电。

14、在一些实施例中,每一所述电容模块均包括并联设置的多个电容结构,所 述电容结构的第一端均连接到所属的电容模块的电源端,所述电容结构的第二 端均连接到所属的电容模块的接地端。

15、在一些实施例中,所述电容结构为柱状电容结构。

16、在一些实施例中,所述连续区域在第二方向上存在第一开口和第二开口, 且所述第一开口和所述第二开口沿所述逻辑模块对称分布;

17、在所述数据处理结构有多个的情况下,多个所述数据处理结构沿第二方向 依次排列;其中,所述数据采样模块中连续区域的第一开口与相邻的所述数据 采样模块中连续区域的第二开口连通,以使得所有的数据采样模块的连续区域 连通。

18、在一些实施例中,所述控制模块包括第一控制模块和第二控制模块;在第 二方向上,所述第一控制模块和所述第二控制模块对称的位于所述逻辑模块的 两侧;

19、在第一方向上,所述第一控制模块的长度和所述第二控制模块的长度均为 第三值,所述逻辑模块的长度为第四值,且所述第四值与所述第一值之和大于 所述第三值。

20、在一些实施例中,在第二方向上,所述数据处理结构中的第一控制模块与 另一所述数据处理结构中的第二控制模块相邻;在多个所述电容模块中,其中 一个所述电容模块为所述第一控制模块和相邻的所述第二控制模块共同提供电 源去噪功能。

21、在一些实施例中,所述数据采样模块至少为并转串模块,所述第一阱区和 所述第二阱区为深n阱。

22、第二方面,本公开实施例提供了一种半导体结构,该半导体结构包括多个 如第一方面所述的数据处理结构。

23、第三方面,本公开实施例提供了一种存储器,该存储器包括如第二方面所 述的半导体结构。

24、本公开实施例提供了一种数据处理结构、半导体结构和存储器,该数据处 理结构包括数据采样模块,且数据采样模块包括逻辑模块和控制模块,控制模 块位于逻辑模块的外围;逻辑模块包括第一阱区,控制模块包括第二阱区,第 一阱区与第二阱区之间存在间隔,以使得控制模块和逻辑模块分离设置;其中, 控制模块,用于产生使能控制信号;逻辑模块,用于接收第一数据信号、时钟 信号和使能控制信号;在使能控制信号有效的情况下,利用时钟信号对第一数 据信号进行采样处理,输出第二数据信号。这样,由于控制模块和逻辑模块完 全分离,能够改善控制模块给逻辑模块带来的干扰问题,提高逻辑模块的数据采样效果,降低衬底噪声。

技术特征:

1.一种数据处理结构,其特征在于,所述数据处理结构包括数据采样模块,且所述数据采样模块包括逻辑模块和控制模块,所述控制模块位于所述逻辑模块的外围;所述逻辑模块包括第一阱区,所述控制模块包括第二阱区,所述第一阱区与所述第二阱区之间存在间隔,以使得所述控制模块和所述逻辑模块分离设置;其中,

2.根据权利要求1所述的数据处理结构,其特征在于,

3.根据权利要求1-2任一项所述的数据处理结构,其特征在于,所述数据处理结构还包括数据缓冲模块,所述数据缓冲模块用于输出所述第一数据信号,或者接收所述第二数据信号;

4.根据权利要求3所述的数据处理结构,其特征在于,

5.根据权利要求4所述的数据处理结构,其特征在于,

6.根据权利要求5所述的数据处理结构,其特征在于,所述数据处理结构还包括多个电容模块;其中,

7.根据权利要求6所述的数据处理结构,其特征在于,所述电容模块的电源端通过金属层和接触结构连接到电源信号端,所述电容模块的接地端通过金属层和接触结构连接到地信号端;

8.根据权利要求6所述的数据处理结构,其特征在于,每一所述电容模块均包括并联设置的多个电容结构,所述电容结构的第一端均连接到所属的电容模块的电源端,所述电容结构的第二端均连接到所属的电容模块的接地端。

9.根据权利要求8所述的数据处理结构,其特征在于,所述电容结构为柱状电容结构。

10.根据权利要求6所述的数据处理结构,其特征在于,所述连续区域在第二方向上存在第一开口和第二开口,且所述第一开口和所述第二开口沿所述逻辑模块对称分布;

11.根据权利要求10所述的数据处理结构,其特征在于,

12.根据权利要求10所述的数据处理结构,其特征在于,在第二方向上,所述数据处理结构中的第一控制模块与另一所述数据处理结构中的第二控制模块相邻;在多个所述电容模块中,其中一个所述电容模块为所述第一控制模块和相邻的所述第二控制模块共同提供电源去噪功能。

13.根据权利要求2所述的数据处理结构,其特征在于,

14.一种半导体结构,其特征在于,所述半导体结构包括多个如权利要求1-13任一项所述的数据处理结构。

15.一种存储器,其特征在于,所述存储器包括如权利要求14所述的半导体结构。

技术总结

本公开实施例提供了一种数据处理结构、半导体结构和存储器,该数据处理结构包括数据采样模块,且数据采样模块包括逻辑模块和控制模块,控制模块位于逻辑模块的外围;逻辑模块包括第一阱区,控制模块包括第二阱区,第一阱区与第二阱区之间存在间隔,以使得控制模块和逻辑模块分离设置;其中,控制模块,用于产生使能控制信号;逻辑模块,用于接收第一数据信号、时钟信号和使能控制信号;在使能控制信号有效的情况下,利用时钟信号对第一数据信号进行采样处理,输出第二数据信号。这样,由于控制模块和逻辑模块完全分离,能够改善控制模块给逻辑模块带来的干扰问题,提高逻辑模块的数据采样效果,降低衬底噪声。

技术研发人员:单雪,郭迎冬,徐静

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!