通信接口结构和管芯对管芯封装的制作方法

本发明涉及用于数据通信的两个集成电路(integrated circuit;ic)管芯之间的接口,且尤其是涉及一种通信接口结构(communication interface structure)和管芯对管芯(die-to-die)封装。

背景技术:

1、基于半导体集成电路的数字电子设备(例如移动电话、数码相机、个人数字助理(personal digital assistants;pdas)等)被设计成必须具有更强大的功能性,以适应现代数字世界中的各种应用。然而,作为半导体制造趋势的数字电子设备希望在具有改进的功能性和更高性能的情况下变得更小和更轻。半导体装置可封装成2.5d半导体装置,其中若干电路芯片可集成为更大的集成电路,其中接触元件、中介层(interposer)或再分布层(redistribution layer;rdl)被用于在芯片之间进行连接。

2、集成扇出型(integrated fan-out;info)和衬底上晶片上芯片(chip-on-wafer-on-substrate;cowos)的封装技术已被提出,来封装并排装配的多个芯片。

3、关于管芯对管芯封装,以glink(ucie合规性)多管芯互连为例,可能需要通过中介层或再分布层(rdl)将系统单芯片(system on a chip;soc)管芯连接到高带宽存储器(high bandwidth memory;hbm)管芯。换句话说,中介层或rdl中的接口包括很多凸块和迹线以在其间连接。

4、接口中的交错凸块分配已经被开发用于硅可布线性的通孔。交错凸块图(staggerbump map)比直列式凸块图(in-line bump map)具有更高的海滨效率(beachfrontefficiency)。然而,在所述交错凸块分配中,在w-e(西-东)方向的每个界面上只能提供一条迹线。换句话说,在先进封装技术(advanced packaging technology;apt)的glink多芯片互连设计中,微凸块图(ubump map)只能支持一个方向(例如,南北方向)的高速互连。

5、为了增强hbm管芯和soc管芯之间的信号完整性(signal integrity),需要适当设计rdl的通信接口结构。

技术实现思路

1、基于半导体集成电路的数字电子设备(例如移动电话、数码相机、个人数字助理(personal digital assistants;pdas)等)被设计成必须具有更强大的功能性,以适应现代数字世界中的各种应用。然而,作为半导体制造趋势的数字电子设备希望在具有改进的功能性和更高性能的情况下变得更小和更轻。半导体装置可封装成2.5d半导体装置,其中若干电路芯片可集成为更大的集成电路,其中接触元件、中介层(interposer)或再分布层(redistribution layer;rdl)被用于在芯片之间进行连接。

2、集成扇出型(integrated fan-out;info)和衬底上晶片上芯片(chip-on-wafer-on-substrate;cowos)的封装技术已被提出,来封装并排装配的多个芯片。

3、关于管芯对管芯封装,以glink(ucie合规性)多管芯互连为例,可能需要通过中介层或再分布层(rdl)将系统单芯片(system on a chip;soc)管芯连接到高带宽存储器(high bandwidth memory;hbm)管芯。换句话说,中介层或rdl中的接口包括很多凸块和迹线以在其间连接。

4、接口中的交错凸块分配已经被开发用于硅可布线性的通孔。交错凸块图(staggerbump map)比直列式凸块图(in-line bump map)具有更高的海滨效率(beachfrontefficiency)。然而,在所述交错凸块分配中,在w-e(西-东)方向的每个界面上只能提供一条迹线。换句话说,在先进封装技术(advanced packaging technology;apt)的glink多芯片互连设计中,微凸块图(ubump map)只能支持一个方向(例如,南北方向)的高速互连。

5、为了增强hbm管芯和soc管芯之间的信号完整性(signal integrity),需要适当设计rdl的通信接口结构。

技术特征:

1.一种通信接口结构,其特征在于,包括:

2.根据权利要求1所述的通信接口结构,其特征在于,多个所述第二凸块的行数与多个所述第一凸块的行数相同,并且多个所述第二凸块的列数是多个所述第一凸块的列数的一半。

3.根据权利要求1所述的通信接口结构,其特征在于,还包括:

4.根据权利要求1所述的通信接口结构,其特征在于,还包括:

5.根据权利要求1所述的通信接口结构,其特征在于,所述奇数行的所述第一凸块彼此对齐,且所述偶数行的所述第一凸块彼此对齐。

6.根据权利要求1所述的通信接口结构,其特征在于,相邻列中的所述第一凸块相互交错配置。

7.根据权利要求1所述的通信接口结构,其特征在于,沿行方向的多个所述第二凸块中的两个之间的间距大于沿所述行方向的多个所述第二凸块之一与多个所述第一凸块之一之间的间距。

8.根据权利要求1所述的通信接口结构,其特征在于,每条所述导线在平面图中具有c形或u形。

9.一种管芯对管芯封装,其特征在于,包括:

10.根据权利要求9所述的管芯对管芯封装,其特征在于,所述多个第二凸块的行数与所述多个第一凸块的行数相同,并且所述多个第二凸块的列数是所述多个第一凸块的列数的一半。

11.根据权利要求9所述的管芯对管芯封装,其特征在于,所述通信接口结构还包括多条第一迹线,设置在多个所述第二凸块下方的东西方向,且多条所述第一迹线位于多个所述第二凸块中的两个之间。

12.根据权利要求9所述的管芯对管芯封装,其特征在于,所述通信接口结构还包括多条第二迹线,沿南北方向设置在多个所述第二凸块下方,以及多条所述第二迹线位于多个所述第二凸块中的两个之间。

13.根据权利要求9所述的管芯对管芯封装,其特征在于,所述奇数行的所述第一凸块彼此对齐,且所述偶数行的所述第一凸块彼此对齐。

14.根据权利要求9所述的管芯对管芯封装,其特征在于,相邻列中的所述第一凸块相互交错配置。

15.根据权利要求9所述的管芯对管芯封装,其特征在于,沿行方向的多个所述第二凸块中的两个之间的间距大于沿所述行方向的多个所述第二凸块之一与多个所述第一凸块之一之间的间距。

16.根据权利要求9所述的管芯对管芯封装,其特征在于,每条所述导线在平面图中具有c形或u形。

17.根据权利要求9所述的管芯对管芯封装,其特征在于,所述通信接口结构是中介层或重分布层。

18.根据权利要求9所述的管芯对管芯封装,其特征在于,还包括在所述第一管芯和所述第二管芯下方的凸点底部金属化结构。

19.根据权利要求9所述的管芯对管芯封装,其特征在于,所述第一管芯是系统单芯片管芯,并且所述第二管芯是高带宽存储器管芯。

20.根据权利要求9所述的管芯对管芯封装,其特征在于,所述第一管芯相对于所述第二管芯沿行方向横向偏移。

技术总结

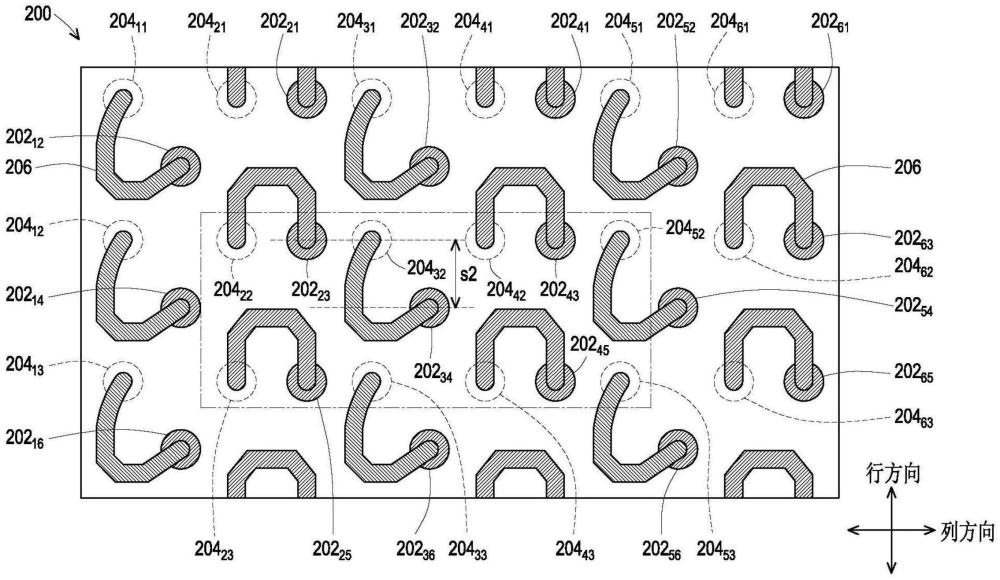

本发明提供一种通信接口结构以及管芯对管芯(Die‑to‑Die)封装。通信接口结构包括排列成第一行列配置的第一凸块、排列成第二行列配置的第二凸块以及设置在第一凸块和第二凸块之间以将每个第一凸块连接到每个第二凸块的迹线。相邻行中的第一凸块彼此交错配置。第二凸块设置在第一凸块下方或上方,其中偶数行中的每个第二凸块位于从偶数行中的每个第一凸块的中心沿列方向偏移的位置处,以及奇数行中的每个第二凸块在列方向上位于偶数行中的两个第二凸块之间的位置。

技术研发人员:杨昇帆,洪志强,林元鸿,许世弦,毅格·艾尔卡诺维奇

受保护的技术使用者:创意电子股份有限公司

技术研发日:

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!