半导体芯片、晶圆及其制造方法、封装结构及封装方法与流程

本发明实施例涉及半导体封装,尤其涉及一种半导体芯片、晶圆及其制造方法、封装结构及封装方法。

背景技术:

1、在半导体制造中,随着超大规模集成电路的发展趋势,集成电路特征尺寸持续减小。相应的,对集成电路的封装要求也日益提高,在多芯片组件(multichip-module,mcm)x、y平面内的二维封装的基础上,沿z方向堆叠的3d封装技术得到了充分发展,且所述3d封装技术具有更高密度。

2、三维集成电路(3d ic:three-dimensional integrated circuit)是利用先进的芯片堆叠技术制备而成,将具不同功能的芯片堆叠成具有三维结构的集成电路。相较于二维结构的集成电路,三维集成电路的堆叠技术不仅可使三维集成电路信号传递路径缩短,还可以使三维集成电路的运行速度加快,从而满足半导体器件更高性能、更小尺寸、更低功耗以及更多功能的需求。

3、根据三维集成电路中芯片间连接方法的不同,使堆叠的芯片能互连的技术分为金属引线封装(wire bonding)、倒装芯片封装(wafer bonding)以及穿透硅通孔封装(through silicon via,tsv)。其中,由于tsv封装技术具有能够使芯片在三维方向堆叠的密度增大、芯片之间的互连线缩短、外形尺寸减小,并且可以大大改善芯片速度和低功耗的性能,成为了三维集成电路中堆叠芯片实现互连的最常用的方法。

技术实现思路

1、本发明实施例解决的问题是提供一种半导体芯片、晶圆及其制造方法、封装结构及封装方法,提高封装可靠性。

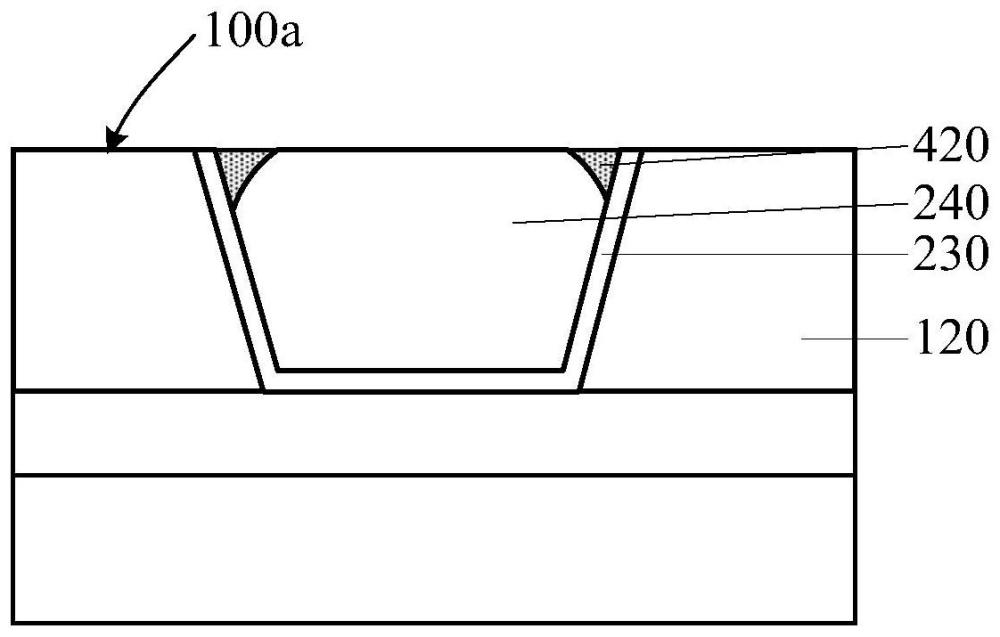

2、为解决上述问题,本发明实施例提供一种半导体芯片,包括键合面,半导体芯片包括:基底,包括衬底和位于衬底上的电路结构层;介质层,位于基底上,介质层顶面为键合面;键合焊垫,位于介质层中,键合面露出键合焊垫顶面;阻挡层,覆盖键合焊垫的侧壁和底部,阻挡层侧壁与键合焊垫顶角间具有间隙;填充层,填充于间隙中。

3、相应的,本发明实施例还提供一种晶圆,包括多个本发明实施例提供的半导体芯片。

4、相应的,本发明实施例还提供一种封装结构,包括:相键合的第一芯片和第二芯片,第一芯片和第二芯片均具有键合面,且第一芯片和第二芯片均包括被相对应的键合面暴露的键合焊垫,第一芯片的键合焊垫与第二芯片的键合焊垫相对设置并键合,其中,第一芯片的键合焊垫与第二芯片的键合焊垫在键合面重叠或不重叠;其中,第一芯片和第二芯片中的一者或两者为本发明实施例提供的半导体芯片。

5、相应的,本发明实施例还提供一种封装方法,包括:提供第一芯片和第二芯片,第一芯片和第二芯片均具有键合面,且第一芯片和第二芯片均包括被相对应的键合面暴露的键合焊垫,其中,第一芯片和第二芯片中的一者或两者为本发明实施例提供的半导体芯片;使第一芯片的键合面与第二芯片的键合面相对设置并实现键合,第一芯片的键合焊垫与第二芯片的键合焊垫相键合,其中,第一芯片的键合焊垫与第二芯片的键合焊垫在键合面重叠或不重叠。

6、相应的,本发明实施例还提供一种晶圆制造方法,包括键合面,晶圆制造方法包括:提供基底,基底上形成有介质层,介质层顶面为键合面;在键合面一侧的介质层中形成开口;在开口的侧壁形成阻挡层;在形成有阻挡层的开口中形成键合焊垫,键合面露出键合焊垫顶面,阻挡层侧壁与键合焊垫顶角间形成有间隙;形成填充间隙的填充层。

7、与现有技术相比,本发明实施例的技术方案具有以下优点:

8、本发明实施例提供的半导体芯片中,阻挡层侧壁与键合焊垫顶角间具有间隙,填充层填充于间隙中;填充层填充于间隙中,当后续采用半导体芯片进行键合时,有利于减小半导体芯片的键合面处产生空洞的概率,增加该半导体芯片与其他芯片或晶圆的接触面积,从而有利于减小因该半导体芯片键合面处的空洞而导致键合良率下降的概率,进而提高了该半导体芯片与其他芯片或晶圆的键合良率,相应提高了封装可靠性。

9、本发明实施例提供的晶圆中,填充层填充于间隙中,当后续采用晶圆进行键合时,有利于减小晶圆的键合面处产生空洞的概率,增加该晶圆与其他芯片或晶圆的接触面积,从而有利于减小因该晶圆键合面处的空洞而导致键合良率下降的概率,进而提高了该晶圆与其他芯片或晶圆的键合良率,相应提高了封装可靠性。

10、本发明实施例提供的封装结构中,填充层填充于间隙中,当有利于减小封装结构的键合面处产生空洞的概率,增加相键合的半导体芯片的接触面积,从而有利于减小因封装结构的键合面处的空洞而导致键合良率下降的概率,进而提高了封装结构的键合良率,相应提高了封装可靠性。

11、本发明实施例提供的封装方法中,填充层填充于间隙中,当有利于减小封装时键合面处产生空洞的概率,增加相键合的半导体芯片的接触面积,从而有利于减小因封装时键合面处的空洞而导致键合良率下降的概率,进而提高了封装结构的键合良率,相应提高了封装可靠性。

12、本发明实施例提供的晶圆制造方法中,填充层填充于间隙中,当后续采用晶圆进行键合时,有利于减小晶圆的键合面处产生空洞的概率,增加该晶圆与其他芯片或晶圆的接触面积,从而有利于减小因该晶圆键合面处的空洞而导致键合良率下降的概率,进而提高了该晶圆与其他芯片或晶圆的键合良率,相应提高了封装可靠性。

技术特征:

1.一种半导体芯片,其特征在于,所述半导体芯片包括键合面,所述半导体芯片包括:

2.如权利要求1所述的半导体芯片,其特征在于,所述填充层的材料包括介质材料。

3.如权利要求2所述的半导体芯片,其特征在于,所述介质材料包括氮化硅或氧化硅。

4.如权利要求1所述的半导体芯片,其特征在于,所述介质层、键合焊垫、阻挡层和填充层的顶面相齐平。

5.如权利要求1所述的半导体芯片,其特征在于,所述键合焊垫的宽度大于或等于0.3μm。

6.如权利要求1所述的半导体芯片,其特征在于,所述填充层的材料与所述介质层的材料相同。

7.如权利要求1所述的半导体芯片,其特征在于,所述键合焊垫的材料包括铜、钛、铝、金、镍、铁、锡、银、锌和铬中的一种或多种。

8.如权利要求1所述的半导体芯片,其特征在于,所述半导体芯片还包括:互连结构,位于所述键合焊垫底部的介质层中,并与所述键合焊垫电连接。

9.一种晶圆,其特征在于,包括多个如权利要求1~8中任意一项所述的半导体芯片。

10.一种封装结构,其特征在于,包括:

11.如权利要求10所述的封装结构,其特征在于,所述第一芯片的数量为多个、并集成于第一晶圆中,所述第二芯片的数量为多个、并集成于第二晶圆中,所述第一晶圆和第二晶圆的键合面相对设置并键合。

12.一种封装方法,其特征在于,包括:

13.如权利要求12所述的封装方法,其特征在于,所述第一芯片的数量为多个、并集成于第一晶圆中,所述第二芯片的数量为多个、并集成于第二晶圆中;

14.如权利要求12所述的封装方法,其特征在于,使所述第一芯片的键合面与所述第二芯片的键合面相对设置并实现键合后,所述封装方法还包括:对所述键合焊垫进行第一膨胀处理。

15.一种晶圆制造方法,其特征在于,所述晶圆包括键合面,所述晶圆制造方法包括:

16.如权利要求15所述的晶圆制造方法,其特征在于,形成填充所述间隙的填充层的步骤包括:形成填充于所述间隙中、且覆盖所述键合焊垫和键合面的填充材料层;

17.如权利要求16所述的晶圆制造方法,其特征在于,形成所述填充材料层的工艺包括化学气相沉积工艺或原子层沉积工艺。

18.如权利要求16所述的晶圆制造方法,其特征在于,采用化学机械研磨工艺去除高于所述键合面的填充材料层。

19.如权利要求15所述的晶圆制造方法,其特征在于,在所述开口的侧壁形成阻挡层的步骤包括:形成覆盖所述开口底面和侧壁、以及键合面的阻挡材料层,其中位于所述开口底面和侧壁的阻挡材料层作为阻挡层;

20.如权利要求20所述的晶圆制造方法,其特征在于,在形成有所述阻挡层的开口中形成键合焊垫的步骤包括:形成填充所述开口并覆盖所述阻挡材料层的焊垫材料层;

21.如权利要求20所述的晶圆制造方法,其特征在于,在同一步骤中,去除高于所述键合面的阻挡材料层和焊垫材料层。

22.如权利要求21所述的晶圆制造方法,其特征在于,采用化学机械研磨工艺去除高于所述键合面的阻挡材料层和焊垫材料层。

23.如权利要求15所述的晶圆制造方法,其特征在于,在形成有所述阻挡层的开口中形成键合焊垫之后,形成填充所述间隙的填充层之前,所述晶圆制造方法还包括:对所述键合焊垫进行第二膨胀处理。

24.如权利要求23所述的晶圆制造方法,其特征在于,采用热处理合金工艺对所述键合焊垫进行第二膨胀处理。

25.如权利要求15所述的晶圆制造方法,其特征在于,所述填充层的材料包括介质材料。

26.如权利要求15所述的晶圆制造方法,其特征在于,所述填充层的材料与所述介质层的材料相同。

技术总结

一种半导体芯片、晶圆及其制造方法、封装结构及封装方法,半导体芯片包括键合面,半导体芯片包括:基底,包括衬底和位于衬底上的电路结构层;介质层,位于基底上,介质层顶面为键合面;键合焊垫,位于介质层中,键合面露出键合焊垫顶面;阻挡层,覆盖键合焊垫的侧壁和底部,阻挡层侧壁与键合焊垫顶角间具有间隙;填充层,填充于间隙中。本发明提高了封装可靠性。

技术研发人员:隋凯

受保护的技术使用者:中芯国际集成电路制造(北京)有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!